# WIDEBAND QUAD DIGITAL DOWN-CONVERTER/UP-CONVERTER

### FEATURES

- Four Independently Configurable Wideband Down-Converter or Up-Converter Channels

- Four Channel Down Convert Mode

- Four Channel Up Convert Mode

- Two Channels Down and Two Channels Up Mode

- **Down-Conversion Channel Mode**

- Input Rates to 160-MSPS for Four Channels, 320-MSPS for Two Channels in **Double Rate Mode**

- Four Wideband Down-Conversion **Channels Support UMTS Standards**

- 115-dB SFDR

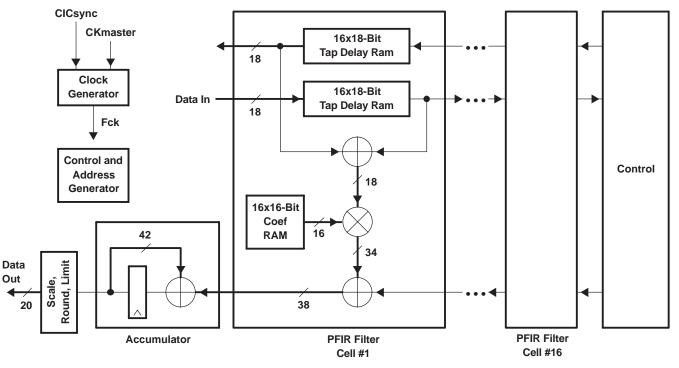

- FIR Filter Block Consists of 16 Cells Providing Up to 256 Taps Per Channel

- 64 Parallel Input Bits and 64 Parallel **Output Bits Provide Flexible I/O Options**

- Many Multiplex Output Options

- **Up-Conversion Channel Mode**

- Output Rates to 160-MSPS for Four Channels, 320-MSPS for Two Channels

- Four Up-Conversion Channels Support **UMTS Standards**

- FIR Filter Block Consists of 16 Cells

- Providing up to 256 Taps Per Channel

- 64 Parallel Input Bits and 64 Parallel Output Bits Provide Flexible I/O Options

- Multiple Real and Complex Outputs

- Two Channel Double Rate Real Output Mode With Rates to 320 MSPS

- Outputs Can Be Independent, Summed Into Two or One Output(s), and Optionally Merged With Multiple GC5016 Chips

- **JTAG Boundary Scan**

- 3.3-V I/O, 1.8-V Core

- Power Dissipation: <1 W for Four Channels

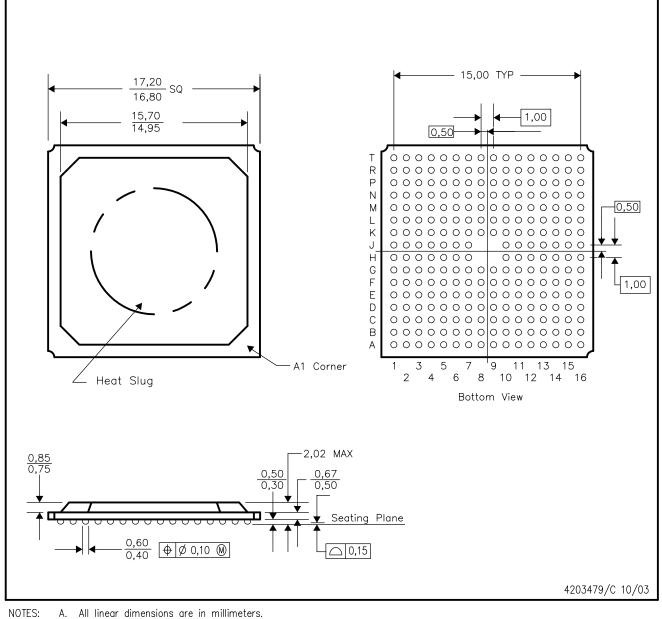

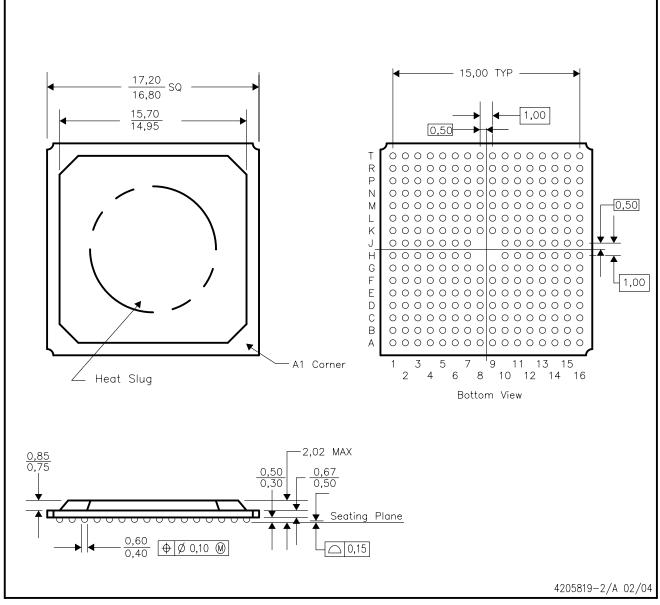

- Package: 252-Ball, 17-mm PBGA, 1-mm Pitch

### APPLICATIONS

- **Cellular Base Transceiver Station Transmit** and Receive Channels WWW.DZSC.COM

- WCDMA

- CDMA2000

- Radar

- **General Filtering**

- Test and Measurement

#### **Table of Contents**

| 1  | Description                      | 2 | 12 | Terminal Functions          | 10 |

|----|----------------------------------|---|----|-----------------------------|----|

| 2  | Ordering Information             | 2 | 13 | GC5016 Down-Conversion Mode | 11 |

| 3  | Other Reference Material         | 2 | 14 | GC5016 Up-Conversion Mode   | 33 |

| 4  | Absolute Maximum Ratings         | 3 | 15 | GC5016 in Transceiver Mode  | 53 |

| 5  | Recommended Operating Conditions | 3 | 16 | General GC5016 Features     | 53 |

| 6  | DC Characteristics               | 3 | 17 | Configuration Software      | 63 |

| 7  | AC characteristics               | 4 | 18 | Examples                    | 81 |

| 8  | Thermal Characteristics          | 4 | 19 | Board Bring-Up Procedure    | 83 |

| 9  | Power Consumption                | 5 |    | Mechanical Data             | 85 |

| 10 | Functional Block Diagram         | 6 |    |                             |    |

| 11 | Pin Assignments                  | 9 |    |                             |    |

|    | WWW.925                          |   |    |                             |    |

|    |                                  |   |    |                             |    |

|    |                                  |   |    |                             |    |

lease be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. com

60

### **1 DESCRIPTION**

The GC5016 is a flexible wideband 4-channel digital up-converter and down-converter. The GC5016 is designed for high-speed, high bandwidth digital signal processing applications like 3G cellular base transceiver station transmit and receive channels. The GC5016 is also applicable for general-purpose digital filtering applications. The four identical processing channels can be independently configured for up-conversion, down-conversion, or a combination of two up-conversion and two down-conversion channels.

In up-conversion mode, the channel accepts real or complex signals, interpolates them by programmable amounts ranging from 1 to 4096, and modulates them up to selected center frequencies. The 4 digital up-converter signals can be output individually, summed together on one or two outputs on a single GC5016, or optionally summed between multiple GC5016s. Channels can be used in pairs to increase the output sample rate, to increase filtering capacity, to increase the input bandwidth, or any combination. Each channel contains a user programmable input filter (PFIR), which can be used to shape the transmitted signal's spectrum or as a Nyquist transmit filter for shaping digital data such as QPSK, GMSK, or QAM symbols.

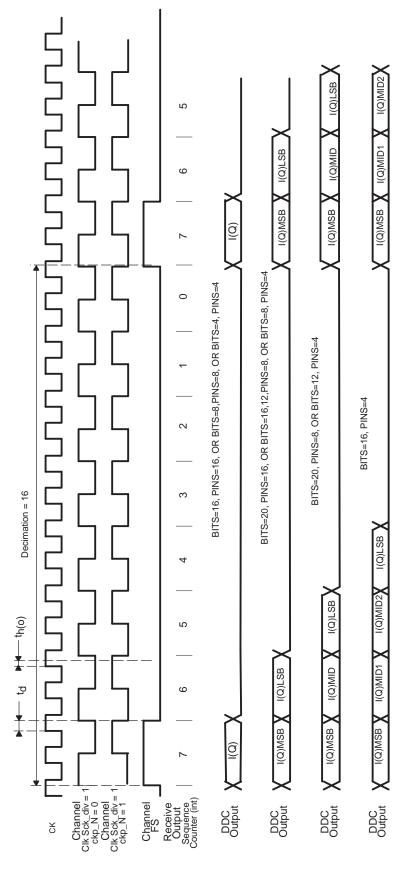

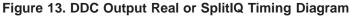

In down-conversion mode, the channel accepts real or complex signals, demodulates them from selected carrier frequencies, decimates them by programmable amounts ranging from 1 to 4096, applies a gain from a user defined automatic gain control, and produces 20-bit outputs. The frequencies and phase offsets of the four sine/cosine sequence generators can be independently specified, as can the decimation and filtering of each circuit. Channels can be synchronized to support beam forming or frequency hopped systems. The output from the down-conversion channel is formatted and output in up to four output ports as either real or complex data.

# **2 ORDERING INFORMATION**

| PART NAME  | TEMPERATURE   | PACKAGE           | DESCRIPTION             |  |  |

|------------|---------------|-------------------|-------------------------|--|--|

| GC5016-PB  | -40°C to 85°C | GDJ (S-PBGA-N252) | 252 ball PBGA           |  |  |

| GC5016-PBZ | −40°C to 85°C | ZDJ (S-PBGA-N252) | 252 ball lead free PBGA |  |  |

# **3 OTHER REFERENCE MATERIALS**

The TI Web site has developer toolkit and application notes that provide application specific programming and configuration information. The CMD5016 configuration program, along with a user specified source and tap coefficient file, is used to configure the GC5016 registers. The GC5016 register settings are intended to be configured through the development toolkit software.

**NOTE:**Names in italics refer to parameter inputs to the cmd5016 software configuration program.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **4 ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                           |                                         | GC5016                            |  |  |

|-----------------------------------------------------------|-----------------------------------------|-----------------------------------|--|--|

| Pad ring supply voltage, VPAD                             | -0.3 V to 4 V                           |                                   |  |  |

| Core supply voltage, VCORE                                |                                         | –0.3 V to 2.3 V                   |  |  |

| Input voltage (undershoot and overshoot), $V_{\text{IN}}$ |                                         | –0.5 V to V <sub>PAD</sub> +0.5 V |  |  |

| Storage temperature, T <sub>stg</sub>                     | –65°C to 150°C                          |                                   |  |  |

| Junction temperature, TJ                                  | 105°C                                   |                                   |  |  |

| Lead soldering temperature (10 seconds)                   | Lead soldering temperature (10 seconds) |                                   |  |  |

|                                                           | Human body model                        | 2 kV                              |  |  |

| ESD classification                                        | Machine body model                      | 200 V                             |  |  |

|                                                           | Charged device model                    | 500 V                             |  |  |

| Moisture sensitivity                                      | Level 3                                 |                                   |  |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **5 RECOMMENDED OPERATING CONDITIONS**

|                                                      | MIN | MAX | UNITS |

|------------------------------------------------------|-----|-----|-------|

| Pad ring supply voltage, V <sub>PAD</sub>            | 3   | 3.6 | V     |

| Core supply voltage, VCORE                           | 1.6 | 2   | V     |

| Temperature ambient, no air flow, T <sub>A</sub> (1) | -40 | 85  | °C    |

| Junction temperature, $T_{J}^{(2)}$                  |     | 105 | °C    |

(1) Chips specifications in the AC CHARACTERISTICS and DC CHARACTERISTICS tables are production tested at 100°C case temperature. QA tests are performed at 85°C case temperature.

(2) Thermal management may be required for full rate operation (see the THERMAL CHARACTERISTICS table). The circuit is designed for junction temperatures up to 125°C. Sustained operation at elevated temperatures reduces long-term reliability. Lifetime calculations based on maximum junction temperature of 105°C.

# **6 DC CHARACTERISTICS**

-40°C to 85°C case temperature unless otherwise noted

|                                                                                                                                          | VPAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                                                                                                | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MAX                                                                                                                                                                                                                                                                                                                                                             | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Voltage input low (1)                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.8                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Voltage input high (1)                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Voltage output low $(I_{OL} = 2 \text{ mA})$ (1)                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Voltage output high $(I_{OH} = -2 \text{ mA})$ (1)                                                                                       | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Leakage current ( $V_{IN} = 0 V$ or VPAD), inputs or outputs in high-impedance state condition (1)                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                               | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pullup current (V <sub>IN</sub> = 0 V) ( TDI, TMS, TCK) (1)                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35                                                                                                                                                                                                                                                                                                                                                              | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Quiescent supply current, I <sub>CORE</sub> or I <sub>PAD</sub> ( $V_{IN}=0$ or $V_{PAD}$ , $\overline{RST} = \overline{TRST} = 0$ ) (1) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                               | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Data input capacitance (all inputs except CK) (2)                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                 | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Clock input capacitance (CK input) <sup>(2)</sup>                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                 | pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                          | Voltage input high (1)<br>Voltage output low (I <sub>OL</sub> = 2 mA) (1)<br>Voltage output high (I <sub>OH</sub> = $-2$ mA) (1)<br>Leakage current (V <sub>IN</sub> = 0 V or VPAD), inputs or outputs in high-impedance state condition (1)<br>Pullup current (V <sub>IN</sub> = 0 V) ( TDI, TMS, TCK) (1)<br>Quiescent supply current, I <sub>CORE</sub> or I <sub>PAD</sub> (V <sub>IN</sub> =0 or V <sub>PAD</sub> , RST = TRST = 0) (1)<br>Data input capacitance (all inputs except CK) (2) | PARAMETERMINVoltage input low (1)Voltage input high (1)2Voltage output low (I <sub>OL</sub> = 2 mA) (1)2Voltage output low (I <sub>OL</sub> = 2 mA) (1)2.4Leakage current (V <sub>IN</sub> = 0 V or VPAD), inputs or outputs in high-impedance state condition (1)5Pullup current (V <sub>IN</sub> = 0 V) (TDI, TMS, TCK) (1)5Quiescent supply current, I <sub>CORE</sub> or IPAD(V <sub>IN</sub> =0 or VPAD, RST = TRST = 0) (1)5Data input capacitance (all inputs except CK) (2)5 | PARAMETERMINTYPVoltage input low (1)2Voltage input high (1)2Voltage output low (IOL = 2 mA) (1)2Voltage output high (IOH = -2 mA) (1)2.4Leakage current (VIN = 0 V or VPAD), inputs or outputs in high-impedance state condition (1)5Pullup current (VIN = 0 V) (TDI, TMS, TCK) (1)5Quiescent supply current, ICORE or IPAD(VIN=0 or VPAD, RST = TRST = 0) (1)4 | MINTYPMAXVoltage input low (1) $0.8$ Voltage input high (1) $2$ Voltage output low (I <sub>OL</sub> = 2 mA) (1) $2$ Voltage output high (I <sub>OH</sub> = -2 mA) (1) $2.4$ Leakage current (V <sub>IN</sub> = 0 V or VPAD), inputs or outputs in high-impedance state condition (1) $1$ Pullup current (V <sub>IN</sub> = 0 V) (TDI, TMS, TCK) (1) $5$ $35$ Quiescent supply current, I <sub>CORE</sub> or IPAD(V <sub>IN</sub> =0 or VPAD, RST = TRST = 0) (1) $4$ |

(1) Each part is tested with a 100°C case temperature for the given specification.

(2) Controlled by design and process and not directly tested.

NOTE: General: Voltages are measured at low speed. Output voltages are measured with the indicated current load.

General: Currents are measured at nominal voltages, high temperature (100°C for production test, 85°C for QA).

# 7 AC CHARACTERISTICS

-40°C to 85°C case, supplies across recommended range unless otherwise noted

|                                 | PARAMETER                                                                                                               | MIN | MAX | UNITS |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| fCK                             | Clock frequency (1)                                                                                                     | (3) | 160 | MHz   |

| <sup>t</sup> CKL                | Clock low period (below VIL) (1)                                                                                        | 2   |     | ns    |

| <sup>t</sup> CKH                | Clock high period (above VIH) <sup>(1)</sup>                                                                            | 2   |     | ns    |

| t <sub>r</sub> , t <sub>f</sub> | Clock rise and fall times (V <sub>IL</sub> to V <sub>IH</sub> ) $^{(4)}$                                                |     | 2   | ns    |

| t <sub>su</sub>                 | Input set up before CK goes high (AI, BI, CI, DI, SIA, or SIB) <sup>(1)</sup>                                           | 2   |     | ns    |

| t <sub>h</sub>                  | Input hold time after CK goes high (1)                                                                                  | 0.5 |     | ns    |

| t <sub>d</sub>                  | Data output delay from rising edge of CK. (AO, BO, CO, DO, IFLG, [A–D]FS, [A–D]CK, or SO) <sup>(1)</sup>                |     | 5   | ns    |

| <sup>t</sup> h(o)               | Data output hold from rising edge of CK (1)                                                                             | 1   |     | ns    |

| fJCK                            | JTAG clock frequency <sup>(1)</sup>                                                                                     |     | 40  | MHz   |

| <sup>t</sup> JCKL               | JTAG clock low period (below $V_{  L }$ (1)                                                                             | 10  |     | ns    |

| <sup>t</sup> JCKH               | JTAG clock high period (above V <sub>IH</sub> ) <sup>(1)</sup>                                                          | 10  |     | ns    |

| <sup>t</sup> su(J)              | JTAG input (TDI or TMS) set up before TCK goes high <sup>(1)</sup>                                                      | 1   |     | ns    |

| th(J)                           | JTAG input (TDI or TMS) hold time after TCK goes high <sup>(1)</sup>                                                    | 10  |     | ns    |

| <sup>t</sup> d(J)               | JTAG output (TDO) delay from falling edge of TCK <sup>(1)</sup>                                                         |     | 10  | ns    |

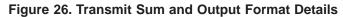

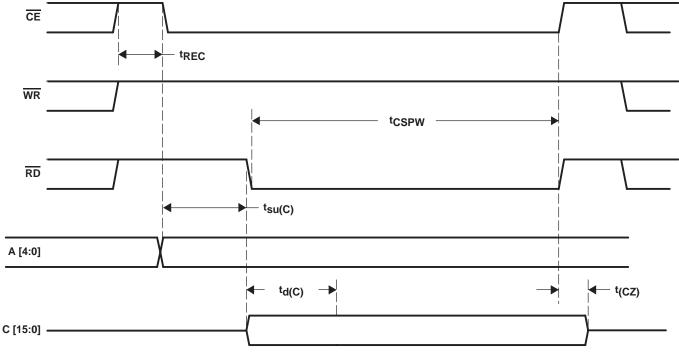

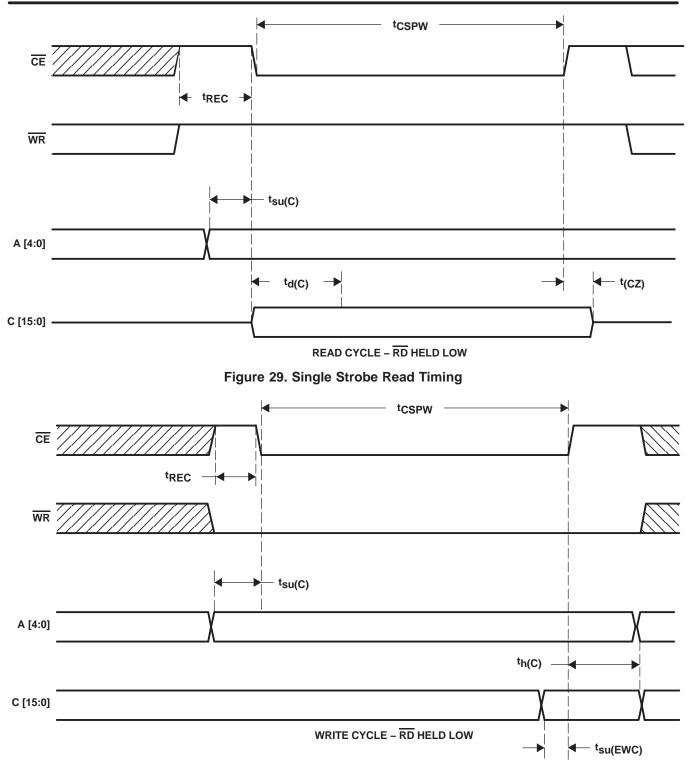

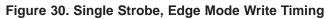

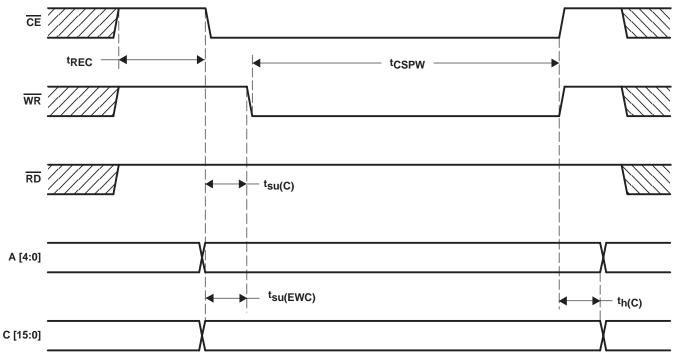

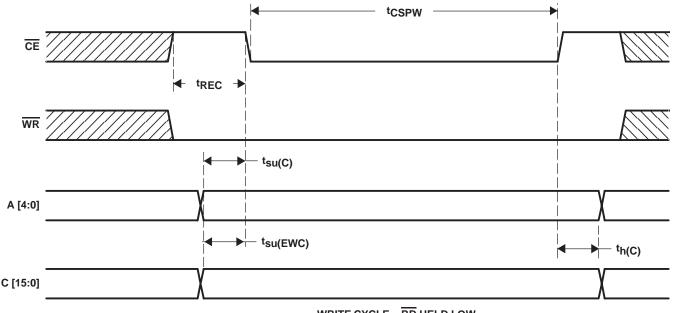

| <sup>t</sup> su(C)              | Control setup during reads or writes. (1)(5)                                                                            | 2   |     | ns    |

| t <sub>su</sub> (EWC)           | Control data setup during writes (normal mode). (1)(5)                                                                  | 4   |     | ns    |

| <sup>t</sup> h(C)               | Control hold during writes. (1)(5)                                                                                      | 1   |     | ns    |

| tCSPW                           | Control strobe ( $\overline{CE}$ and $\overline{WR}$ low) pulse width (write operation). (1)(5)                         | 20  |     | ns    |

| <sup>t</sup> d(C)               | Control output delay CE and RD low and A stable to C (read operation). (1)(5)                                           |     | 12  | ns    |

| <sup>t</sup> REC                | Control recovery time between reads or writes. (1)(5)                                                                   | 20  |     | ns    |

| <sup>t</sup> (CZ)               | End of read to HI-Z (2)(5)                                                                                              |     | 5   | ns    |

| IC(DYN)                         | Core dynamic supply current nominal voltages, 100 MHz, four channels active, full length filters, high temperature. (6) |     | 420 | mA    |

(1) Each part is tested with a 100°C case temperature for the given specification. Lots are sample tested at -40°C.

(2) Controlled by design and process and not directly tested.

(3) The minimum clock rate is calculated in the cmd5016 configuration program. It may be estimated by (1 + ncic – nfir) x 200 kHz.

(4) Recommended practice

(5) See Figure 27 through Figure 32.

(6) Each port is tested with a 100°C case temperature for the given specification.

General: Timing is measured from CK at VPAD/2 to input or output at VPAD/2. Output loading is a 50-Ω transmission line whose delay is calibrated out.

# 8 THERMAL CHARACTERISTICS

|                                          | 252 BGA |       |

|------------------------------------------|---------|-------|

| THERMAL CONDUCTIVITY                     | 1 W     | UNITS |

| Theta junction to ambient, $\theta_{JA}$ | 22      | °C/W  |

| Theta junction to case, $\theta_{JC}$    | 5       | °C/W  |

NOTE: Air flow reduces  $\theta_{JA}$  and is highly recommended.

## **9 POWER CONSUMPTION**

The maximum power consumption depends on the operating mode of the chip. The following equation estimates the typical power supply current for the chip. Chip-to-chip variation is typically  $\pm 5\%$ . The AC Characteristics provides the production test limit for current in a maximum configuration. It is 10% over the typical value.

Icore = (f<sub>CK</sub>/100 MHz) (Vcore/1.8 V) (Number\_of\_Active\_Channels/4) (0.75 + FIRDutyCycle) 220 mA

The FIRDutyCycle is calculated in the cmd5016 programming software. The '.ANL' extension of the user programming file contains the power analysis value.. It can be estimated by:

Down Converter Mode:

FIRDutyCycle = 1 for  $f_{CK}$ /Fout  $\leq$  16

16 x Fout/f<sub>CK</sub> otherwise

Up Converter Mode:

FIRDutyCycle = 1 for  $f_{CK}$ /Fin  $\leq$  32

32 x Fin/f<sub>CK</sub> otherwise

Current consumption on the pad supply is primarily due to the external loads and follows C x V x F. Internal loads are estimated at 2 pF per pin. Data outputs transition from a zero to a one once per four clocks, while clock outputs transition every cycle. The frame strobes consume negligible power due to the low transition frequency. In general:

Ipad =  $\Sigma$  DataPad/4 x C x F x V +  $\Sigma$  ClockPad x C x F x V

Typically loads are 20 pF per pin. A worst case current would be all four output ports operating at 125 MHz and the four output clocks with [A–D]CK active at 125 MHz.

Ipad = (64/4 + 4) x (C+2pF) x Fout x Vpad = 20 x 22 pF x 125 MHz x 3.3 V = 180 mA

SLWS142G - JANUARY 2003 - REVISED NOVEMBER 2005

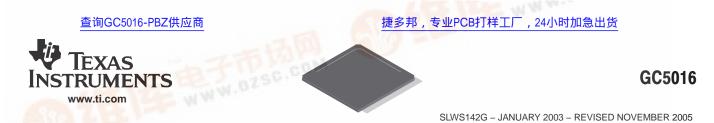

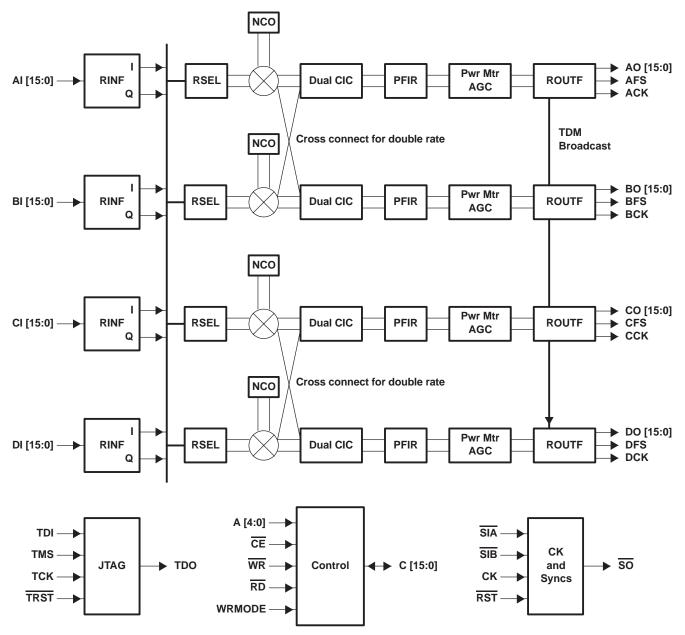

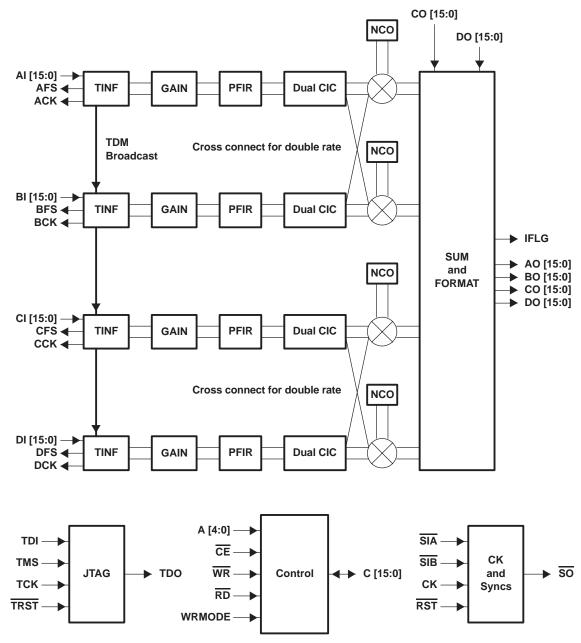

# **10** Functional Block Diagram

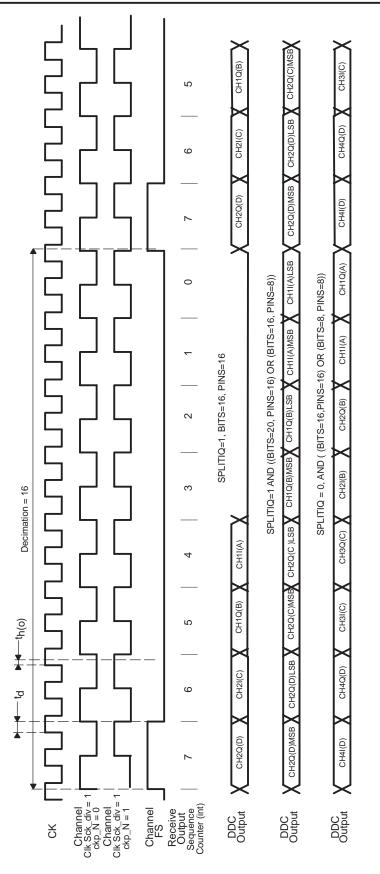

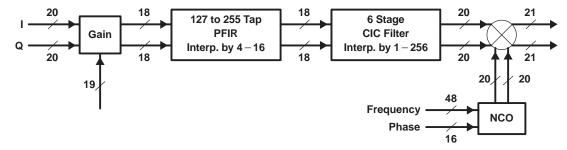

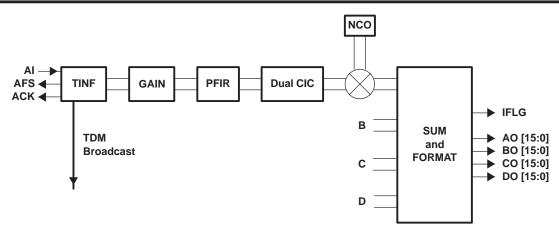

Figure 1. GC5016 in Digital Down-Conversion Mode

SLWS142G - JANUARY 2003 - REVISED NOVEMBER 2005

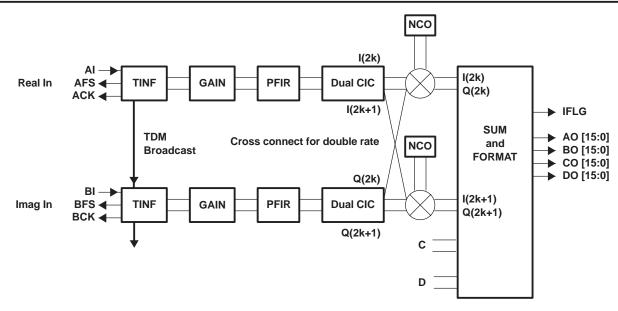

Figure 2. GC5016 in Digital Up-Conversion Mode

#### SLWS142G - JANUARY 2003 - REVISED NOVEMBER 2005

Figure 3. GC5016 in Transceiver Mode

# **11 PIN ASSIGNMENTS**

|   | 1    | 2    | 3      | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

|---|------|------|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Α | GND  | BCK  | BO14   | BO13 | AO11 | AO10 | BO8  | GND  | GND  | AO6  | BO4  | BO3  | AO1  | IFLG | TMS  | GND  |

| в | Al1  | BI0  | AO15   | AO14 | BO11 | BO10 | AO9  | VPAD | VPAD | BO5  | AO4  | BO2  | BO0  | TDI  | TRST | RST  |

| С | BI3  | BI2  | AIO    | AFS  | BO15 | AO12 | BO9  | AO7  | BO6  | AO5  | AO3  | BO1  | SO   | GND  | SIB  | CI15 |

| D | AI5  | AI3  | AI2    | BFS  | ACK  | AO13 | BO12 | BO7  | AO8  | AO2  | AO0  | TDO  | тск  | DI15 | DI14 | CI13 |

| Е | BI6  | Al6  | BI5    | BI1  | GND  | VPAD | VPAD | VPAD | VPAD | VPAD | VPAD | GND  | SIA  | DI13 | DI12 | DI11 |

| F | AI8  | BI7  | AI7    | BI4  | VCOR | GND  | GND  | VPAD | VPAD | GND  | GND  | VCOR | CI14 | CI12 | CI11 | DI10 |

| G | BI9  | AI9  | BI8    | Al4  | VCOR | GND  | GND  | GND  | GND  | GND  | GND  | VCOR | CI10 | CI9  | DI8  | CI8  |

| н | GND  | AI10 | BI11   | BI10 | VCOR | VCOR | GND  | /    | /    | GND  | VCOR | VCOR | DI9  | VPAD | DI7  | GND  |

| J | GND  | BI12 | AI12   | AI11 | VCOR | VCOR | GND  | /    | /    | GND  | VCOR | VCOR | DI5  | CI7  | DI6  | GND  |

| к | AI13 | BI13 | AI14   | BI14 | VCOR | GND  | GND  | GND  | GND  | GND  | GND  | VCOR | CI5  | DI4  | Cl4  | CI6  |

| L | AI15 | BI15 | СК     | A0   | VCOR | GND  | GND  | VPAD | VPAD | GND  | GND  | VCOR | ССК  | DI2  | CI3  | DI3  |

| м | A1   | A2   | A3     | A4   | GND  | VPAD | VPAD | VPAD | VPAD | VPAD | VPAD | GND  | DFS  | CI1  | DI1  | CI2  |

| N | CE   | RD   | WRMODE | C0   | C3   | C9   | C10  | DO1  | CO2  | C07  | CO12 | DO13 | CO15 | DCK  | CI0  | DIO  |

| Ρ | WR   | C1   | GND    | C5   | C8   | C14  | DO2  | CO4  | DO4  | CO6  | DO8  | CO11 | CO13 | GND  | DO15 | CFS  |

| R | C2   | C4   | C6     | C12  | C13  | DO0  | CO3  | VPAD | VPAD | DO5  | DO7  | CO9  | DO10 | DO12 | CO14 | DO14 |

| т | GND  | C7   | C11    | C15  | CO0  | CO1  | DO3  | GND  | GND  | CO5  | DO6  | CO8  | DO9  | CO10 | DO11 | GND  |

/ = No Ball

# **12 TERMINAL FUNCTIONS**

Bit 0 is the least significant bit on all buses. All outputs are able to be put into a high-impedance state. JTAG related inputs have pull-ups if an external pulldown is used, it must be less than 500  $\Omega$ . When I and Q are multiplexed, I comes first. All clocked inputs are registered on the rising edge of CK and all clocked outputs are released on the rising edge of CK, except for Jtag output (TDO). It is recommended that TRST have a user controlled pull-down. This input must be a '1' for JTAG testing, and is recommended to be '0' for normal operation.

| SIGNAL   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL  | I/O  |                                                                                                                                                                                                                                                                                                                                                                  |

| A[40]    | I    | Control address bus – Active high inputs<br>These pins are used to address the control registers within the chip. Each of the control registers within the chip are<br>assigned a unique address. A control register can be written to or read from by having the page register set to the<br>appropriate page and then setting A[40] to the register's address. |

| C[150]   | I/O  | Control data I/O bus – Active high bidirectional I/O pins<br>This is the 16-bit control data I/O bus. Control registers are written to or read from through these pins. The chip drives<br>these pins when CE is low, RD is low, and WR is high.                                                                                                                 |

| CE       | I    | Chip enable – Active low input pin<br>This control strobe enables the read or write operations.                                                                                                                                                                                                                                                                  |

| WR       | I    | Write enable – Active low input pin<br>The value on the C[150] pins is written into the register selected by the A[40] and page register when $\overline{WR}$ and $\overline{CE}$ are low.                                                                                                                                                                       |

| RD       | I    | Read enable – Active low input pin<br>The register selected by A[40] and the page register is output on the C[150] pins when $\overline{RD}$ and $\overline{CE}$ are low.                                                                                                                                                                                        |

| DATA I/O |      |                                                                                                                                                                                                                                                                                                                                                                  |

| AI[150]  | I    | Clocked input port A, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                                                                                                                                                               |

| BI[150]  | I    | Clocked input port B, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                                                                                                                                                               |

| CI[150]  | I    | Clocked input port C, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                                                                                                                                                               |

| DI[150]  | I    | Clocked input port D, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                                                                                                                                                               |

| AO[150]  | 0    | Clocked output port A, data bits 0 through 15<br>Can be configured for many possible output formats.                                                                                                                                                                                                                                                             |

| BO[150]  | 0    | Clocked output port B, data bits 0 through 15<br>Can be configured for many possible output formats.                                                                                                                                                                                                                                                             |

| CO[150]  | I/O  | Dual function:<br>Clocked output – port C, data bits 0 through 15<br>Can be configured for many possible output formats.<br>Clocked input – Sum IO input data, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                      |

| DO[150]  | I/O  | Dual function:<br>Clocked output – port D, data bits 0 through 15<br>Can be configured for many possible output formats.<br>Clocked input – sum IO input data, data bits 0 through 15<br>Can be configured for many possible input formats.                                                                                                                      |

| [AD]CK   | 0    | Clocked output for ports [AD]<br>The clock for input ports in up-conversion mode and output ports in down-conversion mode. When configured as a<br>transceiver, channels A and B are in up-conversion and channels C and D are in down-conversion mode.                                                                                                          |

| [AD]FS   | 0    | Clocked output frame strobes for channels AD<br>Used to signify the beginning of a data frame for each input port in up-conversion mode and output in down-conversion<br>mode. The frame strobes are set high by the GC5016 with the first word in a frame. The frame strobes can be programmed<br>to be sent early.                                             |

| СК       | I    | Main input clock. The clock input to the chip.                                                                                                                                                                                                                                                                                                                   |

| SIGNAL               | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DATA I/O (CONTINUED) |      |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| IFLG                 | 0    | Clocked output A flag used to indicate which samples are real or imaginary in up-conversion mode when I and Q are time multiplexed.                                                                                                                                                                                                     |  |  |  |  |  |  |

| WRMODE               | I    | A static control input that changes the timing of control writes. Normally tied low. When low control write data must be stable for a setup time ahead and hold time after the end of the write strobe. When high data must be stable for a setup time ahead of the write strobe going active until a hold time after it goes inactive. |  |  |  |  |  |  |

| RST                  | I    | Chip reset bar. Active low signal. Not clocked. RST requires an external pull-up resistor or connection to VCOR Power Monitor "1" is OK.                                                                                                                                                                                                |  |  |  |  |  |  |

| SIA                  | I    | Sync input A bar. Active low data input signal. SIA requires an external pull-up resistor if not used.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| SIB                  | I    | Sync input B bar. Active low data input signal. SIB requires an external pull-up resistor if not used.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| SO                   | 0    | Sync output bar. Active low data output signal                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| JTAG I/O             |      |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TCK                  | I    | JTAG clock – Active high input. Internal pullup                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TDI                  | I    | JTAG data in – Active high input clocked on TCK rising. Internal pullup                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| TDO                  | 0    | JTAG data out – High-impedance state output clocked on falling edge of TCK.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| TMS                  | I    | JTAG interface – Active high input clocked on TCK rising. Internal pullup                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| TRST                 | I    | Asynchronous JTAG reset bar. Internal pullup                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| SUPPLIES             |      |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GND                  |      | Ground                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| VCOR(1)              |      | Core supply voltage. Used to supply the core logic, nominally set to 1.8 V.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| VPAD(1)              |      | Interface voltage. Used to set the I/O levels for all pins, nominally set at 3.3 V.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

(1) The VCore and VPad must both be powered before programming the GC5016 Control Bus. There is no required power sequence. The recommendation is to power VCore before or simultaneously with VPad.

# 13 GC5016 DOWN-CONVERSION MODE

### 13.1 Overview

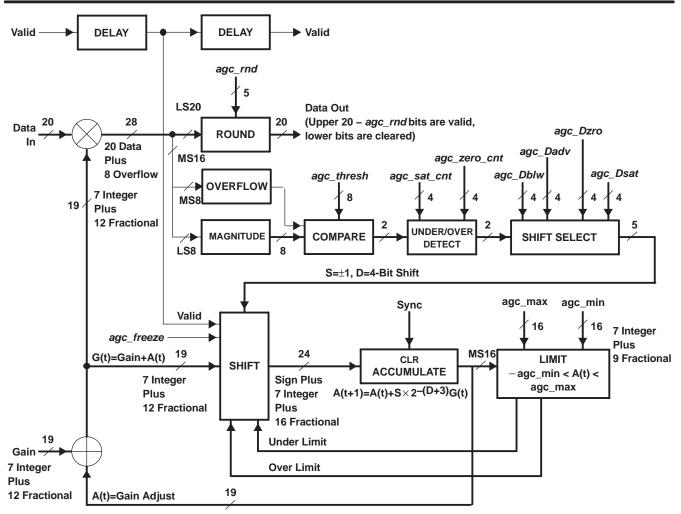

Figure 1 shows the functional block diagram for the GC5016 when configured as a 4-channel digital down-converter(DDC). In a common configuration, each down-conversion channel demodulates ADC sampled data down from an IF frequency to 0Hz, low pass filters the signal data, reduces the signal rate (decimation), and outputs I and Q baseband data. The baseband signal is measured by the Power Meter, and a gain or gain + automatic gain are applied to the IQ data. Several output formats are available for transmitting the IQ outputs.

The DDC input can be configured for real or complex inputs. The input data on ports AI[15..0], BI[15..0], CI[15..0], are converted to a complex input format in the Receive Input Formatter (RINF).

The Mixer stage provides the Receive Input channel selection (RSEL), digital oscillator (NCO), and complex mixing logic (mixer) to translate the input down to 0 Hz.

After the Mixer, the 5 stage Cascade Integrator Comb (CIC) provides complex filtering and decimation. The CIC decimation is an integer value from 1 to 256. Special logic is used for double rate processing.

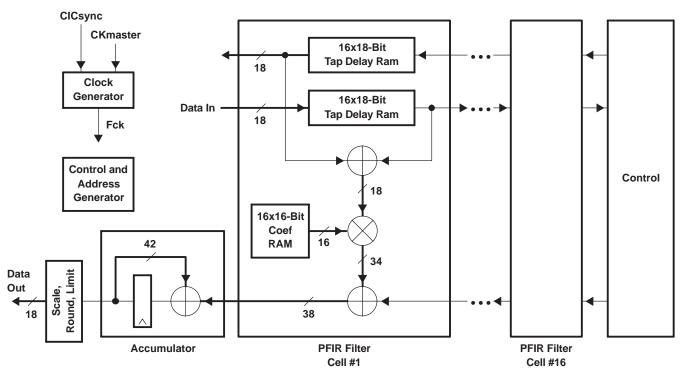

After the CIC complex filter, the Programmable Finite Impulse Response (PFIR) filter provides CIC correction, spectral shaping, and further decimation. The PFIR decimates from 1 to 16.

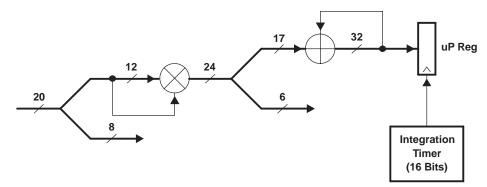

The PFIR complex output is measured by the Complex Power Meter. The Power Meter integrates the IQ power. The time integrated value can be read through the Microprocessor port.

The PFIR complex output is gain (manual + adaptive) scaled. An automatic gain (adaptive gain) is computed based on the current IQ output level. The gain scaled output is rounded to a desired number of bits resolution, and is formatted for the DDC output.

Channels can be synchronized to support beam forming or frequency hopped systems. Two channels can be operated in tandem to allow double input bandwidth, double output bandwidth, or both.

### 13.2 Receive Input Formatter (RINF)

The GC5016 has four 16-bit input ports AI[15..0], BI[15..0], CI[15..0], and DI[15..0]. The formatter converts the representation of real or complex data at the input pins to a complex format output.

#### 13.2.1 Receive Input Data Formats

Five data formats are supported (see Table 1):

- Full Rate, Real Input, one signal per input port

- Double Rate, Real Input, one signal per two input ports (even and odd)

- Half Rate, Complex Input, one signal per input port

- Full Rate, Complex Input, one signal per two input ports (I and Q)

- Double Rate, Complex Input, one signal per four input ports (leven, Qeven, lodd, Qodd)

NOTE: Full Rate means the sample input rate is equal to the GC5016 clock rate.

Each input port has a receive input data formatter. The data formatter accepts 2s complement format data 16 bits from its input port and outputs a 16-bit I bus and a 16-bit Q bus (the rinf bus). When there is no data to send, the output bus is held to zero.

#### For example:

If the input data is real, at full rate, the Q bus is zero.

If the input data is complex, at half rate, every second time sample is zero.

If the input data is complex at full rate, the I data is expected in port A (or C) and A's Q bus is zero. The imaginary data is expected in port B (or D) and B's I bus is zero.

The input format can be specified to the cmd5016 software by setting pseudo-commands rin\_rate and rin\_cmplx.

**NOTE:**Pseudo-commands are user specified variables that the software uses to set the hardware register values.

Table 1 shows the modes, the pseudo-commands, and register variables, programmed through the cmd5016 software.

For example, for the mode with four complex inputs, data from source 1 is entered time multiplexed I, followed by Q onto port AI. Configuration using the software requires that rin\_cmplx be set to 1 and rin\_rate be set to 0 (half rate). Alternatively, if the user wishes to program the hardware register fields directly, rinf\_sel\_A should be set to 3, mix\_rcv\_sel to 0 for channel A, and mix\_rcv\_cmplx to 0 for channel A (etc., for channels B, C, and D).

|                         | INPUT PORTS |          |         |          | SOFTWARE<br>CONTROLS | FIELDS FOR CHANNELS A, B, C, AND D<br>rinf_sel/ mix_rcv_sel/ mix_rcv_cmplx |       |       |       |  |  |

|-------------------------|-------------|----------|---------|----------|----------------------|----------------------------------------------------------------------------|-------|-------|-------|--|--|

| MODE                    | AI          | BI       | CI      | DI       | rin_cmplx/ rin_rate  | Α                                                                          | В     | С     | D     |  |  |

| Four real               | 11          | 21       | 31      | 41       | 0/1                  | 4/0/0                                                                      | 4/1/0 | 4/2/0 | 4/3/0 |  |  |

| Four complex            | 1I/1Q       | 21/2Q    | 3I/3Q   | 4I/4Q    | 1/0                  | 3/0/0                                                                      | 3/1/0 | 3/2/0 | 3/3/0 |  |  |

| Two complex             | 11          | 1Q       | 21      | 2Q       | 1/1                  | 4/0/1                                                                      | 1/x/x | 4/2/1 | 1/x/x |  |  |

| Two double rate real    | 1I(2k)      | 1I(2k+1) | 2I(2k)  | 2l(2k+1) | 0/2                  | 4/0/0                                                                      | 4/1/0 | 4/2/0 | 4/3/0 |  |  |

| One double rate complex | l(2k)       | Q(2k)    | l(2k+1) | Q(2k+1)  | 1/2                  | 4/0/1                                                                      | 1/x/1 | 4/2/x | 1/x/x |  |  |

**Table 1. Receive Input Modes and Controls**

### 13.2.2 Synchronization for IQ Multiplexed Mode

When I and Q are time multiplexed, a synchronization signal is used to determine which sample is I and which is Q. The input data is delayed by one cycle to form the I stream and is directly output for the Q stream. Thus far the data stream is (I0,Q0), (Q0, I1), (I1, Q1), — where I0 is the real portion of the sample at time 0. Then every other complex sample is zeroed using receive interpolation as discussed below, so that the stream is now (I0,Q0), (0,0), (I1,Q1), (0,0). — The timing for proper receive interpolation sync is shown in the next section.

### 13.2.3 Receive Interpolation

If the GC5016 CK rate divided by the input sample rate is an integer ratio, receive interpolation can be used (see Figure 4). In this case, the chip can be programmed to insert 0–15 zeros (rinf\_zpad) between input samples. This effectively interpolates the signal up by rinf\_zpad+1. The higher CK rate means the chip is operating faster, so the PFIR has more multiplication operations available per sample. It also allows greater flexibility in selecting the output sample rate since:

Fs\_out=Fck / (cic\_dec x fir\_dec), where Fck=Fadc x (1+rinf\_zpad).

One sample is registered while the data input on the other rinf\_zpad clocks are zeroed. The user has control over which sample is used through rinf\_zpad\_sync. The zpad selected sync encounters a two CK cycle delay, then loads a counter. When the counter reaches the terminal count, it is reloaded and a data sample is kept. All other data samples are zeroed. The sample occurring two plus (rinf\_zpad + 1) clock cycles after the sync is used, while the other samples are ignored. The sync input may be periodic in any multiple of (rinf\_zpad+1) or may occur just once.

If I and Q are time multiplexed, then the sync should be coincident with the Q sample.,

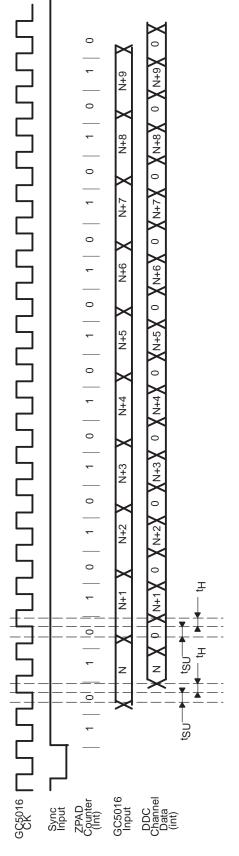

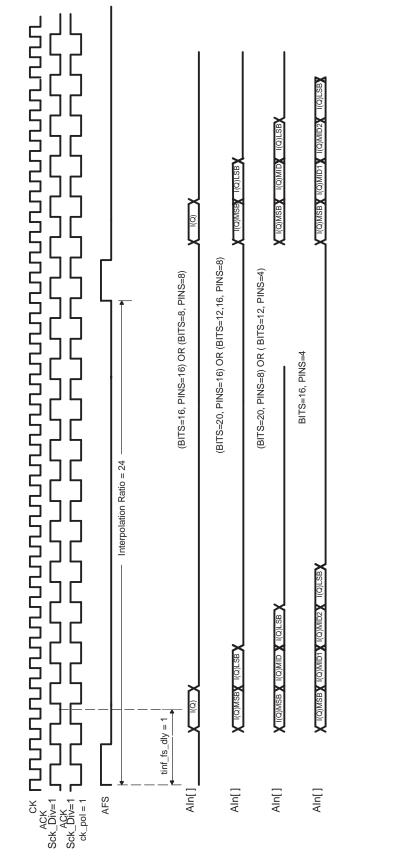

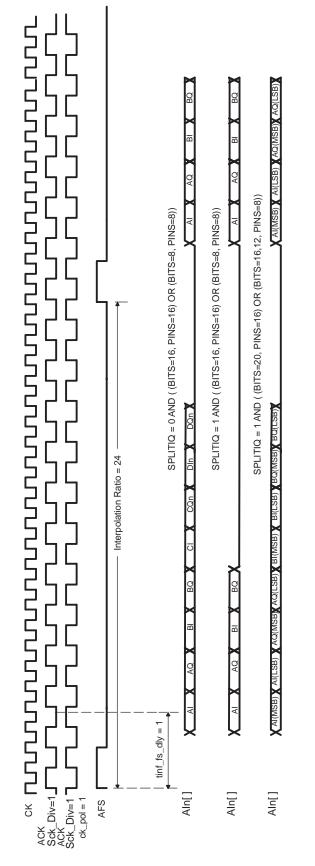

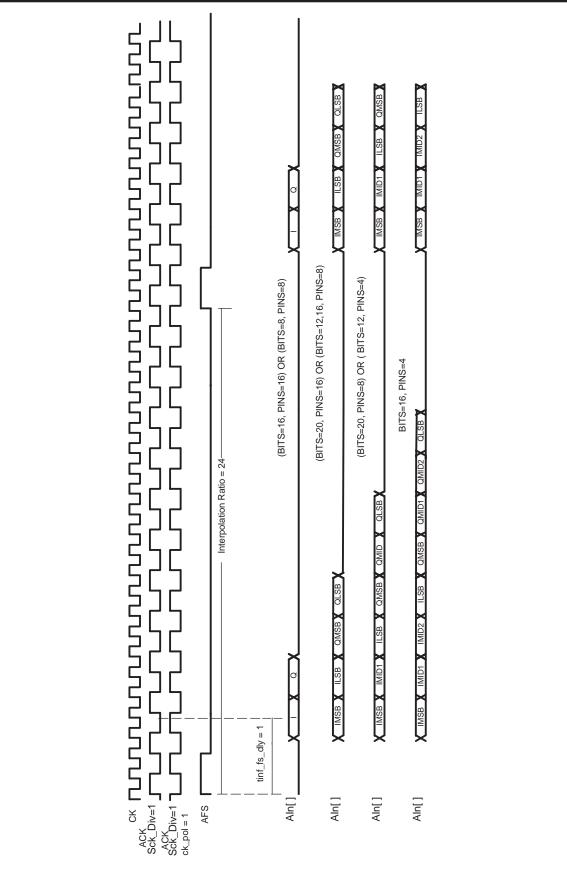

Figure 4. DDC Input Timing Diagram

### 13.2.4 Receiver Desensitizing

In a few circumstances, it is necessary to reduce the receiver sensitivity, which can be done by adding noise to the signal. The GC5016 allows this to be done digitally by adding pseudo random noise to selected bits in the input data stream. The noise power is added by bit wise xoring the input data stream with a Pseudo-random Noise (PN) sequence. The user has control over the noise power by programming which bits get the noise added. The noise power can go from –3 dBFS (0xfff) to –99 dbFS (0x1). This is programmed using rcv\_noise\_A (or B, C, or D). The noise uses the PN generator that is also used for diagnostics. The generator must be enabled for this feature to work by setting cksum \_sync.front to 0.

### **13.3 Receiver Diagnostic Selection**

The Receiver RINF can select the counter (ramp), zero, a constant, or the PN sequence as the DDC channel real input. The 0x4000 constant is used with the NCO setting to generate a known complex tone for output testing. The rinf\_sel and rinf\_diag controls are used to select a diagnostic input for a DDC channel. See the Diagnostics section.

### **13.4 Receive Input Selection**

In each channel an input selector exists at the input to the mixer. This selects I and Q data from one of four receive input formatters. The field mix\_rcv\_sel allows selection of the rinf bus. Full rate real or 1/2 rate complex inputs are selected with the mix\_rcv\_sel value as the input port. Special mix\_rcv\_sel values are needed for full rate complex, and double rate processing. See Table 1.

### 13.5 Mixer

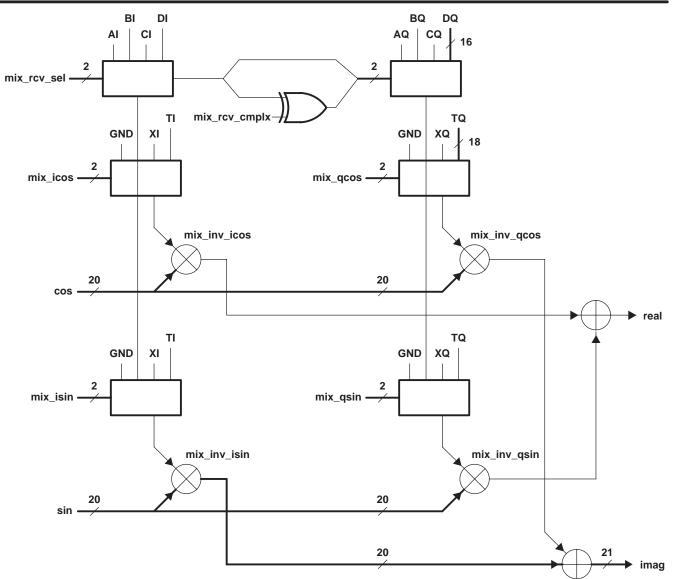

The DDC application of the mixer uses the selected RINF and RSEL with the NCO sine and cosine values. The Mixer equations are:

Imixout = lin × cos(Phase\_NCO) – Qin × sin(Phase\_NCO)

$Qmixout = Qin \times cos(Phase_NCO) + In \times sin(Phase_NCO)$

Each of the four multipliers (I x cos, I x sin, Q x cos, Q x sin) can be programmed in one of four modes (off, receive, cross transmit, normal transmit) (see Figure 5). A programmable inversion is provided for each I or Q data source. Programming Q x sin to be inverted corresponds to a mathematical view of down-conversion (mix with negative frequency tone to get a positive spectrum). Programming I x sin to be inverted corresponds to a radio view (tune to a frequency to get the signal at that frequency). The fields involved are mix\_icos, mix\_isin, mix\_qcos, mix\_qsin, and mix\_inv\_icos, mix\_isin, mix\_inv\_qcos, and mix\_inv\_qsin. The cmd5016 software automatically programs these fields assuming a mathematical view.

Selected RINF and RSEL data is accepted into the mixer as 16-bit data, placed into the upper bits of an 18-bit word, and inverted if programmed. The 18bit input is multiplied by a 20-bit NCO word, summed with the output of a second multiplier creating a 21-bit output. The Mixer output in the DDC application is sent to the CIC.

This means there is a 6dB attenuation going through the mixer. In other words, there is a 1-bit growth on top to allow for the extreme case of both real and imaginary inputs at full scale being multiplied by an NCO word that is at 45 degrees. For real inputs, the attenuation is 6 dB, so the CIC can safely be programmed to have 6-dB gain. For complex inputs, the attenuation is 3dB peak. The cmd5016 software includes this attenuation in its gain calculations when gain is set using the overall-gain keyword.

SLWS142G - JANUARY 2003 - REVISED NOVEMBER 2005

### 13.6 Numerically Controlled Oscillator (NCO)

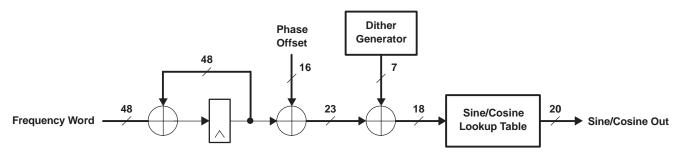

The tuning frequency of each up-converter is specified as a 48-bit word and the phase offset is specified as a 16-bit word. The 48-bit tuning word is calculated based on:

Freq words = FTune(negative for DDC) / CK  $\times 2^{48}$

The NCO phase is computed as the integrated frequency word phase + phase\_offset + dither. A block diagram of the NCO circuit is shown in Figure 6. The tuning frequency is set to FREQ according to the formula FREQ = (248) x F/fCK, where F is the desired tuning frequency and fCK is the chip's clock rate. The 16-bit phase offset setting is

phase =  $(2^{16}) \times Ph/2\pi$ , where Ph is the desired phase in radians ranging between 0 and  $2\pi$ .

A negative tuning frequency should be used for down-conversion. A positive tuning frequency can be used to flip the spectrum of the desired signal (if the input is real). FREQ and phase are set as shown in Table 53 through Table 56 or in software by specifying freq\_msb, freq\_mid, freq\_lsb, and phase. The configuration software calculates the appropriate settings for freq\_msb, freq\_mid, and freq\_lsb given the chip clock frequency (fCK) and freq. (If both freq and freq\_msb are set freq\_msb takes priority). The calculation includes the effects of zpad and double rate processing. Both fck and freq are expressed in Mhz.

Figure 6. Numerically Control Oscillator (NCO) Circuit

The NCOs can be synchronized with NCOs on other chips. This allows multiple down converter outputs to be coherently combined, each with a unique phase and amplitude. The NCO's frequency, phase and accumulator can be initialized and synchronized with other channels using the freq\_sync, phase\_sync, and nco\_sync controls. The freq\_sync and phase\_sync controls determine when new frequency and phase settings become active. Normally, these are set to Always so that they take effect immediately, but can be used to synchronize frequency hopping or beam forming systems. The nco\_sync control is usually set to Never, but can be used to synchronize the NCOs of multiple channels.

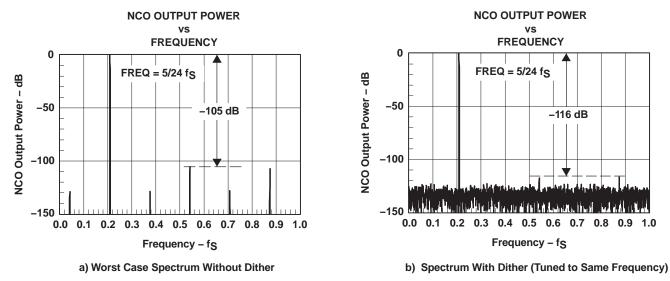

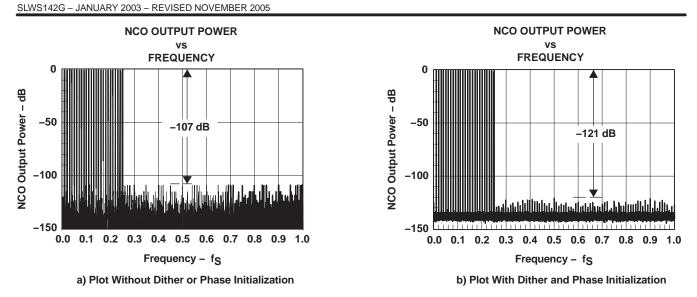

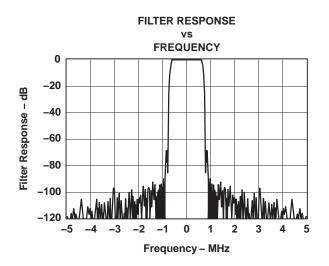

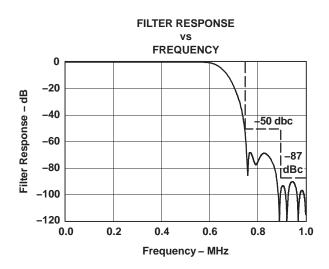

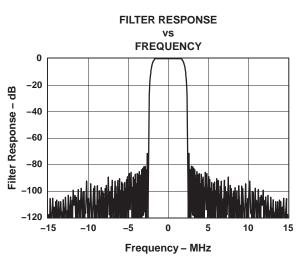

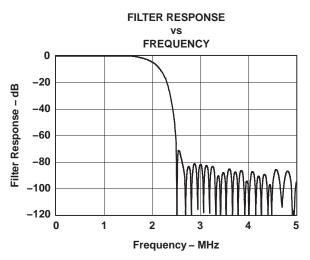

The NCO's spur level is reduced to below –113 dB through the use of phase dithering. The spectrums in Figure 7 show the NCO spurs for a worst case tuning frequency with and without dithering. Dithering decreases the spur level from –105 dB to –116 dB. Dithering is turned on or off using the dith\_sync controls. Holding dith\_sync always on freezes the dither value, effectively turning off dither.

Figure 7. Example NCO Spurs With and Without Dithering

Figure 8. NCO Peak Spur Plot

The worst-case NCO spurs at –113 dB to –116 dB, such as the one shown in Figure 7(b), are due to a few frequencies that are related to the sampling frequency by multiples of  $f_{CK}/96$  and  $f_{CK}/124$ . In these cases, the rounding errors in the sine/cosine lookup table repeat in a regular fashion, thereby concentrating the error power into a single frequency, rather than spreading it across the spectrum. These worst-case spurs can be eliminated by selecting an initial phase that minimizes the errors or by changing the tuning frequency by a small amount (50 Hz). Setting the initial phase register value to 4 for multiples of  $f_{CK}/96$  or  $f_{CK}/124$  (and to 0 for other frequencies) results in spurs below –115 for all frequencies.

Figure 8 shows the maximum spur levels as the tuning frequency is scanned over a portion of the frequency range with the peak hold function of the spectrum analyzer turned on. Notice that the peak spur level is -107 dB before dithering and is -121 dB after dithering has been turned on and the phase initialization described above has been used.

Double rate processing is done by sending time samples (2k) to mixer A and time samples (2k+1) to mixer B. The frequency is tuned to  $freq = (2^{48}) \times F/f_{CK}$ , where F is the desired tuning frequency and  $f_{CK}$  is the chip's clock rate as before. The 16-bit phase offset for mixer A is set to  $phase = (2^{16}) \times Ph/2\pi$ , where Ph is the desired phase in radians ranging between 0 and  $2\pi$ . The phase offset for mixer B is set to  $phase = (2^{16}) \times Ph/2\pi$ , where Ph is the desired phase in radians ranging between 0 and  $2\pi$ . The phase offset for mixer B is set to  $phase = (2^{16}) \times Ph/2\pi + (2^{15}) \times F/f_{CK}$ . Note that the second mixer phase offset is one frequency step at the sample rate of 2  $f_{CK}$  hence  $2^{15}$  rather than  $2^{16}$  scaling. The configuration software automatically calculates these.

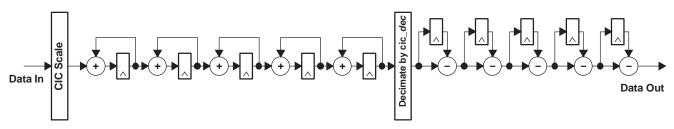

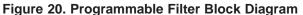

### 13.6.1 CIC Decimate Filter

The Cascade Integrator Comb (CIC) filter is a 5 stage decimating filter. The CIC filter is set to decimation mode using the register variable cic\_rcv. Each CIC channel contains two CIC filters (one for I and one for Q) allowing input rates of CK complex samples per second. The CIC filter has several sections: scaling, integration, rate change, comb filtering, and output scaling. The two CIC filter sections have special logic used in the double rate mode. The double rate mode is discussed in a later section.

The mixer IQ input is scaled to the 60 bit range using cic\_shift. The shifted mixer data is then input to the 5 integrator M=1 stages. The 5th integrator is decimated in the rate changer, by ncic samples. The cic scaling is based on shifting the input data to compensate for the 5 integrator stages' (cic\_dec ^ 5) gain.

$Ncic = cic_dec - 1$

The decimation logic samples the integrator output every cic\_dec clocks. The cic\_dec value can be set between 1 and 256. The value of cic\_dec can actually be programmed up to 4096 but the gain restrictions normally limit the usable range to 256 (up to 1024 in unusual circumstances).

<sup>[1]</sup>Hogenhauer, Eugene V., An Economical Class of Digital Filters for Decimation and Interpolation, IEEE transactions on Acoustics, Speech and Signal Processing, April 1981.

TEXAS INSTRUMENTS www.ti.com

SLWS142G - JANUARY 2003 - REVISED NOVEMBER 2005

The decimated output is scaled to 24bits and input to the 5 stage comb section M=1. After the 5 comb sections, the 24bit output is scaled to 18 bits. The 18 bit output is saturated to 17 or 18 bits. The 17bit output is used when the PFIR uses symmetry. A block diagram of the decimating CIC filter is shown in Figure 9.

The CIC filter has a gain equal to cic\_dec5 that must be compensated for by the CIC scale circuit. and the scale circuit must limit the peak signal gain from the rinf\_zpad, mixer, and through the CIC to be 1 or less. The peak gain is:

peak gain =  $(1/(1+rinf_zpad)) \times (mixer_gain) \times (cic_dec^5 \times 2^{(cic_shift-39)})$

The cmd5016 program will set the gain properly if the overall-gain keyword is used.

The register field cic\_sync controls the precise moment of decimation. The sync can be periodic at any multiple of cic\_dec without disturbing the processing. If sync is held active, the CIC freezes its output.

The output of the CIC can be attenuated in gain by 6 dB by clearing cic\_rshift. This is appropriate only when cic\_shift has been set to zero, the signal gain to this point is greater than 0.5, and symmetry is being used in the PFIR filter. In other words, cic\_rshift should almost always be set to one. The rshift\_gain is 2<sup>cic\_rshift-1</sup>.

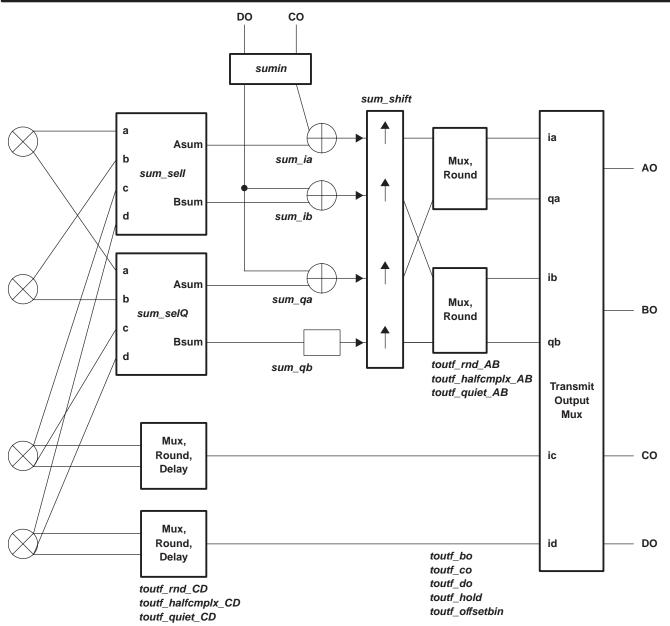

The CIC output data feeding the PFIR must be limited to half scale if the PFIR is using symmetry. Control bit field cic\_rcv\_full must be cleared in this case. If the PFIR is not using symmetry, the data is limited to full scale and the bit field cic\_rcv\_full should be set to one. The CIC gain is adjusted by the cmd5016 configuration software.