[查询GDC21D701C供应商](#)

[捷多邦，专业PCB打样工厂，24小时加急出货](#)

# **GDC21D701C**

## **(Video Display Processor)**

**Version 1.0**

LDS - GDC21D701C - 9903 / 10

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by LG for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of LG or others.

These LG products are intended for usage in general electronic equipment (office equipment, communication equipment, measuring equipment, domestic electrification, etc.). Please make sure that you consult with us before you use these LG products in equipment which require high quality and/or reliability, and in equipment which could have major impact to the welfare of human life (atomic energy control, airplane, spaceship, traffic signal, combustion control, all types of safety devices, etc.). LG cannot accept liability to any damage which may occur in case these LG products were used in the mentioned equipment without prior consultation with LG.

Purchase of LG I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Copyright 1998 LG Semicon Co., Ltd.

All Rights Reserved

---

## TABLE OF CONTENTS

---

|                                                       |    |

|-------------------------------------------------------|----|

| 1. General Description .....                          | 6  |

| 2. Features .....                                     | 6  |

| 3. Pin Description .....                              | 8  |

| 4. Block Diagram .....                                | 13 |

| 5. Functional Description .....                       | 15 |

| 5.1 Format Conversion .....                           | 15 |

| 5.2 I <sup>2</sup> C bus interface .....              | 21 |

| 5.3 Host Interface .....                              | 22 |

| 5.3.1. <i>Host Interface Signal Description</i> ..... | 22 |

| 5.3.2 DMA Operation .....                             | 25 |

| 5.4 On-screen Display .....                           | 27 |

| 5.5 Color Space Conversion .....                      | 34 |

| 5.6 Lookup Table Control .....                        | 35 |

| 5.7 D/A Conversion .....                              | 35 |

| 5.8 Display Sync Timing .....                         | 37 |

| 5.9 SDRAM/Clock Interface .....                       | 38 |

| 5.10 NTSC/VGA Interface .....                         | 39 |

| 5.11 Video Decoder Interface .....                    | 43 |

| 6. Register Descriptions .....                        | 44 |

| 6.1 Coefficients of Color Space Converter .....       | 46 |

| 6.2 Coefficients of FIR filter .....                  | 47 |

| 6.3 coef_load(default: xxxx xx00) x: unused bit ..... | 47 |

| 6.4 csc_offset(default : xxxx x011) .....             | 48 |

| 6.5 display_mode(0000 0000) .....                     | 48 |

| 6.6 multi_chnl_pos(0xx0 0000) .....                   | 49 |

| 6.7 multi_brdr_clr(0010 1101) - blue .....            | 50 |

| 6.8 pip_mode(0000 0110) .....                         | 50 |

| 6.9 pip_brdr_clr(0100 0111) – red .....               | 51 |

| 6.10 pip_win_clr(0111 0100) - green .....             | 51 |

| 6.11 pip_pos_x(001 1110 0000) .....                   | 51 |

| 6.12 pip_pos_y(00 1000 1000) .....                    | 52 |

| 6.13 zoom_pos(xxxx 0000) .....                        | 52 |

| 6.14 osd_mode(0000 0xxx) .....                        | 52 |

| 6.15 sd_pos_x(0010 1000) .....                        | 53 |

---

---

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 6.16 sd_pos_y(xx01 1110) .....                                            | 53 |

| 6.17 nvin_h(x000 0000).....                                               | 53 |

| 6.18 nvin_v(xx00 0000) .....                                              | 53 |

| 6.19 nvinputformat(xxx0 0--0) : - Means read only bit.....                | 54 |

| 6.20 atvformat(x--- ----) : This register operates in read only mode..... | 54 |

| 6.21 arc_mode(x100 0000) .....                                            | 55 |

| 6.22 deint_th(0001 1000) .....                                            | 55 |

| 6.23 test_ptrn(xxxx x000) .....                                           | 56 |

| 6.24 osd_base(x000 0000).....                                             | 57 |

| 6.25 dma_block_size(x000 0000).....                                       | 57 |

| 6.26 dma_mode(xxxx 0000) .....                                            | 57 |

| 6.27 host_wait(1111 1111) .....                                           | 57 |

| 6.28 nonactive_val(0001 0000) .....                                       | 57 |

| 6.29 lut_sel(xxxx xx00).....                                              | 58 |

| 6.30 lutwrgb(xxxx x111).....                                              | 58 |

| 6.31 palette_sel(xxxx xx00) .....                                         | 59 |

| 6.32 disp_sel(xxx1 0100).....                                             | 59 |

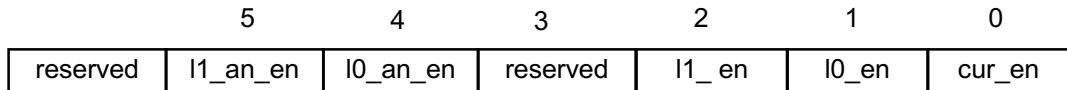

| 6.33 osd_en(xx00 x000).....                                               | 60 |

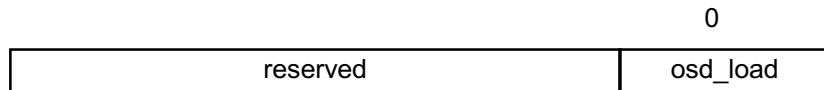

| 6.34 osd_load(xxxx xxx0) .....                                            | 60 |

| <br>                                                                      |    |

| 7. Electrical Characteristics .....                                       | 61 |

| 7.1 Absolute Maximum Rating.....                                          | 61 |

| 7.2 Recommended Operating Range .....                                     | 61 |

| 7.3 DC Characteristics (VDD = 3.3 V $\pm$ 10%, TA = 0 ~ 70°C) .....       | 61 |

| 7.4 AC Characteristics (VDD = 3.3 V $\pm$ 10%, TA = 0 ~ 70°C) .....       | 61 |

| <br>                                                                      |    |

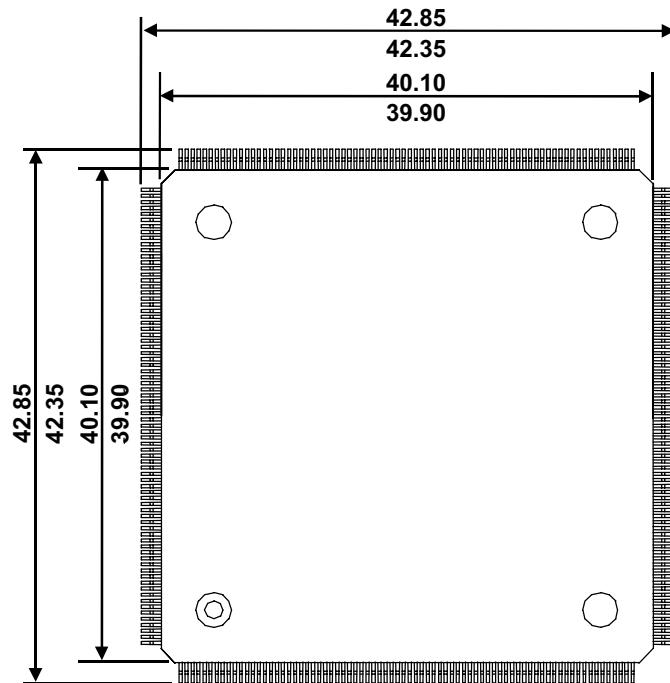

| 8. Package Mechanical Data .....                                          | 63 |

| 8.1 Package Pin Out .....                                                 | 63 |

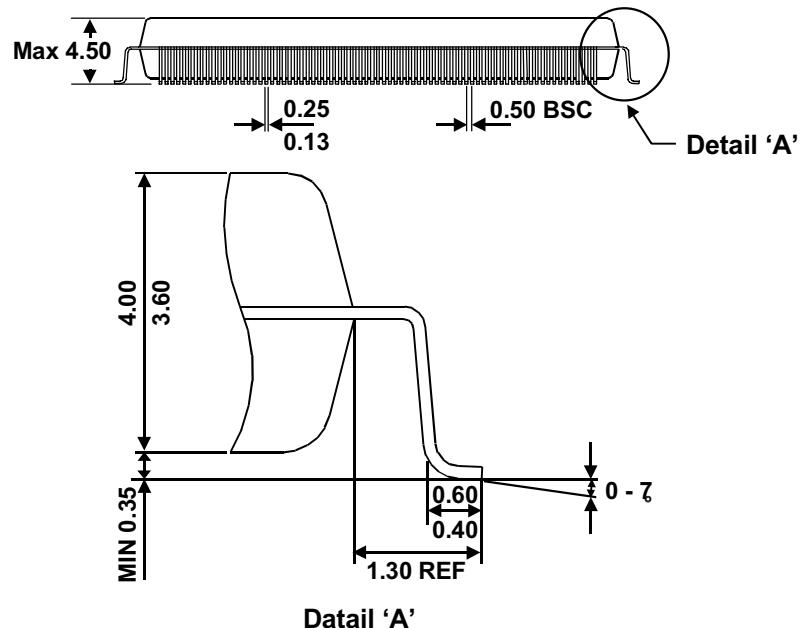

| 8.2 Package Dimensions .....                                              | 67 |

---

## GDC21D701C

Video Display Processor

### 1. General Description

The Video Display Processor(GDC21D701C) converts digital image data into analog image data for HDTV display. The VDP receives all Grand Alliance input image formats(including HD and SD) and converts them into 1080x1920 60I HD display formats. The VDP also converts digital NTSC image format(480x768 60I, 480x768 60P) or VGA input format(480x640 60P or 768x1024 60P) into HD display format. During the display format conversion, the VDP converts 4:2:0 or 4:2:2 chrominance format into 4:4:4 chrominance one. The VDP supports bit-mapped-type On-screen Display(OSD) function, and OSD data can be loaded by DMA operation.

In the GBR display mode, the VDP converts YCbCr color space into GBR color space using the digital dematrix function. The VDP has two sets of user programmable Lookup Tables for customer control and special video effects. Finally, the VDP converts digital GBR/YCbCr signal into analog GBR/YPbPr signal and generates associated video sync signals for high-definition display.

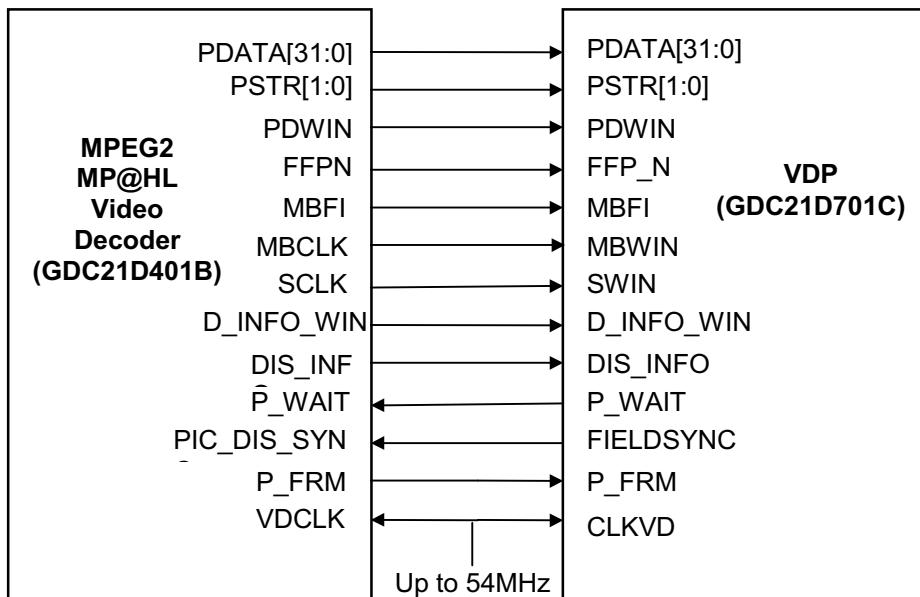

The VDP can directly interface with MPEG2 MP@HL Video Decoder(GDC21D401B).

### 2. Features

#### Format Conversion

- Supports all HD, SD(4:2:0), and digital NTSC(4:2:2) and VGA(4:2:2) input format

- 720x1280(60P,30P,24P)

- 1080x1920(60I,30P,24P)

- 480x704(60P,30P,24P,60I)

- 480x720(60P,30P,24P,60I)

- 480x640(60P,30P,24P,60I)

- 480x768(60I, 60P) : digital NTSC and double scanned NTSC

- 480x720(60I) : NTSC

- 480x640(60P) : VGA

- 768x1024(60P) : VGA

- 1080x1920(60I) Interlaced display format

- 3-D de-interlacing

- Motion compensated de-interlacing

- Use 3 field memories

- Applied to NTSC 60I / SD 60I input

- Chrominance format conversion

- 4:2:0 => 4:4:4(ATV)

- 4:2:2 => 4:4:4(digital NTSC or VGA)

- 9-tap FIR filter for horizontal filtering (Luminance part only)

- 2-tap Linear Interpolation filter for vertical filtering

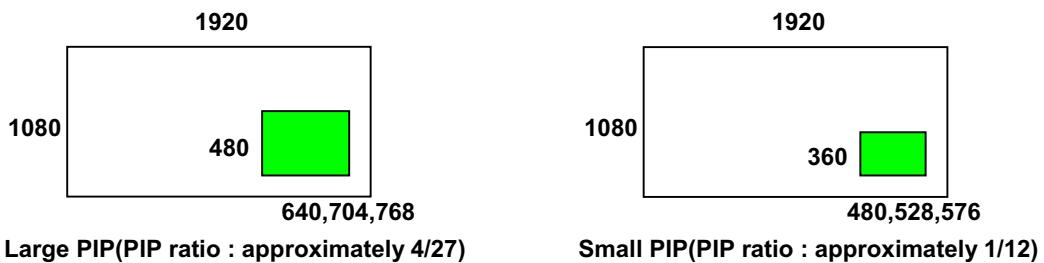

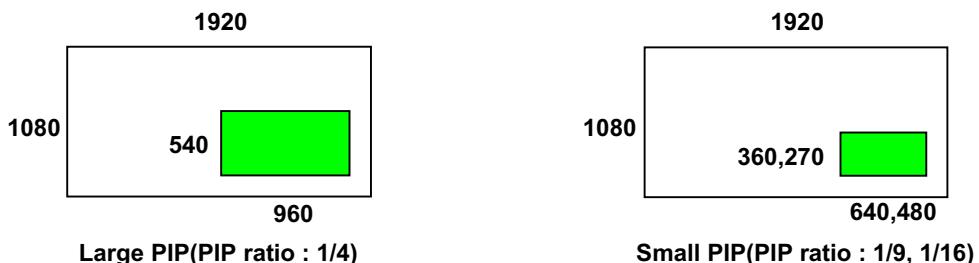

#### PIP & Display Control

- Supports ATV main display and NTSC PIP and vice versa

- Supports two selectable PIP sizes

- Supports programmable PIP positions

- Supports 4:3 display and 16:9 display for 4:3 input format(SD and NTSC case)

- x4 zoom at 9 selectable positions for HD input formats

- Multi-PIP display(16 Multi-PIPs)

- Freeze function

**On-screen Display**

- Display Format : 1080 x 1920(4:4:4, 60I, 74.25MHz)

- Supports transparency and 16-level blending

- Multiple layers : cursor, two OSD layers above video

- 2, 4, 8 bitmap bits per cell

- Top and bottom fields share the same OSD data

- Linked-list memory management

- Supports full OSD screen

- Supports maximum four OSD buffers

- 32 x 32-pixel 4-color cursor movable all over the screen

- Animation function

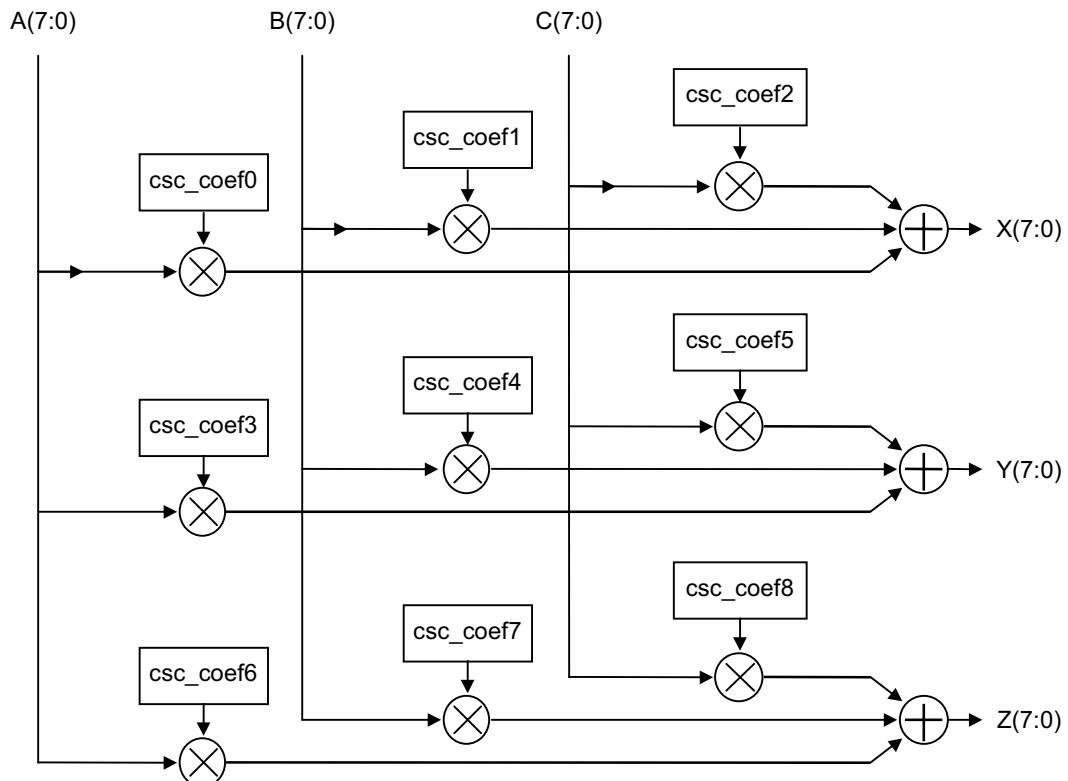

**Color Space Conversion**

- Supports programmable color space conversion function (including YCbCr => GBR, YCbCr => YPbPr )

- Three channels, 8-bit color space conversion

- Uses 9 parallel multipliers to process high resolution image

- Uses 9 10-bit matrix coefficients(integer range: 1023/2 ~ -1024/2)

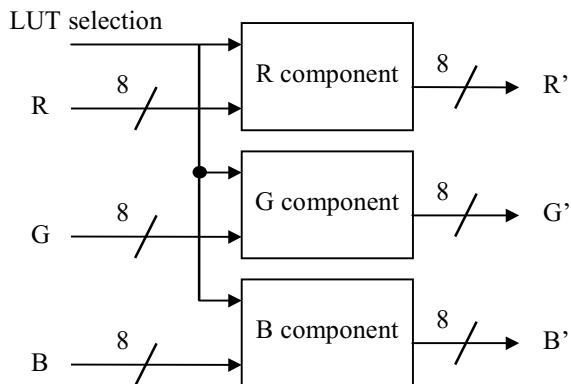

**Customer Controls**

- Two swappable sets of RGB tables

- 8-bit 256-level Lookup Table (RAM)

**Output Formats**

- GBR / YCbCr 10-bit digital output

- GBR / YPbPr analog output (10-bit D/A conversion)

- Provides external sync signals - HDOOUT\_N, VDOUT\_N

- Supports SMPTE 274M digital/analog output formats

- Provides 7 built-in test patterns

**Host Interface (Use digital output ports)**

- Supports 16-bit host bus interface

- Supports DMA operation(up to 36Mbyte/sec) for OSD data loading.

- Supports I<sup>2</sup>C Interface

### 3. Pin Description

**Figure 1. Pin Configuration**

**(Package: 304 PQ2)**

| NAME                                | PIN                                                                                                                                                                                                                                   | TYPE | DESCRIPTIONS                                                                                                                                                                                               |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Clocks</b>                       |                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                            |

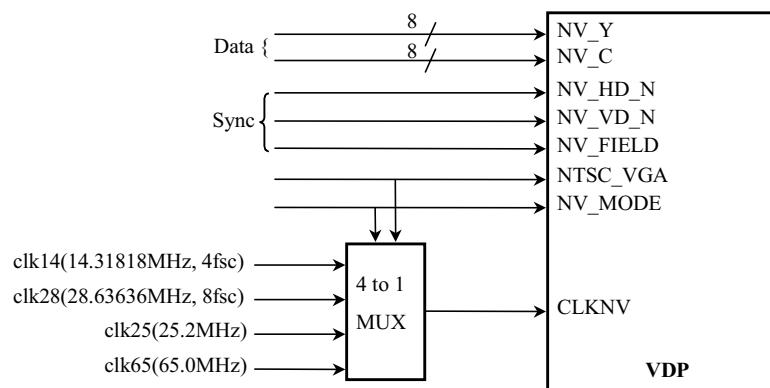

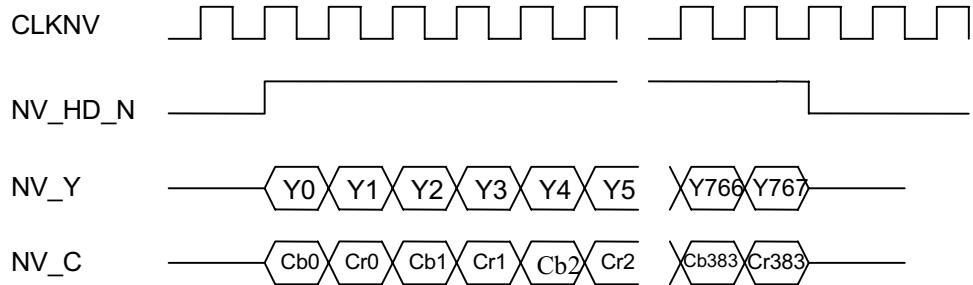

| <b>CLKNV</b>                        | 2                                                                                                                                                                                                                                     | I    | NTSC/VGA Interface Clock. Its operating clock frequency depends on the NV_MODE input and it can be 14MHz, 25MHz, 28MHz, or 65MHz.                                                                          |

| <b>CLKVD</b>                        | 221                                                                                                                                                                                                                                   | I    | Video Decoder Interface Clock. Its operating clock frequency is the same as that of Video Decoder and it can be up to 54MHz.                                                                               |

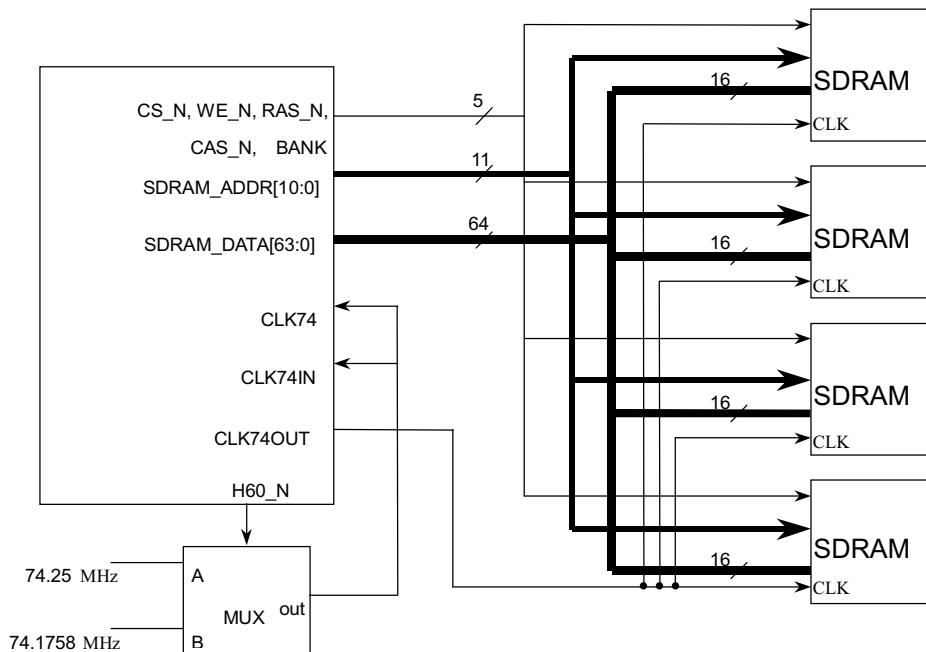

| <b>CLK74</b>                        | 224                                                                                                                                                                                                                                   | I    | VDP Display Clock. Its operating clock frequency can be 74.25MHz or 74.175MHz.                                                                                                                             |

| <b>CLK74IN</b>                      | 161                                                                                                                                                                                                                                   | I    | Additional Clock for SDRAM Interface. This clock outputs clk74out signal for SDRAM interface. Its operating clock frequency is the same as that of VDP display clock.                                      |

| <b>CLK74OUT</b>                     | 159                                                                                                                                                                                                                                   | O    | Additional Clock for SDRAM Interface. For stable data transfer between SDRAM and VDP, VDP provides the additional clock for SDRAM interface. Its operating clock frequency is the same as that of clk74in. |

| <b>Resets</b>                       |                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                            |

| <b>RESET_N</b>                      | 235                                                                                                                                                                                                                                   | I    | Global Reset(active-low). This signal asynchronously resets the VDP IC.                                                                                                                                    |

| <b>RESETS_N</b>                     | 236                                                                                                                                                                                                                                   | I    | Display Sync Reset. This signal asynchronously resets the display sync signal.                                                                                                                             |

| <b>I<sup>2</sup>C-Bus Interface</b> |                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                            |

| <b>SCL</b>                          | 104                                                                                                                                                                                                                                   | I    | I <sup>2</sup> C-Bus Serial Clock. The maximum operation clock is 400KHz.                                                                                                                                  |

| <b>SDA</b>                          | 102                                                                                                                                                                                                                                   | I/O  | I <sup>2</sup> C-Bus Serial Data. Bi-directional data.                                                                                                                                                     |

| <b>SDRAM Interface</b>              |                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                            |

| <b>SDRAM_DATA [63:0]</b>            | 46,45,43,42,41,39,38, 36,35,34,33,31,30,28, 27,26,25,23,22,21,20, 18,17,15,14,13,12,10, 9,7,6,4,282,281,280, 278,277,275,274,273, 270,269,268,265,264, 263,261,260,259,257, 256,254,253,252,251, 249,248,246,245,244, 243,241,240,238 | I/O  | SDRAM Data Bus. Bi-directional data.                                                                                                                                                                       |

| <b>SDRAM_ADDR [10:0]</b>            | 297,296,294,293,292, 291,289,288,287,286, 284                                                                                                                                                                                         | O    | SDRAM Address.                                                                                                                                                                                             |

| <b>BANK</b>                         | 298                                                                                                                                                                                                                                   | O    | SDRAM Bank Selection Signal.                                                                                                                                                                               |

| <b>WE_N</b>                         | 300                                                                                                                                                                                                                                   | O    | SDRAM Write Enable Signal(active-low).                                                                                                                                                                     |

| <b>CAS_N</b>                        | 301                                                                                                                                                                                                                                   | O    | SDRAM Column Address Strobe Signal(active-low).                                                                                                                                                            |

| <b>RAS_N</b>                        | 302                                                                                                                                                                                                                                   | O    | SDRAM Row Address Strobe Signal(active-low).                                                                                                                                                               |

| <b>CS_N</b>                         | 303                                                                                                                                                                                                                                   | O    | SDRAM Chip Selection Signal(active-low).                                                                                                                                                                   |

**Pin Description(continued)**

| NAME                           | PIN                                                                                                                                   | TYPE | DESCRIPTION                                                                                                                                          |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Video Decoder Interface</b> |                                                                                                                                       |      |                                                                                                                                                      |

| <b>PDATA[31:0]</b>             | 172,173,175,176,178, 179,181,182,183,185, 186,187,188,190,191, 192,194,195,197,198, 200,201,203,204,206, 207,209,210,212,213, 215,216 | I    | Video Decoder Output Data. These ports can be directly connected to the Video Decoder PDATA output.                                                  |

| <b>PSTR[1:0]</b>               | 218,219                                                                                                                               | I    | Picture Structure Information. These ports can be directly connected to the Video Decoder PSTR output.                                               |

| <b>PDWIN</b>                   | 226                                                                                                                                   | I    | Picture Data Window. This port can be directly connected to the Video Decoder PDWIN output.                                                          |

| <b>FFP_N</b>                   | 230                                                                                                                                   | I    | First Field Parity(active-low). This port can be directly connected to the Video Decoder FFPN output.                                                |

| <b>MBFI</b>                    | 231                                                                                                                                   | I    | Macro Block IDCT Type. ‘0’ means frame IDCT and ‘1’ means field IDCT. This port can be directly connected to the Video Decoder MBFI output.          |

| <b>MBWIN</b>                   | 233                                                                                                                                   | I    | Macro Block Data Window. This port can be directly connected to the Video Decoder MBCLK output.                                                      |

| <b>SWIN</b>                    | 234                                                                                                                                   | I    | Slice Data Window. This port can be directly connected to the Video Decoder SCLK output.                                                             |

| <b>D_INFO_WIN</b>              | 227                                                                                                                                   | I    | Picture Format Data Window. This port can be directly connected to the Video Decoder D_INFO_WIN output.                                              |

| <b>DIS_INFO</b>                | 228                                                                                                                                   | I    | Picture Format Data. The picture information is coded in serial format and this port can be directly connected to the Video Decoder DIS_INFO output. |

| <b>P_FRM</b>                   | 167                                                                                                                                   | I    | Progressive Frame Information. This port can be directly connected to the Video Decoder P_FRM output. If not, this port should be connected to VSS.  |

| <b>P_WAIT</b>                  | 170                                                                                                                                   | O    | PDATA Wait Signal. This port can be directly connected to the Video Decoder P_WAIT input.                                                            |

| <b>NTSC/VGA Interface</b>      |                                                                                                                                       |      |                                                                                                                                                      |

| <b>NV_Y[7:0]</b>               | 58,57,55,54,52,51,49, 48                                                                                                              | I    | Luminance Data Input of NTSC or VGA.(4:2:2 format)                                                                                                   |

| <b>NV_C[7:0]</b>               | 70,69,67,66,64,63,61, 60                                                                                                              | I    | Chrominance Data Input of NTSC or VGA.(4:2:2 format)                                                                                                 |

| <b>NTSC_VGA</b>                | 72                                                                                                                                    | I    | Select NTSC or VGA Input. NTSC input set to “0” and VGA input set to “1”.                                                                            |

| <b>NV_MODE</b>                 | 73                                                                                                                                    | I    | Select NTSC and VGA Input Mode. NTSC input or VGA input set to “0” and double scan NTSC or SVGA input set to “1”.                                    |

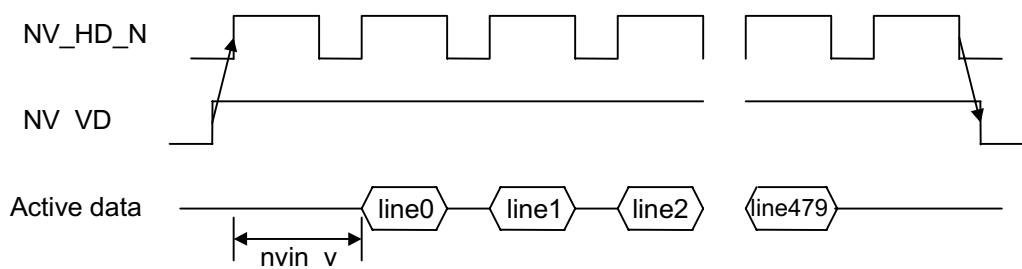

| <b>NV_HD_N</b>                 | 74                                                                                                                                    | I    | Horizontal Drive or Horizontal Sync Input.                                                                                                           |

| <b>NV_VD_N</b>                 | 75                                                                                                                                    | I    | Vertical Drive or Vertical Sync Input.                                                                                                               |

| <b>NV_FIELD</b>                | 91                                                                                                                                    | I    | NTSC Field Signal. It is set to ‘0’ that present input is top field and set to “1” that is bottom field. This is used in the NTSC input mode.        |

**Pin Description(*continued*)**

| NAME                                                   | PIN                                       | TYPE | DESCRIPTION                                                                                                                                                                                        |

|--------------------------------------------------------|-------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Display</b>                                         |                                           |      |                                                                                                                                                                                                    |

| <b>ROUT/PROUT</b>                                      | 82                                        | O    | Analog Output - Red /Pr Signal.                                                                                                                                                                    |

| <b>GOUT/YOUT</b>                                       | 84                                        | O    | Analog Output - Green /Y Signal.                                                                                                                                                                   |

| <b>BOUT/PBOUT</b>                                      | 86                                        | O    | Analog Output - Blue /Pb Signal.                                                                                                                                                                   |

| <b>ADJ</b>                                             | 80                                        | I    | Full-scale Adjustment.<br>It controls the magnitude of analog video signal.                                                                                                                        |

| <b>REF</b>                                             | 78                                        | I    | Voltage Reference Input.                                                                                                                                                                           |

| <b>HDOUT_N</b>                                         | 92                                        | O    | Horizontal Drive Output.                                                                                                                                                                           |

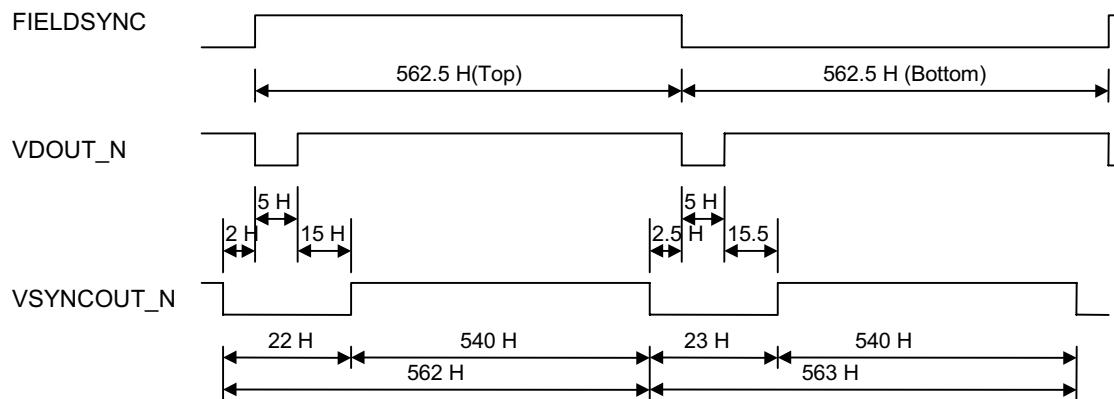

| <b>VDOUT_N</b>                                         | 93                                        | O    | Vertical Drive Output.                                                                                                                                                                             |

| <b>HSYNCOUT_N</b>                                      | 97                                        | O    | Horizontal Sync Output. This signal represents active data window.                                                                                                                                 |

| <b>VSYNCOUT_N</b>                                      | 98                                        | O    | Vertical Sync Output.<br>This signal represents active data window.                                                                                                                                |

| <b>FIELDSYNC</b>                                       | 99                                        | O    | Field SYNC Output. It is set to '1' that present display is top field and set to '0' that is bottom field. This port can be directly connected to the Video Decoder PIC_DIS_SYNC input.            |

| <b>H60_N</b>                                           | 100                                       | O    | Clock Selection Signal. It is set to '0' that VDP requires 74.25MHz clock and set to '1' that VDP requires 74.175MHz clock.                                                                        |

| <b>RDOUT[9:0] / CRDOUT[9:0]</b>                        | 106,107,109,110,111, 113,114,116,89,95    | I/O  | 10-bit Digital Output-Red/Cr Component. 74MHz data rate. These pins can be used by host interface signals                                                                                          |

| <b>GDOOUT[9:0] / YDOUT[9:0]</b>                        | 117,119,120,122,123, 125,126,128,142, 150 | I/O  | 10-bit Digital Output-Green/Y Component. 74MHz data rate. These pins can be used by host interface signals                                                                                         |

| <b>BDOOUT[9:0] / CBDOUT[9:0]</b>                       | 129,131,133,134,135, 137,138,140,151,153  | I/O  | 10-bit Digital Output-Blue/Cb Component. 74MHz data rate. These pins can be used by host interface signals                                                                                         |

| <b>Host Bus Interface (Shared RGB Digital Outputs)</b> |                                           |      |                                                                                                                                                                                                    |

| <b>HOST_SEL</b>                                        | 76                                        | I    | Host Select Signal. It is set to "1" that digital output signals are activated for digital interface and set to "0" that host interface address and data signals are used in digital output ports. |

| <b>D_STB_N</b>                                         | 151                                       | I    | Data Strobe (active-low) : Asynchronous.<br>Used by the host processor to access this chip. When D_STB_N signal is active, H_ADDR[8:1], H_DATA[15:0], and H_CS_N should be valid.                  |

| <b>H_RW_N</b>                                          | 150                                       | I    | Read/Write (active-low) : Asynchronous.<br>The state of the signal defines the data transfer type.<br>0 = Write to the device 1= Read from the device                                              |

| <b>H_CS_N</b>                                          | 142                                       | I    | Chip Selection (active-low).<br>This signal is used to activate and access to the internal registers and memories of the GDC21D701C.                                                               |

| <b>READY_TYPE</b>                                      | 153                                       | I    | It is set to "1" that ready signal is active-high and set to "0" that ready signal is active-low                                                                                                   |

| <b>H_ADDR[8:1]</b>                                     | 129,131,133,134,135, 137,138,140          | I    | Host Address Bus. These signals are connected to the address bus of the host processor interfaced with the GDC21D701C.                                                                             |

**Pin Description(*continued*)**

| NAME                                                   | PIN                                                                                                                                                                                       | TYPE  | DESCRIPTION                                                                                              |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------|

| <b>Host Bus Interface (Shared RGD Digital Outputs)</b> |                                                                                                                                                                                           |       |                                                                                                          |

| <b>H_DATA[15:0]</b>                                    | 106,107,109,110,111,<br>113,114,116,117,119,<br>120,122,123,125,126,<br>128                                                                                                               | I/O/Z | Data Bus. These signals are connected to the address bus of the external host processor.                 |

| <b>READY</b>                                           | 88                                                                                                                                                                                        | O/Z   | Data Acknowledge                                                                                         |

| <b>DMA_REQ_N</b>                                       | 89                                                                                                                                                                                        | O     | DMA Request Signal (active-low)                                                                          |

| <b>DMA_ACK_N</b>                                       | 95                                                                                                                                                                                        | I     | DMA Acknowledge Signal (active-low)                                                                      |

| <b>Power / Ground</b>                                  |                                                                                                                                                                                           |       |                                                                                                          |

| <b>VDD</b>                                             | 3,8,16,24,32,40,50,<br>56,62,68,94,101,105,<br>112,118,127,132,136,<br>141,154,171,177,184,<br>193,199,205,211,217,<br>222,223,229,237,242,<br>250,258,266,267,276,<br>285,295, 299       | PWR   | Digital Power - 3.3V                                                                                     |

| <b>Power / Ground</b>                                  |                                                                                                                                                                                           |       |                                                                                                          |

| <b>VSS</b>                                             | 1,5,11,19,29,37,44,<br>47,53,59,65,71,90,96,<br>103,108,115,121,124,<br>130,139,143,152,174,<br>180,189,196,202,208,<br>214,220,225,232,239,<br>247,255,262,271,272,<br>279,283, 290, 304 | GND   | Digital Ground                                                                                           |

| <b>VDDA</b>                                            | 79, 83, 87                                                                                                                                                                                | PWR   | Analog Power - 3.3V                                                                                      |

| <b>VSSA</b>                                            | 77, 81, 85                                                                                                                                                                                | GND   | Analog Ground                                                                                            |

| <b>Scan Test</b>                                       |                                                                                                                                                                                           |       |                                                                                                          |

| <b>SCAN_IN[6:1]<br/>Test Mode Input</b>                | 162, 160, 158, 157,<br>156,155, 163, 164,<br>165, 166                                                                                                                                     | I     | Test Input. These pins are only used for test mode. For normal function, these pins are connected to GND |

| <b>SCAN_OUT[6:1]<br/>Test Mode Output</b>              | 149, 148, 147, 146,<br>145,144, 168, 169                                                                                                                                                  | O     | Test Output. These pins are only used for test mode. For normal function, these pins are not connected.  |

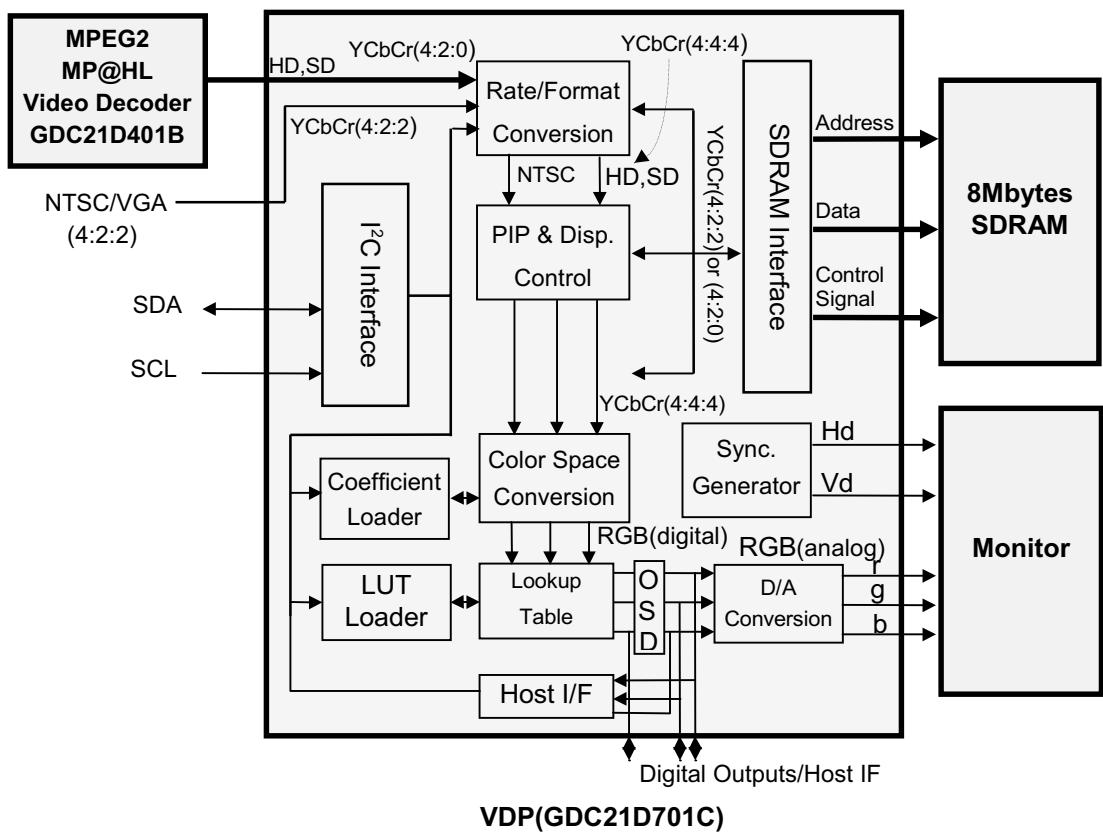

#### 4. Block Diagram

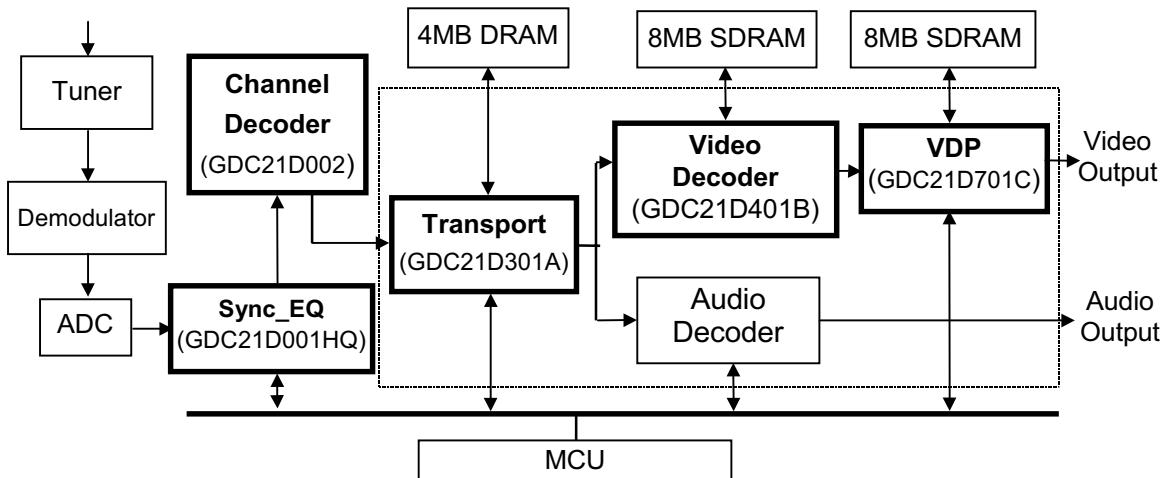

The Video Display Processor offers a solution for the design of display systems for Grand Alliance DTV applications. Figure 2. shows the internal block diagram of the VDP. It consists of Format Conversion, PIP function, On-Screen Display, Color Space Conversion, Lookup tables for

Customer Controls, and D/A Conversion. The Format Conversion requires 8Mbytes external SDRAMs (four 2Mbytes SDRAM: GM72V161621AT or same type). Figure 3. shows one DTV solution by using VDP chip.

Figure 2. Block Diagram of Video Display Processor

Figure 3. DTV Solution Diagram

## 5. Functional Description

### 5.1 Format Conversion

The Format Conversion Block receives all Grand Alliance input image formats, 480x720 image format, two digital NTSC image formats, and

VGA/SVGA input formats and converts them into 1080x1920 interlaced display format. The followings are specifications of the format conversion functions of the VDP.

**Table 1. HD Input Formats (Chrominance Format 4:2:0, Aspect Ratio 16:9)**

| VIDEO RESOLUTIONS<br>(Vertical lines x Horizontal Pixels) | FRAME RATES | SCAN TYPES  |

|-----------------------------------------------------------|-------------|-------------|

| 1080x1920                                                 | 30Hz        | Progressive |

| 1080x1920                                                 | 24Hz        | Progressive |

| 1080x1920                                                 | 30Hz        | Interlaced  |

| 720x1280                                                  | 60Hz        | Progressive |

| 720x1280                                                  | 30Hz        | Progressive |

| 720x1280                                                  | 24Hz        | Progressive |

**Table 2. SD Input Formats (Chrominance Format 4:2:0)**

| VIDEO RESOLUTIONS<br>(Vertical lines x Horizontal Pixels) | FRAME RATES | ASPECT RATIOS | SCAN TYPES  |

|-----------------------------------------------------------|-------------|---------------|-------------|

| 480x704                                                   | 60Hz        | 4:3 or 16:9   | Progressive |

| 480x704                                                   | 30Hz        | 4:3 or 16:9   | Progressive |

| 480x704                                                   | 24Hz        | 4:3 or 16:9   | Progressive |

| 480x704                                                   | 30Hz        | 4:3 or 16:9   | Interlaced  |

| 480x720                                                   | 60Hz        | 4:3 or 16:9   | Progressive |

| 480x720                                                   | 30Hz        | 4:3 or 16:9   | Progressive |

| 480x720                                                   | 24Hz        | 4:3 or 16:9   | Progressive |

| 480x720                                                   | 30Hz        | 4:3 or 16:9   | Interlaced  |

| 480x640                                                   | 60Hz        | 4:3           | Progressive |

| 480x640                                                   | 30Hz        | 4:3           | Progressive |

| 480x640                                                   | 24Hz        | 4:3           | Progressive |

| 480x640                                                   | 30Hz        | 4:3           | Interlaced  |

**Table 3. Digital NTSC and VGA Input Formats (Chrominance Format 4:2:2, Aspect Ratio 4:3)**

| VIDEO RESOLUTIONS<br>(Vertical lines x Horizontal Pixels) | FRAME RATES | SCAN TYPES  |

|-----------------------------------------------------------|-------------|-------------|

| 480x720                                                   | 30Hz        | Interlaced  |

| 480x768                                                   | 30Hz        | Interlaced  |

| 480x768                                                   | 60Hz        | Progressive |

| 480x640                                                   | 60Hz        | Progressive |

| 768x1024                                                  | 60Hz        | Progressive |

**Table 4. Display Output Format (Chrominance Format 4:4:4, Aspect Ratio 16:9)**

| VIDEO RESOLUTIONS<br>(Vertical lines x Horizontal Pixels) | FRAME RATES | SCAN TYPES |

|-----------------------------------------------------------|-------------|------------|

| 1080x1920                                                 | 30Hz        | Interlaced |

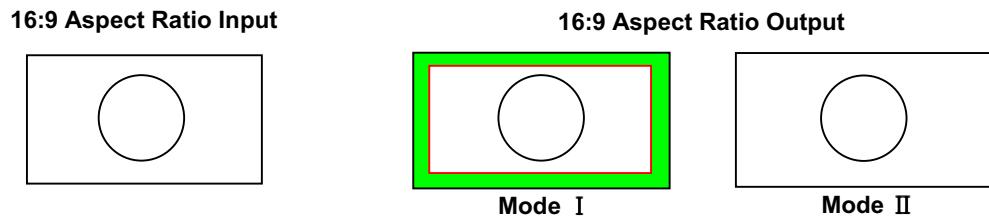

### 16x9 Image Display Mode

Two HD size images are converted into 1080x1920 display size. But SD size images are converted into 960x1760 or 1080x1920 active image size and displayed in the 1080x1920 display as shown in Figure 4. Therefore, there is some black area at the

outer part of the display in the Mode I. The active display position can be moved by ‘sd\_pos\_x’, ‘sd\_pos\_y’ registers. The resolution of active display is shown in Table 5.

Figure 4. Display Modes

Table 5. Main Picture Display Resolution(16:9 Input Image)

| INPUT FRAME RESOLUTIONS<br>(Vertical Lines x Horizontal Pixels) | ACTIVE DISPLAY RESOLUTION<br>(Vertical Lines x Horizontal Pixels) |

|-----------------------------------------------------------------|-------------------------------------------------------------------|

| 1080x1920                                                       | 1080x1920                                                         |

| 720x1280                                                        | 1080x1920                                                         |

| 480x704                                                         | 960x1706, 1080x1920                                               |

| 480x720                                                         | 960x1706, 1080x1920                                               |

#### 4x3 Image Display Modes

The 4x3 SD input and NTSC input can be displayed into 4x3 aspect ratio image or 16x9 aspect ratio one. The display mode can be selected by ‘arc\_mode’ register. Mode I, the default display mode, generates 4x3 active display. Mode III and Mode IV generates 16x9 active display.

The active display resolution in each mode is shown in Table 6. In the mode V display, active display area can be controlled by ‘v\_offset’ value of ‘arc\_mode’ register.

4:3 Aspect Ratio Input

16:9 Aspect Ratio Output

Mode I

Mode II

Mode III

Mode IV

Mode V

Figure 5. Display Mode

Table 6. Active Display Resolution for Each Mode

| MODE     | ACTIVE DISPLAY RESOLUTION |

|----------|---------------------------|

| Mode I   | 960x1280                  |

| Mode II  | 1080x1440                 |

| Mode III | 960x1706                  |

| Mode IV  | 1080x1920                 |

| Mode V   | 1080(1440)x1920           |

Table 7. Possible Display Modes for Progressive Frame Input Formats

| INPUT FRAME RESOLUTIONS<br>(Vertical lines x Horizontal Pixels) | DISPLAY MODES          |

|-----------------------------------------------------------------|------------------------|

| 480x640                                                         | mode I, II, III, IV, V |

| 480x704                                                         | mode I, II, III, IV, V |

| 480x720                                                         | mode I, II, III, IV, V |

| 480x768                                                         | mode I, II, III, IV, V |

Table 8. Possible Display Modes for Interlaced Frame Input Formats

| INPUT FRAME RESOLUTIONS<br>(Vertical Lines x Horizontal Pixels) | DISPLAY MODES          |

|-----------------------------------------------------------------|------------------------|

| 480x640                                                         | mode I, II, III, IV, V |

| 480x704                                                         | mode I, II, III, IV, V |

| 480x720                                                         | mode I, II, III, IV, V |

| 480x768                                                         | mode I, II, III, IV, V |

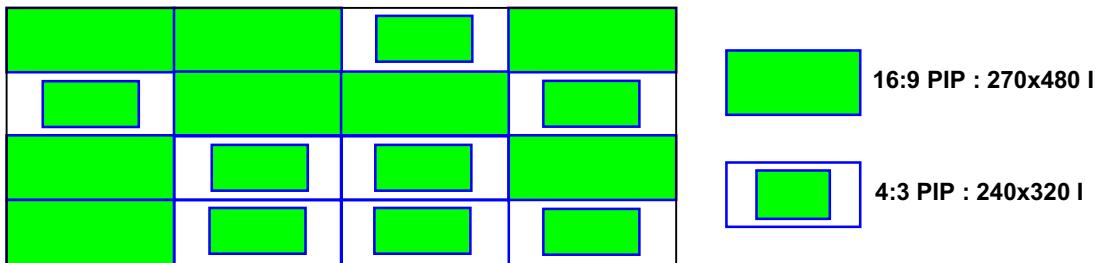

### PIP Specification

The VDP supports two selectable PIP sizes. Each PIP can be located in the arbitrary positions. The size of each PIP window is slightly different depending on the input format size. The VDP cannot run two ATV or two NTSC images simultaneously by PIP operation.

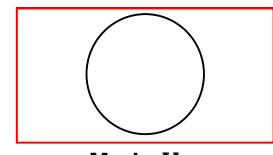

As shown in the Figure 6. and Figure 7. only “ATV main, NTSC PIP” mode or “NTSC main,

ATV PIP” mode is possible. The PIP size and location can be controlled by ‘**pip\_mode**’ and ‘**pip\_pos\_x**’ and ‘**pip\_pos\_y**’ registers. The PIP border line width and color can be controlled by ‘**pip\_mode**’ register and ‘**pip\_brdr\_clr**’ register. The boundary part of PIP can be 5%, 10% cropped to remove the noisy boundary part images.

Figure 6. PIP Modes - 4:3 PIP Mode (Main ATV, PIP NTSC or Main NTSC, PIP:SD)

Figure 7. PIP Modes - 16:9 PIP Mode (Main:NTSC, PIP:ATV)

Table 9. PIP Conversion Size(Main: NTSC, 16:9 PIP)

| INPUT FRAME SIZE<br>(Vertical Lines x Horizontal Pixels) | LARGE PIP SIZE | SMALL PIP SIZE |

|----------------------------------------------------------|----------------|----------------|

| 1080x1920                                                | 540x960        | 270x480        |

| 720x1280                                                 | 540x960        | 360x640        |

| 480x704                                                  | 480x880        | 360x704        |

| 480x720                                                  | 480x880        | 360x704        |

Table 10. PIP Conversion Size(Main: HD or NTSC, 4:3 PIP)

| FRAME SIZE<br>(Vertical Lines x Horizontal Pixels) | LARGE PIP SIZE | SMALL PIP SIZE |

|----------------------------------------------------|----------------|----------------|

| 480x640                                            | 480x640        | 360x480        |

| 480x704                                            | 480x704        | 360x528        |

| 480x720                                            | 480x704        | 360x528        |

| 480x768                                            | 480x768        | 360x576        |

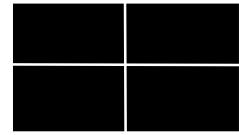

### Multi-PIP Specification

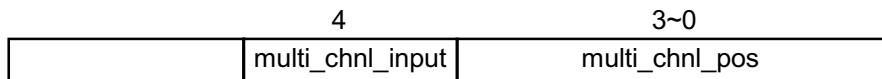

The VDP supports 16 channel Multi-PIP operation. The only one of the 16 PIPs is motion picture and the other images are in the frozen status. The ‘display mode’ register is used for selecting Multi-PIP mode. The ‘multi\_chnl\_pos’ register is used to select motion picture position among 16 PIP positions.

ATV input and NTSC input can be displayed in the Multi-PIP window. The border colors of Multi-PIP and PIP can be programmed independently. If the border colors of Multi-PIP and PIP are different,

the border of motion picture window can be moved by programming ‘pip\_pos\_x’ and ‘pip\_pos\_y’ register to synchronize with “multi\_chnl\_pos” register.

Multi-PIP operation only operates when ATV input signal is valid.

The required position register values are listed in the register description section. Setting FIR Filter coefficients can enhance display quality. Low pass Filtering can reduce the aliasing effect in the multi-PIP display mode.

Figure 8. Multi-PIP(16 PIPs)

Table 11. PIP Conversion Size for Multi-PIP(16:9 PIP)

| INPUT FRAME SIZE<br>(Vertical Lines x Horizontal Pixels) | PIP SIZE |

|----------------------------------------------------------|----------|

| 1080x1920                                                | 270x480  |

| 720x1280                                                 | 270x480  |

| 480x704                                                  | 240x352  |

| 480x720                                                  | 240x352  |

Table 12. PIP Conversion Ratio for Multi-PIP(4:3 PIP)

| INPUT FRAME SIZE<br>(Vertical Lines x Horizontal Pixels) | PIP SIZE |

|----------------------------------------------------------|----------|

| 480x640                                                  | 240x320  |

| 480x704                                                  | 240x352  |

| 480x720                                                  | 240x352  |

| 480x768                                                  | 240x384  |

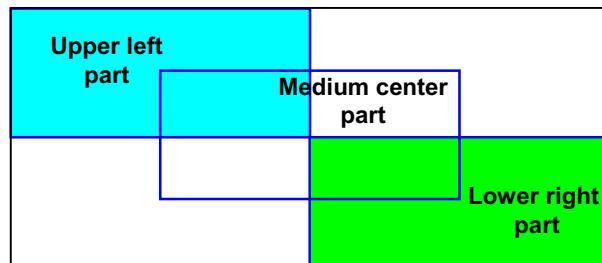

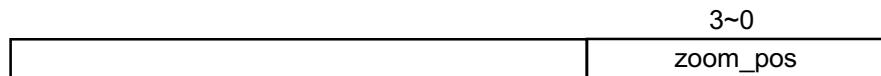

### Zoom Specification

The VDP supports x4 zoom operation for 1080x1920 or 720x1280 input format. The nine zoom positions(upper left, upper center, upper right, medium left, medium center, medium right, lower left, lower center, and lower right part) can be selected and zoomed into 1080x1920 image

size. Zoom operation can also be used after the freeze operation. After the freeze operation, the picture quality can be enhanced or changed by lookup table and FIR filter control. In the zoom operation mode, PIP operation is not supported.

Figure 9. Zoom Operation

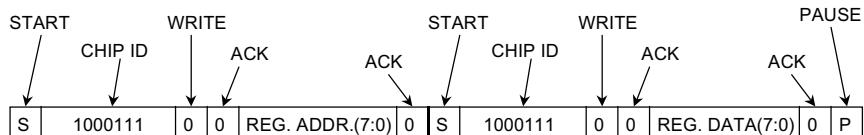

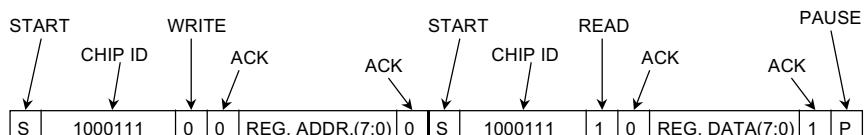

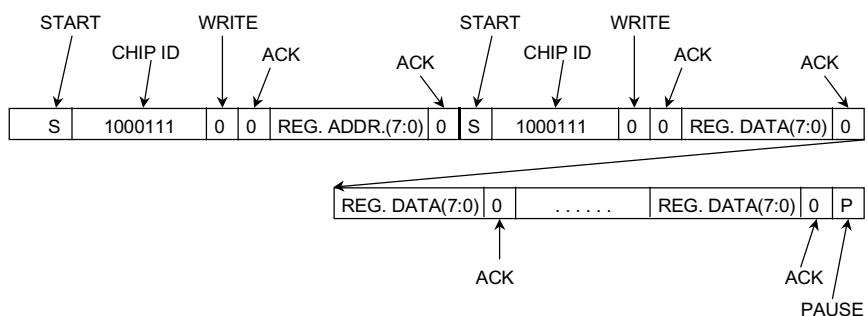

## 5.2 I<sup>2</sup>C bus interface

The I<sup>2</sup>C bus interface is used for host data interface. It operates only as a Slave. The Chip-ID(dev address) of the VDP is '1000111' b(0x8e). The data on the I<sup>2</sup>C-bus can be transferred at the rate up to 100 Kbit/s in the standard mode, or up to 400 Kbit/s in the fast mode. The I<sup>2</sup>C bus data Read/Write(R/W) formats of the VDP are shown

in Figure 10. and Figure 11. Normal register R/W uses this R/W cycle. The OSD, palette, and the lookup table data write operation use the I<sup>2</sup>C burst write (incremental address) mode. I<sup>2</sup>C Burst Write Cycle is shown in Figure 12. For more I<sup>2</sup>C bus information, refer to the I<sup>2</sup>C bus standard.

Figure 10. Write Cycle Diagram

Figure 11. Read Cycle Diagram

Figure 12. Burst Write Cycle Diagram

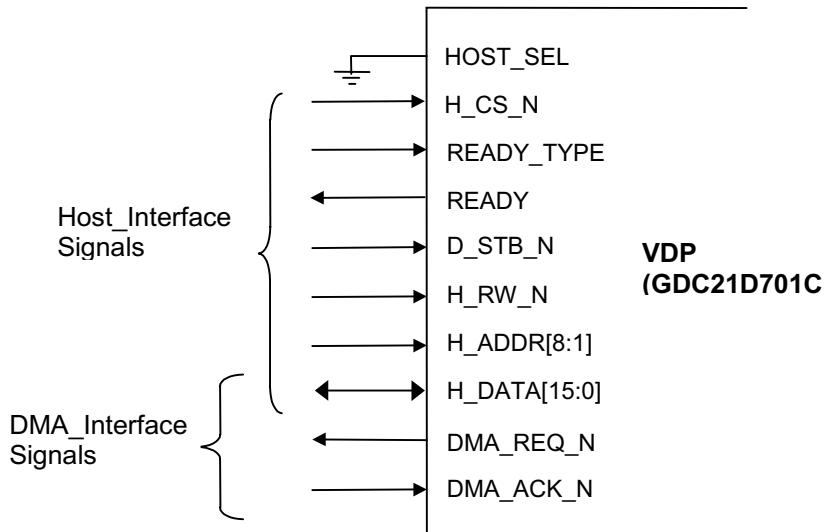

### 5.3 Host Interface

Figure 13. Host Interface

#### 5.3.1. Host Interface Signal Description

|                     |                  |                                                                                                                                                                                                                                                                                                        |

|---------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>H_CS_N</b>       | Host Chip Select | If this signal is set to '0', the host interface of the GDC21D701C is selected. According to H_RW_N signal status, microprocessor performs write/read operation. If this signal is '1', the host interface doesn't answer to external microprocessor address and dataline, databus is on 3-state mode. |

| <b>READY-TYPE</b>   | Ready Type       | If this signal is set to '0', Ready signal status is Active LOW, if this is '1', it is Active HIGH.                                                                                                                                                                                                    |

| <b>H_ADDR[8:1]</b>  | Host Address     | This 8-bit address bus is used when external host processor approaches to the GDC21D701C internal register or external SDRAM through the GDC21D701C. One bus cycle is generated when H_CS_N signal is activated. This address supports only 16-bit word approach.                                      |

| <b>READY</b>        | Data Ready       | When H_CS_N signal is not activated, the Ready signal goes to high-impedance output. It informs the host processor of termination of the GDC21D701C internal operation.                                                                                                                                |

| <b>H_DATA[15:0]</b> | Data Bus         | This 16-bit data bus sends or takes the data from the host processor. When the host processor is reading, the GDC21D701C drives this data bus, and it is writing, the host processor drives this. If it isn't in any bus cycle, this data bus goes to 3-state.                                         |

| <b>D_STB_N</b>      | Data Strobe      | When the host processor is writing, this signal indicates that the data is ready. When it is reading, this indicates that the data is read at the moment of change from LOW to HIGH.                                                                                                                   |

| <b>H_RW_N</b>       | Read/Write       | If this signal is LOW, it indicates that the host processor is writing. If this is HIGH, it indicates that the host processor is reading. When writing, data should be valid at the moment that the D_STB_N signal is changed from '1' to '0'.                                                         |

| <b>HOST_SEL</b>     | Host Select      | If this signal is '0', the host interface in the GDC21D701C is activated. If this is '1', pins related to the host interface are used as digital output.                                                                                                                                               |

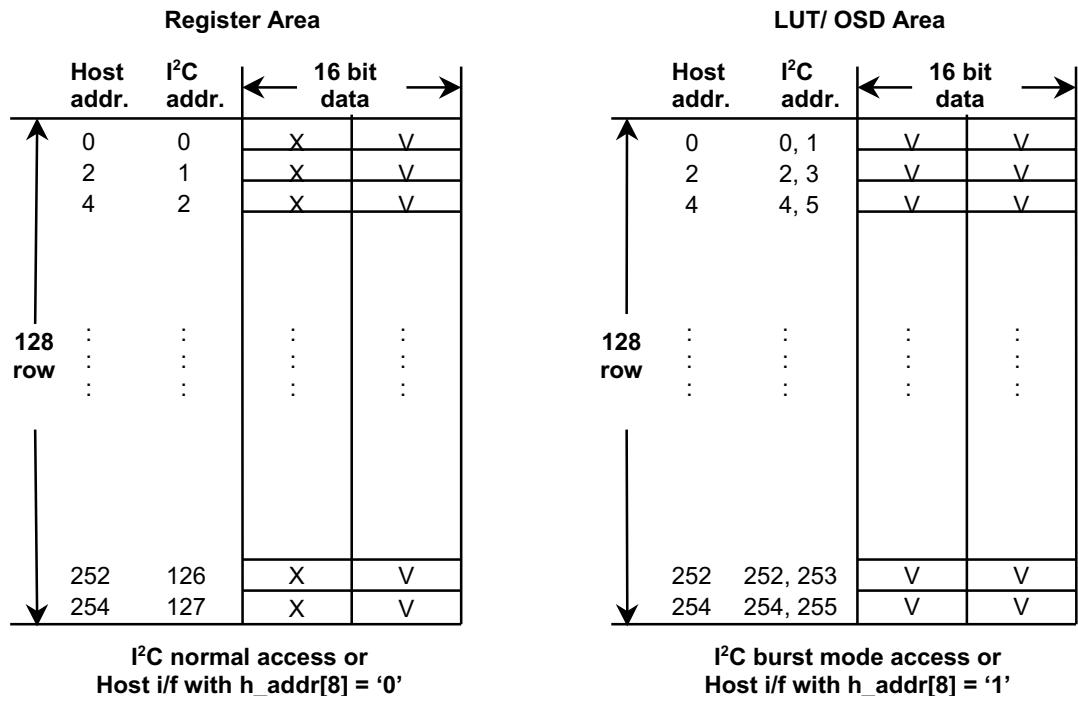

Figure 14. Address Map

Figure 14. shows address map of registers and LUT and OSD blocks in I<sup>2</sup>C mode operation and parallel host interface operation. In parallel host interface

mode, each LUT data elements can be changed individually.

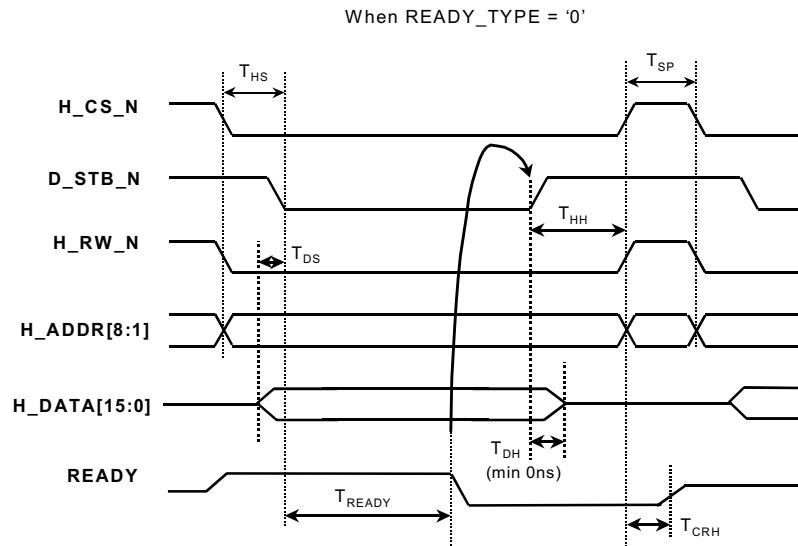

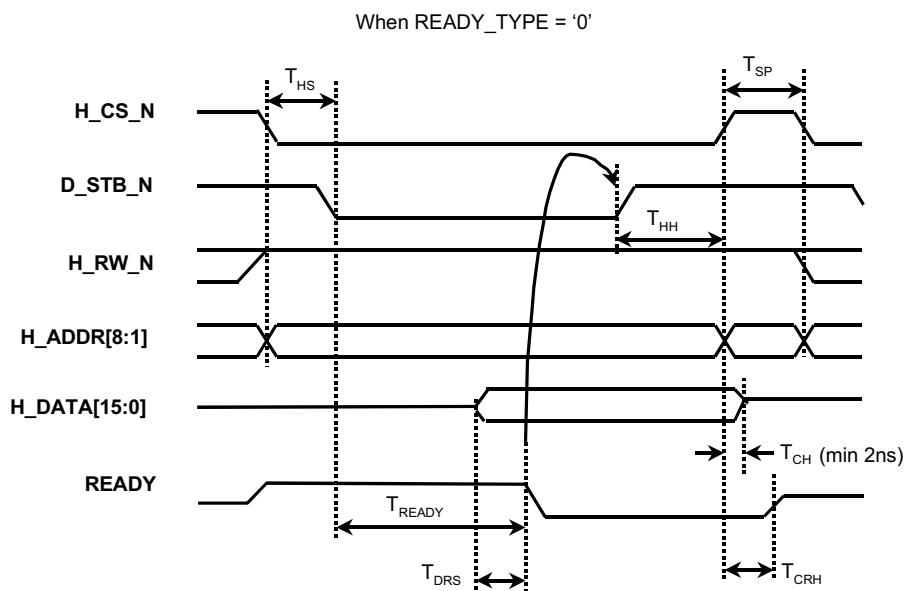

Figure 15. Host Write Timing

|          | MIN  | MAX |             | MIN  | MAX          |

|----------|------|-----|-------------|------|--------------|

| $T_{HS}$ | 0    |     | $T_{CRH}$   | 18.5 |              |

| $T_{SP}$ | 18.5 |     | $T_{READY}$ | 130  | User setting |

| $T_{HH}$ | 0    |     | $T_{DRS}$   | 18.5 |              |

Figure 16. Host Read Timing

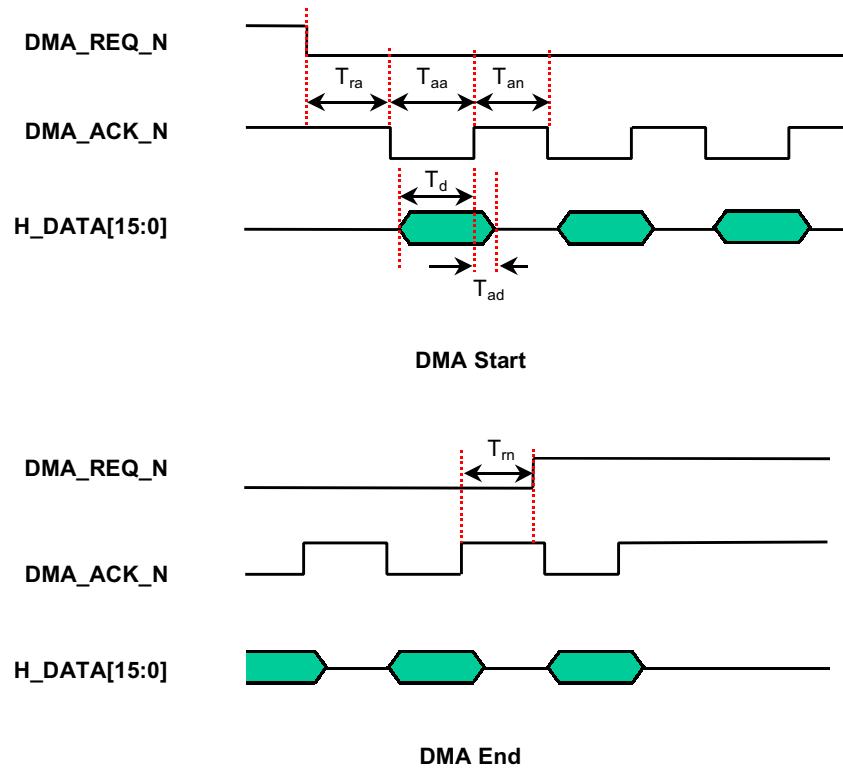

### 5.3.2 DMA Operation

#### DMA Start

If dma\_start field of dma\_mode register is set to '1', DMA\_REQ\_N signal is asserted to '0' and the VDP demands to DMAC the OSD data transmission.

When `dma_mode='0'`

DMA\_REQ\_N

(`dma_block_size + 1`) x 128 transfers

When `dma_mode='1'`

DMA\_REQ\_N

4 transfers 4 transfers ..... Total 128 transfers

#### DMA operation mode

dma\_mode field of dma\_mode register decides the assertion duration of DMA\_REQ\_N signal.

#### DMA Idle time

DMA operation is that 128 transfers compose 1 block, which total block number is set at `dma_block_size` register. After all blocks are transmitted, DMA\_REQ\_N signal is deasserted.

#### DMA\_REQ\_N timing

DMA\_REQ\_N signal deasserts maximum 55.5ns after deassertion of DMA\_ACK\_N signal at the end of transmission in case that `dma_mode='0'` and in every 3<sup>rd</sup> in case that `dma_mode='1'`.

#### DMA End

DMA operation is ended after it transfers the blocks as many as the blocks which are set at `dma_block_size` register.

Figure 17. DMA Timing

| SYMBOL   | DESCRIPTION                                | MIN     | MAX       |

|----------|--------------------------------------------|---------|-----------|

| $T_{ra}$ | DMA_REQ_N Assertion to DMA_ACK_N Assertion | 0 ns    | -         |

| $T_{aa}$ | DMA_ACK_N Assertion                        | 18.5 ns | -         |

| $T_{an}$ | DMA_ACK_N Negation                         | 18.5 ns | -         |

| $T_d$    | H_DATA Start to DMA_ACK_N Negation         | 18.5 ns | -         |

| $T_{ad}$ | DMA_ACK_N Negation to H_DATA End           | 0 ns    | -         |

| $T_m$    | DMA_ACK_N Negation to DMA_REQ_N Negation   |         | 55.5 ns - |

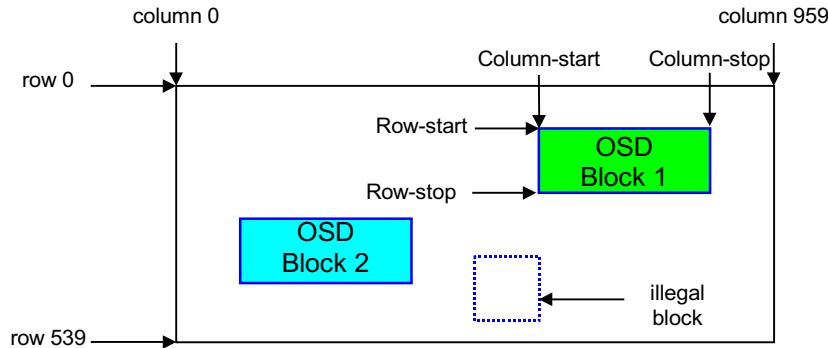

## 5.4 On-screen Display

The VDP supports On-screen Display(OSD) function. The OSD block gets 4:4:4 format video signal and sends converted video to the color-space converter. The input video signal is overlaid by user-defined OSD data including characters, symbols, and/or any other kind of graphic image.

The OSD data is described as a collection of rectangular blocks as shown in Figure 18. Two blocks can not be defined in the same row. As shown in Figure 19, a block is composed of a header and a bitmap data. The header contains positional information and the number of color used in the block.

There are 3 OSD layers in addition to the video layer; on the top is a cursor and below the cursor are 2 OSD layers and video. The mouse cursor, 32x32 pixels, can be moved just by programming the actual position. View ports are used for the layers to get OSD data seamlessly from external memory.

Main features are as follows:

- Multiple layers: cursor, two OSD layers above video

- Unlimited number of OSD regions per video field

- Capable of horizontal doubling

- Color resolution of 2/4/8 bits per pixel using pseudo color or 16 bits per pixel using true color

- Mouse cursor (32x32 pixel bitmap, 4 colors) movable all over screen

- Alpha keying factor variable between 0 and 1 in steps of 1/16

- Linked-list memory management

- Ease of animation

## Control Registers

Control registers are checked for their values during every vertical blanking interval.

| ADDRESS | BIT FIELD             | FUNCTION                                                                                                                        |

|---------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 40h     | 7 : 0                 | Start Address of Cursor Bitmap, LSB                                                                                             |

| 41h     | 7 : 0                 | Start Address of Cursor Bitmap, MSB                                                                                             |

| 42h     | 7 : 0                 | Start Address of the First Header of OSD Layer 0, LSB                                                                           |

| 43h     | 7 : 0                 | Start Address of the First Header of OSD Layer 0, MSB                                                                           |

| 44h     | 7 : 0                 | Start Address of the First Header of OSD Layer 1, LSB                                                                           |

| 45h     | 7 : 0                 | Start Address of the First Header of OSD Layer 1, MSB                                                                           |

| 48h     | 0<br>1<br>2<br>4<br>5 | Cursor Enable<br>OSD Layer 0 (top) Enable<br>OSD Layer 1 Enable<br>OSD Layer 0 Animation Enable<br>OSD Layer 1 Animation Enable |

| 4Ah     | 7:0                   | Cursor Position X, LSB                                                                                                          |

| 4Bh     | 2:0                   | Cursor Position X, MSB                                                                                                          |

| 4Ch     | 7:0                   | Cursor Position Y, LSB                                                                                                          |

| 4Dh     | 2:0                   | Cursor Position Y, MSB                                                                                                          |

| 4Eh     | 0                     | OSD Register Update                                                                                                             |

Figure 18. OSD Blocks in Video Display

### OSD Data Addressing

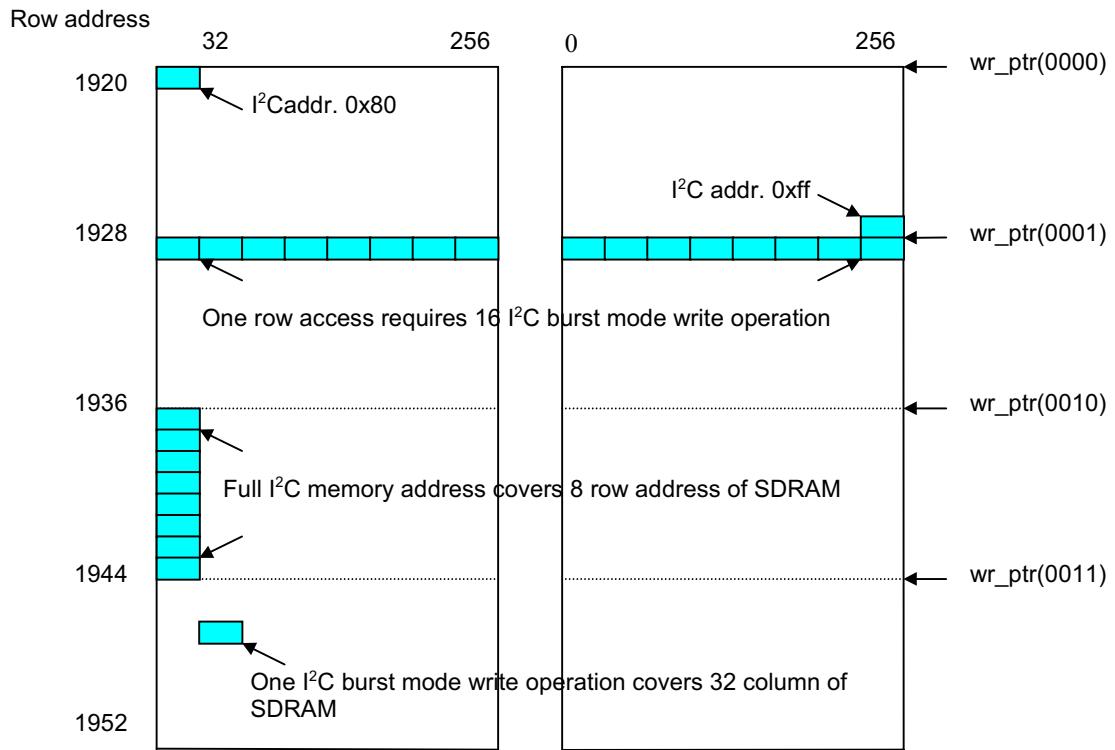

The I<sup>2</sup>C bus address block of the VDP uses 8-bit programmable address and 8-bit incremental address. The only programmable address is used for VDP register access. But both programmable address and incremental address are used in lookup table write operation and in OSD data and palette write operation.

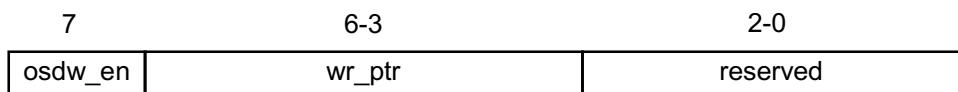

Lookup table access and OSD data write operation uses 0x80 ~ 0xff programmable address and 8-bit incremental address. Before the lookup table access, palette access, or OSD data write operation, each register must be set to the proper value. For lookup table access, 'lutw\_en' bit of 'lut\_sel' register must be set to '1', and 'osdw\_en' bit of 'osd\_mode' register must be set to '0'. For OSD data write operation, 'lutw\_en' bit of 'lut\_set' register and must be set to '0', 'lutwrgb' register must be set to '1' and 'osdw\_en' bit of 'osd\_mode' register must be set to '1'. The 'osd\_en' flag in 'osd\_mode' register enables or disables the OSD function.

The four OSD buffers of SDRAM can be accessed by the 4-bit 'wr\_ptr' value of 'osd\_mode' register, 8-bit programmable address(0x80~0xff), and 8-bit incremental address(0x00~0xff). The 8-bit incremental address covers 32 column address

of SDRAM(32 column x 8 byte/column = 256 byte). The 8-bit programmable address(0x80 ~ 0xff) covers 8 row of SDRAM(8 access/bank x 2 x 8 row = 128). As full I<sup>2</sup>C address range covers a quarter of OSD data buffer, the 4-bit 'wr\_ptr' is used for addressing four OSD data buffers. Before the OSD data write, proper 'wr\_ptr' must be set.

The VDP uses these register values for proper OSD address generation. In incremental addressing mode, 256 sequential data must be written to the VDP. If there is no sufficient data, zero padding to 256-byte is necessary for the proper operation of the VDP. When the digital output part of the VDP isn't be used, parallel host interface is used to load OSD data fast. In case that the host interface is used, as mentioned in chapter 5.3, register access, LUT and OSD data can be accessed, and OSD data can be loaded via DMA. When OSD is loaded through the host interface, the address corresponding to I<sup>2</sup>C programmable address uses 'osd\_base' register value, and when via DMA, the OSD data start address refers to this register.

## Memory Map

OSD data is organized in regions. Each region consists of a header and a bitmap. The header contains a pointer to the next OSD region, which is displayed at a lower screen position. The header of the first region is directed by a control register. To indicate that this is the last region, header pointer value must be all '0's.

In a layer of OSD, OSD regions cannot be overlapped in a horizontal row of pixels. A region can be placed anywhere on the screen if it doesn't exceed display area and row position (y) is greater than 1. For the interlaced raster scanning, top field lines have even numbers from 0 while bottom field lines have odd numbers from 1.

The number of bits per pixel (<nbits>) in the associated bitmap data can be 2, 4, or 8; therefore, <R> cannot be 2. It also defines the maximum number of colors within the image, and the maximum number of elements in the following color map table, if it follows. For the layer under video, <nbits> is restricted to just 2 or 4, yielding maximum 16 color image using a color map table.

In case a new color map exists, it follows right after the header definition. A color map entry comprises blending bit B and 6-bit Y, 2x4 bit Cb/Cr as described below.

The 4-bit alpha makes 16 steps of blending of video and OSD. Alpha value 0 produces completely transparent OSD and value 15 produces completely opaque OSD. Y component value 0 also makes the color transparent regardless of Cb and Cr. Before an OSD color is mixed, it is left justified to produce 8 bits each of Y, Cb and Cr with the lower bits padded with zeros.

The format of the actual image is defined as the series of pixel color index values that make up the image. The pixels are stored left to right and top to bottom sequentially. The first pixel within an OSD region begins at the most significant bit of the first bitmap word. If true color mode is used, the image is defined as either 4:2:2 format CbYCrY or YCbCrAlpha (6:3:3:4 bits), both yielding 16 bits per pixel. In this case, the horizontal size of image should be a multiple of two.

| Bits                          |   |   |   |   |   |   |   |   |   | Word |   |   |   |   |   |             |

|-------------------------------|---|---|---|---|---|---|---|---|---|------|---|---|---|---|---|-------------|

| F                             | E | D | C | B | A | 9 | 8 | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 | No.         |

| T                             | P | R |   | A |   | 0 | 0 |   |   |      |   |   |   |   |   | 1           |

| H                             | 0 | 0 | 0 |   |   |   |   |   |   |      |   |   |   |   |   | 2           |

| Reserved                      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 3           |

| Next OSD Header Pointer       |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 4           |

| Upper-left Corner Position X  |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 5           |

| Upper-left Corner Position Y  |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 6           |

| Lower-right Corner Position X |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 7           |

| Lower-right Corner Position Y |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 8           |

| Reserved                      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 9           |

| Top Field Bitmap Pointer      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 10          |

| Reserved                      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 11          |

| Bottom Field Bitmap Pointer   |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 12          |

| Reserved                      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 13          |

| Animation Up Pointer          |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 14          |

| Reserved                      |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 15          |

| Animation Down Pointer        |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 16          |

| Color Map Table (if needed)   |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | 17          |

|                               |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   | (20/32/272) |

Figure 19. OSD Header Definition

Note :

T=0 - Pseudo color

P=0 - Use existing color map

P=1 - New color map follows

T=1 - True color (16 bits/pel)

P=0 - CbYCrY (8 bits each)

P=1 - YCbCrAlpha (6:3:3:4)

R+1 - <nbits>/2, where nbits is number of bits per pixel (2, 4, or 8)

A - alpha keying value

F+1 - animation frame count

H=1 - horizontal doubling

L= ceil(image\_size\*nbits/2048)

All pointers are 16-bit values which points a 64-bit word. : ( <row 7 bits> & <bank 1 bits> & <column 8 bits> )

| Bits |   |   |   |   |   |   |   |   |   |    | Word |   |   |    |   |     |

|------|---|---|---|---|---|---|---|---|---|----|------|---|---|----|---|-----|

| F    | E | D | C | B | A | 9 | 8 | 7 | 6 | 5  | 4    | 3 | 2 | 1  | 0 | No. |

|      |   |   |   | Y |   | 0 | B |   |   | Cb |      |   |   | Cr |   | 1   |

**Figure 20. Color Map Entry**

Note :

B=0 - opaque color

B=1 - blend allowed

## Cursor

The cursor has size of 32x32 at maximum and can be placed anywhere on the screen. The position information which is written on a register is read every vertical blanking interval. The bitmap start address is also checked during that interval and a new cursor bitmap is loaded into internal memory if the new bitmap pointer differs from old one. Four cursor colors and hotspot position data follows bitmap. The hotspot point of a cursor will

be located on the screen position specified by registers.

The cursor bitmap is defined as the series of 2-bit pixel color index values. Every four 16-bit words defines a horizontal row of 32 pixels from left to right and the 32 succession of 4 words makes up a whole cursor. If you want a smaller cursor than 32x32 one, fill the non-used space with a transparent-color index.

| Bits            |   |   |   |   |           |   |   |   |   |   | Word |   |   |   |   |     |

|-----------------|---|---|---|---|-----------|---|---|---|---|---|------|---|---|---|---|-----|

| F               | E | D | C | B | A         | 9 | 8 | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 | No. |

| 32 x 32 pattern |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   |     |

| Cursor Color 0  |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   |     |

| Cursor Color 1  |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   |     |

| Cursor Color 2  |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   |     |

| Cursor Color 3  |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   |     |

| Hotspot X       |   |   |   |   | Hotspot Y |   |   |   | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 128 |

| 0               | 0 | 0 | 0 | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 129 |

|                 |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   | 130 |

|                 |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   | 131 |

|                 |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   | 132 |

|                 |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   | 133 |

|                 |   |   |   |   |           |   |   |   |   |   |      |   |   |   |   | 134 |

**Figure 21. Cursor Definition**

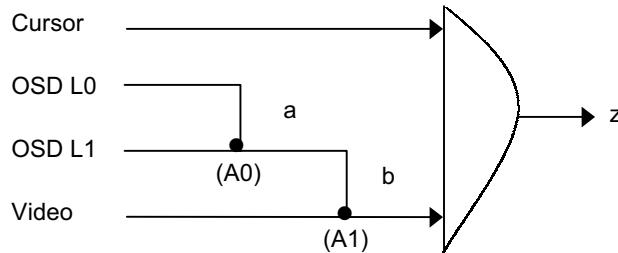

### Mixing

There are two OSD layers above video and one layer under video; and on top is the cursor. The top two OSD layers can be mixed at 16 levels and the

result can be mixed with video at 16 levels. The bottom OSD layer is visible only when video is not active, for example, outside of a PIP box.

Note :

X denotes mixing operation with blending factor A0 or A1.

$a = L0xA0 + L1x(1-A0)$

$b = axA1 + Videox(1-A1)$  when  $A0 \neq 1$ , else  $b = L0$

$A0, A1 = k/64$  where  $k = 0 \dots 62, 64$

### Animation

OSD layers 0 and 1 (L0, L1) supports simple animation. Only one animation object is allowed at a time on a layer. To support animation, a header contains two pointers in order to make a double linked list. If animation was enabled and both pointers are not 0 in a header, next animation object (OSD header) is automatically called by tracking animation up/down pointers.

#### EXAMPLE: CASE 1 - circular animation

Values inside parentheses = (header\_ptr, anim\_up\_ptr, anim\_dn\_ptr, [anim\_Frame\_cnt])

OSD display order in frame number from the start of animation:

|                 |   |       |   |       |   |

|-----------------|---|-------|---|-------|---|

| Frame 0: OSD 1  | → | OSD 2 | → | OSD 3 | } |

| Frame 1: OSD 1  | → | OSD 2 | → | OSD 3 |   |

| Frame 2: OSD 1  | → | OSD 4 | → | OSD 3 |   |

| Frame 3: OSD 1  | → | OSD 5 | → | OSD 3 |   |

| Frame 4: OSD 1  | → | OSD 5 | → | OSD 3 |   |

| Frame 5: OSD 1  | → | OSD 6 | → | OSD 3 |   |

| Frame 6: OSD 1  | → | OSD 6 | → | OSD 3 |   |

| Frame 7: OSD 1  | → | OSD 6 | → | OSD 3 |   |

| Frame 8: OSD 1  | → | OSD 5 | → | OSD 3 |   |

| Frame 9: OSD 1  | → | OSD 5 | → | OSD 3 |   |

| Frame 10: OSD 1 | → | OSD 4 | → | OSD 3 |   |

| Frame 11: OSD 1 | → | OSD 2 | → | OSD 3 |   |

One Cycle

:

:

**EXAMPLE: CASE 2** - linear animation

|                 |   |                   |   |                 |

|-----------------|---|-------------------|---|-----------------|

| 1st OSD (1,0,0) | → | 2nd OSD (2,0,4,1) | → | 3rd OSD (3,0,0) |

|                 |   | ↓                 |   |                 |

|                 |   | 4th OSD (4,2,5,0) |   |                 |

|                 |   | ↓                 |   |                 |

|                 |   | 5th OSD (5,4,6,1) |   |                 |

|                 |   | ↓                 |   |                 |

|                 |   | 6th OSD (6,0,0,2) |   |                 |

Values inside parentheses = (header\_ptr, anim\_up\_ptr, anim\_dn\_ptr, [anim\_Frame\_cnt])

OSD display order in frame number from the start of animation:

|                 |   |       |   |       |   |

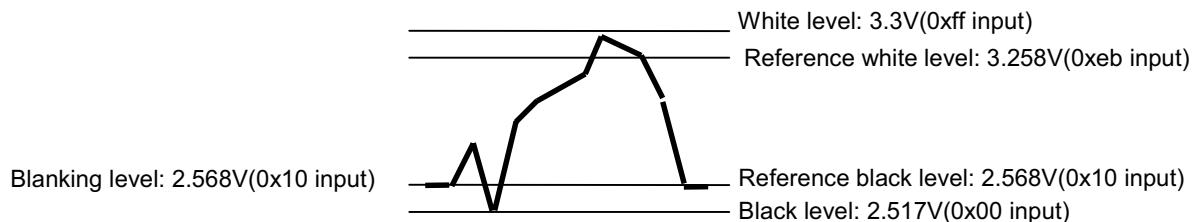

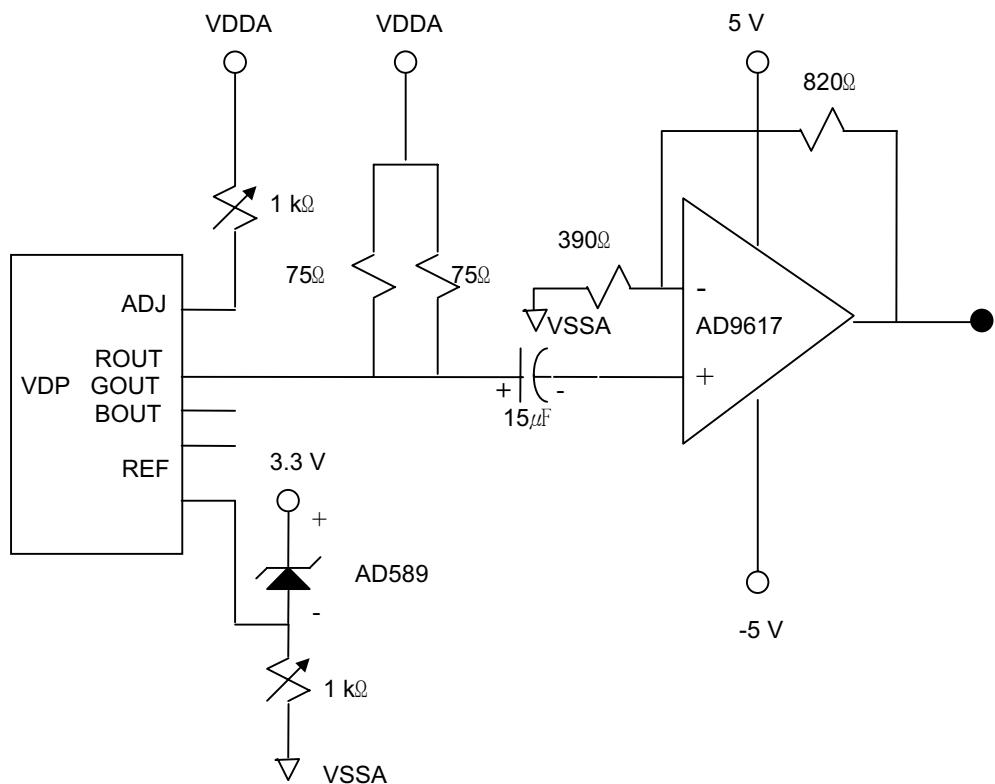

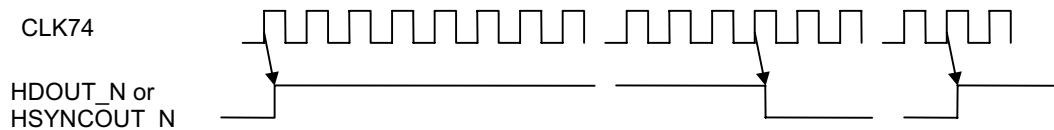

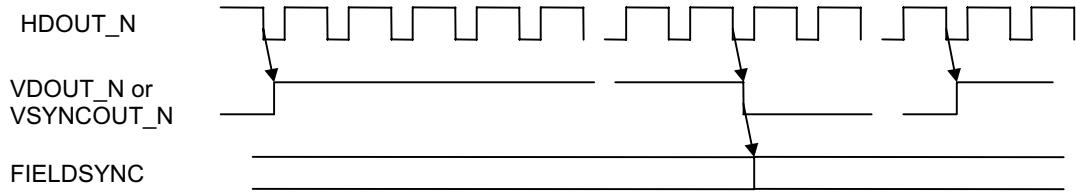

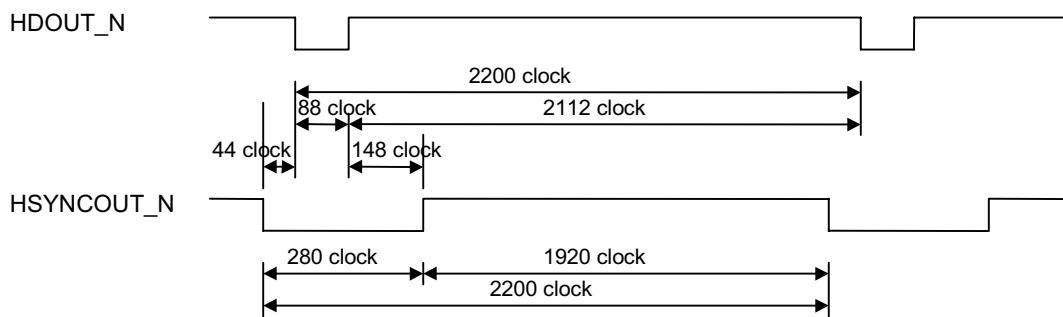

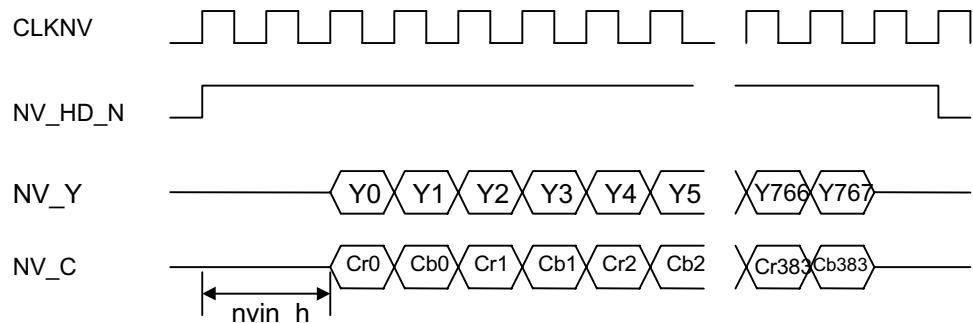

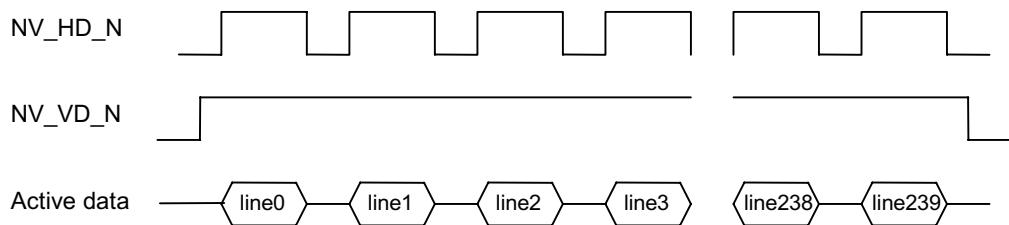

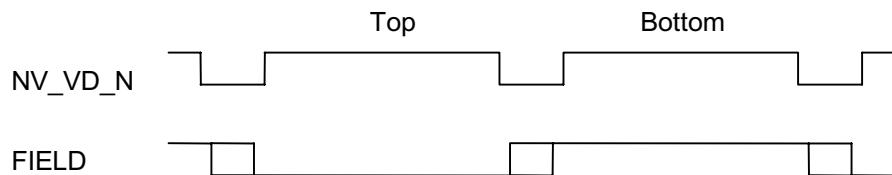

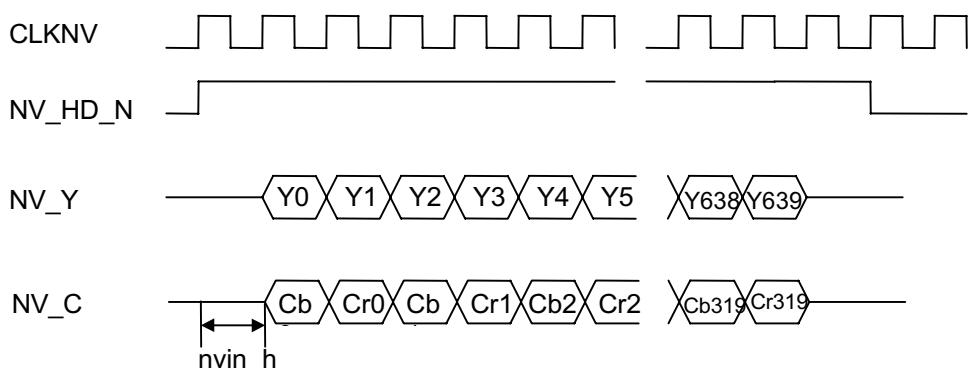

|-----------------|---|-------|---|-------|---|