Your Imagination, Our Creation

# GL641USB

# USB ATA/ATAPI/ COMPACT FLASH CARD CONTROLLER

SPECIFICATION REVISION 1.2

Genesys Logic, Inc.

10F, No.11, Ln.3, Tsao Ti Wei, Shenkeng, Taipei, Taiwan Tel: 886-2-2664-6655 Fax: 886-2-2664-5757

http://www.genesyslogic.com

# **INDEX**

| 1. | Features                         | 2 |

|----|----------------------------------|---|

| 2. | Functional Overview              | 3 |

|    | PIN Definitions and Descriptions |   |

|    | General Purpose I/O Ports        |   |

|    | Package Diagram                  |   |

|    | - w                              |   |

#### 1. Features

- High performance and low cost solution for USB ATA / ATAPI / Compact Flash controller

- USB Specification Compliance

- Conforms to USB 12Mbps Specification, Version 1.1

- Conforms to USB Storage Class Specification, Version 1.0 (bulk only protocol)

- Supports 1 device address and 4 endpoints (include endpoint 0)

- Operating System Supported

- Windows 2000 & Windows ME

- Supported by Microsoft default driver

- Windows 98 & Windows 98 SE

- Supported by Genesys Logic USB Storage driver

- Mac OS 9.X & Mac OS X

- Supported by Apple default driver or Genesys Logic USB Storage driver

- On-chip 3.3v output for USB D+ pulled up

- Integrated USB transceiver

- External EEPROM interface for customizing VID & PID of USB device

- Support ATA hard disk / ATAPI CD-ROM, CD-RW, MO / Compact Flash card in one chip

- Data transfer rate up to 1.1Mbytes/sec when read/write the USB storage device

- Improved output drivers with slew-rate control to reduce EMI

- 12 MHz external clock

- Internal power-on reset (POR)

- Internal power-fail detector

- Supports suspend/normal mode power management

- Available in cost saving 48-pins LQFP

- Suspend power consumption of bus powered CF card reader is less than 500μA (USB specification)

#### 2. Functional Overview

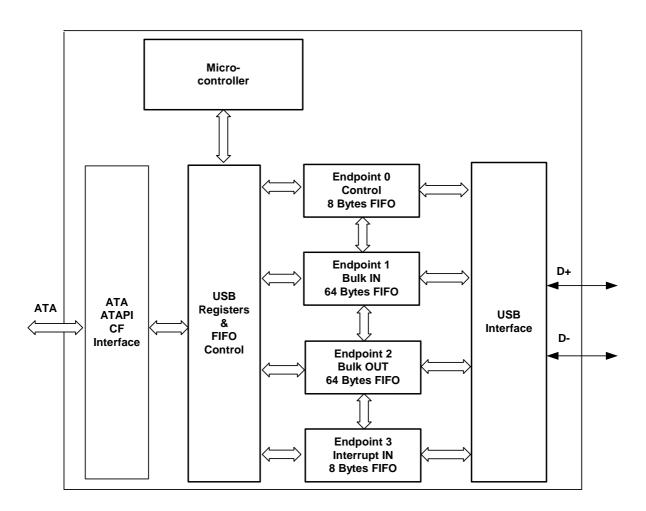

The GL641USB is a USB storage class controller that supports ATA/ATAPI/Compact Flash device. It is compliant to USB 12Mbps protocol and data transfer rate is up to 1.1Mbytes/Sec. It is also compliant to USB Storage Class Bulk Only protocol. There are 4 endpoints in GL641USB controller. Endpoint 0 is a Control endpoint for this controller. It is used to initialize this USB device. Endpoint 1 is a Bulk IN endpoint. It is used to read data from the storage device. Endpoint 2 is a Bulk OUT endpoint. It is used to issue SCSI packet command to the storage device and write data to the storage device. Endpoint 3 is an Interrupt IN endpoint and not used by USB Storage Class Bulk Only protocol currently.

Figure 2-1 Block Diagram of GL641USB

## 3. PIN Definitions and Descriptions

| Pin No. | Name        | I/O | Description                                 |  |

|---------|-------------|-----|---------------------------------------------|--|

| 1       | PVDD        | PWR | Power supplier for storage device interface |  |

| 2       | D8          | I/O | Storage device data bus bit 8*              |  |

| 3       |             |     | Storage device data bus bit 9*              |  |

| 4       |             |     | Storage device data bus bit 10*             |  |

| 5       | D11         | I/O | Storage device data bus bit 11*             |  |

| 6       | PGND        | PWR | Ground for storage device interface         |  |

| 7       | D12         | I/O | Storage device data bus bit 12*             |  |

| 8       | D13         | I/O | Storage device data bus bit 13*             |  |

| 9       | D14         | I/O | Storage device data bus bit 14*             |  |

| 10      | D15         | I/O | Storage device data bus bit 15*             |  |

| 11      | DIOR#       | 0   | Storage device read strobe signal*          |  |

| 12      | DIOW#       | 0   | Storage device write strobe signal*         |  |

| 13      | INTRQ       | I   | Storage device interrupt request signal*    |  |

| 14      | DVDD        | PWR | 5V power supplier for internal logic        |  |

| 15      | DGND        | PWR | Ground for internal logic                   |  |

| 16      | Crystal out | CLK | Crystal clock output                        |  |

| 17      | Crystal in  | CLK | Crystal clock input                         |  |

| 18      | GPIO1       | I/O | General purpose I/O 1                       |  |

| 19      | GPIO2       | I/O | General purpose I/O 2                       |  |

| 20      | V3.3        | USB | 3.3v power supplier for USB bus             |  |

| 21      | D+          | USB | D+ signal for USB                           |  |

| 22      | D-          | USB | D- signal for USB                           |  |

| 23      | AVDD        | PWR | 5V power supplier for USB interface         |  |

| 24      | AGND        | PWR | Ground for USB interface                    |  |

| 25      | GPIO3       | I/O | General purpose I/O 3                       |  |

| 26      | GPIO4       | I/O | General purpose I/O 4                       |  |

| 27      | TSTMODE     | I   | Used at test mode only                      |  |

| 28      | EXTRST#     | I   | Used at test mode only                      |  |

| 29      | GPIO8       | I/O | General purpose I/O 8                       |  |

| 30      | GPIO7       | I/O | General purpose I/O 7                       |  |

| 31      | GPIO6       | I/O | General purpose I/O 6                       |  |

| 32      | GPIO5       | I/O | General purpose I/O 5                       |  |

| 33      | DGND        | PWR | Ground for internal logic                   |  |

| 34      | DVDD        | PWR | 5V power supplier for internal logic        |  |

| 35      | CS3FX#      | O   | Storage device register bank 3 selector*    |  |

| 36      | CS1FX#      | О   | Storage device register bank 1 selector*    |  |

| 37      | A0          | О   | Storage device address bus bit 0*           |  |

| 38      | A1          | О   | Storage device address bus bit 1*           |  |

| 39      | A2          | 0   | Storage device address bus bit 2*           |  |

| 40      | D0          | I/O | Storage device data bus bit 0*              |  |

| 41      | D1          | I/O | Storage device data bus bit 1*              |  |

| 42      | D2          | I/O | Storage device data bus bit 2*              |  |

| 43      | D3          | I/O | Storage device data bus bit 3*              |  |

| 44      | PGND        | PWR | Ground for storage device interface         |  |

| 45      | D4          | I/O | Storage device data bus bit 4*              |  |

| 46      | D5          | I/O | Storage device data bus bit 5*              |  |

| 47      | D6          | I/O | Storage device data bus bit 6*              |  |

| 48      | D7          | I/O | Storage device data bus bit 7*              |  |

Table 3-1 GL641USB Pin Definitions and Descriptions

<sup>\*</sup> Output voltage of this pin is equivalent to voltage supplied by PVDD. Input voltage of this pin can be from 0v to 5v, and it threshold is  $1v \sim 2v$ . Therefore, these pins can support 3v/5v interface according to voltage of PVDD.

GL641USB

#### 4. General Purpose I/O Ports

The GL641USB interface with peripherals is conducted via up to 8 GPIO signals. Host driver can control all of these I/O pins directly. The GL641USB provides 3 vendor specific control transfer functions to host driver. One of these functions is used to set I/O pins direction. One is used to read data from I/O pins. And the other one is used to write data to I/O pins.

GPIO1 is used as a power on strapping to distinguish the application is used for Compact Flash card or other ATA/ATAPI device. If this pin is pulled up when USB bus reset, GL641USB will treat the connected device is a Compact Flash card. Otherwise, GL641USB will assume the connected device is an ATA/ATAPI device.

GPIO2 is used as power control signal for bus powered device, especially for Compact Flash card reader. Hence USB bus powered device must consume less than 500uA when suspend mode, power of the Compact Flash card should be turned off when system suspend.

GPIO3 is connected to external reset pin of ATA/ATAPI/Compact Flash card. The GL641USB can only work at True IDE mode when Compact Flash card is connected.

GPIO4~GPIO7 are used as serial EEPROM interface. System maker can write their own vendor ID and product ID into the serial EEPROM by a test program provided by Genesys Logic.

GPIO8 is used for Compact Flash card reader. This pin is pulled up by a resistor on board and connected to ground when Compact Flash card is inserted. This is used as a card detection signal.

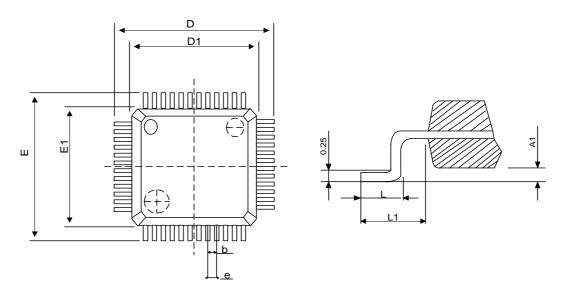

# 5. Package Diagram

## 48-LQFP

| SYVBOIS | MIN     | MAX  |  |

|---------|---------|------|--|

| A       |         | 1.6  |  |

| A1      | 0.05    | 0.15 |  |

| A2      | 1.35    | 1.45 |  |

| C1      | 0.09    | 0.16 |  |

| D       | 9.00BSC |      |  |

| D1      | 7.00BSC |      |  |

| Е       | 9.00BSC |      |  |

| E1      | 7.00BSC |      |  |

| e       | 0.5BSC  |      |  |

| b       | 0.17    | 0.27 |  |

| L       | 0.45    | 0.75 |  |

| L1      | 1 REF   |      |  |