## PRELIMINARY DATA SHEET

# gmZAN3 XGA Analog Interface LCD Monitor Controller

## GENESIS MICROCHIP CONFIDENTIAL

Publication Number: C0523-DAT-01G Publication Date: July 2003

The following are trademarks or registered trademarks of Genesis Microchip, Inc.:  $\mathsf{Genesis}^{\mathsf{TM}}, \mathsf{Genesis} \, \mathsf{Display} \, \mathsf{Perfection}^{\mathsf{TM}}, \, \mathsf{ESM}^{\mathsf{TM}}, \, \mathsf{RealColor}^{\mathsf{TM}}, \, \mathsf{Ultra-Reliable} \, \mathsf{DVI}^{\mathsf{TM}}, \, \mathsf{Real} \, \mathsf{Recovery}^{\mathsf{TM}}, \, \mathsf{Sage}^{\mathsf{TM}}, \, \mathsf{JagASM}^{\mathsf{TM}}, \, \mathsf{RealColor}^{\mathsf{TM}}, \, \mathsf{Color}^{\mathsf{TM}}, \, \mathsf{Color}^{\mathsf{TM}}$ SureSync<sup>™</sup>, Adaptive Backlight Control<sup>™</sup>, Faroudja<sup>™</sup>, DCDi<sup>™</sup>, TrueLife<sup>™</sup>, IntelliComb<sup>™</sup> Other brand or product names are trademarks of their respective holders.

© Copyright 2003 Genesis Microchip Inc. All Rights Reserved.

document.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to obtain the most recent revision of the document. Genesis Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors or omissions that may appear in this

## **Table Of Contents**

| 1 | Over  | view                                                                  | 8  |

|---|-------|-----------------------------------------------------------------------|----|

|   | 1.1   | gmZAN3 System Design Examples                                         |    |

|   | 1.2   | gmZAN3 Features                                                       | 9  |

| 2 | gmZ   | AN3 Pinout                                                            | 10 |

| 3 | gmZ   | AN3 Pin List                                                          | 12 |

| 4 | Func  | tional Description                                                    | 19 |

|   | 4.1   | Clock Generation                                                      | 19 |

|   | 4.1.1 | Using the Internal Oscillator with External Crystal                   | 19 |

|   | 4.1.2 | Using an External Clock Oscillator                                    | 22 |

|   | 4.1.3 | Clock Synthesis                                                       | 23 |

|   | 4.2   | Hardware Reset                                                        | 24 |

|   | 4.3   | Analog to Digital Converter                                           | 26 |

|   | 4.3.1 | ADC Pin Connection                                                    | 26 |

|   | 4.3.2 | ADC Characteristics                                                   | 28 |

|   | 4.3.3 | Clock Recovery Circuit                                                | 28 |

|   | 4.3.4 | Sampling Phase Adjustment                                             | 29 |

|   | 4.3.5 | Integrated Schmitt Trigger for Horizontal and Vertical Sync input     | 29 |

|   | 4.3.6 | SOG and CSYNC support                                                 | 30 |

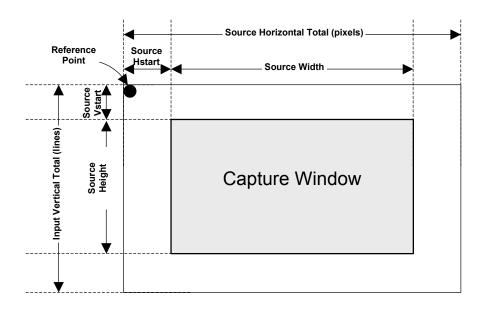

|   | 4.3.7 | ADC Capture Window                                                    | 31 |

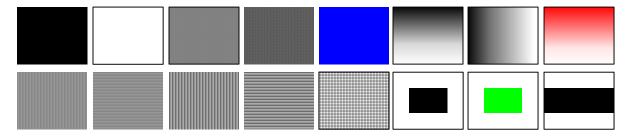

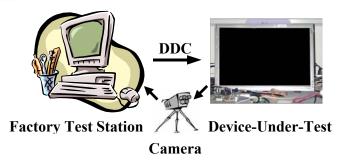

|   | 4.4   | Test Pattern Generator (TPG)                                          | 32 |

|   | 4.5   | Input Format Measurement                                              | 33 |

|   | 4.5.1 | Horizontal and Vertical Measurement                                   | 33 |

|   | 4.5.2 | Format Change Detection                                               | 33 |

|   | 4.5.3 | Watchdog                                                              | 34 |

|   | 4.5.4 | Internal Odd/Even Field Detection (For Interlaced Inputs to ADC Only) | 34 |

|   | 4.5.5 | Input Pixel Measurement                                               | 34 |

|   | 4.5.6 | Image Phase Measurement                                               | 34 |

|   | 4.5.7 | Image Boundary Detection                                              | 34 |

|   | 4.5.8 | Image Auto Balance                                                    | 34 |

|   | 4.6   | High-Quality Scaling                                                  | 35 |

|   | 4.6.1 |                                                                       |    |

|   | 4.6.2 |                                                                       |    |

|   | 4.7   | Gamma LUT                                                             | 35 |

|   | 4.8   | Display Output Interface                                              |    |

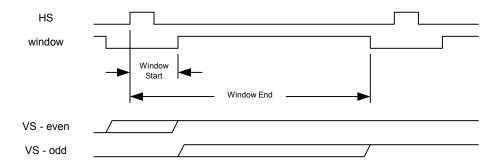

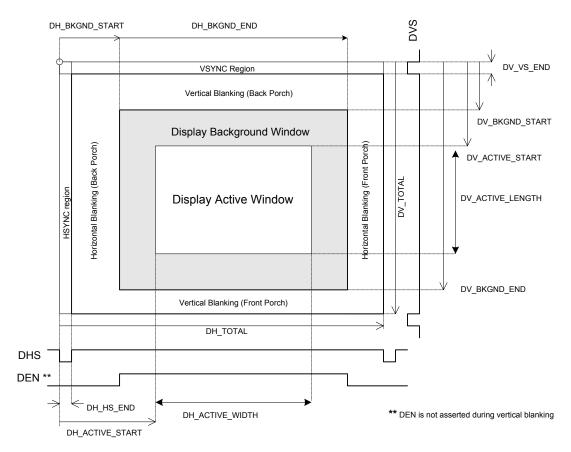

|   | 4.8.1 | Display Synchronization                                               | 35 |

|   | _     | DISPLAY PERFECTION                                 |    |

|---|-------|----------------------------------------------------|----|

|   | 4.8.2 | Programming the Display Timing                     | 36 |

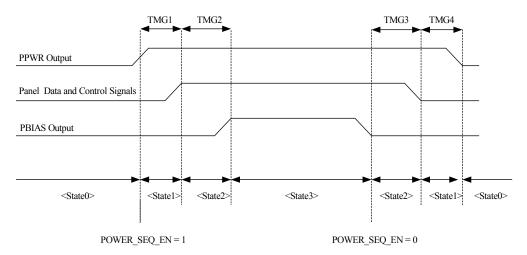

|   | 4.8.3 | Panel Power Sequencing (PPWR, PBIAS)               | 37 |

|   | 4.8.4 | Output Dithering                                   | 38 |

|   | 4.9   | Four Channel LVDS Transmitter (for gmZAN3L Only)   | 38 |

|   | 4.10  | Flexible TTL Outputs (gmZAN3T Only)                | 39 |

|   | 4.11  | Energy Spectrum Management (ESM)                   | 39 |

|   | 4.12  | OSD                                                | 39 |

|   | 4.12  | .1 On-Chip OSD SRAM                                | 40 |

|   | 4.12  | .2 Color Look-up Table (LUT)                       | 41 |

|   | 4.13  | General Purpose Inputs and Outputs (GPIO's)        | 41 |

|   | 4.14  | Bootstrap Configuration Pins                       | 41 |

|   | 4.15  | Host Interface                                     | 41 |

|   | 4.15  | .1 Host Interface Command Format – for 2 or 6-wire | 42 |

|   | 4.15  | 2 2-wire Serial Protocol                           | 42 |

|   | 4.15  | .3 8-bit Parallel Interface                        | 44 |

|   | 4.16  | Miscellaneous Functions                            | 45 |

|   | 4.16  | 1 Low Power State                                  | 45 |

|   | 4.16  | Pulse Width Modulation (PWM) Back Light Control    | 45 |

| 5 | Elec  | trical Specifications                              | 46 |

|   | 5.1   | Preliminary DC Characteristics                     | 46 |

|   | 5.2   | Preliminary AC Characteristics                     | 49 |

| ) | Orde  | ering Information                                  | 52 |

| 7 | Mec   | hanical Specifications                             | 53 |

## List Of\_Tables

| Table 1.  | Analog Input Port (Common to gmZAN3T and gmZAN3L)                             | 12     |

|-----------|-------------------------------------------------------------------------------|--------|

| Table 2.  | Clock Pins (Common to gmZAN3T and gmZAN3L)                                    | 12     |

| Table 3.  | System Interface and GPIO Signals (gmZAN3T)                                   | 13     |

| Table 4.  | System Interface and GPIO Signals (gmZAN3L)                                   | 14     |

| Table 5.  | Display Output Port for (gmZAN3L)                                             | 15     |

| Table 6.  | Display Output Port for (gmZAN3T)                                             | 16     |

| Table 7.  | Reserved Pins for gmZAN3L                                                     | 17     |

| Table 8.  | Reserve Pins for gmZAN3T                                                      | 17     |

| Table 9.  | I/O Power and Ground Pins for gmZAN3L                                         | 17     |

| Table 10. | Power and Ground Pins for LVDS Transmitter for gmZAN3L                        | 18     |

| Table 11. | I/O Power and Ground pins for gmZAN3T                                         | 18     |

| Table 12. | TCLK Specification                                                            | 22     |

| Table 13. | Temperature and Voltage variations for TRESETn                                | 26     |

| Table 14. | Pin Connection for RGB Input with HSYNC/VSYNC                                 | 26     |

| Table 15. | ADC Characteristics                                                           | 28     |

| Table 16. | Temperature and Voltage Variation for Schmitt Trigger                         | 30     |

| Table 17. | Supported LVDS 24-bit Panel Data Mappings                                     | 39     |

| Table 18. | Supported LVDS 18-bit Panel Data Mapping                                      | 39     |

| Table 19. | Bootstrap Signals                                                             | 41     |

| Table 20. | Instruction Byte Map                                                          | 42     |

| Table 21. | Absolute Maximum Ratings                                                      | 46     |

| Table 22. | gmZAN3L DC Characteristics                                                    | 47     |

| Table 23. | gmZAN3T DC Characteristics                                                    | 48     |

| Table 24. | Maximum Speed of Operation                                                    | 49     |

| Table 25. | Display Timing and DCLK Adjustments                                           | 49     |

| Table 26. | 2-Wire Host Interface Port Timing                                             | 49     |

| Table 27. | Microcontroller Interface Timing (Muxed Address/Data) for Register Read/Write | 50     |

| Table 28  | Microcontroller Interface Timing (Muyed Address/Data) for OSD Memory Read/W   | rite51 |

## **List Of Figures**

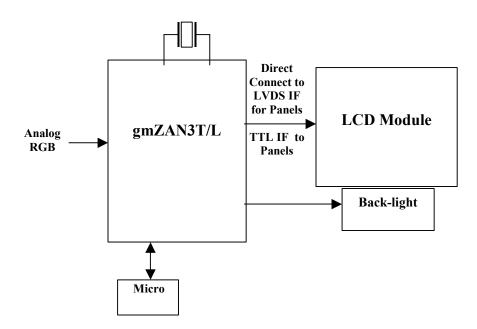

| Figure 1.  | gmZAN3 System Design Examples                       | 8  |

|------------|-----------------------------------------------------|----|

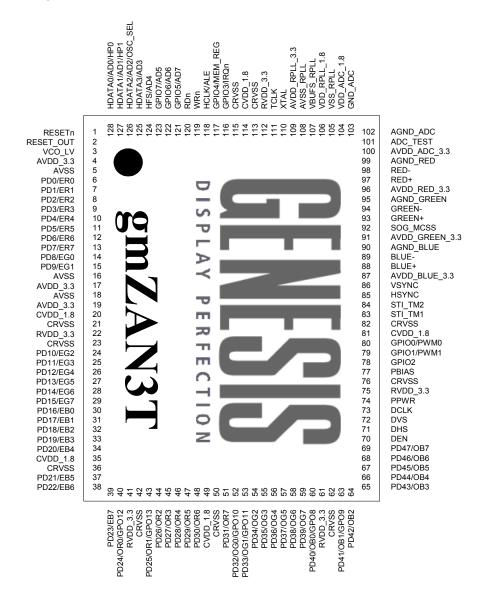

| Figure 2.  | gmZAN3T Pin Out Diagram                             | 10 |

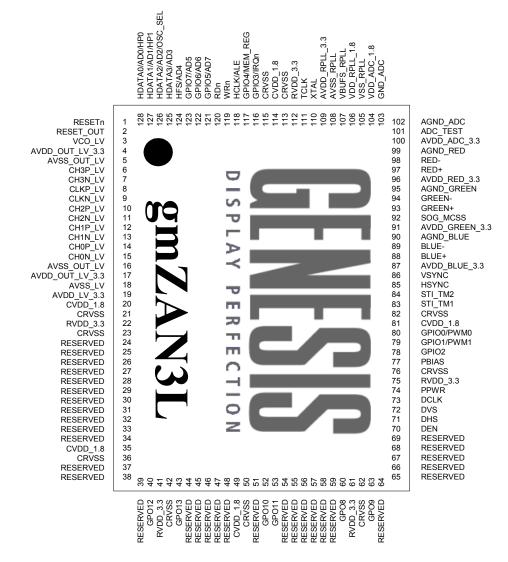

| Figure 3.  | gmZAN3L Pin out Diagram                             | 11 |

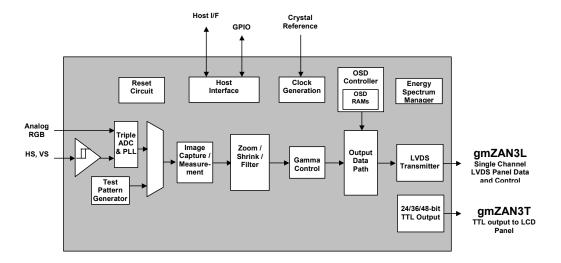

| Figure 4.  | gmZAN3 Functional Block Diagram                     | 19 |

| Figure 5.  | Using the Internal Oscillator with External Crystal | 20 |

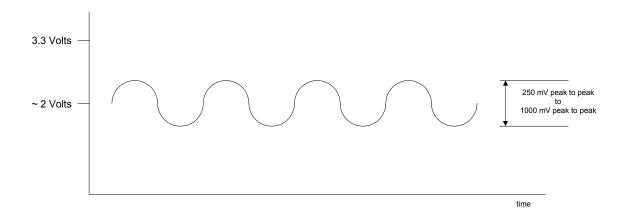

| Figure 6.  | Internal Oscillator Output                          | 21 |

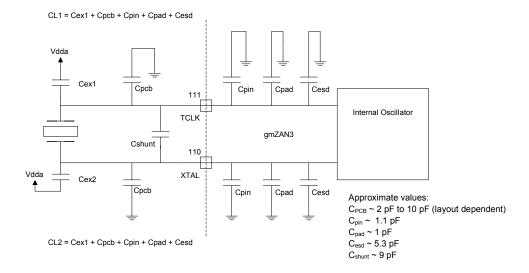

| Figure 7.  | Sources of Parasitic Capacitance                    | 22 |

| Figure 8.  | Using an External Single-ended Clock Oscillator     | 22 |

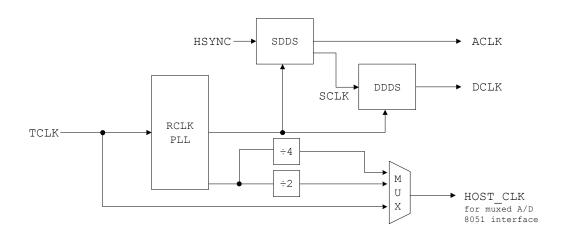

| Figure 9.  | Internally Synthesized Clocks                       | 23 |

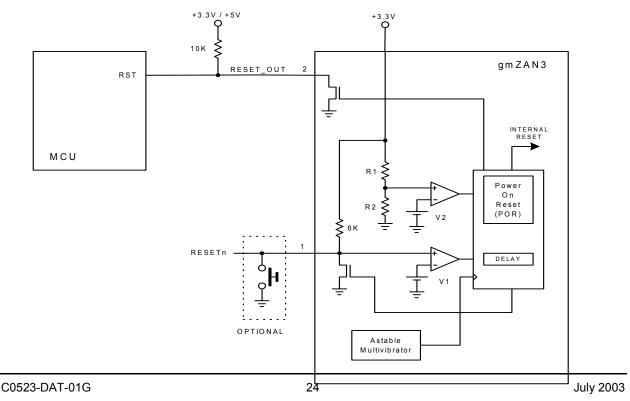

| Figure 10. | gmZAN3 Re-setting External MCU                      | 25 |

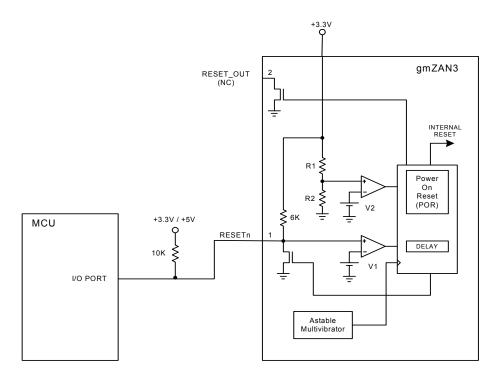

| Figure 11. | External MCU Re-setting gmZAN3                      | 25 |

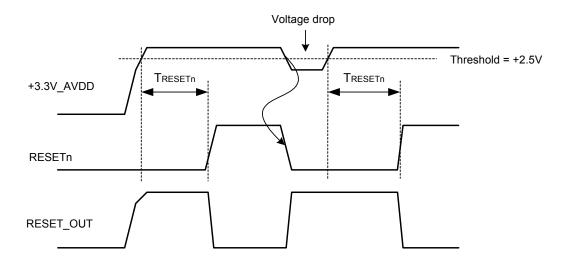

| Figure 12. | Reset Signal Timing (T <sub>RESETn</sub> )          | 25 |

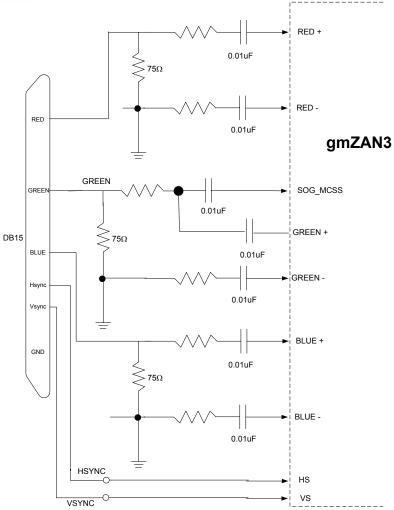

| Figure 13. | Example ADC Signal Terminations                     | 27 |

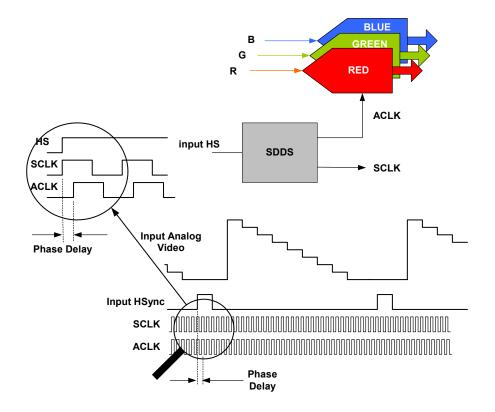

| Figure 14. | gmZAN3 Clock Recovery                               | 29 |

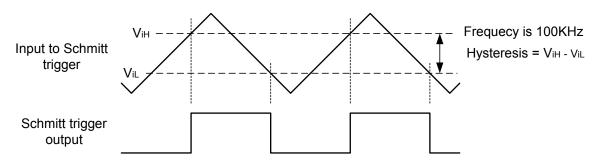

| Figure 15. | Schmitt Trigger Timing Diagram                      | 30 |

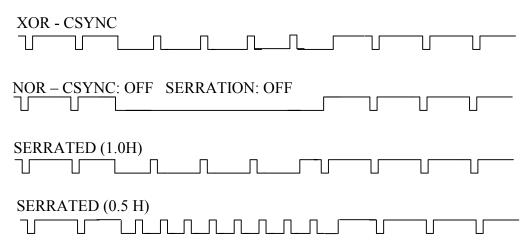

| Figure 16. | Supported SOG and CSYNC signals                     | 31 |

| Figure 17. | ADC Capture Window                                  | 32 |

| Figure 18. | Some of gmZAN3 built-in test patterns               | 32 |

| Figure 19. | Factory Calibration and Test Environment            | 33 |

| Figure 20. | ODD/EVEN Field Detection                            | 34 |

| Figure 21. | Display Windows and Timing                          | 36 |

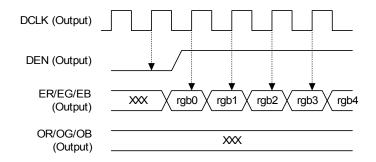

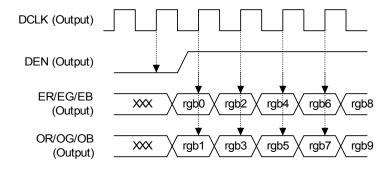

| Figure 22. | Single Pixel Width Display Data                     | 37 |

| Figure 23. | Double Pixel Wide Display Data                      | 37 |

| Figure 24. | Panel Power Sequencing                              | 38 |

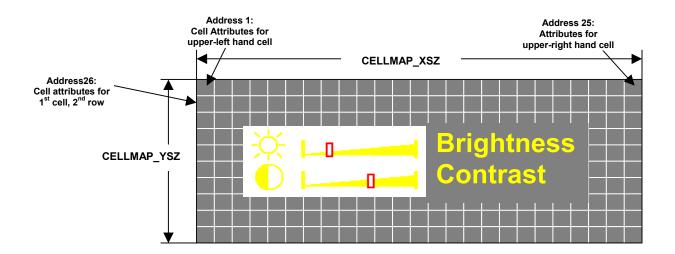

| Figure 25. | OSD Cell Map                                        | 40 |

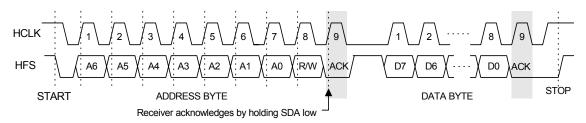

| Figure 26. | 2-Wire Protocol Data Transfer                       | 43 |

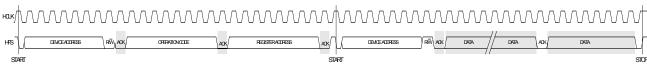

| Figure 27. | 2-Wire Write Operations (0x1x and 0x2x)             | 43 |

| Figure 28. | 2-Wire Read Operation (0x9x and 0xAx)               | 44 |

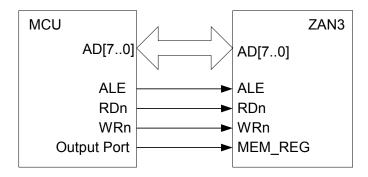

| Figure 29. | 8-bit Parallel Interface                            | 44 |

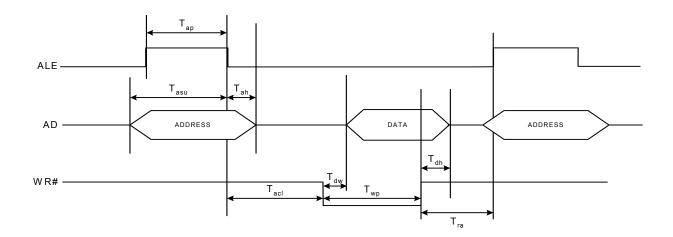

| Figure 30. | Microcontroller Register Write Cycle                | 50 |

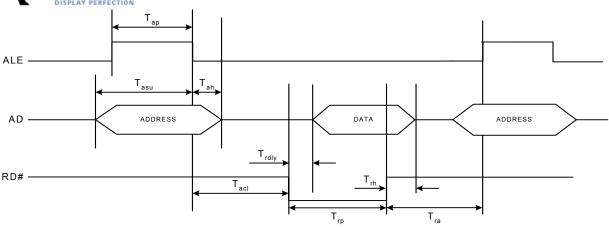

| Figure 31. | Microcontroller Register Read Cycle                 | 51 |

| Figure 32. | Microcontroller OSD CCF Write Cycle                 | 52 |

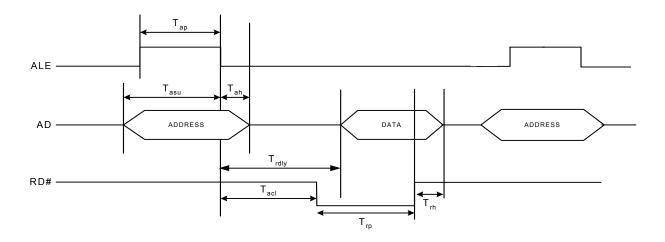

| Figure 33. | Microcontroller OSD CCF Read Cycle                  | 52 |

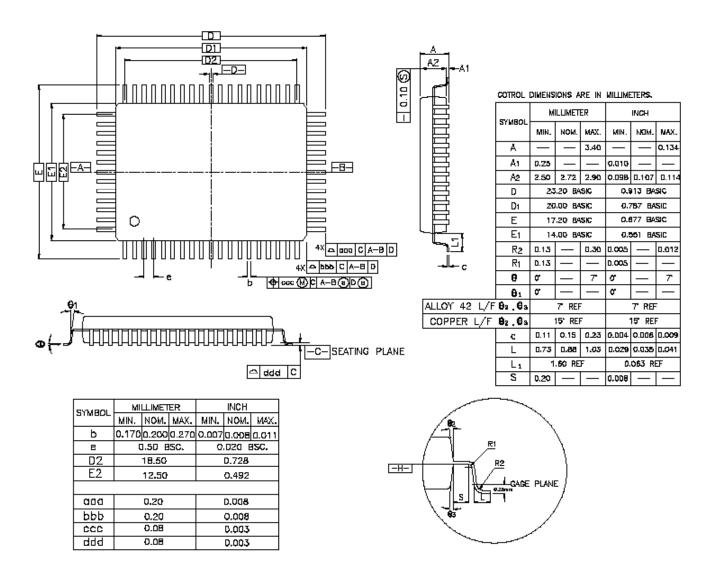

| Figure 34  | gmZAN3 128-pin POFP Mechanical Drawing              |    |

## **Revision History**

| Document      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date      |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| C0523-DAT-01A | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Feb. 2003 |

| C0523-DAT-01B | Changed the LVDS pin names to allow simple board layout. See Figure 3 and Table 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                | Feb. 2003 |

| C0523-DAT-01C | <ul> <li>Fixed typo in Table 19 V<sub>VDD_1.85</sub> &gt;&gt; V<sub>VDD_1.8</sub>.</li> <li>Updated Table 20 with correct 1.8V voltage min and max</li> <li>Updated the minimum and maximum operating conditions in Section 5.2 Preliminary AC Characteristics.</li> </ul>                                                                                                                                                                                                                                                        | Mar. 2003 |

| C0523-DAT-01D | <ul> <li>Removed Dual- edge clocking from section 4.11</li> <li>Updated Table 19 with Theta Jc and Theta Ja values</li> <li>Updated Table 20 with measured Power consumption for gmZAN3L</li> <li>Added Table 21 with gmZAN3T DC characteristics with measured Power Consumption</li> </ul>                                                                                                                                                                                                                                       | Apr. 2003 |

| C0523-DAT-01E | <ul> <li>Added information on the integrated Reset Circuit</li> <li>Figure 10 gmZAN3 Re-setting external MCU</li> <li>Figure 11 External MCU re-setting gmZAN3</li> <li>Figure 12 Reset Signal Timing</li> <li>Table 13 Temperature &amp; Voltage Variation on the Reset Circuit</li> <li>Added Section 4.3.5 on the Schimtt Trigger</li> <li>Figure 15 Schmitt Trigger Timing</li> <li>Table 16 Temperature &amp; Voltage Variation on the Schimtt Trigger</li> <li>Changed Figure 14 drawing with more clarification</li> </ul> | May 2003  |

| C0523-DAT-01F | Pin corrections (documentation error):  gmZAN3L – corrected pins: 40, 43, 52,53, 60, 63 (GPIO[8:13] to GPO[8:13])  gmZAN3T – corrected pins: 40, 43, 52, 53, 60, 63  Part Number change: removed hyphen from chip name throughout document  Updated frequency in TCLK specification table.  Corrected storage temperature in Preliminary DC Characteristics                                                                                                                                                                       | May 2003  |

| C0523-DAT-01G | Updated Table 16 Temperature and Voltage variation of the Schmitt trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                         | July 2003 |

#### 1 Overview

The gmZAN3 is a graphics processing IC for Liquid Crystal Display (LCD) monitors at XGA resolution. It provides all key IC functions required for the highest quality LCD monitors. On-chip functions include a high-speed triple-ADC and PLL, a high quality zoom and shrink scaling engine, an on-screen display (OSD) controller and digital color controls.

The gmZAN3 is provided with two versions;

- gmZAN3T with 48-bit TTL output and

- gmZAN3L with industry standard single four channel LVDS transmitter for direct connect to LCD panels with LVDS interface.

With this level of integration, the gmZAN3 devices simplify and reduce the cost of LCD monitors while maintaining a high-degree of flexibility and quality.

#### 1.1 gmZAN3 System Design Examples

Figure 1 below shows a typical analog interface LCD monitor system based on the gmZAN3. The gmZAN3 reduces system cost, simplifies hardware and firmware design and increased reliability because only a minimal number of components are required in the system.

Figure 1. gmZAN3 System Design Examples

#### 1.2 gmZAN3 Features

#### **FEATURE OVERVIEW**

- Zoom (from VGA) and shrink (from SXGA) scaling

- Integrated 8-bit triple-channel ADC / PLL

- Csync and SOG support

- On-chip versatile OSD engine

- All system clocks synthesized from a single external crystal

- On-chip reset circuit

- Programmable gamma correction (CLUT)

- PWM back light intensity control

- 5-Volt tolerant inputs up to 13 GPIO pins

- Low EMI and power saving features

#### **High-Quality Advanced Scaling**

- Fully programmable zoom ratios

- Shrink capability from SXGA resolution

- Real Recovery<sup>™</sup> function provides full color recovery image for refresh rates higher than those supported by the LCD panel

#### **Analog RGB Input Port**

- Supports up to SXGA input

- On-chip high-performance PLLs (only a single reference crystal required)

#### **Auto-Configuration / Auto-Detection**

- Automatic input format detection

- Robust phase and image positioning

#### **On-Chip OSD Controller**

- On-chip RAM for downloadable menus

- 1 and 2-bit per pixel character cells

- Horizontal and vertical stretch of OSD menus

- Blinking and transparency

- Proportional font support

- 90 degree rotation of fonts for Portrait Display support

#### **Built in Test Pattern Generator**

Simplifies manufacturing and testing

#### Highly Integrated Solution to Provide Low System Cost

- Two layer PCB support

- On-chip reset feature to eliminate external reset component

- Output slew rate control

- Integrated Schmitt trigger for Vsync and Hsync

#### **OUTPUT INTERFACE**

#### gmZAN3T

- Support for 8 or 6-bit panels (with high-quality dithering)

- Swap red and green channels

- Ability to reverse bit order of each R, G, B output

- Single or double pixel clock

- Support up to XGA 85Hz

## Built in Flexible LVDS Transmitter for gmZAN3L

- Four channel 6/8-bit LVDS transmitter (with high-quality dithering)

- Programmable channel swapping and polarity

- Support up to XGA 85Hz output

#### **PACKAGE**

• 128-pin PQFP

## 2 gmZAN3 Pinout

These devices are available in a 128-pin Plastic Quad Flat Pack (PQFP) package. Figure 2 provides the pin locations for all signals.

Figure 2. gmZAN3T Pin Out Diagram

Figure 3. gmZAN3L Pin out Diagram

## 3 gmZAN3 Pin List

I/O Legend: A = Analog, I = Input, O = Output, P = Power, G = Ground, I-PU = Input with pull-up, I-PD = Input with pull down, IO-PD = Bidirectional with pull down

Table 1. Analog Input Port (Common to gmZAN3T and gmZAN3L)

| Pin Name       | No. | I/O | Description                                                                                                                                                                                                                                                               |

|----------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDD_RED_3.3   | 96  | AP  | Analog power (3.3V) for the red channel. Must be bypassed with decoupling capacitor (0.1μF) to AGND_RED pin on system board (as close as possible to the pin).                                                                                                            |

| RED+           | 97  | Al  | Positive analog input for Red channel.                                                                                                                                                                                                                                    |

| RED-           | 98  | Al  | Negative analog input for Red channel.                                                                                                                                                                                                                                    |

| AGND_RED       | 99  | AG  | Analog ground for the red channel.  Must be directly connected to the system ground plane.                                                                                                                                                                                |

| AVDD_GREEN_3.3 | 91  | AP  | Analog power (3.3V) for the green channel. Must be bypassed with decoupling capacitor (0.1µF) to AGND_GREEN pin on system board (as close as possible to the pin).                                                                                                        |

| SOG_MCSS       | 92  | Al  | Dedicated Sync-on-Green pin                                                                                                                                                                                                                                               |

| GREEN+         | 93  | Al  | Positive analog input for Green channel.                                                                                                                                                                                                                                  |

| GREEN-         | 94  | Al  | Negative analog input for Green channel.                                                                                                                                                                                                                                  |

| AGND_GREEN     | 95  | AG  | Analog ground for the green channel.  Must be directly connected to the system ground plane.                                                                                                                                                                              |

| AVDD_BLUE_3.3  | 87  | AP  | Analog power (3.3V) for the blue channel. Must be bypassed with decoupling capacitor (0.1µF) to AGND_BLUE pin on system board (as close as possible to the pin).                                                                                                          |

| BLUE+          | 88  | Al  | Positive analog input for Blue channel.                                                                                                                                                                                                                                   |

| BLUE-          | 89  | Al  | Negative analog input for Blue channel.                                                                                                                                                                                                                                   |

| AGND_BLUE      | 90  | AG  | Analog ground for the blue channel.  Must be directly connected to the system ground plane.                                                                                                                                                                               |

| AVDD_ADC_3.3   | 100 | AP  | Analog power (3.3V) for ADC analog blocks that are shared by all three channels. Includes band gap reference, master biasing and full-scale adjust. Must be bypassed with decoupling capacitor (0.1µF) to AGND_ADC pin on system board (as close as possible to the pin). |

| ADC_TEST       | 101 | AO  | Analog test output for ADC. Do not connect.                                                                                                                                                                                                                               |

| AGND_ADC       | 102 | AG  | Analog ground for ADC analog blocks that are shared by all three channels. Includes band gap reference, master biasing and full-scale adjust.  Must be directly connected to system ground plane.                                                                         |

| GND_ADC        | 103 | AG  | Digital ground for ADC clocking circuit.  Must be directly connected to system ground plane.                                                                                                                                                                              |

| VDD_ADC_1.8    | 104 | Р   | Digital power (1.8V) for ADC encoding logic. Must be bypassed with decoupling capacitor (0.1µF) to GND_ADC pin on system board (as close as possible to the pin).                                                                                                         |

| HSYNC          | 85  | I   | ADC input horizontal sync input. The input hysteresis can be set to 0.5V or 1.5V [Input, Schmitt trigger, 5V-tolerant]                                                                                                                                                    |

| VSYNC          | 86  | I   | ADC input vertical sync input. The input hysteresis can be set to 0.5V or 1.5V [Input, Schmitt triggered, 5V-tolerant]                                                                                                                                                    |

#### Table 2. Clock Pins (Common to gmZAN3T and gmZAN3L)

| Pin Name      | No  | I/O | Description                                                                                                                                                                              |

|---------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK          | 111 | Al  | Reference clock (TCLK) from the 14.3MHz crystal oscillator (see Figure 5), or from single-<br>ended CMOS/TTL clock oscillator (see Figure 8). This is a 5V-tolerant input. See Table 14. |

| XTAL          | 110 | AO  | Crystal oscillator output.                                                                                                                                                               |

| VBUFS_RPLL    | 107 | AO  | Reserved. For test purposes only. Do not connect                                                                                                                                         |

| AVSS_RPLL     | 108 | G   | Analog ground for the reference DDS PLL. Must be directly connected to the system ground plane.                                                                                          |

| VSS_RPLL      | 105 | G   | Digital ground for the RCLK and clock generator. Must be directly connected to the system ground plane.                                                                                  |

| VDD_RPLL_1.8  | 106 | Р   | Digital power for the RCLK and clock generators. Connect to 1.8V supply. Must be bypassed with a 0.1µFcapacitor to pin AVSS_RPLL                                                         |

| AVDD_RPLL_3.3 | 109 | Р   | Analog power for the reference DDS PLL. Connect to 3.3V supply. Must be bypassed with a 0.1µFcapacitor to pin VSS_RPLL                                                                   |

#### Table 3. System Interface and GPIO Signals (gmZAN3T)

| _                                |            | - , . | <b></b>                                                                                                                                                                                                                                                                                          |

|----------------------------------|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                         | No         | I/O   | Description                                                                                                                                                                                                                                                                                      |

| RESETn                           | 1          | Ю     | Active-low hardware reset signal. The reset signal is held low for at least 150ms on the chip power up. It has an internal 60KΩl pull-up resistor which can be used for re-setting other system devices. See section 4.2 [Bi-directional (open drain), 5V-tolerant]                              |

| RESET_OUT                        | 2          | 0     | Active-high hardware reset signal. The reset signal is held high for at least 150ms on the chip power up. It can be used for re-setting other system devices[Output, open-drain 5V-tolerant]                                                                                                     |

| GPIO0/PWM0                       | 80         | Ю     | General-purpose input/output signal or PWM0. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                  |

| GPIO1/PWM1                       | 79         | Ю     | General-purpose input/output signal or PWM1. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                  |

| GPIO2                            | 78         | Ю     | General-purpose input/output signal. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                          |

| GPIO3/IRQn                       | 116        | Ю     | General-purpose input/output signal. This is also active-low interrupt input external micro-controller.  [Bi-directional, Active low open drain, 5V-tolerant]                                                                                                                                    |

| GPIO4/MEM_REG                    | 117        | IO-PD | General-purpose input/output signal. Open drain option via register setting. For 8-bit A/D host interface, this selects between OSD memory (high) and register access (low). [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]                  |

| GPIO5/AD7                        | 121        | Ю     | General-purpose input/output signal or Adddress/data[7] for 8-bit A/D host interface. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                         |

| GPIO6/AD6                        | 122        | Ю     | General-purpose input/output signal or Adddress/data[6] for 8-bit A/D host interface.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                 |

| GPIO7/AD5                        | 123        | Ю     | General-purpose input/output signal or Adddress/data[5] for 8-bit A/D host interface.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                                 |

| GPO8/PD40/OB0                    | 60         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Blue0.                                                                                                                                                                                                                           |

| GPO9/PD41/OB1                    | 63         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Blue1.                                                                                                                                                                                                                           |

| GPO10/PD32/OG0                   | 52         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Green0.                                                                                                                                                                                                                          |

| GPO11/PD33/OG1                   | 53         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Green1.                                                                                                                                                                                                                          |

| GPO12/PD24/OR0                   | 40         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Red0.                                                                                                                                                                                                                            |

| GPO13/PD25/OR1                   | 43         | 0     | General-purpose output signal. GPO or TTL 48-bit panel data/Odd Red1.                                                                                                                                                                                                                            |

| HDATA0/ADO/HP0<br>HDATA1/AD1/HP1 | 128<br>127 | IO-PD | Host data for 6-wire serial protocol.  For 8-bit A/D host interface determines A/D0 and A/D1 bit.  Note: See Table 19, Boostrap Signals  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-                                                           |

| HDATA2/AD2/OSC_SEL               | 126        | IO-PD | down]  If using 6-wire protocol the HDATA[2] determines bit 2 of the host data. For 8-bit A/D host interface determines A/D2 bit.  Note: See Table 19, Boostrap Signals  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]                      |

| HDATA3/AD3                       | 125        | IO-PD | If using 6-wire protocol the HDATA[3] determines the upper A/D3 bits of the host data. For 8-bit A/D host interface determines address/data bit.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]                                             |

| HFS/AD4                          | 124        | Ю     | Host Frame Sync. Frames the packet on the serial channel 6-wire interface. For 8-bit A/D host interface determines A/D4 bit.                                                                                                                                                                     |

| HCLK/ALE                         | 118        | I     | [Bi-directional, Schmitt trigger (400mV typical hysteresis), slew rate limited, 5V-tolerant]  Clock signal input for the 6-wire interface and 2-wire modes.  For 8-bit A/D host interface it becomes the Address Latch Enable.  [Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant] |

| WRn                              | 119        | I-PU  | For 8-bit A/D host interface write strobe input. Internal 60KΩ pull-up.                                                                                                                                                                                                                          |

| RDn                              | 120        | I-PU  | For 8-bit A/D host interface read strobe input. Internal 60KΩ pull-up                                                                                                                                                                                                                            |

|                                  |            |       |                                                                                                                                                                                                                                                                                                  |

#### Table 4. System Interface and GPIO Signals (gmZAN3L)

| Pin Name                         | No         | I/O   | Description                                                                                                                                                                                                                                                                     |

|----------------------------------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETn                           | 1          | Ю     | Active-low hardware reset signal. The reset signal is held low for at least 150ms on the chip power up. It has an internal 60KΩl pull-up resistor which can be used for re-setting other system devices. See section 4.2 [Bi-directional (open drain), 5V-tolerant]             |

| RESET_OUT                        | 2          | 0     | Active-high hardware reset signal. The reset signal is held high for at least 150ms on the chip power up. It can be used for re-setting other system devices[Output, 5V-tolerant]                                                                                               |

| GPIO0/PWM0                       | 80         | Ю     | General-purpose input/output signal or PWM0. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                 |

| GPIO1/PWM1                       | 79         | Ю     | General-purpose input/output signal or PWM1. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                 |

| GPIO2                            | 78         | Ю     | General-purpose input/output signal. Open drain option via register setting. [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                          |

| GPIO3/IRQn                       | 116        | Ю     | General-purpose input/output signal. This is also active-low interrupt input external micro-controller.  [Bi-directional, Active low open drain, 5V-tolerant]                                                                                                                   |

| GPIO4/MEM_REG                    | 117        | IO-PD | General-purpose input/output signal. Open drain option via register setting. For 8-bit A/D host interface, this selects between OSD memory (high) and register access (low). [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down] |

| GPIO5/AD7                        | 121        | Ю     | General-purpose input/output signal or Adddress/data[7] for 8-bit A/D host interface. Open drain option via register setting.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                        |

| GPIO6/AD6                        | 122        | Ю     | General-purpose input/output signal or Adddress/data[6] for 8-bit ADD host interface.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                |

| GPIO7/AD5                        | 123        | Ю     | General-purpose input/output signal or Adddress/data[5] for 8-bit A/D host interface.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                                                                |

| GPO8                             | 60         | 0     | General-purpose output signal.                                                                                                                                                                                                                                                  |

| GPO9                             | 63         | 0     | General-purpose output signal.                                                                                                                                                                                                                                                  |

| GPO10                            | 52         | 0     | General-purpose output.                                                                                                                                                                                                                                                         |

| GPO11                            | 53         | 0     | General-purpose output signal.                                                                                                                                                                                                                                                  |

| GPO12                            | 40         | 0     | General-purpose output signal.                                                                                                                                                                                                                                                  |

| GPO13                            | 43         | 0     | General-purpose output signal.                                                                                                                                                                                                                                                  |

| HDATA0/ADO/HP0<br>HDATA1/AD1/HP1 | 128<br>127 | IO-PD | Host data for 6-wire serial protocol. For 8-bit A/D host interface determines AD0 and AD1 bit. Note: See Table 19, Boostrap Signals [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]                                          |

| HDATA2/AD2/OSC_SEL               | 126        | IO-PD | If using 6-wire protocol the HDATA[2] determines bit 2 of the host data. For 8-bit A/D host interface determines AD2 bit.  Note: See Table 19, Boostrap Signals [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]              |

| HDATA3/AD3                       | 125        | IO-PD | If using 6-wire protocol the HDATA[3] determines the upper AD3 bits of the host data. For 8-bit A/D host interface determines address/data bit. [Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60KΩ pull-down]                              |

| HFS/AD4                          | 124        | Ю     | Host Frame Sync. Frames the packet on the serial channel 6-wire interface. For 8-bit A/D host interface determines AD4 bit.  [Bi-directional, Schmitt trigger (400mV typical hysteresis), slew rate limited, 5V-tolerant]                                                       |

| HCLK/ALE                         | 118        | I     | Clock signal input for the 6-wire interface and 2-wire modes.  For 8-bit A/D host interface it becomes the Address Latch Enable.  [Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]                                                                              |

| WRn                              | 119        | I-PU  | For 8-bit A/D host interface write strobe input. Internal 60KΩ pull-up.                                                                                                                                                                                                         |

| RDn                              | 120        | I-PU  | For 8-bit A/D host interface read strobe input. Internal 60KΩ pull-up.                                                                                                                                                                                                          |

#### Table 5. Display Output Port for (gmZAN3L)

|          |    |     | , , ,                                                                                                                                        |

|----------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | No | I/O | Description                                                                                                                                  |

| DCLK     | 73 | 0   | Not required. Panel output clock. Can be used for test purposes [Tri-state output, Programmable Drive]                                       |

| DVS      | 72 | 0   | Not required. Panel Vertical Sync. Can be used for test purposes [Tri-state output, Programmable Drive]                                      |

| DHS      | 71 | 0   | Not required. Panel Horizontal Sync. Can be used for test purposes [Tri-state output, Programmable Drive]                                    |

| DEN      | 70 | 0   | Not required. Panel Display Enable, which frames the output background. Can be used for test purposes [Tri-state output, Programmable Drive] |

| PBIAS    | 77 | 0   | Panel Bias Control (back light enable)                                                                                                       |

| PPWR     | 74 | 0   | Panel Power Control                                                                                                                          |

| CH3P_LV  | 6  | 0   | LVDS Channel 3 positive <sup>1</sup>                                                                                                         |

| CH3N_LV  | 7  | 0   | LVDS Channel 3 negative <sup>1</sup>                                                                                                         |

| CLKP_LV  | 8  | 0   | LVDS Clock positive <sup>1</sup>                                                                                                             |

| CLKN_LV  | 9  | 0   | LVDS Clock negative <sup>1</sup>                                                                                                             |

| CH2P_LV  | 10 | 0   | LVDS Channel 2 positive <sup>1</sup>                                                                                                         |

| CH2N_LV  | 11 | 0   | LVDS Channel 2 negative <sup>1</sup>                                                                                                         |

| CH1P_LV  | 12 | 0   | LVDS Channel 1 positive <sup>1</sup>                                                                                                         |

| CH1N_LV  | 13 | 0   | LVDS Channel 1 negative <sup>1</sup>                                                                                                         |

| CH0P_LV  | 14 | 0   | LVDS Channel 0 positive <sup>1</sup>                                                                                                         |

| CH0N_LV  | 15 | 0   | LVDS Channel 0 negative <sup>1</sup>                                                                                                         |

Note: <sup>1</sup>These pin names are based on having swapping enabled on the initial positive and negative LVDS signals.

#### Table 6. Display Output Port for (gmZAN3T)

|                      |          | Tab | e 6. Display Output Fort for (gillzAN31)                                                                                                                           |

|----------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | No       | I/O | Description                                                                                                                                                        |

| DCLK                 | 73       | 0   | Panel output clock. [Tri-state output, Programmable Drive]                                                                                                         |

| DVS                  | 72       | 0   | Panel Vertical Sync.                                                                                                                                               |

| DHS                  | 71       | 0   | [Tri-state output, Programmable Drive] Panel Horizontal Sync.                                                                                                      |

| DEN                  | 70       | 0   | [Tri-state output, Programmable Drive]                                                                                                                             |

| DEN                  | 70       | U   | Panel Display Enable, which frames the output background. [Tri-state output, Programmable Drive]                                                                   |

| PBIAS                | 77       | 0   | Panel Bias Control (back light enable)                                                                                                                             |

| PPWR<br>PD47/OB7     | 74<br>69 | 0   | Panel Power Control                                                                                                                                                |

|                      |          |     | Panel output data or Odd Blue 7 data bit. [Tri-state output, Programmable Drive]  Panel output data or Odd Blue 6 data bit. [Tri-state output, Programmable Drive] |

| PD46/OB6<br>PD45/OB5 | 68<br>67 | 0   | Panel output data or Odd Blue 5 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD44/OB4             | 66       | 0   | Panel output data or Odd Blue 4 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD43/OB3             | 65       | 0   | Panel output data or Odd Blue 3 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD42/OB2             | 64       | 0   | Panel output data or Odd Blue 2 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD41/OB1/GPO9        | 63       | 0   | Panel output data or Odd Blue 1 data bit. [Tri-state output, Programmable Drive] When used                                                                         |

|                      |          |     | with 6-bit panels can be used as GPO.                                                                                                                              |

| PD40/OB0/GPO8        | 60       | 0   | Panel output data or Odd Blue 0 data bit. [Tri-state output, Programmable Drive] When used with 6-bit panels can be used as GPO.                                   |

| PD39/OG7             | 59       | 0   | Panel output data or Odd Green 7 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD38/OG6             | 58       | 0   | Panel output data or Odd Green 6 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD37/OG5             | 57       | 0   | Panel output data or Odd Green 5 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD36/OG4             | 56       | 0   | Panel output data or Odd Green 4 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD35/OG3             | 55       | 0   | Panel output data or Odd Green 3 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD34/OG2             | 54       | 0   | Panel output data or Odd Green 2 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD33/OG1/GPO11       | 53       | 0   | Panel output data or Odd Green 1 data bit. [Tri-state output, Programmable Drive] When used with 6-bit panels can be used as GPO.                                  |

| PD32/OG0/GPO10       | 52       | 0   | Panel output data or Odd Green 0 data bit. [Tri-state output, Programmable Drive] When used with 6-bit panels can be used as GPO.                                  |

| PD31/OR7             | 51       | 0   | Panel output data or Odd Red 7 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD30/OR6             | 48       | 0   | Panel output data or Odd Red 6 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD29/OR5             | 47       | 0   | Panel output data or Odd Red 5 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD28/OR4             | 46       | 0   | Panel output data or Odd Red 4 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD27/OR3             | 45       | 0   | Panel output data or Odd Red 3 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD26/OR2             | 44       | 0   | Panel output data or Odd Red 2 data bit. [Tri-state output, Programmable Drive]                                                                                    |

| PD25/OR1/GPO13       | 43       | 0   | Panel output data or Odd Red 1 data bit. [Tri-state output, Programmable Drive] When used with 6-bit panels can be used as GPO.                                    |

| PD24/OR0/GPO12       | 40       | 0   | Panel output data or Odd Red 0 data bit. [Tri-state output, Programmable Drive] When used with 6-bit panels can be used as GPO.                                    |

| PD23/EB7             | 39       | 0   | Panel output data or Even Blue 7 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD22/EB6             | 38       | 0   | Panel output data or Even Blue 6 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD21/EB5             | 37       | 0   | Panel output data or Even Blue 5 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD20/EB4             | 34       | 0   | Panel output data or Even Blue 4 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD19/EB3             | 33       | 0   | Panel output data or Even Blue 3 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD18/EB2             | 32       | 0   | Panel output data or Even Blue 2 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD17/EB1             | 31       | 0   | Panel output data or Even Blue 1 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD16/EB0             | 30       | 0   | Panel output data or Even Blue 0 data bit. [Tri-state output, Programmable Drive]                                                                                  |

| PD15/EG7             | 29       | 0   | Panel output data or Even Green 7 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD14/EG6             | 28       | 0   | Panel output data or Even Green 6 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD13/EG5             | 27       | 0   | Panel output data or Even Green 5 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD12/EG4             | 26       | 0   | Panel output data or Even Green 4 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD11/EG3             | 25       | 0   | Panel output data or Even Green 3 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD10/EG2             | 24       | 0   | Panel output data or Even Green 2 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD9/EG1              | 15       | 0   | Panel output data or Even Green 1 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD8/EG0              | 14       | 0   | Panel output data or Even Green 0 data bit. [Tri-state output, Programmable Drive]                                                                                 |

| PD7/ER7              | 13       | 0   | Panel output data or Even Red 7 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD6/ER6              | 12       | 0   | Panel output data or Even Red 6 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD5/ER5              | 11       | 0   | Panel output data or Even Red 5 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD4/ER4              | 10       | 0   | Panel output data or Even Red 4 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD3/ER3              | 9        | 0   | Panel output data or Even Red 3 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| PD2/ER2              | 8        | 0   | Panel output data or Even Red 2 data bit. [Tri-state output, Programmable Drive]                                                                                   |

| Pin Name | No | I/O | Description                                                                      |

|----------|----|-----|----------------------------------------------------------------------------------|

| PD1/ER1  | 7  | 0   | Panel output data or Even Red 1 data bit. [Tri-state output, Programmable Drive] |

| PD0/ER0  | 6  | 0   | Panel output data or Even Red 0 data bit. [Tri-state output, Programmable Drive] |

#### Table 7. Reserved Pins for gmZAN3L

| Pin Name | No | I/O | Description                                                                                           |  |  |  |

|----------|----|-----|-------------------------------------------------------------------------------------------------------|--|--|--|

| Reserved | 69 | 0   | Do not connect                                                                                        |  |  |  |

| Reserved | 68 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 67 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 66 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 65 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 64 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 59 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 58 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 57 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 56 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 55 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 54 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 51 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 48 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 47 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 46 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 45 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 44 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 39 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 38 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 37 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 34 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 33 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 32 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 31 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 30 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 29 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 28 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 27 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 26 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 25 | 0   | Do not connect.                                                                                       |  |  |  |

| Reserved | 24 | 0   | Do not connect.                                                                                       |  |  |  |

| VC0_LV   | 3  | 0   | For test purposes only. Do not connect                                                                |  |  |  |

| STI_TM1  | 83 | I   | For test purposes only. Has internal $60K\Omega$ pull-down register. Must be connected to GND         |  |  |  |

| STI_TM2  | 84 | I   | For test purposes only. Has internal $60 \text{K}\Omega$ pull-down register. Must be connected to GND |  |  |  |

#### Table 8. Reserve Pins for gmZAN3T

| Pin Name | No | I/O  | Description                                                   |

|----------|----|------|---------------------------------------------------------------|

| VCO_LV   | 3  | 0    | For test purposes only. Do not connect                        |

| STI_TM1  | 83 | I-PD | For test purposes only. Has internal 60KΩ pull-down resistor. |

| STI_TM2  | 84 | I-PD | For test purposes only. Has internal 60KΩ pull-down resistor. |

#### Table 9. I/O Power and Ground Pins for gmZAN3L

| Pin Name | No  | I/O | Description                                                                         |

|----------|-----|-----|-------------------------------------------------------------------------------------|

| RVDD_3.3 | 22  | Р   | Connect to 3.3V digital supply.                                                     |

|          | 41  | Р   | Must be bypassed with a 0.1µF capacitor to CRVSS (as close to the pin as possible). |

|          | 61  | Р   |                                                                                     |

|          | 75  | Р   |                                                                                     |

|          | 112 | Р   |                                                                                     |

| CRVSS    | 21  | G   | Connect to digital ground.                                                          |

|          | 23  | G   |                                                                                     |

|          | 36  | G   |                                                                                     |

| DISPLAT PERI | Lemon |   |                                                                                     |

|--------------|-------|---|-------------------------------------------------------------------------------------|

|              | 42    | G |                                                                                     |

|              | 50    | G |                                                                                     |

|              | 62    | G |                                                                                     |

|              | 76    | G |                                                                                     |

|              | 82    | G |                                                                                     |

|              | 113   | G |                                                                                     |

|              | 115   | G |                                                                                     |

| CVDD_1.8     | 20    | Р | Connect to 1.8V digital supply.                                                     |

|              | 35    | Р | Must be bypassed with a 0.1µF capacitor to CRVSS (as close to the pin as possible). |

|              | 49    | Р |                                                                                     |

|              | 81    | Р |                                                                                     |

|              | 114   | Р |                                                                                     |

Table 10. Power and Ground Pins for LVDS Transmitter for gmZAN3L

| Pin Name        | No      | I/O | Description                                                                                                                    |

|-----------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| AVDD_OUT_LV_3.3 | 4<br>17 | AP  | Analog power for on-chip LVDS output buffer. Connect to 3.3V supply. Must be bypassed with a 0.1µFcapacitor to pin AVSS_OUT_LV |

| AVDD_LV_3.3     | 19      | AP  | Analog power for on-chip LVDS PLL. Connect to 3.3V supply. Must be bypassed with a 0.1µFcapacitor to pin AVSS_LV               |

| AVSS_OUT_LV     | 5<br>16 | G   | Analog ground for on-chip LVDS output buffer.  Must be directly connected to the system ground plane                           |

| AVSS_LV         | 18      | G   | Analog ground for on-chip LVDS PLL.  Must be directly connected to the system ground plane                                     |

Table 11. I/O Power and Ground pins for gmZAN3T

| Pin Name | No  | I/O | Description                                                                         |

|----------|-----|-----|-------------------------------------------------------------------------------------|

| RVDD_3.3 | 22  | Р   | Connect to 3.3V digital supply.                                                     |

|          | 41  | Р   | Must be bypassed with a 0.1µF capacitor to CRVSS (as close to the pin as possible). |

|          | 61  | Р   |                                                                                     |

|          | 75  | Р   |                                                                                     |

|          | 112 | Р   |                                                                                     |

| CRVSS    | 21  | G   | Connect to digital ground.                                                          |

|          | 23  | G   |                                                                                     |

|          | 36  | G   |                                                                                     |

|          | 42  | G   |                                                                                     |

|          | 50  | G   |                                                                                     |

|          | 62  | G   |                                                                                     |

|          | 76  | G   |                                                                                     |

|          | 82  | G   |                                                                                     |

|          | 113 | G   |                                                                                     |

|          | 115 | G   |                                                                                     |

| CVDD_1.8 | 20  | Р   | Connect to 1.8V digital supply.                                                     |

|          | 35  | Р   | Must be bypassed with a 0.1µF capacitor to CRVSS (as close to the pin as possible). |

|          | 49  | Р   |                                                                                     |

|          | 81  | Р   |                                                                                     |

|          | 114 | Р   |                                                                                     |

| AVSS     | 5   | G   | Connect to digital ground                                                           |

|          | 16  | G   |                                                                                     |

|          | 18  | G   |                                                                                     |

| AVDD_3.3 | 4   | Р   | Connect to 3.3V supply                                                              |

|          | 17  |     | Must be bypassed with a 0.1μF capacitor to ACVSS (as close to the pin as possible). |

|          | 19  |     |                                                                                     |

## 4 Functional Description

A functional block diagram is illustrated below. Each of the functional units shown is described in the following sections.

Figure 4. gmZAN3 Functional Block Diagram

#### 4.1 Clock Generation

The gmZAN3 features two clock inputs. All additional clocks are internal clocks derived from one or more of these:

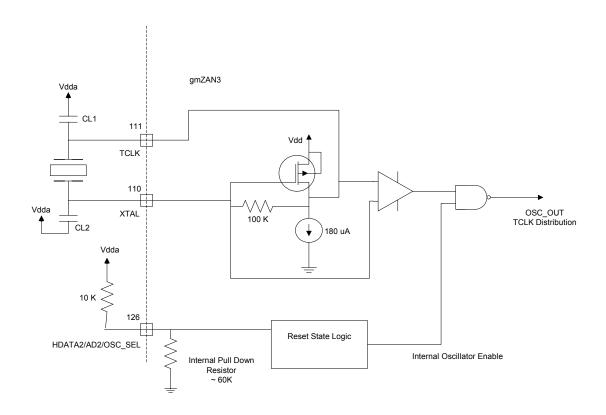

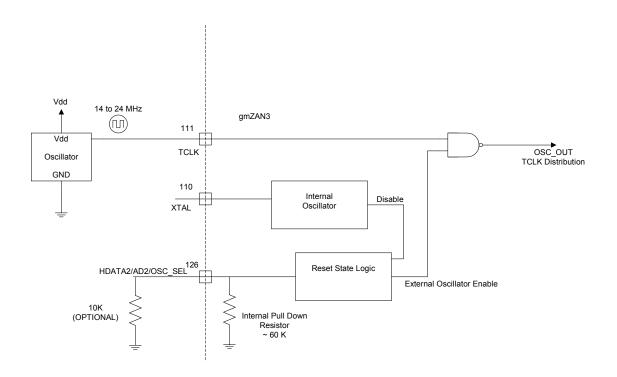

- 1. Crystal Input Clock (TCLK and XTAL). This is the input pair to an internal crystal oscillator and corresponding logic. A 14.318 MHz crystal is recommended. Other crystal frequencies may be used, but require custom programming. This is illustrated in Figure 5 below. This option is selected by connecting a 10KΩ pull-up to HDATA2/AD2/OSC\_SEL. Alternatively a single-ended TTL/CMOS clock oscillator can be driven into the TCLK pin (leave XTAL and HDATA2/AD2/OSC\_SEL as N/C in this case). This is illustrated in Figure 8 below. See also Table 14.

- 2. Host Interface Transfer Clock (HCLK). For 2 or 6-wire Host Interface Port only. Not for muxed A/D.

The gmZAN3 TCLK oscillator circuitry is a custom designed circuit to support the use of an external oscillator or a crystal resonator to generate a reference frequency source for the gmZAN3 device.

#### 4.1.1 Using the Internal Oscillator with External Crystal

The first option for providing a clock reference is to use the internal oscillator with an external crystal. The oscillator circuit is designed to provide a very low jitter and very low harmonic clock to the internal circuitry of the gmZAN3. An Automatic Gain Control (AGC) is used to insure startup and operation over

a wide range of conditions. The oscillator circuit also minimizes the overdrive of the crystal, which reduces the aging of the crystal.