# GX434 Monolithic 4x1 Video Multiplexer

DATA SHEET

### **FEATURES**

- low differential gain: 0.03% typ. at 4.43 MHz

- low differential phase: 0.012 deg. typ. at 4.43 MHz

- low insertion loss: 0.05 dB max at 100 kHz

- low disabled power consumption: 5.2 mW typ.

- high off isolation: 110 dB at 10 MHz

- all hostile crosstalk @ 5 MHz, 97 dB typ.

- bandwidth (-3dB) with 30 pF load, 100 MHz typ.

- fast make-before-break switching: 200 ns typ.

- TTL and 5 volt CMOS compatible logic inputs

- low cost 14 pin DIP and16 pin SOIC packages

- optimised performance for NTSC, PAL and SECAM applications

### **APPLICATIONS**

Glitch free analog switching for...

- High quality video routing

- A/D input multiplexing

- Sample and hold circuits

- TV/ CATV/ monitor switching

## **AVAILABLE PACKAGING**

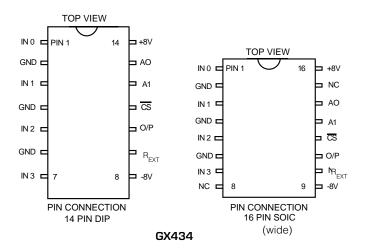

14 pin DIP and 16 pin SOIC (wide)

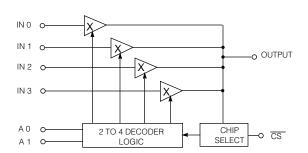

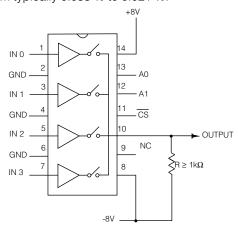

### **FUNCTIONAL BLOCK DIAGRAM**

### **CIRCUIT DESCRIPTION**

The GX434 is a high performance low cost monolithic 4x1 video multiplexer incorporating four bipolar switches with a common output, a 2 to 4 address decoder and fast chip select circuitry. The chip select input allows for multi-chip paralleled operation in routing matrix applications. The chip is selected by applying a logic 0 on the chip select input.

Unlike devices using MOS bilateral switching elements, these bipolar circuits represent fully buffered, unilateral transmission paths when selected. This results in extremely high output to input isolation. They also feature fast make-before-break switching action. These features eliminate such problems as switching 'glitches' and output-to-input signal feedthrough.

The GX434 operates from  $\pm 7$  to  $\pm 13.2$  volt DC supplies. They are specifically designed for video signal switching which requires extremely low differential phase and gain. Logic inputs are TTL and 5 volt CMOS compatible providing address and chip select functions. When the chip is not selected, the output goes to a high impedance state.

### **PIN CONNECTIONS**

### **TRUTH TABLE**

| cs | A1 | A0 | OUTPUT |

|----|----|----|--------|

| 0  | 0  | 0  | IN 0   |

| 0  | 0  | 1  | IN 1   |

| 0  | 1  | 0  | IN 2   |

| 0  | 1  | 1  | IN 3   |

| 1  | Х  | Х  | HI - Z |

X = DON'T CARE

Document No. 510 - 34 - 2

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                    | Value & Units                                    |

|------------------------------|--------------------------------------------------|

| Supply Voltage               | ±13.5V                                           |

| Operating Temperature Range  | $0^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ 70° C |

| Storage Temperature Range    | -65°C ≤ T <sub>S</sub> ≤ 150° C                  |

| Lead Temperature (Soldering, | 10 Sec) 260° C                                   |

| Analog Input Voltage         | $-4V \le V_{ N} \le +2.4V$                       |

| Analog Input Current         | 50μA AVG, 10 mA peak                             |

| Logic Input Voltage          | $-4V \le V_L \le +5.5V$                          |

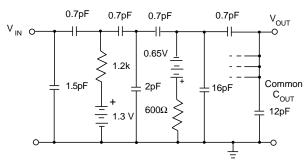

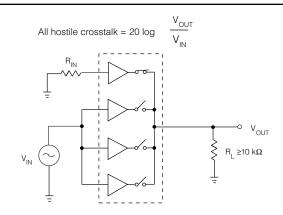

Fig.1 Crosspoint Equivalent Circuit

### **ORDERING INFORMATION**

| Part Number | Package Type     | Temperature Range |  |  |

|-------------|------------------|-------------------|--|--|

| GX434 CDB   | 14 Pin DIP       | 0° to 70° C       |  |  |

| GX434 CKC   | 16 Pin SOIC      | 0° to 70° C       |  |  |

| GX434 CTC   | Tape 16 Pin SOIC | 0° to 70° C       |  |  |

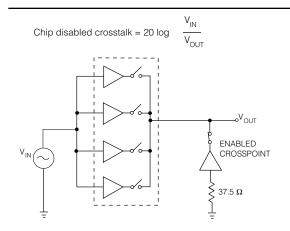

Fig. 2 Disabled Crosspoint Equivalent Circuit

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \ (\text{V}_{\text{S}} = \pm 8 \text{V DC}, \, 0^{\circ}\text{C} < \text{T}_{\text{A}} < 70^{\circ}\text{C}, \, \text{C}_{\text{L}} = 30 \, \text{pF}, \, \text{R}_{\text{L}} = 10 \text{k}\Omega \, \text{unless otherwise shown.})$

|        |                                |                          |                                     |     | G)   | X434 |       |

|--------|--------------------------------|--------------------------|-------------------------------------|-----|------|------|-------|

|        | PARAMETER                      | SYMBOL                   | CONDITIONS                          | MIN | TYP  | MAX  | UNITS |

|        | Supply Voltage                 | ±V <sub>S</sub>          |                                     | 7   | 8    | 13.2 | ٧     |

| DC     |                                | I+                       | Chip selected (CS=0)                | -   | 10.5 | 11.5 | mA    |

| SUPPLY |                                |                          | Chip not selected (CS=1)            | -   | 0.4  | 0.58 | mA    |

|        | Supply current                 | l-                       | Chip selected (CS=0)                | -   | 10.2 | 11.2 | mA    |

|        |                                |                          | Chip not selected (CS=1)            | -   | 0.25 | 0.38 | mA    |

|        | Analog Output                  | V <sub>OUT</sub>         | Extremes before clipping            | -   | +2   | -    |       |

|        |                                |                          | occurs.                             | -   | -1.2 |      | V     |

|        | Analog Input Bias              | I <sub>BIAS</sub>        |                                     | -   | 22   | -    | μА    |

|        | Current                        |                          |                                     |     |      |      |       |

| STATIC | Output Offset Voltage          | V <sub>OS</sub>          | $T_A = 25$ °C, 75 $\Omega$ resistor |     |      |      |       |

|        |                                |                          | on each input to gnd                | 0   | 7    | 14   | mV    |

|        | Output Offset Voltage<br>Drift | $\Delta V_{OS}/\Delta T$ |                                     | -   | +50  | +200 | μV/°C |

$\mathsf{R}_{\mathsf{EXT}} = 33.2 \; \mathsf{k}\Omega, \; 1\%$

# $\textbf{ELECTRICAL CHARACTERISTICS} \quad \textbf{continued} \qquad (\textbf{V}_{S} = \pm 8 \textbf{V DC}, \, 0^{\circ} \textbf{C} < \textbf{T}_{A} < 70^{\circ} \textbf{C}, \textbf{C}_{L} = 30 \text{pF}, \, \textbf{R}_{L} = 10 \text{k}\Omega \, \, \text{unless otherwise shown.})$

|         |                                                            |                        |                                                                                          |       | GΧ    | (434  |         |

|---------|------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|---------|

|         | PARAMETER                                                  | SYMBOL                 | CONDITIONS                                                                               | MIN   | TYP   | MAX   | UNITS   |

|         | Crosspoint Selection<br>Turn-On Time                       | t <sub>ADR-ON</sub>    | Control input to appearance of signal at the output.                                     | 130   | 200   | 270   | ns      |

|         | Crosspoint Selection<br>Turn-Off Time                      | t <sub>ADR-OFF</sub>   | Control input to disappear-<br>ance of signal at output.                                 | 390   | 600   | 800   | ns      |

|         | Chip Selection<br>Turn-On Time                             | t <sub>CS-ON</sub>     | Control input to appearance of signal at output.                                         | 200   | 300   | 400   | ns      |

|         | Chip Selection<br>Turn-Off Time                            | t <sub>CS-OFF</sub>    | Control input to disappearance of signal at output.                                      | 460   | 700   | 940   | ns      |

| LOGIC   | Logic Input                                                | V <sub>IH</sub>        | 1                                                                                        | 2.0   | -     | -     | ٧       |

|         | Thresholds                                                 | V <sub>IL</sub>        | 0                                                                                        | -     | -     | 1.1   | V       |

|         | Address Input                                              | $I_{\text{BIAS(ADR)}}$ | Chip selected A0,A1 = 1                                                                  | -     | -     | 5.0   | μΑ      |

|         | Bias Current                                               |                        | Chip selected A0,A1 = 0                                                                  | -     | -     | 0.1   | nA      |

|         | Chip Select Bias                                           | $I_{\text{BIAS(CS)}}$  | CS = 1                                                                                   | -     | -     | 1.0   | nA      |

|         | Current                                                    |                        | CS = 0                                                                                   | -     | -     | 30    | μΑ      |

|         | Insertion Loss                                             | I.L.                   | 1V p-p sine or sq. wave at 100 kHz                                                       | 0.025 | 0.03  | 0.04  | dB      |

|         | Bandwidth (-3 dB)                                          | B.W.                   |                                                                                          | 100   | 120   | -     | MHz     |

|         | Gain Spread at 8 MHz                                       |                        |                                                                                          | -0.04 | -     | +0.06 | dB      |

|         | Input to Output Signal<br>Delay Matching<br>(chip to chip) | Δt <sub>p</sub>        | $T_A = 25^{\circ}\text{C}, R_S = 75\Omega$<br>f = 3.579545  MHz                          | -0.04 | -     | ±0.15 | degrees |

|         |                                                            |                        | 0°C < T <sub>A</sub> < 70°C, R <sub>S</sub> as above.                                    | -     | -     | ±0.3  | degrees |

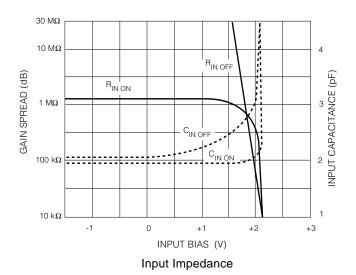

|         | Input Resistance                                           | R <sub>IN</sub>        | Chip selected (CS = 0)                                                                   | 900   | -     | -     | kΩ      |

| DYNAMIC | Input Capacitance                                          | C <sub>IN</sub>        | Chip selected (CS = 0)                                                                   | -     | 2.0   | -     | pF      |

|         |                                                            |                        | Chip not selected (CS = 1)                                                               | -     | 2.4   | -     | pF      |

|         | Output Resistance                                          | R <sub>OUT</sub>       | Chip selected (CS = 0)                                                                   | •     | 14    | -     | Ω       |

|         | Output Capacitance                                         | C <sub>OUT</sub>       | Chip not selected (CS = 1)                                                               | -     | 15    | -     | pF      |

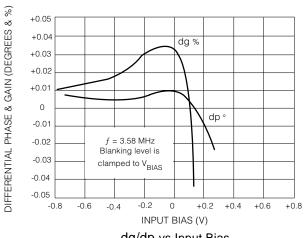

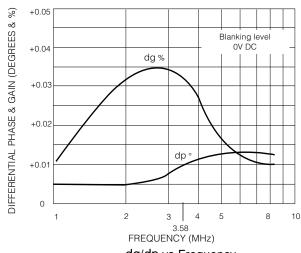

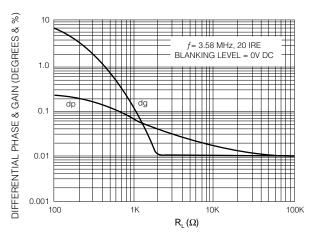

|         | Differential Gain                                          | dg                     |                                                                                          | -     | 0.03  | 0.05  | %       |

|         | Differential Phase                                         | dp                     | at 3.579545 MHz<br>V <sub>IN</sub> = 40 IRE, (Fig. 7)                                    | -     | 0.012 | 0.025 | degrees |

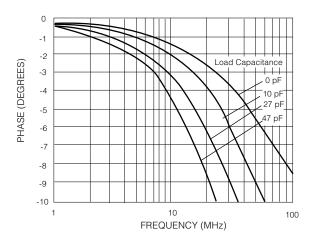

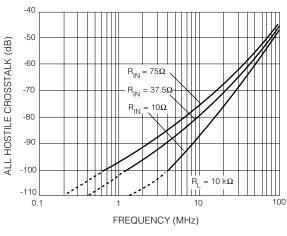

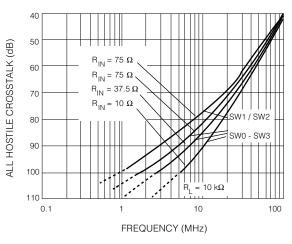

|         | All Hostile Crosstalk<br>(see graph)                       | X <sub>TALK (AH)</sub> | Sweep on 3 inputs 1V p-p 4th input has 10 $\Omega$ resistor to gnd. $f = 5$ MHz (Fig. 6) | 94    | 97    | -     | dB      |

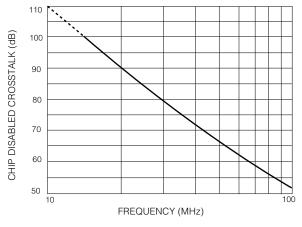

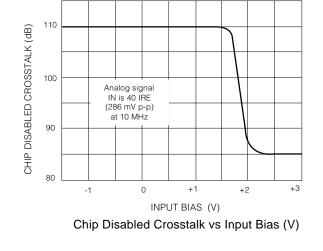

|         | Chip Disabled Crosstalk (see graph)                        | X <sub>TALK(CD)</sub>  | f = 10 MHz (Fig. 5)                                                                      | 100   | 110   | -     | dB      |

|         | a                                                          | +SR                    | V = 3V n-n (C = 0 nE)                                                                    | 360   | 450   | -     | V/μs    |

|         | Slew Rate                                                  |                        | $V_{IN} = 3V \text{ p-p } (C_L = 0 \text{ pF})$                                          |       | 200   | -     | V/µs    |

$R_{EXT} = 33.2k\Omega$ , 1%

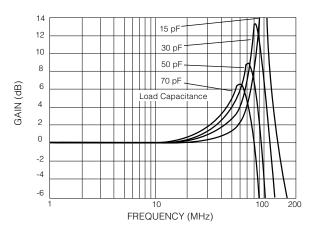

# TYPICAL PERFORMANCE CURVES OF THE GX434

Gain vs Frequency

Phase vs Frequency

All Hostile Crosstalk (14 pin DIP)

All Hostile Crosstalk (16 pin SOIC)

For all graphs,  $V_S = \pm 8$  V DC and  $T_A = 25$  °C. The curves shown above represent typical batch sampled results.

Chip Disabled Crosstalk vs Frequency

dg/dp vs Input Bias

dg/dp vs Frequency

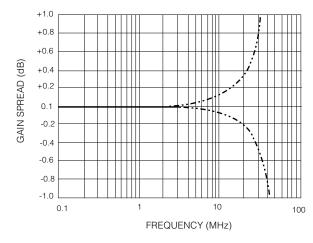

Normalized Gain Spread  $C_L = 30pF$

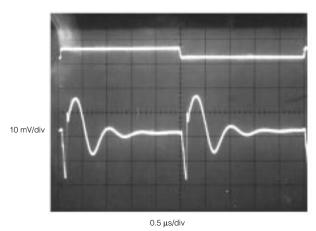

Fig.3 Switching Transient (crosspoint to crosspoint)

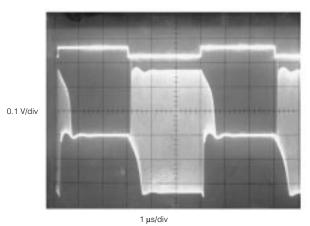

Fig. 4 Switching Envelope (crosspoint to crosspoint)

Fig. 5 Chip Disabled Crosstalk Test Circuit

Fig. 6 All Hostile Crosstalk Test Circuit

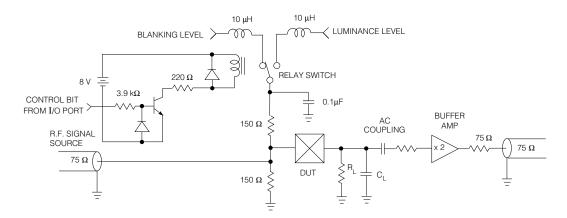

Fig. 7 Differential Phase and Gain Test Circuit

# **DIFFERENTIAL GAIN AND PHASE TEST CIRCUIT**

The test circuit of Figure 7 allows two DC bias levels, set by the user, to be superimposed on a high frequency signal source. A computer controlled relay selects either the preset blanking or luminance level. One measurement is taken at each level and the change in gain or phase is calculated. This procedure is repeated one hundred times to provide a reasonably large sample.

The results are averaged to reduce the standard deviation and therefore improve the accuracy of the measurement.

The output from the device under test is AC coupled to a buffer amplifier which allows the buffer to operate at a constant luminance level so that it does not contribute any dg or dp to the measurement.

6

### **OPTIMISING THE PERFORMANCE OF THE GX434**

# 1. Power Supply Considerations

Table 1 shows the effect on differential gain (dg) and differential phase (dp) of various power supply voltages that may be used. A nominal supply voltage of  $\pm 8$  volts result in parameter values as shown in the top row of the table. By using other power supply voltage combinations, improvements to these parameters are possible at the sacrifice of increased chip power dissipation. Maximum degradation of the differential gain and phase occurs for the last combination of +12 , -7 volts along with an increase in power dissipation; these voltages are not recommended.

| Supply<br>Voltage | Differential Gain<br>%<br>(Typical) | Differential Phase<br>degrees<br>(Typical) |

|-------------------|-------------------------------------|--------------------------------------------|

| ±8                | 0.030                               | 0.012                                      |

| +8/ -12           | 0.010                               | 0.007                                      |

| ±12               | 0.010                               | 0.007                                      |

| +12/ -7           | 0.084                               | 0.080                                      |

Table 2 shows the general characteristic variations of the GX434 when different combinations of power supply voltages are used. These changes are relative to a circuit using  $\pm$  8 volts Vcc.

| Supply Voltage | Characteristic Changes                                                                                                                                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ± 7            | - lower logic thresholds<br>- max logic I/P (≈ 4.5V)<br>- loss of off isolation (≈20 dB)<br>- poorer dg and dp                                                           |

| +8/ -12        | <ul> <li>slight increase in negative<br/>supply current</li> <li>slight decrease in offset</li> <li>very similar frequency response</li> <li>better dg and dp</li> </ul> |

| ±12            | <ul> <li>increase in supply current (10%)</li> <li>increase in offset (≈ 2-4 mV)</li> <li>very similar frequency response</li> <li>better dg and dp</li> </ul>           |

| +12/ -7        | <ul><li>loss in off isolation (≈20 dB)</li><li>poorer dg and dp</li></ul>                                                                                                |

510 -34 -2

7

### 2. Load Resistance Considerations

The GX434 crosspoint switch is optimised for load resistances equal to or greater than 3 k $\Omega$ . Figure 8 shows the effect on the differential gain and phase when the load resistance is varied from 100  $\Omega$  to 100 k $\Omega$ .

Fig. 8 dg/dp vs R,

The negative slew rate is dependant upon the output current and load capacitance as shown below.

$$-SR = I + 3 \, mA \qquad I \le 8 \, mA$$

The current *I* is determined from the following equation:

$$I = \frac{-V_{EE}}{R} \quad R \ge 1 \, k \, \Omega$$

It is possible to increase the negative slew rate (-S.R.) and thus the large signal bandwidth, by adding a resistance from the output to -  $V_{\text{EE}}$ . This resistor increases the output current above the 3 mA provided by the internal current generator and increases the negative slew rate. The additional slew rate improving resistance must not be less than  $1k\Omega$  in order to prevent excessive currents in the output of the device. An adverse effect of utilising this negative slew rate improving resistor, is the increase in differential phase from typically  $0.009^{\circ}$  to  $0.014^{\circ}$ . Under these same conditions, the differential gain drops from typically 0.033 % to 0.021 %.

Fig.9 Negative Slew Rate (-SR) Improvement

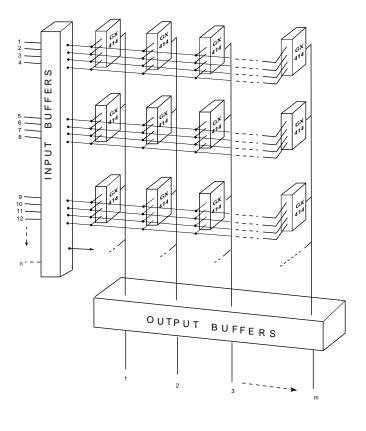

## 3. Multi-chip Considerations

Whenever multi-chip bus systems are to be used, the total input and output capacitance must be carefully considered. The input capacitance of an enabled crosspoint (chip selected), is typically only 2 pF and increases slightly to 2.4 pF when the chip is disabled. The total output capacitance when the chip is disabled is approximately 15 pF per chip.

Usually the GX434 multiplexer switch is used in a matrix configuration of (n x 1) crosspoints perhaps combined in an (n x m) total routing matrix. This means for example, that four ICs produce a  $16 \times 1$  configuration and have a total output capacitance of  $4 \times 15$  pF or 60 pF if all four chips are disabled. For any one enabled crosspoint, the effective load capacitance will be  $3 \times 15$  pF or 45 pF.

In a multi-input/multi-output matrix, it is important to consider the total input bus capacitance. The higher the bus capacitance and the more it varies from the ON to OFF condition, the more difficult it is to maintain a wide frequency response and constant drive from the input buffer. A  $16 \times 16$  matrix using 64 ICs ( $16 \times 4$ ), would have a total input bus capacitance of  $16 \times 2.4$  pF or 40 pF.

Fig.10 Multi-chip Connections

#### APPLICATIONS INFORMATION

The GX434 multiplexer is a very high performance, wideband circuit requiring careful external circuit design. Good power supply regulation and decoupling are necessary to achieve optimum results. The circuit designer must use proper lead dress, component placement and PCB layout as in any high frequency circuit.

Functionally, the video switches are non-inverting, unity gain bipolar switches with buffered inputs requiring DC coupling and  $75\Omega$  line terminating resistors when directly driven from  $75\Omega$  cable. The output must be buffered to drive  $75\Omega$  lines. This is usually accomplished with the addition of an operational amplifier/ buffer which also allows adjustments to be made to the gain, offset and frequency response of the overall circuit.

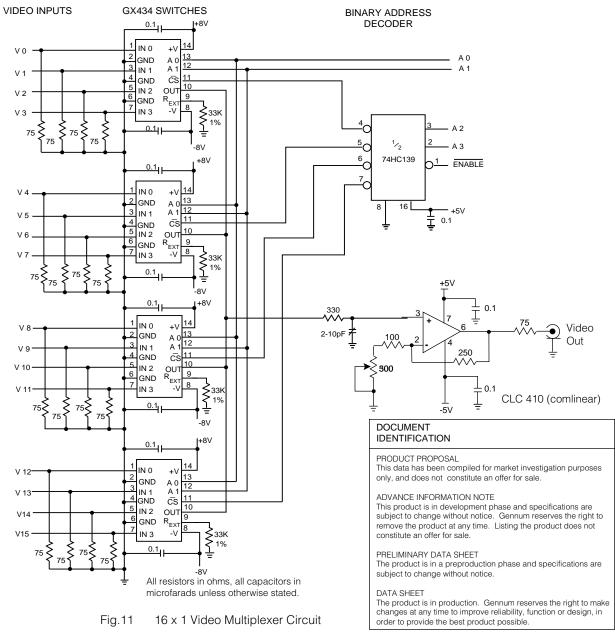

A typical video routing application is shown in Figure 11. Four ICs are used in a 16 x 1 multiplexer switching circuit.

An external address decoder is shown which generates the 16 address and chip enable codes from a binary number. The address inputs to each chip are active high while the chip select inputs are active low. Depending on the application and speed of the logic family used, latches may be required for synchronization where timing and delays are critical. Since the individual crosspoint switching circuits are unidirectional bipolar elements, low crosstalk and high isolation are inherent. The makebefore-break switching characteristics of the GX434 means virtually 'glitch' free switching.

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

©Copyright August 1989 Gennum Corporation. Revision date: January 1993. All rights reserved. Printed in Canada.