# ICs for Communications

PLL-Frequency Synthesizer

PMB2306R/PMB2306T Version 2.2

Data Sheet 02.97

| PMB2306R/PMB2306T<br>Revision History: |                             | Current Version: 02.97                                                                                                                                                                                              |  |  |

|----------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Previous Ver                           | rsion: 01.94                |                                                                                                                                                                                                                     |  |  |

| Page<br>(in previous<br>Version)       | Page<br>(in new<br>Version) | Subjects (major changes since last revision)                                                                                                                                                                        |  |  |

| 14-15                                  | 19-20                       | AC/DC Characteristics H-input current $I_{\rm H}$ : is changed from 10μA to 30μA and L-input current $I_{\rm L}$ : is changed from -10μA to -30μA                                                                   |  |  |

| 26                                     | 26                          | Clock frequency $f_{\rm CL}$ max. is changed from 10MHz to 12MHz;<br>H-pulsewidth (CL) $t_{\rm WHCL}$ min. is changed from 60ns to 40ns;<br>H-pulsewidth (enable) $t_{\rm WHEN}$ min. is changed from 60ns to 40ns; |  |  |

| 18                                     | 18                          | Input reference frequency $f_{\rm CRI}$ : is changed from 20MHz to 22MHz                                                                                                                                            |  |  |

| 19                                     | 19                          | Input Signal RI Input voltage $V_{\rm I}$ : is changed from 20MHz to 22MHz                                                                                                                                          |  |  |

### Edition 02.97

This edition was realized using the software system FrameMaker  $^{\! @}\! .$

Published by Siemens AG,

**HLIT**

© Siemens AG 1997.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose! Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

## PMB2306R/PMB2306T

| Table o | Table of Contents                             |    |  |  |  |  |  |

|---------|-----------------------------------------------|----|--|--|--|--|--|

| 1       | Overview                                      | 4  |  |  |  |  |  |

| 1.1     | Features                                      |    |  |  |  |  |  |

| 1.2     | Pin Configuration                             | 5  |  |  |  |  |  |

| 1.3     | Pin Definitions and Functions                 | 6  |  |  |  |  |  |

| 1.4     | Functional Block Diagram                      | 9  |  |  |  |  |  |

| 2       | Circuit Description                           | 10 |  |  |  |  |  |

| 3       | Electrical Characteristics                    | 18 |  |  |  |  |  |

| 3.1     | Absolute Maximum Ratings                      | 18 |  |  |  |  |  |

| 3.2     | Typical Supply Current <i>I</i> <sub>DD</sub> | 18 |  |  |  |  |  |

| 3.3     | AC/DC Characteristics                         | 19 |  |  |  |  |  |

| 4       | Package Outlines                              | 34 |  |  |  |  |  |

| 4.1     | Plastic-Package, P-TSSOP-16                   | 34 |  |  |  |  |  |

| 4.2     | Plastic-Package, P-DSO-14-1(SMD)              | 35 |  |  |  |  |  |

### **PLL-Frequency Synthesizer**

### PMB2306R/PMB2306T

**PMB2306T**

Version 2.2 Bipolar IC

#### 1 Overview

#### 1.1 Features

- Low operating current consumption (typically 3.5 mA)

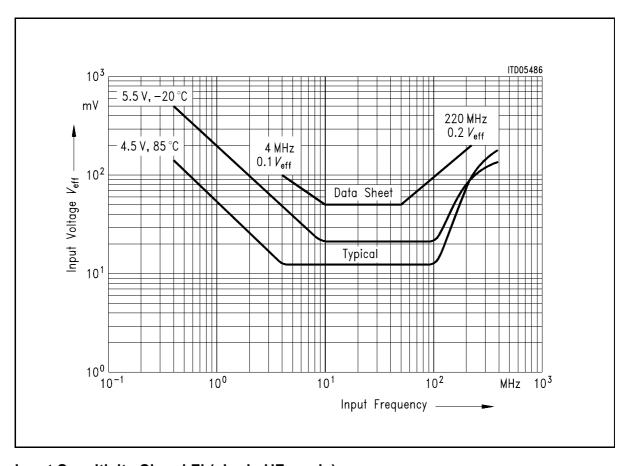

- High input sensitivity, high input frequencies (220 MHz)

- Extremely fast phase detector without dead zone

- Linearization of the phase detector output by current sources

- Synchronous programming of the counters (n-, n/a-, r-counters) and system parameters

- Fast modulus switchover for 65-MHz operation

- Switchable modulus trigger edge

- Large dividing ratios for small channel spacing A scaler 0 to 127

N scaler 3 to 16.380

R scaler 3 to 65.535

P-TSSOP-16

- Serial control (3-wire bus: data, clock, enable) for fast programming ( $f_{max} \sim 10 \text{ MHz}$ )

- Switchable polarity and phase detector current programmable

- 2 Multifunction outputs

- Digital phase detector output signals (e.g. for external charge pump)

- $f_m$ ,  $f_{vn}$  outputs of the R and N scalers

- Port 1 output (e.g. for standby of the prescaler)

- External current setting for PD output

- Lock detect output with gated anti-backlash pulse (quasi digital lock detect)

| Туре      | Version | Ordering Code       | Package                     |

|-----------|---------|---------------------|-----------------------------|

| PMB 2306T | V2.2    | Q67100-H6423        | P-DSO-14 (SMD)              |

| PMB 2306T | V2.2    | Q67106-H6423        | P-DSO-14 (SMD, Tape & Reel) |

| PMB 2306R | V2.2    | Q-67106-H6514 (T&R) | P-TSSOP-16 (SMD, T&R)       |

The PMB 2306T PLL is a high speed CMOS IC, especially designed for use in battery powered radio equipment and mobile telephones. The primary applications will be in digital systems e.g. GSM, PCN, ADC, JDC and DECT systems. The wide range of dividing ratios also allows application in modern analog systems

Overview

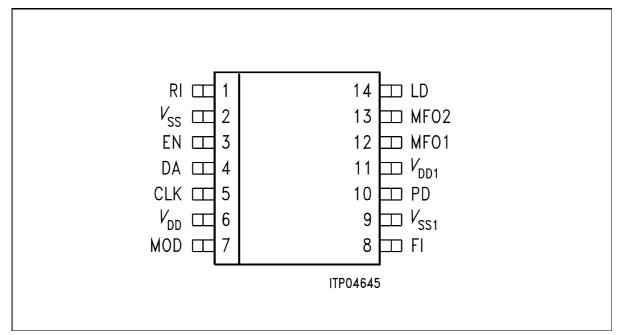

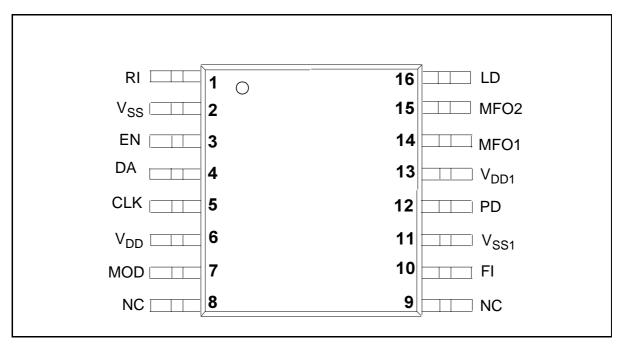

## 1.2 Pin Configuration

(top view)

### **P-DSO-14**

## P-TSSOP-16

Overview

### 1.3 Pin Definitions and Functions

### Table 1

| DSO-14 | TSSOP-16 | Symbol            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | 6        | $V_{DD}$          | Positive supply voltage for serial control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2      | 2        | $V_{\mathtt{SS}}$ | Ground for serial control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11     | 13       | $V_{DD1}$         | Positive supply voltage for the preamplifiers, counters, phase detector and charge pump.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9      | 11       | $V_{\rm SS1}$     | Ground for the preamplifiers, counters, phase detector and charge pump. (Note: The pins $V_{\rm DD}$ and $V_{\rm DD1}$ respectively $V_{\rm SS}$ and $V_{\rm SS1}$ have to have the same supply voltage.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

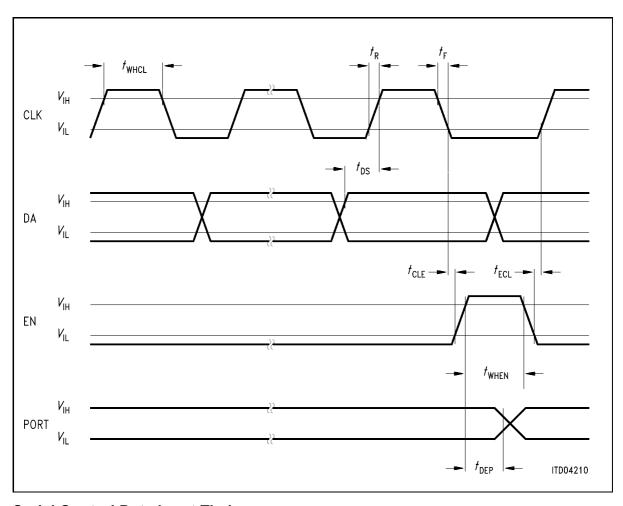

| 3      | 3        | EN                | 3-Line Bus: Enable Enable line of the serial control with internal pull-up resistor. When EN = H the input signals CLK and DA are disabled internally. When EN = L the serial control is activated. The received data are transferred into the latches with the positive edge of the EN-signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4      | 4        | DA                | 3-Line Bus: Data Serial data input with internal pull-up resistor. The last two bits before the EN-signal define the destination address. In a byte-oriented data structure the transmitted data have to end with the EN-signal, i.e. bits to be filled in (don't care) are transmitted first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5      | 5        | CLK               | <b>3-Line Bus: Clock</b> Clock line with internal pull-up resistor. The serial data are read into the internal shift register with the positive edge (see pulse diagram for serial data control).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

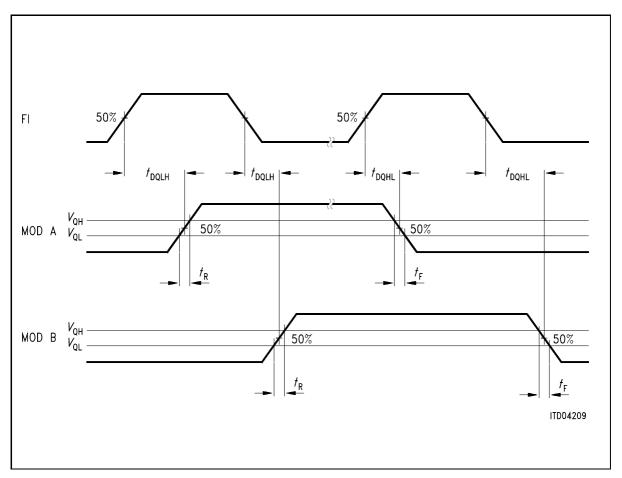

| 7      | 7        | MOD               | Modulus Control Output for external dual modulus prescaler. The modulus output is low at the beginning of the cycle. When the a-counter has reached its set value, MOD switches to high. When the n-counter has reached its set value, MOD switches to low again, and the cycle starts from the top. When the prescaler has the counter factor P or P+1 (P for MOD = H, P+1 for MOD = L), the overall scaling factor is NP + A. The value of the acounter must be smaller than that of the n-counter. The trigger edge of the modulus signal to the input signal can be selected (see programming tables and MOD A, B) according to the needs of the prescaler. In single modulus operation and for standby operation in dual modulus operation, the output is low. |

## PMB2306R/PMB2306T

Overview

### Table 1

| DSO-14 | TSSOP-16 | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|--------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 8      | 10       | FI     | VCO-Frequency Input with highly sensitive preamplifier for 14-bit n-counter and 7-bit a-counter. With small input signals AC coupling must be set up, where DC coupling can be used for large input signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1      | 1        | RI     | Reference Frequency Input with highly sensitive preamplifier for 16-bit r-counter. With small input signals AC coupling must be set up, where DC coupling can be used for large input signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

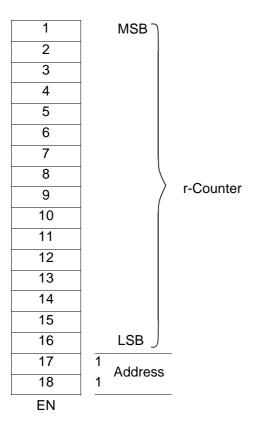

| 10     | 12       | PD     | Phase Detector Tristate charge pump output. The integrated, positive and negative current sources can be programmed with respect to their current density by means of the serial control. Activation and deactivation depend on the phase relationship of the scaled-down input signals FI:N, RI:R. (See phase detector output waveforms.) frequency $f_{\rm V} < f_{\rm R}$ or $f_{\rm V}$ lagging: p-channel current source active frequency $f_{\rm V} > f_{\rm R}$ or $f_{\rm R}$ leading: n-channel current source active frequency $f_{\rm V} > f_{\rm R}$ and PLL locked: current sources are switched off, PD-output is tristate In standby mode the PD-output is set to tristate. The assignment of the current sources to the output signals of the phase detector can be swapped in it's polarity, i.e. the sign of the phase detector constant can be controlled. |  |  |  |  |

| 14     | 16       | LD     | Lock Detector Output (open drain). Unipolar output of the phase detector in the form of a pulse-width modulated signal. The L-pulse width corresponds to the phase difference. Phase differences < 20 ns are not indicated due to gating of the antibacklash impuls. In the locked state the LD-signal is at H-level. In standby mode the output is resistive. Only for ABL status 11 no gating of ABL impulse is performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

## PMB 2306R/PMB2306T

Overview

02.97

### Table 1

| DSO-14 | TSSOP-16 | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12     | 14       | MFO1   | <b>Multifunction Output</b> for the signals $f_{\rm RN}$ , $\Phi_{\rm V}$ , $\Phi_{\rm VN}$ and port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

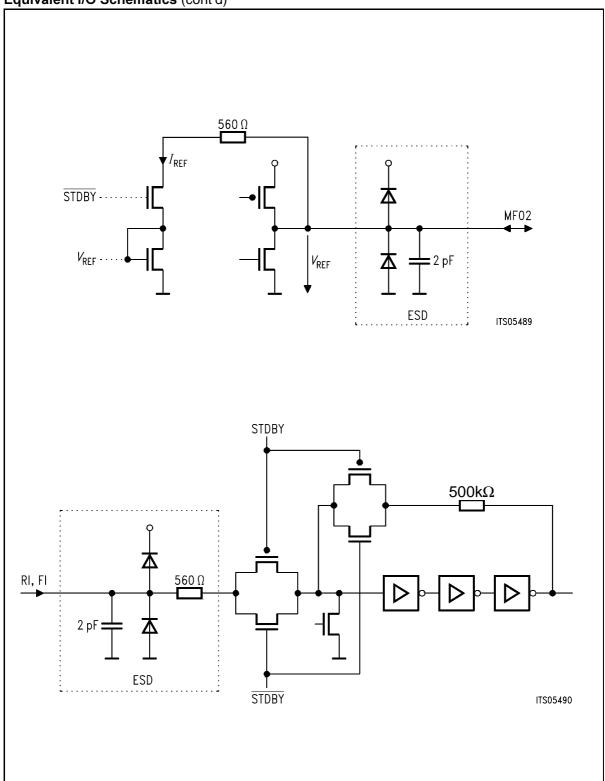

| 13     | 15       | MFO2   | <ul> <li>Multifunction I/O-Pin for the output signals f<sub>VN</sub>, Φ<sub>RN</sub> and the input signal I<sub>REF</sub>.</li> <li>The signals Φ<sub>R</sub> and Φ<sub>V</sub> are the digital output signals of the phase and frequency detector for use in external active current sources (see phase detector output wave forms).</li> <li>The signals f<sub>RN</sub> and f<sub>VN</sub> are the scaled down signals of the reference frequency and VCO-frequency. The L-time corresponds to 1/f<sub>RI</sub> and 1/f<sub>FI</sub> respectively.</li> <li>In the port function the port 1 output signal is assigned to the information of the status program. The output switches with the rising edge of the EN-signal. The standby mode does not affect the port function.</li> <li>In the internal charge pump mode the input signal I<sub>REF</sub> determines the value of the PD-output current.</li> <li>Reference current for charge pump:</li> <li>I<sub>REF</sub> = (V<sub>DD</sub> - V<sub>REF</sub>)/R1</li> <li>= 100µA (tolerance of ±20% or less is recommended)</li> <li>R1:see application circuit</li> <li>V<sub>REF</sub>:see AC/DC characteristics</li> </ul> |

Overview

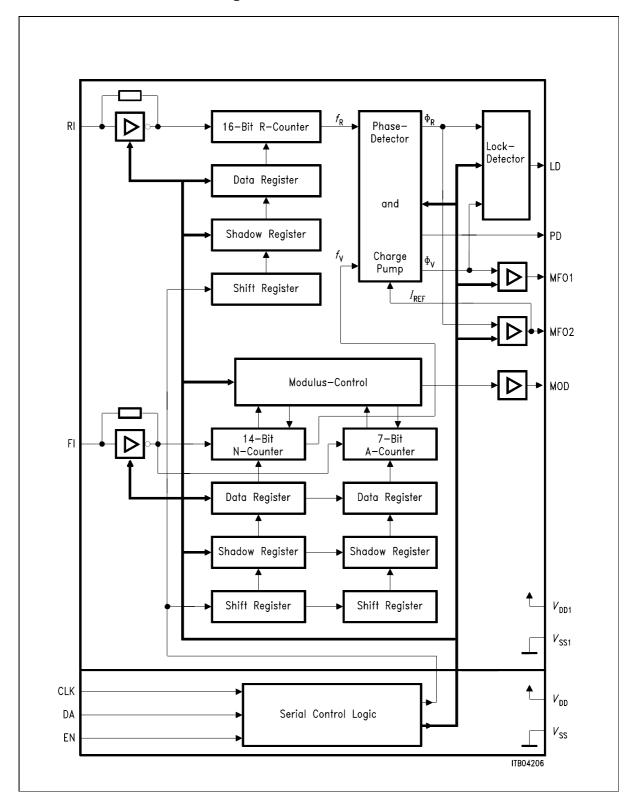

### 1.4 Functional Block Diagram

**Circuit Description**

### 2 Circuit Description

### **General Description**

The circuit consists of a reference-, a- and n-counter, a dual modulus control logic, a phase detector with charge pump output and a serial control logic. The setting of the operating mode and the selection of the counter ratios is done serially at the ports CLK, DA and FN.

The operating modes allow the selection of single or dual operation, asynchronous or synchronous data acquisition, 4 different antibacklash-impulse times, 8 different PD-output current modes, polarity setting of the PD-output signal, adjustment of the triggeredge of the MOD-output signal, 2 standby modes and the control of the multifunction outputs MFO1 and MFO2.

The reference frequency is applied at the RI-input and scaled down by the r-counter. It's maximum value is 100 MHz. The VCO-frequency is applied at the FI-input and scaled down by the n- or n/a-counter according to single or dual mode operation. The maximum value at FI is 220 MHz at single-, and 65 MHz at dual mode operation.

The phase and frequency sensitive phase detector produces an output signal with adjustable anti-backlash impulses in order to prevent a dead zone for very small phase deviations. Phase differences of less than 100 ps can be resolved. In general the shortest anti-backlash pulse gives the best system performance.

### **Programming**

Programming of the IC is done by a serial data control. The contents of the message are assigned to the functional units according to the address. Single or dual mode operation as well as asynchronous or synchronous data acquisition is set by status 2 and should therefore precede the programming of the counters.

### **Data acquisition**

The PMB 2306T offers the possibility of synchronous data acquisition to avoid error signals at the phase detector due to non-corresponding dividing factors in the counters produced by asynchronous loading.

Synchronous programming guarantees control during changes of frequency or channel. That means that the state of the phase detector or the phase difference is kept maintained, and in case of "lock in", the control process starts with the phase difference "zero".

**Circuit Description**

This is done as follows:

- 1. Setting of synchronous data acquisition by status 2.

- 2.Programming of the r-counter, status 1 (optional)-data is being loaded into shadow registers.

- 3.Programming of the n- or n/a-counter-data is being loaded into shadow registers, the EN-signal starts the synchronous loading procedure.

- 4.Synchronous programming which means data transfer of all data from the shadow registers to the data registers takes place at that point in time when the respective counter reaches "zero + 1", the maximum repetition rate for channel change is therefore  $f_{\text{FI}}$ :N.

- 5. Transfer of status 1 information into the corresponding data register is tied to the n-counter loading, but follows the loading of the n-data register in the distance of one n-counter dividing ratio, this guarantees that for example a new PD-current value becomes valid at the same time when the counters are loaded with the new data.

Synchronous avoids additional phase error caused by programming. Synchronous data acquisition is of especial advantage, when large steps in frequency are to be made in a short time. For this purpose a high reference frequency can be programmed in order to achieve rapid – "rough" – transient response. This method increases the fundamental frequency nearly by the square route of the reference frequency relation. When rough lock is achieved, another synchronous data transfer is needed to switch back to the original channel spacing. A "fine" lock in will finish the total step response. It may not be necessary to change reference frequency, but it make sense to perform synchronous data acquisition in any case. Especially for GSM, PCN, DECT, DAMPS, JDC, PHP systems the synchronous mode should be used to get best performance of the PMB 2306T.

### **Standby Condition**

The PMB 2306T has two standby modes (standby 1, 2) to reduce the current consumption.

Standby 1 switches off the whole circuit, the current consumption is reduced below 1  $\mu$ A. Standby 2 switches off the counters, the charge pump and the outputs, only the preamplifiers stay active.

The standby modes do not affect the port output signal. For the influence on the other output signals **see standby table**.

Note:  $f_{RN}$ ,  $f_{VN}$ ,  $\Phi_{RN}$  and  $\Phi_{VN}$  are the inverted signals of  $f_{R}$ ,  $f_{V}$ ,  $\Phi_{R}$  and  $\Phi_{V}$ .

### PMB 2306R/PMB2306T

### **Circuit Description**

### **Programming Tables**

| Status Bits   |   | Multifunc   | Multifunction Outputs |                             |  |  |

|---------------|---|-------------|-----------------------|-----------------------------|--|--|

| Mode 2 Mode 1 |   | MFO 1       | MFO 2                 | Remarks                     |  |  |

| 0             | 0 | $f_{RN}$    | $f_{\sf VN}$          | test mode                   |  |  |

| 0             | 1 | $\Phi_{V}$  | $\Phi_{RN}$           | external charge pump mode 1 |  |  |

| 1             | 0 | $\Phi_{VN}$ | $\Phi_{RN}$           | external charge pump mode 2 |  |  |

| 1             | 1 | Port 1      | $I_{REF}$             | internal charge pump mode   |  |  |

| Status Bits  |              | PD-Current Mode |       |

|--------------|--------------|-----------------|-------|

| PD-Current 3 | PD-Current 2 | PD-Current 1    |       |

| 0            | 0            | 0               | 0.175 |

| 0            | 0            | 1               | 0.25  |

| 0            | 1            | 0               | 0.35  |

| 0            | 1            | 1               | 0.5   |

| 1            | 0            | 0               | 0.7   |

| 1            | 0            | 1               | 1     |

| 1            | 1            | 0               | 1.4   |

| 1            | 1            | 1               | 2     |

### Programming Tables (cont'd)

#### **Status Bits**

| Anti-Backlash<br>Pulse Width 2 | Anti-Backlash Pulse Width 1 | <i>t</i> <sub>w</sub> (typ.)<br>[ns] | Application                                           |

|--------------------------------|-----------------------------|--------------------------------------|-------------------------------------------------------|

| 0                              | 0                           | 1.3*                                 | $V_{\rm DD}$ = 5 V                                    |

| 0                              | 1                           | 5                                    |                                                       |

| 1                              | 0                           | 10                                   | not recommended                                       |

| 1                              | 1                           | 13**                                 | any application where continuous lock detect required |

<sup>\*</sup> In general the shortest anti-backlash pulse gives the best system performance.

<sup>\*\*</sup> No ABL (Anti-Backlash-Pulse) gating performed. This means, that at the LD output the anti-backlash pulse will appear. In the other cases the anti-backlash pulse will be surpressed at the LD output.

### PMB2306R/PMB2306T

## **Circuit Description**

| Status Bits          |                        | Preamplifier Function Mode                               |  |  |

|----------------------|------------------------|----------------------------------------------------------|--|--|

| Single/ Dual<br>Mode | Preamplifier<br>Select |                                                          |  |  |

| 0                    | 0                      | FI-input frequency, single HF-mode                       |  |  |

| 0                    | 1                      | FI-input frequency, single LF-mode                       |  |  |

| 1                    | 0                      | FI-input frequency, dual mode, FI-trigger edge LH, MOD A |  |  |

| 1                    | 1                      | FI-input frequency, dual mode, FI-trigger edge HL, MOD B |  |  |

# **Standby Table**

|           |            | Output Pins     |       |           |          |     |

|-----------|------------|-----------------|-------|-----------|----------|-----|

| Status    | MFO 1      |                 | MFO 2 | LD        | PD       | MOD |

|           | $\Phi_{V}$ | $\Phi_{\sf VN}$ |       |           |          |     |

| Standby 1 | low        | high            | high  | resistive | tristate | low |

| Standby 2 | low        | high            | high  | resistive | tristate | low |

**Circuit Description**

### Serial Control Data Format (status 1, 2)

### Status 1 Status 2

|    |                             |    | 0            | 1           |  |

|----|-----------------------------|----|--------------|-------------|--|

|    | Data acquisition mode       | 1  | asynchronous | synchronous |  |

|    | Mode 1                      | 2  | see table    |             |  |

|    | Mode 2                      | 3  | see t        | able        |  |

|    | PD-polarity                 | 4  | negative     | positive    |  |

|    | Standby 1                   | 5  | standby      | active      |  |

|    | Standby 2                   | 6  | standby      | active      |  |

|    | Anti-backlash pulse width 1 | 7  | see table    |             |  |

|    | Anti-backlash pulse width 2 | 8  | see table    |             |  |

|    | Preamplifier select         | 9  | see table    |             |  |

|    | Single / dual mode          | 10 | single       | dual        |  |

| 1  | Port 1                      | 11 | low          | high        |  |

| 2  | PD-current 1                | 12 | see          | table       |  |

| 3  | PD-current 2                | 13 | see table    |             |  |

| 4  | PD-current 3                | 14 | see table    |             |  |

| 5  | 0 Address 0                 | 15 |              |             |  |

| 6  | 0 1                         | 16 |              |             |  |

| EN |                             | EN |              |             |  |

Single or dual mode operation as well as asynchronous or synchronous data acquisition is set by status 2 and should therefore precede the programming of the counters. (see also page 10)

### **Circuit Description**

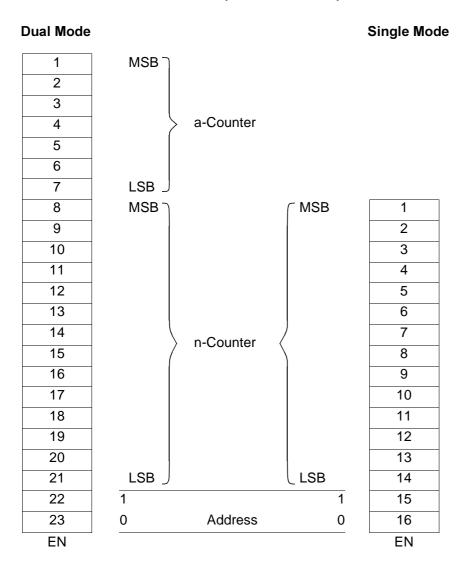

# Serial Control Data Format (n-, n/a-counter)

**Circuit Description**

## **Serial Control Data Format (r-counter)**

## **Circuit Description**

**Phase Detectorn Output Waveforms**

### **Electrical Characteristics**

### 3 Electrical Characteristics

## 3.1 Absolute Maximum Ratings

$T_{\rm A}$  = -40 to 85 °C

| Parameter                    | Symbol    | Limit Values |                    | Unit | Remarks      |

|------------------------------|-----------|--------------|--------------------|------|--------------|

|                              |           | min.         | max.               |      |              |

| Supply voltage               | $V_{DD}$  | - 0.3        | 6                  | V    |              |

| Input voltage                | $V_{I}$   | - 0.3        | $V_{\rm DD}$ + 0.3 | V    |              |

| Output voltage               | $V_{Q}$   | GND          | $V_{DD}$           | V    |              |

| Power dissipation per output | $P_{Q}$   |              | 10                 | mW   |              |

| Total power dissipation      | $P_{tot}$ |              | 300                | mW   |              |

| Ambient temperature          | $T_{A}$   | - 40         | 85                 | ℃    | in operation |

| Storage temperature          | $T_{stg}$ | - 50         | 125                | ℃    |              |

## **Operating Range**

| Supply voltage                 | $V_{DD}$     | 3.0         | 5.5                  | V          |                                     |

|--------------------------------|--------------|-------------|----------------------|------------|-------------------------------------|

| Input frequency dual mode      | $f_{\sf FI}$ | 0.1         | 65                   | MHz        | $V_{\rm DD} = 4.5 \dots 5.5  \rm V$ |

| Input frequency single HF-mode | $f_{FI}$     | 0.1         | 220                  | MHz        | $V_{\rm DD} = 4.5 \dots 5.5  \rm V$ |

| Input frequency single LF-mode | $f_{FI}$     | 0.1         | 90                   | MHz        | $V_{\rm DD} = 4.5 \dots 5.5  \rm V$ |

| Input reference frequency      | $f_{RI}$     |             | 100                  | MHz        | $V_{\rm DD} = 4.5 \dots 5.5  \rm V$ |

| Input frequency dual mode      | $f_{FI}$     | 0.1         | 30                   | MHz        | $V_{\rm DD}$ = 3.3 V                |

| Input frequency single HF-mode | $f_{FI}$     | 0.1         | 120                  | MHz        | $V_{\rm DD}$ = 3.3 V                |

| Input frequency single LF-mode | $f_{FI}$     | 0.1         | 35                   | MHz        | $V_{\rm DD}$ = 3.3 V                |

| Input reference frequency      | $f_{RI}$     |             | 22                   | MHz        | $V_{\rm DD}$ = 3.3 V                |

| PD-output current              | $/I_{PD}/$   |             | 4                    | mA         |                                     |

| PD-output voltage              | $V_{PD}$     | 0.5         | $V_{\rm DD} - 0.5$   | V          | $V_{\rm DD} = 4.5 - 5.5 \text{ V}$  |

| PD-output voltage              | $V_{PD}$     | 0.5         | $V_{\rm DD}$ $-$ 0.5 | V          | $V_{\mathrm{DD}}$ = 3.3 V           |

| Ambient temperature            | $T_{A}$      | <b>- 40</b> | 85                   | $^{\circ}$ |                                     |

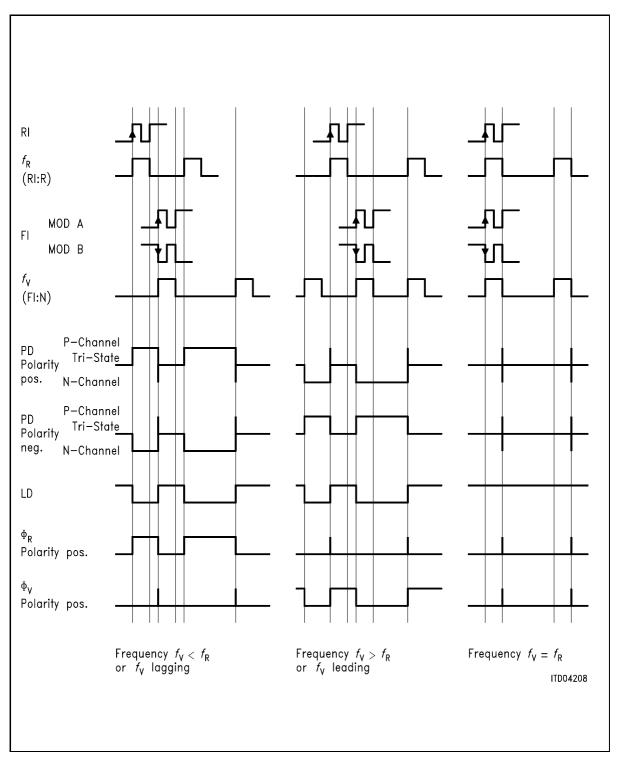

All pins are protected against ESD. Unused inputs without pullup resistors must be connected to either  $V_{\rm DD}$  or  $V_{\rm SS}$ .

# 3.2 Typical Supply Current $I_{DD}$

| Supply voltage                                                         | $V_{DD}$                                        | 3.3                  | 5                   | 5.5                  | V                    | Test conditions:                                                                                                                                          |

|------------------------------------------------------------------------|-------------------------------------------------|----------------------|---------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply current<br>singlemode HF<br>dual mode<br>standby 2<br>standby 1 | $I_{ m DD}$ $I_{ m DD}$ $I_{ m DD}$ $I_{ m DD}$ | 1.63<br>1.76<br>0.11 | 2.6<br>2.80<br>0.62 | 2.94<br>3.17<br>0.75 | mA<br>mA<br>mA<br>μA | $f_{\rm FI}$ = 50 MHz, $V_{\rm FI}$ = 150 mVrms<br>$f_{\rm RI}$ = 10 MHz, $V_{\rm RI}$ = 150 mVrms<br>$I_{\rm PD}$ = 0.25 mA, $I_{\rm ref}$ = 100 $\mu$ A |

### **Electrical Characteristics**

### 3.3 AC/DC Characteristics

| Parameter | Symbol | Limit Values   |  |  | Unit | Test Condition |

|-----------|--------|----------------|--|--|------|----------------|

|           |        | min. typ. max. |  |  |      |                |

|           |        |                |  |  |      |                |

## Input Signals DA, CLK, EN (with internal pull-up resistors)

| H-input voltage | $V_{IH}$ | $0.7~V_{ m DD}$ | $V_{DD}$        | V  |                                         |

|-----------------|----------|-----------------|-----------------|----|-----------------------------------------|

| L-input voltage | $V_{IL}$ | 0               | 0.3 $V_{ m DD}$ | V  |                                         |

| Input capacity  | $C_{I}$  |                 | 5               | pF |                                         |

| H-input current | $I_{H}$  |                 | 10              | μΑ | $V_{\rm I} = V_{\rm DD} = 5.5  {\rm V}$ |

| L-input current | $I_{L}$  | - 300           |                 | μΑ | $V_1 = GND$                             |

Further information about timing see at page 25 and 26

### **Input Signal RI**

| Input voltage   | $V_1$   | 100  |    | mVrms | $f = 4 \dots 100 \text{ MHz},$                       |

|-----------------|---------|------|----|-------|------------------------------------------------------|

|                 |         |      |    |       | $V_{\rm DD}$ =4.5 V                                  |

| Input voltage   | $V_1$   | 100  |    | mVrms | $f = 4 \dots 22 \text{ MHz}, V_{DD} = 3.3 \text{ V}$ |

| Slew rate       |         | 2.5  |    | V/μs  | $V_{\rm DD} = 3.3 \dots 5.5  \rm V$                  |

| Input capacity  | $C_1$   |      | 3  | pF    |                                                      |

| H-input current | $I_{H}$ |      | 30 | μΑ    | $V_{\rm I} = V_{\rm DD} = 5.5  {\rm V}$              |

| L-input current | $I_{L}$ | - 30 |    | μΑ    | $V_1 = GND$                                          |

|                 | 1       |      |    | l     |                                                      |

## Input Signal FI (dual mode)

| Input voltage   | $V_1$   | 180  |    | mVrms | $f = 4 \dots 65 \text{ MHz}, V_{DD} = 4.5 \text{ V}$ |

|-----------------|---------|------|----|-------|------------------------------------------------------|

| Input voltage   | $V_1$   | 180  |    | mVrms | $f = 4 \dots 30 \text{ MHz}, V_{DD} = 3.3 \text{ V}$ |

| Input voltage   | $V_1$   | 50   |    | mVrms | $f$ = 10 30 MHz, $V_{\rm DD}$ = 3.3 V                |

| Slew rate       |         | 4    |    | V/μs  | $V_{\rm DD} = 3.3 \dots 5.5 \text{ V}$               |

| Input capacity  | $C_{I}$ |      | 3  | pF    |                                                      |

| H-input current | $I_{H}$ |      | 30 | μΑ    | $V_{\rm I} = V_{\rm DD} = 5.5 \ { m V}$              |

| L-input current | $I_{L}$ | - 30 |    | μΑ    | $V_{\rm I} = {\sf GND}$                              |

## Input Signal FI (single HF-mode)

|                 | -       |      |    | 5     |                                                       |

|-----------------|---------|------|----|-------|-------------------------------------------------------|

| Input voltage   | $V_1$   | 200  |    | mVrms | $f = 4 \dots 220 \text{ MHz}, V_{DD} = 4.5 \text{ V}$ |

| Input voltage   | $V_1$   | 20   |    | mVrms | $f = 4 \dots 120 \text{ MHz}, V_{DD} = 3.3 \text{ V}$ |

| Input voltage   | $V_1$   | 50   |    | mVrms | $f$ = 10 50 MHz, $V_{DD}$ = 4.5 V                     |

| Slew rate       |         | 2.5  |    | V/μs  | $V_{\rm DD} = 3.3 \dots 5.5 \text{ V}$                |

| Input capacity  | $C_{I}$ |      | 3  | pF    |                                                       |

| H-input current | $I_{H}$ |      | 30 | μΑ    | $V_{\rm I} = V_{\rm DD} = 5.5  {\rm V}$               |

| L-input current | $I_{L}$ | - 30 |    | μΑ    | $V_{\rm I} = {\sf GND}$                               |

|                 |         |      |    |       |                                                       |

### PMB 2306R/PMB2306T

### **Electrical Characteristics**

| Parameter                        | eter Symbol |      | Limit Values |      |       | Test Condition                                       |  |  |

|----------------------------------|-------------|------|--------------|------|-------|------------------------------------------------------|--|--|

|                                  |             | min. | typ.         | max. |       |                                                      |  |  |

| Input Signal FI (single LF-mode) |             |      |              |      |       |                                                      |  |  |

| Input voltage                    | $V_1$       | 100  |              |      | mVrms | $f = 4 \dots 90 \text{ MHz}, V_{DD} = 4.5 \text{ V}$ |  |  |

| Input voltage                    | $V_1$       | 100  |              |      | mVrms | $f = 4 \dots 35 \text{ MHz}, V_{DD} = 3.3 \text{ V}$ |  |  |

| Slew rate                        |             | 2.5  |              |      | V/μs  | $V_{\rm DD} = 3.3 \dots 5.5  \rm V$                  |  |  |

| Input capacity                   | $C_{I}$     |      |              | 3    | pF    |                                                      |  |  |

| H-input current                  | $I_{H}$     |      |              | 30   | μA    | $V_{\rm I} = V_{\rm DD} = 5.5  {\rm V}$              |  |  |

| L-input current                  | $I_L$       | - 30 |              |      | μΑ    | $V_{\rm I} = {\sf GND}$                              |  |  |

## Output Current $I_{PD}$

| $I_{PROG}$ | <b>- 20 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 20 %                                               | mA                                                   |                                                      |

|------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| $I_{PROG}$ | <b>- 20 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 20 %                                               | mA                                                   |                                                      |

| $I_{PROG}$ | <b>- 20 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 20 %                                               | mA                                                   | $V_{\rm DD} = 4.5 \dots 5.5  \rm V$                  |

| $I_{PROG}$ | <b>- 20 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 20 %                                               | mA                                                   | $V_{PD} = V_{DD}/2$                                  |

| -          | <b>- 20 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 20 %                                               | mA                                                   | $I_{REF}$ = 100 $\muA$                               |

| -          | <b>- 10 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 10 %                                               | mA                                                   |                                                      |

| 7          | <b>- 10 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 10 %                                               | mA                                                   |                                                      |

| -          | <b>- 10 %</b>                                                     |                                                                                                                                                                                                                                                                                                   | + 10 %                                               | mA                                                   |                                                      |

| $/I_{PD}/$ |                                                                   | 0.1*                                                                                                                                                                                                                                                                                              | 50                                                   | nA                                                   | $V_{\rm DD} = 5.5  \rm V$                            |

|            |                                                                   |                                                                                                                                                                                                                                                                                                   |                                                      |                                                      |                                                      |

|            |                                                                   |                                                                                                                                                                                                                                                                                                   |                                                      |                                                      |                                                      |

|            | $I_{PROG}$ $I_{PROG}$ $I_{PROG}$ $I_{PROG}$ $I_{PROG}$ $I_{PROG}$ | $\begin{array}{cccc} I_{\text{PROG}} & & -20 \ \% \\ I_{\text{PROG}} & & -10 \ \% \\ I_{\text{PROG}} & & -10 \ \% \\ I_{\text{PROG}} & & -10 \ \% \\ \end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

# Output Tolerances $I_{\mathtt{PD}}$

| $\Delta I_{	extsf{PD}}$ / $I_{	extsf{PROG}}$ | - 20 % |     | + 3 % | $V_{\rm PD} = V_{\rm DD}/2, \ V_{\rm DD} = 3.3 \ {\rm V}$ |

|----------------------------------------------|--------|-----|-------|-----------------------------------------------------------|

| $\DeltaI_{ m PD}$ / $I_{ m PROG}$            |        | ±4% |       | $V_{PD} = 1 \dots 4 \text{ V}, V_{DD} = 5 \text{ V}$      |

## Input Voltage MFO2 (internal charge pump mode)

| Reference voltage | $V_{REF}$ | 0.9 | 1.1 | 1.3 | V | $V_{\rm DD}$ = 4.5 5.5 V, |

|-------------------|-----------|-----|-----|-----|---|---------------------------|

|                   |           |     |     |     |   | $I_{REF}$ = 100 $\muA$    |

### PMB2306R/PMB2306T

### **Electrical Characteristics**

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

## Output Signal MFO1 (push pull)

| H-output voltage | $V_{QH}$ | $V_{\rm DD}$ – 1 |     |    | V  | $V_{\rm DD} = 4.5 \dots 5.5  \text{V},$                           |

|------------------|----------|------------------|-----|----|----|-------------------------------------------------------------------|

|                  |          |                  |     |    |    | $I_{OH}$ = 2 mA                                                   |

| L-output voltage | $V_{QL}$ |                  |     | 1  | V  | $V_{\rm DD} = 4.5 \dots 5.5 \text{ V}, I_{\rm QL} = 2 \text{ mA}$ |

| H-output voltage | $V_{QH}$ | $V_{DD}$ – 1     |     |    | V  | $V_{\rm DD}$ = 3.3 V, $I_{\rm QH}$ = 1.2 mA                       |

| L-output voltage | $V_{QL}$ |                  |     | 1  | V  | $V_{\rm DD}$ = 3.3 V, $I_{\rm QL}$ = 1.2 mA                       |

| Rise time        | $t_{R}$  |                  | 2.5 | 10 | ns | $V_{\rm DD} = 4.5 \dots 5.5 \text{ V}, C_{\rm I} = 10 \text{ pF}$ |

| Fall time        | $t_{F}$  |                  | 2.0 | 10 | ns | $V_{\rm DD}$ = 4.5 5.5 V, $C_{\rm I}$ = 10 pF                     |

| Rise time        | $t_{R}$  |                  | 4.0 | 10 | ns | $V_{\rm DD}$ = 3.3 V, $C_{\rm I}$ = 10 pF                         |

| Fall time        | $t_{F}$  |                  | 2.5 | 10 | ns | $V_{\rm DD}$ = 3.3 V, $C_{\rm I}$ = 10 pF                         |

## Output Signal MFO2 (push pull)

| H-output voltage | $V_{QH}$ | $V_{\rm DD}$ – 1 |   |    | V  | $V_{\rm DD} = 4.5 \dots 5.5  \text{V},$       |

|------------------|----------|------------------|---|----|----|-----------------------------------------------|

|                  |          |                  |   |    |    | $I_{\text{QH}} = 2 \text{ mA}$                |

| L-output voltage | $V_{QL}$ |                  |   | 1  | V  | $V_{\rm DD}$ = 4.5 5.5 V, $I_{\rm QL}$ = 2 mA |

| H-output voltage | $V_{QH}$ | $V_{\rm DD}$ – 1 |   |    | V  | $V_{\rm DD}$ = 3.3 V, $I_{\rm QH}$ = 1.2 mA   |

| L-output voltage | $V_{QL}$ |                  |   | 1  | V  | $V_{\rm DD}$ = 3.3 V, $I_{\rm QL}$ = 1.2 mA   |

| Rise time        | $t_{R}$  |                  | 2 | 10 | ns | $V_{\rm DD}$ = 4.5 5.5 V, $C_{\rm I}$ = 10 pF |

| Fall time        | $t_{F}$  |                  | 2 | 10 | ns | $V_{\rm DD}$ = 4.5 5.5 V, $C_{\rm I}$ = 10 pF |

| Rise time        | $t_{R}$  |                  | 3 | 10 | ns | $V_{\rm DD}$ = 3.3 V, $C_{\rm I}$ = 10 pF     |

| Fall time        | $t_{F}$  |                  | 3 | 10 | ns | $V_{\rm DD}$ = 3.3 V, $C_{\rm I}$ = 10 pF     |

## Output Signal LD (n-channel open drain)

| L-output voltage | $V_{QL}$ |     | 0.4 | V  | $V_{\rm DD} = 4.5 \dots 5.5  \text{V},$                           |

|------------------|----------|-----|-----|----|-------------------------------------------------------------------|

|                  |          |     |     |    | $I_{\rm QL}$ = 0.5 mA                                             |

| L-output voltage | $V_{QL}$ |     | 0.4 | V  | $V_{\rm DD}$ = 3.3 V, $I_{\rm QL}$ = 0.5 mA                       |

| Fall time        | $t_{F}$  | 3   | 10  | ns | $V_{\rm DD} = 4.5 \dots 5.5 \text{ V}, C_{\rm I} = 10 \text{ pF}$ |

| Fall time        | $t_{F}$  | 4.5 | 10  | ns | $V_{\rm DD}$ = 3.3 V, $C_{\rm I}$ = 10 pF                         |

### PMB 2306R/PMB2306T

### **Electrical Characteristics**

| Parameter S | Symbol | Limit Values |      | Unit | Test Condition |  |

|-------------|--------|--------------|------|------|----------------|--|

|             |        | min.         | typ. | max. |                |  |

## Output Signal MOD (push-pull)

| 4    |

|------|

|      |

| ١    |

| 5 pF |

| 5 pF |

| 5 pF |

|      |

| 5 pF |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| 5 5  |

### **Electrical Characteristics**

### **Equivalent I/O Schematics**

### **Electrical Characteristics**

### Equivalent I/O Schematics (cont'd)

**Pulse Diagram**

### **Electrical Characteristics**

# **Serial Control Data Input Timing**

| Parameter                      | Symbol           | Limit Values |      | Unit | Test Condition        |

|--------------------------------|------------------|--------------|------|------|-----------------------|

|                                |                  | min.         | max. |      |                       |

| Clock frequency                | $f_{CL}$         |              | 12   | MHz  | V <sub>DD</sub> =3.3V |

| H-pulsewidth (CL)              | $t_{WHCL}$       | 40           |      | ns   |                       |

| Data setup                     | $t_{	extsf{DS}}$ | 20           |      | ns   |                       |

| Setup time clock-enable        | $t_{\sf CLE}$    | 20           |      | ns   |                       |

| Setup time enable-clock        | $t_{ECL}$        | 20           |      | ns   |                       |

| H-pulsewidth (enable)          | $t_{WHEN}$       | 40           |      | ns   |                       |

| Rise, fall time                | $t_{R},\ t_{F}$  |              | 10   | μs   |                       |

| Propagation delay time EN-PORT | $t_{DEP}$        |              | 1    | μs   |                       |

Input Sensitivity Signal FI (single HF-mode)

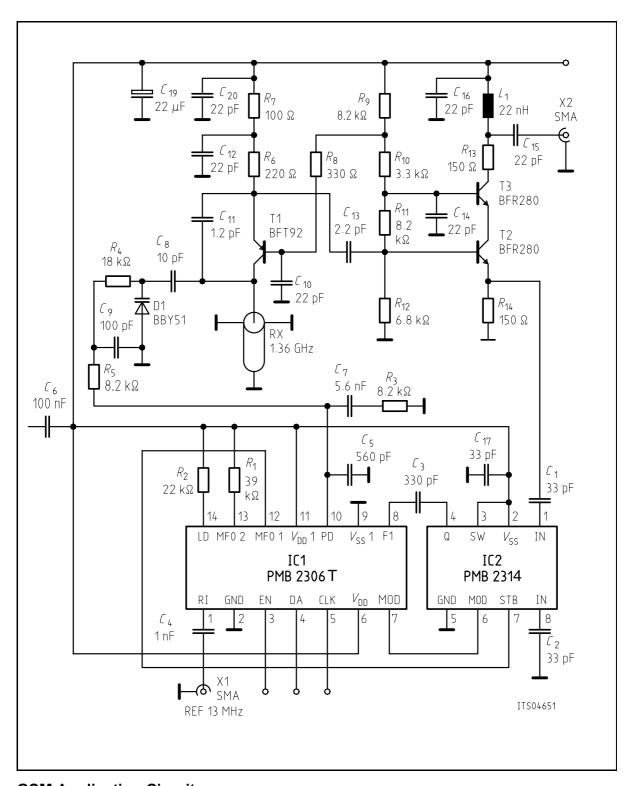

**GSM** Application Circuit

| List of Components                                             |                                                                                                                                                                                                                                                    |                                                                                                        |                                                                                              |                                                                                                                                                                                                                             |                                                                    |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| Item                                                           | <b>Quantity Reference</b>                                                                                                                                                                                                                          |                                                                                                        | Part                                                                                         |                                                                                                                                                                                                                             |                                                                    |  |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                      | 1 R <sub>7</sub> 2 R <sub>13</sub> , R <sub>14</sub> 1 R <sub>6</sub> 1 R <sub>8</sub> 1 R <sub>10</sub> 1 R <sub>12</sub> 4 R <sub>9</sub> , R <sub>3</sub> , R <sub>5</sub> , R <sub>11</sub> 1 R <sub>4</sub> 1 R <sub>2</sub> 1 R <sub>2</sub> | 100 Ω<br>150 Ω<br>220 Ω<br>330 Ω<br>3.3 kΩ<br>6.8 kΩ<br>8.2 kΩ<br>18 kΩ<br>22 kΩ<br>39 kΩ              | SMD/0805<br>SMD/0805<br>SMD/0805<br>SMD/0805<br>SMD/0805<br>SMD/0805<br>SMD/0805<br>SMD/0805 | 5 B54102-A1101-K60<br>5 B54102-A1151-J60<br>5 B54102-A1221-J60<br>6 B54102-A1331-J60<br>6 B54102-A1332-J60<br>6 B54102-A1682-J60<br>6 B54102-A1822-J60<br>6 B54102-A1183-J60<br>6 B54102-A1223-J60<br>6 B54102-A1393-J60    | S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M        |  |  |  |  |

| 11                                                             | 1 <i>L</i> <sub>1</sub>                                                                                                                                                                                                                            | 22 nH                                                                                                  | SIMID 01                                                                                     | B82412-A3220-M                                                                                                                                                                                                              | S+M                                                                |  |  |  |  |

| 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 | 1 $C_{11}$<br>1 $C_{13}$<br>1 $C_{8}$<br>6 $C_{20}$ , $C_{10}$ , $C_{12}$ , $C_{14}$ , $C_{15}$ , $C_{16}$<br>3 $C_{17}$ , $C_{1}$ , $C_{2}$<br>1 $C_{9}$<br>1 $C_{3}$<br>1 $C_{5}$<br>1 $C_{7}$<br>1 $C_{6}$<br>1 $C_{19}$                        | 1.2 pF<br>2.2 pF<br>10 pF<br>22 pF<br>33 pF<br>100 pF<br>330 pF<br>560 pF<br>5.6 nF<br>100 nF<br>22 μF | COG/0805<br>COG/0805<br>COG/0805<br>COG/0805<br>COG/0805<br>COG/0805                         | 5 B37940-K5010-C262<br>5 B37940-K5020-C262<br>5 B37940-K5100-J62<br>5 B37940-K5220-J62<br>5 B37940-K5330-J62<br>5 B37940-K5101-J62<br>5 B37940-K5561-J62<br>6 B37940-K5562-J62<br>8 B37950-K5104-K62<br>8 B45196-E3226-+409 | S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M<br>S+M |  |  |  |  |

| 23<br>24<br>25                                                 | 1 D1<br>2 T3, T2<br>1 T1                                                                                                                                                                                                                           | BBY 51<br>BFR 280<br>BFT 92                                                                            |                                                                                              | Q62702-B631<br>Q62702-F1298<br>Q62702-F1062                                                                                                                                                                                 | SIEMENS<br>SIEMENS<br>SIEMENS                                      |  |  |  |  |

| 26<br>27<br>28<br>29                                           | 1 C <sub>4</sub><br>2 X2, X1<br>1 RX<br>1 IC1<br>1 IC2                                                                                                                                                                                             | 1,0 nF<br>SMA<br>1.3 GHz<br>PMB 2306T P-<br>PMB 2306T P-<br>PMB 2314 P-<br>PMB 2314 P-                 | DSO-14<br>DSO-14<br>DSO-8                                                                    | B37949-K5102-J62<br>Connector<br>B69610-G1307-A412<br>Q67100-H6423<br>Q67106-H6423(T+R)<br>Q67000-A6121<br>Q67006-A6121(T+R)                                                                                                | S+M S+M SIEMENS SIEMENS SIEMENS SIEMENS                            |  |  |  |  |

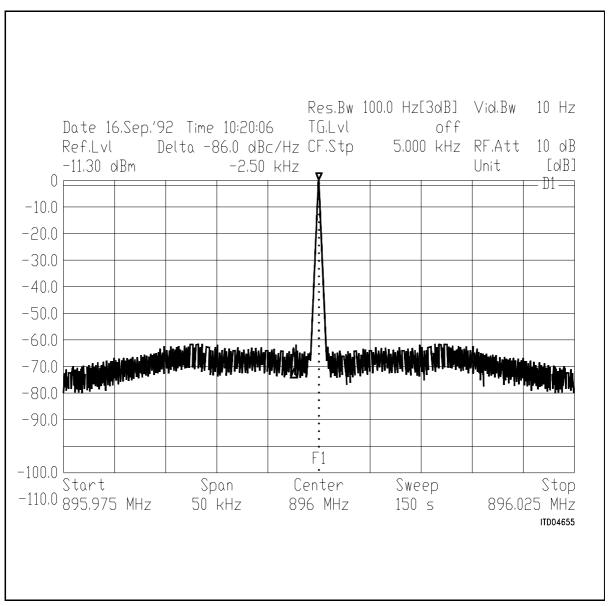

**Phase Noise Close to the Carrier**

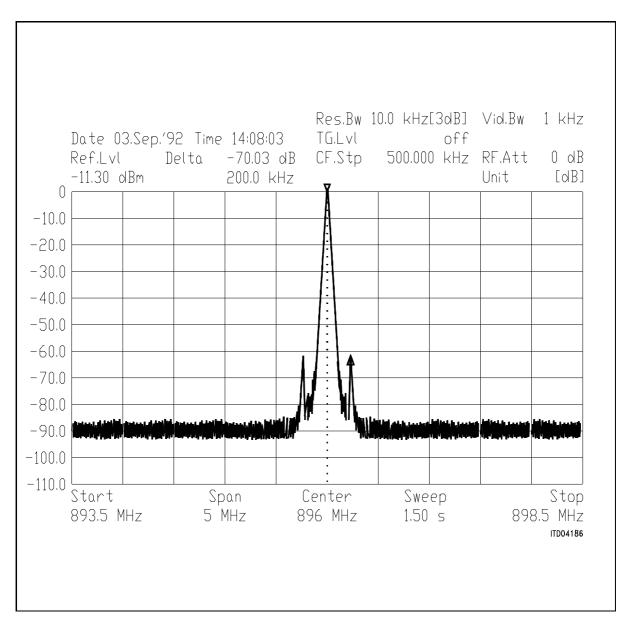

**Spectrum at Lower End of GSM TX Board (Mobile)**

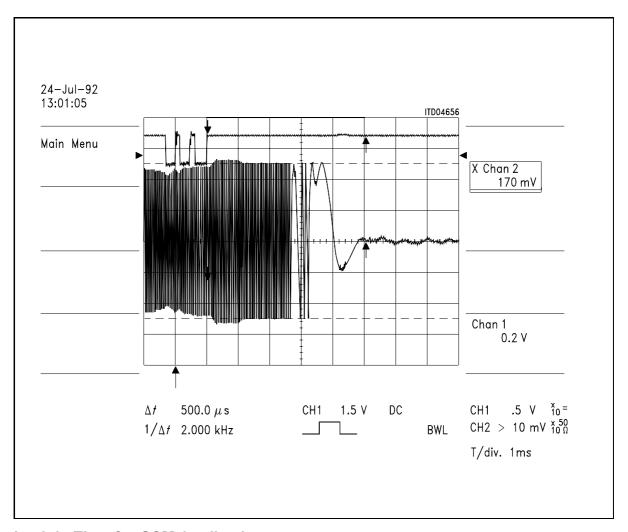

**Lock-In Time for GSM Application**

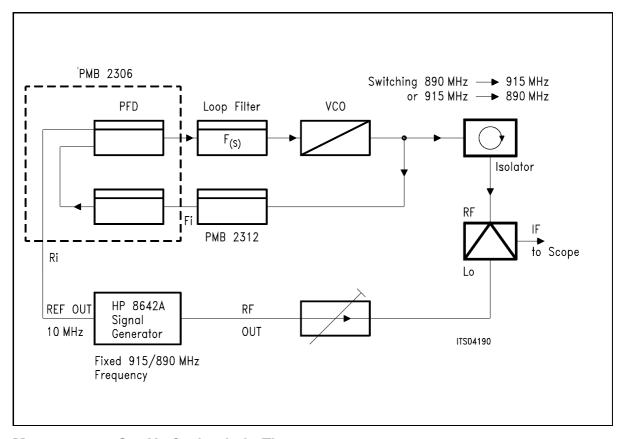

**Measurement Set-Up for Lock- In Time**

**Package Outlines**

02.97

### 4 Package Outlines

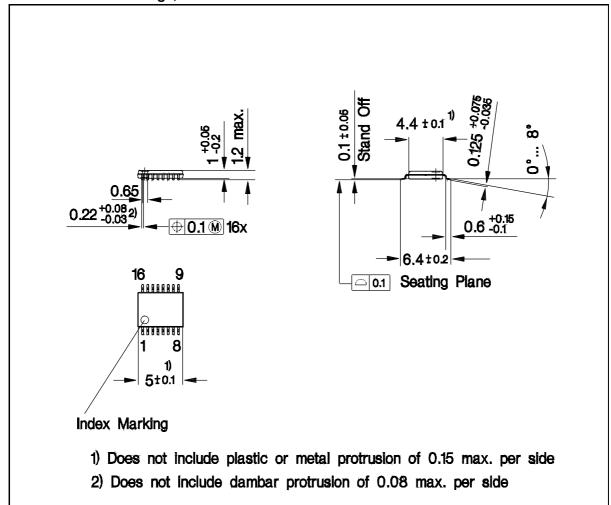

### 4.1 Plastic-Package, P-TSSOP-16

### **Package Outlines**

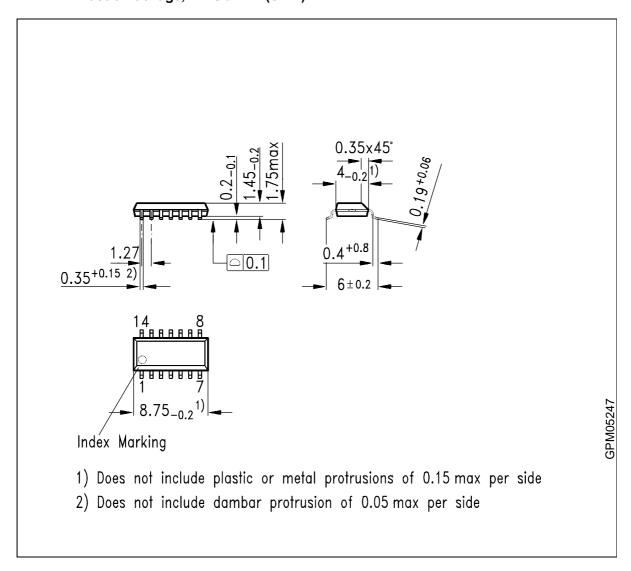

### 4.2 Plastic-Package, P-DSO-14-1(SMD)

### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm