查询HA1-2546/883供应商

## intersil

## July 1994

## Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- High Speed Voltage Output...... 300V/μs (Min)

- 1.6% (Typ)

- Input Bias Currents ...... 5µA (Max) **1.2μA (Typ)** • Wide Signal Bandwidth ...... 30MHz (Typ) Wide Control Bandwidth ..... 17MHz (Typ) Gain Flatness to 5MHz.....0.10dB (Typ)

- Applications

- **Military Avionics**

- Missile Guidance Systems

- Medical Imaging Displays

- **Video Mixers**

- Sonar AGC Processors

- **Radar Signal Conditioning**

- Voltage Controlled Amplifier

- **Vector Generator**

## Description

The HA-2546/883 is a monolithic, high speed, two guadrant, analog multiplier constructed in the Intersil Dielectrically Isolated High Frequency Process. The HA-2546/883 has a voltage output with a 30MHz signal bandwidth, 300V/µs slew rate and a 17MHz control input bandwidth. High bandwidth and slew rate make this part an ideal component for use in video systems. The suitability for precision video applications is demonstrated further by the 0.1dB gain flatness at 5MHz, 1.6% multiplication error, -52dB feedthrough and differential inputs with 1.2µA bias currents. The HA-2546/883 also has low differential gain (0.1% typ.) and phase (0.1° typ.) errors.

捷多邦,专业PCB打样工厂,24小时加急出货

HA2546/883

Wideband Two Quadrant Analog

Multiplier (Voltage Output)

The HA-2546/883 is well suited for AGC circuits as well as mixer applications for sonar, radar, and medical imaging equipment. The voltage output of the HA-2546/883 simplifies many designs by eliminating the current-to-voltage conversion stage required for current output multipliers.

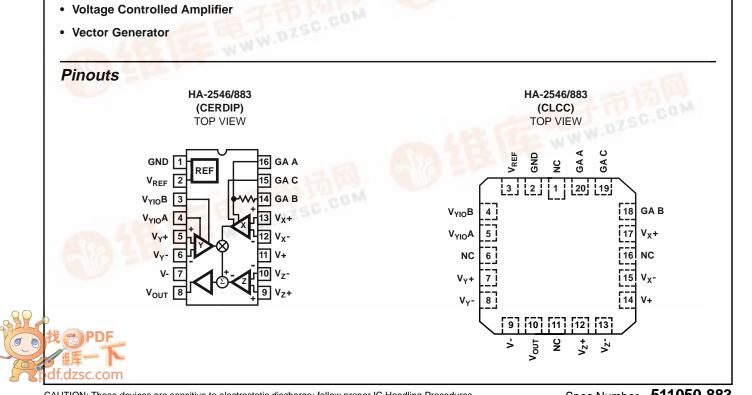

## Ordering Information

| PART NUMBER  | TEMPERATURE<br>RANGE | PACKAGE             |

|--------------|----------------------|---------------------|

| HA1-2546/883 | -55°C to +125°C      | 16 Lead CerDIP      |

| HA4-2546/883 | -55°C to +125°C      | 20 Lead Ceramic LCC |

## Specifications HA2546/883

| Absolute Maximum Ratings                             | Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $\begin{array}{c} \mbox{Thermal Resistance} & \theta_{JA} & \theta_{JC} \\ \mbox{CerDIP Package} & & 80^{\circ}\mbox{C/W} & 25^{\circ}\mbox{C/W} \\ \mbox{Ceramic LCC} & & 61^{\circ}\mbox{C/W} & 12^{\circ}\mbox{C/W} \\ \mbox{Maximum Package Power Dissipation} \\ \mbox{CerDIP Package at +75^{\circ}\mbox{C}} & & 1.25\mbox{W} \\ \mbox{Ceramic LCC Package at +75^{\circ}\mbox{C}} & & 1.64\mbox{W} \\ \mbox{Package Power Dissipation Derating Factor above +75^{\circ}\mbox{C}} \\ \mbox{CerDIP Package} & & 12\mbox{mW/}^{\circ}\mbox{C} \\ \mbox{Ceramic LCC Package} & & 12\mbox{mW/}^{\circ}\mbox{C} \\ \mbox{Ceramic LCC Package} & & 16\mbox{mW/}^{\circ}\mbox{C} \\ \end{array}$ |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## **Operating Conditions**

#### TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Tested at:  $V_{SUPPLY} = \pm 15V$ ,  $R_{LOAD} = 1k\Omega$ ,  $C_{LOAD} = 50pF$ , Unless Otherwise Specified.

|                                        |                                   |                                   | GROUP A       |               | LIMITS |     |       |

|----------------------------------------|-----------------------------------|-----------------------------------|---------------|---------------|--------|-----|-------|

| PARAMETERS                             | SYMBOL                            | CONDITIONS                        | SUBGROU<br>PS | TEMPERATURE   | MIN    | мах | UNITS |

| Multiplication Error                   | ME                                | $V_{Y} = \pm 5V$                  | 1             | +25°C         | -3     | 3   | %FS   |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -5     | 5   | %FS   |

| Scale Factor Error                     | SF                                |                                   | 1             | +25°C         | -5     | 5   | %     |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -5     | 5   | %     |

| Common Mode Range                      | +CMR                              |                                   | 1             | +25°C         | 5      | -   | V     |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | 5      | -   | V     |

|                                        | -CMR                              |                                   | 1             | +25°C         | -      | -5  | V     |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -      | -5  | V     |

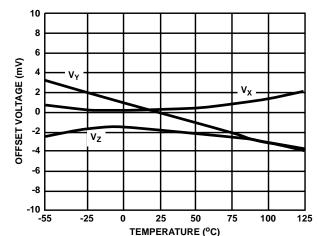

| Input Offset Voltage (V <sub>Y</sub> ) | $V_{IO}(V_Y)$                     | $V_{CM} = 0V$                     | 1             | +25°C         | -10    | 10  | mV    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -15    | 15  | mV    |

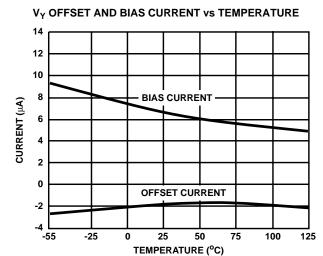

| Input Bias Current (V <sub>Y</sub> )   | I <sub>B</sub> (V <sub>Y</sub> )  | $V_{CM} = 0V$                     | 1             | +25°C         | -15    | 15  | μΑ    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -20    | 20  | μΑ    |

| Input Offset Current (V <sub>Y</sub> ) | I <sub>IO</sub> (V <sub>Y</sub> ) | $V_{CM} = 0V$                     | 1             | +25°C         | -2     | 2   | μΑ    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -3     | 3   | μΑ    |

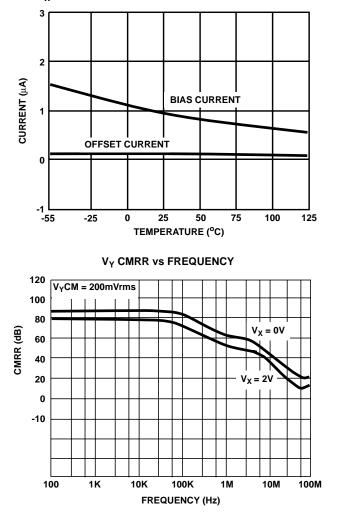

| Common Mode (V <sub>Y</sub> )          | +CMRR(V <sub>Y</sub> )            | $V_{Y} = 0$ to +5V, $V_{X} = +2V$ | 1             | +25°C         | 60     | -   | dB    |

| Rejection Ratio                        |                                   |                                   | 2, 3          | +125°C, -55°C | 60     | -   | dB    |

|                                        | -CMRR(V <sub>Y</sub> )            | $V_{Y} = 0$ to -5V, $V_{X} = +2V$ | 1             | +25°C         | 60     | -   | dB    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | 60     | -   | dB    |

| Input Offset Voltage (V <sub>X</sub> ) | V <sub>IO</sub> (V <sub>X</sub> ) | $V_{CM} = 0V$                     | 1             | +25°C         | -2     | 2   | mV    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -15    | 15  | mV    |

| Input Bias Current (V <sub>X</sub> )   | I <sub>B</sub> (V <sub>X</sub> )  | $V_{CM} = 0V$                     | 1             | +25°C         | -2     | 2   | μΑ    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -5     | 5   | μΑ    |

| Input Offset Current (V <sub>X</sub> ) | I <sub>IO</sub> (V <sub>X</sub> ) | $V_{CM} = 0V$                     | 1             | +25°C         | -2     | 2   | μΑ    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -3     | 3   | μΑ    |

| Input Offset Voltage (V <sub>Z</sub> ) | V <sub>IO</sub> (V <sub>Z</sub> ) | $V_X = 0V, V_Y = 0V$              | 1             | +25°C         | -15    | 15  | mV    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -15    | 15  | mV    |

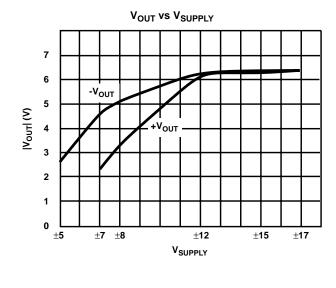

| Output Voltage Swing                   | +V <sub>OUT</sub>                 | $V_{Y} = +5V, V_{X} = +2.5V$      | 1             | +25°C         | 5      | -   | V     |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | 5      | -   | V     |

|                                        | -V <sub>OUT</sub>                 | $V_{Y} = -5V, V_{X} = +2.5V$      | 1             | +25°C         | -      | -5  | V     |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -      | -5  | V     |

| Output Current                         | +I <sub>OUT</sub>                 | $V_{Y} = +5V, V_{X} = +2.5V$      | 1             | +25°C         | 20     | - 1 | mA    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | 20     | - 1 | mA    |

|                                        | -I <sub>OUT</sub>                 | $V_{Y} = -5V, V_{X} = +2.5V$      | 1             | +25°C         | -      | -20 | mA    |

|                                        |                                   |                                   | 2, 3          | +125°C, -55°C | -      | -20 | mA    |

Cree Number 511050 992

## Specifications HA2546/883

## TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

Device Tested at:  $V_{SUPPLY} = \pm 15V$ ,  $R_{LOAD} = 1k\Omega$ ,  $C_{LOAD} = 50pF$ , Unless Otherwise Specified.

|                        |                  |                                              | GROUP A       |               | LIMITS |     |       |  |

|------------------------|------------------|----------------------------------------------|---------------|---------------|--------|-----|-------|--|

| PARAMETERS             | SYMBOL           | CONDITIONS                                   | SUBGROU<br>PS | TEMPERATURE   | MIN    | мах | UNITS |  |

| Power Supply Rejection | +PSRR            | $\Delta V_{S} = 3V, V + = +15V, V - = -15V,$ | 1             | +25°C         | 58     | -   | dB    |  |

| Ratio                  |                  | V+ = +12V, V- = -15V                         | 2, 3          | +125°C, -55°C | 58     | -   | dB    |  |

|                        | -PSRR            | $\Delta V_{S} = 3V, V + = +15V, V - = -15V,$ | 1             | +25°C         | 58     | -   | dB    |  |

|                        |                  | V+ = +15V, V- = -12V                         | 2, 3          | +125°C, -55°C | 58     | -   | dB    |  |

| Quiescent Power Supply | +I <sub>CC</sub> | $V_X = V_Y = 0V, I_{OUT} = 0mA$              | 1             | +25°C         | 29     | -   | mA    |  |

| Current                |                  |                                              | 2, 3          | +125°C, -55°C | 29     | -   | mA    |  |

|                        | -I <sub>CC</sub> | $V_X = V_Y = 0V, I_{OUT} = 0mA$              | 1             | +25°C         | -      | -29 | mA    |  |

|                        |                  |                                              | 2, 3          | +125°C, -55°C | -      | -29 | mA    |  |

## TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

Table 2 Intentionally Left Blank. See AC Specifications in Table 3.

#### TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

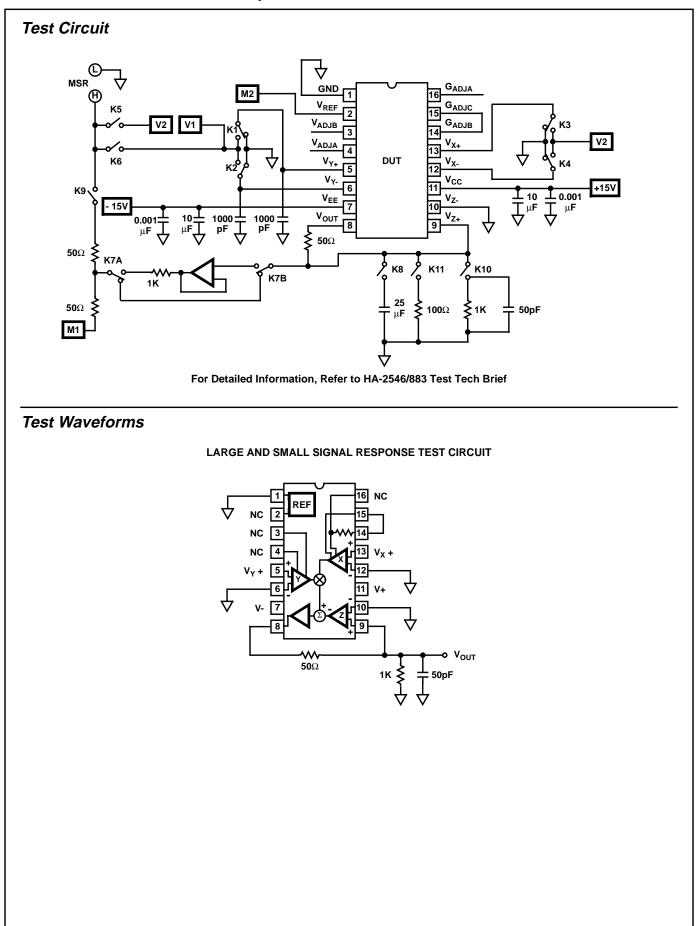

Device Tested at:  $V_{SUPPLY} = \pm 15V$ ,  $R_{LOAD} = 1k\Omega$ ,  $C_{LOAD} = 50pF$ , Unless Otherwise Specified.

|                      |                                        |                                                       |       |               | LIMITS |     |       |

|----------------------|----------------------------------------|-------------------------------------------------------|-------|---------------|--------|-----|-------|

| PARAMETER            | SYMBOL                                 | CONDITIONS                                            | NOTES | TEMPERATURE   | MIN    | MAX | UNITS |

| Slew Rate            | +SR                                    | $V_{OUT} = -5V$ to +5V, $V_X = 2V_{DC}$               | 1     | +25°C         | 300    | -   | V/µs  |

|                      |                                        |                                                       | 1     | +125°C, -55°C | 300    | -   | V/µs  |

|                      | -SR                                    | $V_{OUT}$ = +5V to -5V, $V_X$ = 2 $V_{DC}$            | 1     | +25°C         | 300    | -   | V/µs  |

|                      |                                        |                                                       | 1     | +125°C, -55°C | 300    | -   | V/µs  |

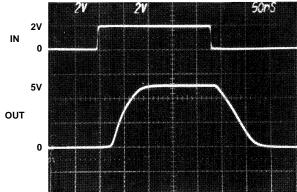

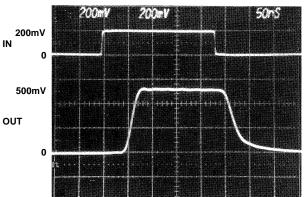

| Rise and Fall Time   | TR                                     | V <sub>OUT</sub> = -100mV to +100mV                   | 1, 3  | +25°C         | -      | 15  | ns    |

|                      |                                        | $V_X = 2V_{DC}$                                       | 1, 3  | +125°C, -55°C | -      | 17  | ns    |

|                      | TF V <sub>OUT</sub> = +100mV to -100mV | 1, 3                                                  | +25°C | -             | 15     | ns  |       |

|                      |                                        | $V_X = 2V_{DC}$                                       | 1, 3  | +125°C, -55°C | -      | 17  | ns    |

| Overshoot +O         |                                        | $V_{OUT} = -100 \text{mV} \text{ to } +100 \text{mV}$ | 1     | +25°C         | -      | 30  | %     |

|                      |                                        | $V_X = 2V_{DC}$                                       | 1     | +125°C, -55°C | -      | 30  | %     |

|                      | -OS                                    | $V_{OUT} = +100 \text{mV} \text{ to } -100 \text{mV}$ | 1     | +25°C         | -      | 30  | %     |

|                      |                                        | $V_X = 2V_{DC}$                                       | 1     | +125°C, -55°C | -      | 30  | %     |

| Full Power Bandwidth | FPBW                                   | $V_{PEAK} = 5V, V_X = 2V_{DC}$                        | 1, 2  | +25°C         | 9.5    | -   | MHz   |

|                      |                                        |                                                       | 1, 2  | +125°C, -55°C | 9.5    | -   | MHz   |

## NOTES:

1. Parameters listed in Table 3 are controlled via design or process parameters and are not directly tested at final production. These parameters are lab characterized upon initial design release, or upon design changes. These parameters are guaranteed by characterization based upon data from multiple production runs which reflect lot to lot and within lot variation.

2. Full Power Bandwidth guarantee based on Slew Rate measurement using FPBW = Slew Rate/ $(2\pi V_{PEAK})$ .

3. Measured between 10% and 90% points.

| TABLE 4. | ELECTRICAL | <b>TEST REQUIREMENTS</b> |  |

|----------|------------|--------------------------|--|

| IADEE 4. | LECONIOAL  |                          |  |

| MIL-STD-883 TEST REQUIREMENTS               | SUBGROUPS (SEE TABLE 1) |

|---------------------------------------------|-------------------------|

| Interim Electrical Parameters (Pre Burn-in) | 1                       |

| Final Electrical Test Parameters            | 1(Note 1), 2, 3         |

| Group A Test Requirements                   | 1, 2, 3                 |

| Groups C and D Endpoints                    | 1                       |

NOTE:

1. PDA applies to Subgroup 1 only.

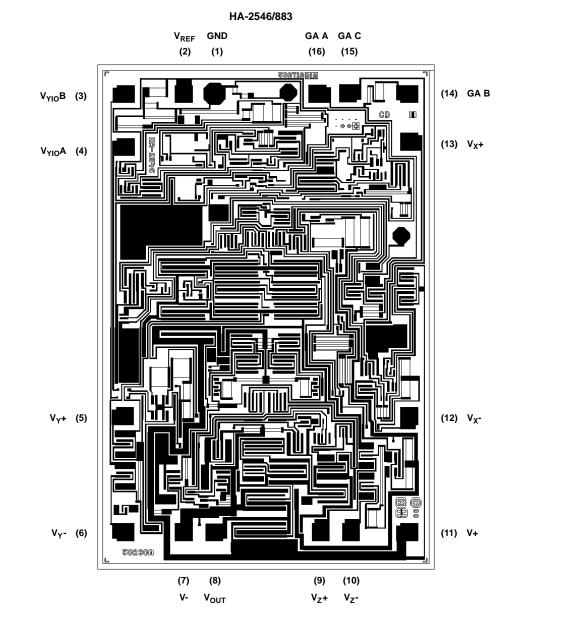

## **Die Characteristics**

## DIE DIMENSIONS:

79.9 mils x 119.7 mils x 19 mils  $\pm$  1 mils

## **METALLIZATION:**

Type: Al, 1%Cu Thickness: 16kÅ ± 2kÅ

## **GLASSIVATION:**

Type: Nitride  $(Si_3N_4)$  over Silox  $(SiO_2, 5\%$  Phos) Silox Thickness: 12kÅ ± 1.5kÅ Nitride Thickness: 3.5kÅ ± 1.5kÅ

## WORST CASE CURRENT DENSITY:

$0.72 \text{ x } 10^5 \text{ A/cm}^2$

## **TRANSISTOR COUNT: 87**

## Metallization Mask Layout

## Specifications HA2546/883

## HA2546/883

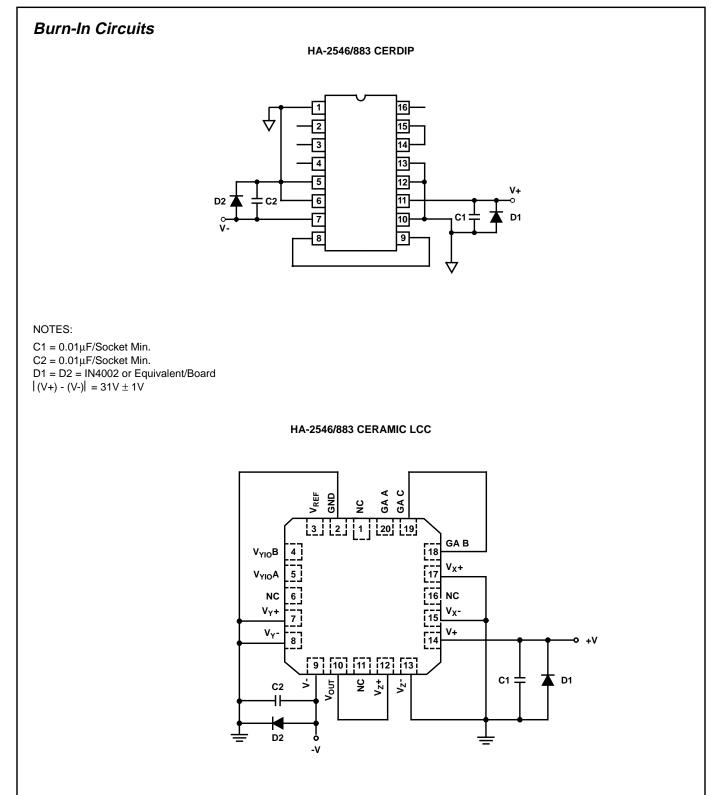

## NOTES:

$\begin{array}{l} C1=C2=0.01 \mu F/Socket \mbox{ Min.} \\ D1=D2=IN4002 \mbox{ or Equivalent/Board} \\ |\mbox{ (V+) - (V-)}| = 31 V \pm 1 V \end{array}$

HA2546/883

## HA2546/883

## NOTES:

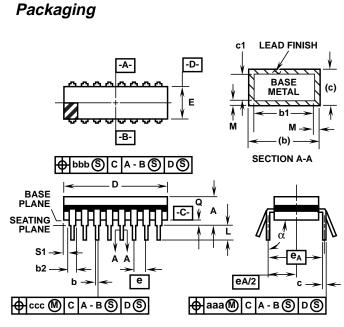

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- 2. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b1.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling Dimension: Inch.

- 11. Materials: Compliant to MIL-I-38535.

#### **F16.3** MIL-STD-1835 GDIP1-T16 (D-2, CONFIGURATION A) 16 LEAD DUAL-IN-LINE FRIT-SEAL CERAMIC PACKAGE

|        | INC             | HES              | MILLIM          |                  |       |  |

|--------|-----------------|------------------|-----------------|------------------|-------|--|

| SYMBOL | MIN             | MAX              | MIN             | MAX              | NOTES |  |

| A      | -               | 0.200            | -               | 5.08             | -     |  |

| b      | 0.014           | 0.026            | 0.36            | 0.66             | 2     |  |

| b1     | 0.014           | 0.023            | 0.36            | 0.58             | 3     |  |

| b2     | 0.045           | 0.065            | 1.14            | 1.65             | -     |  |

| b3     | 0.023           | 0.045            | 0.58            | 1.14             | 4     |  |

| С      | 0.008           | 0.018            | 0.20            | 0.46             | 2     |  |

| c1     | 0.008           | 0.015            | 0.20            | 0.38             | 3     |  |

| D      | -               | 0.840            | -               | 21.34            | 5     |  |

| E      | 0.220           | 0.310            | 5.59            | 7.87             | 5     |  |

| е      | 0.100           | BSC              | 2.54 BSC        |                  | -     |  |

| eA     | 0.300           | BSC              | 7.62            | BSC              | -     |  |

| eA/2   | 0.150           | BSC              | 3.81            | BSC              | -     |  |

| L      | 0.125           | 0.200            | 3.18            | 5.08             | -     |  |

| Q      | 0.015           | 0.060            | 0.38            | 1.52             | 6     |  |

| S1     | 0.005           | -                | 0.13            | -                | 7     |  |

| S2     | 0.005           | -                | 0.13            | -                | -     |  |

| α      | 90 <sup>0</sup> | 105 <sup>0</sup> | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |  |

| aaa    | -               | 0.015            | -               | 0.38             | -     |  |

| bbb    | -               | 0.030            | - 0.76          |                  | -     |  |

| CCC    | -               | 0.010            | -               | 0.25             | -     |  |

| М      | -               | 0.0015           | -               | 0.038            | 2     |  |

| N      | 1               | 6                | 16              |                  | 8     |  |

## HA2546/883

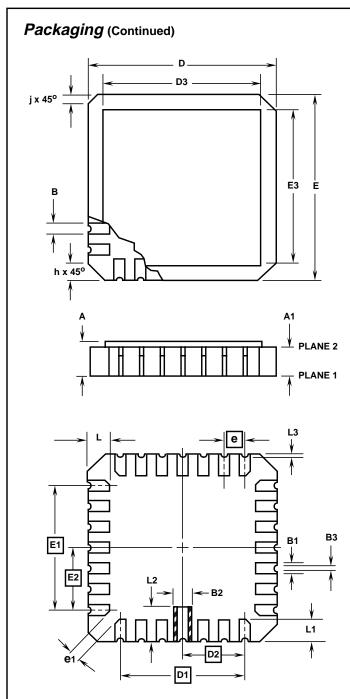

## J20.A MIL-STD-1835 CQCC1-N20 (C-2) 20 PAD METAL SEAL LEADLESS CERAMIC CHIP CARRIER

|        | INC   | HES   | MILLIM |      |       |

|--------|-------|-------|--------|------|-------|

| SYMBOL | MIN   | MAX   | MIN    | MAX  | NOTES |

| А      | 0.060 | 0.100 | 1.52   | 2.54 | 6, 7  |

| A1     | 0.050 | 0.088 | 1.27   | 2.23 | 7     |

| В      | -     | -     | -      | -    | 4     |

| B1     | 0.022 | 0.028 | 0.56   | 0.71 | 2, 4  |

| B2     | 0.072 | REF   | 1.83   | REF  | -     |

| B3     | 0.006 | 0.022 | 0.15   | 0.56 | -     |

| D      | 0.342 | 0.358 | 8.69   | 9.09 | -     |

| D1     | 0.200 | BSC   | 5.08   | BSC  | -     |

| D2     | 0.100 | BSC   | 2.54   | BSC  | -     |

| D3     | -     | 0.358 | -      | 9.09 | 2     |

| E      | 0.342 | 0.358 | 8.69   | 9.09 | -     |

| E1     | 0.200 | BSC   | 5.08   | BSC  | -     |

| E2     | 0.100 | BSC   | 2.54   | BSC  | -     |

| E3     | -     | 0.358 | -      | 9.09 | 2     |

| е      | 0.050 | BSC   | 1.27   | BSC  | -     |

| e1     | 0.015 | -     | 0.38   | -    | 2     |

| h      | 0.040 | REF   | 1.02   | REF  | 5     |

| j      | 0.020 | REF   | 0.51   | REF  | 5     |

| L      | 0.045 | 0.055 | 1.14   | 1.40 | -     |

| L1     | 0.045 | 0.055 | 1.14   | 1.40 | -     |

| L2     | 0.075 | 0.095 | 1.91   | 2.41 | -     |

| L3     | 0.003 | 0.015 | 0.08   | 0.38 | -     |

| ND     | Ę     | 5     | 5      |      | 3     |

| NE     | Ę     | 5     | 5      |      | 3     |

| N      | 2     | 0     | 20     |      | 3     |

NOTES:

- 1. Metallized castellations shall be connected to plane 1 terminals and extend toward plane 2 across at least two layers of ceramic or completely across all of the ceramic layers to make electrical connection with the optional plane 2 terminals.

- 2. Unless otherwise specified, a minimum clearance of 0.015 inch (0.381mm) shall be maintained between all metallized features (e.g., lid, castellations, terminals, thermal pads, etc.)

- Symbol "N" is the maximum number of terminals. Symbols "ND" and "NE" are the number of terminals along the sides of length "D" and "E", respectively.

- 4. The required plane 1 terminals and optional plane 2 terminals shall be electrically connected.

- 5. The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown on the drawing.

- 6. Chip carriers shall be constructed of a minimum of two ceramic layers.

- 7. Maximum limits allows for 0.007 inch solder thickness on pads.

- 8. Materials: Compliant to MIL-I-38535.

## **DESIGN INFORMATION**

# HA2546

August 1999

## Wideband Two Quadrant Analog Multiplier

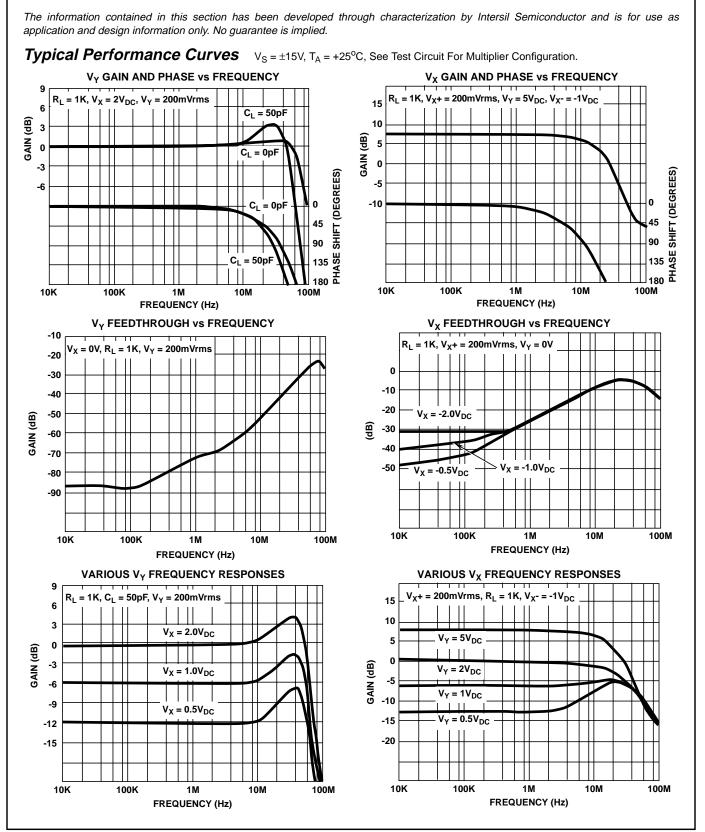

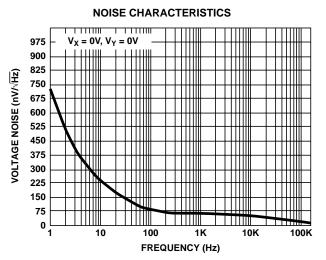

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

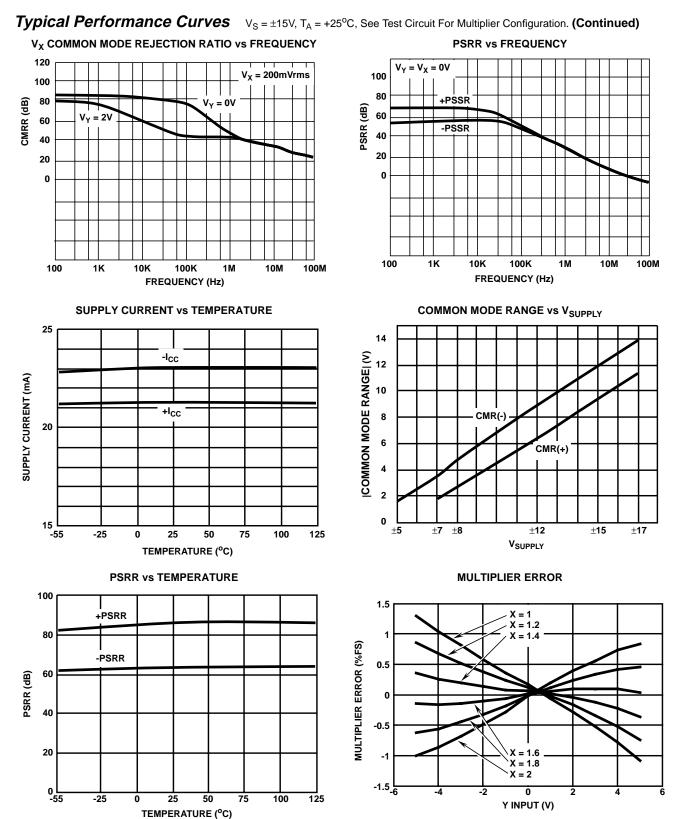

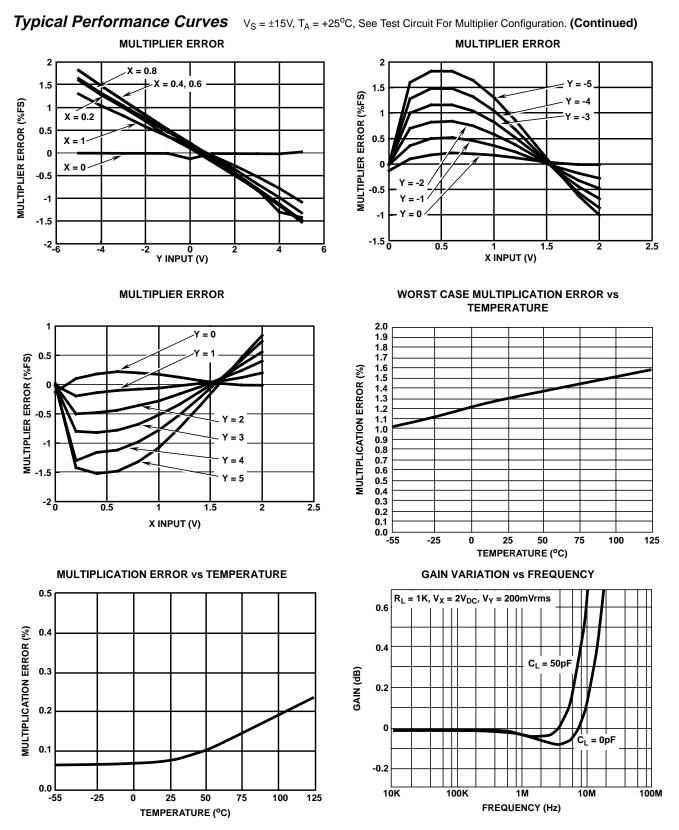

## **Typical Performance Curves** $V_{S} = \pm 15V$ , $T_{A} = +25^{\circ}C$ , See Test Circuit For Multiplier Configuration. (Continued)

**OFFSET VOLTAGE vs TEMPERATURE**

V<sub>x</sub> OFFSET AND BIAS CURRENT vs TEMPERATURE

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

## HA2546

## **DESIGN INFORMATION (Continued)**

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

#### **DESIGN INFORMATION (Continued)** The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied. **Typical Performance Curves** V<sub>S</sub> = ±15V, T<sub>A</sub> = +25°C, See Test Circuit For Multiplier Configuration. (Continued) SCALE FACTOR vs TEMPERATURE **OUTPUT VOLTAGE SWING vs LOAD RESISTANCE** 2.010 7.0 $f_0 = 10$ kHz, $V_X = 2V_{DC}$ , THD < 0.1% 2.008 6.0 = ±15 2.006 PEAK OUTPUT VOLTAGE = +12 5.0 2.004 V<sub>S</sub> = ±10 SCALE FACTOR 2.002 4.0 2.000 3.0 1.998 V<sub>S</sub> = ±8 1.996 2.0 1.994 1.0 1.992 0.0 └─ 10 1.990 75 100 125 -25 25 50 0 -55 100 1K 10K 100K TEMPERATURE (°C) LOAD RESISTANCE (Ω) **SLEW RATE vs TEMPERATURE RISE TIME vs TEMPERATURE** 500 24 22 20 V<sub>Y</sub> CHANNEL V<sub>X</sub> CHANNEL 400 18 SLEW RATE (V/µs) 16 RISE TIME (ns) 300 14 12 V<sub>Y</sub> CHANNEL 10 200 8 V<sub>x</sub> CHANNEL 6 100 4 2 0 0 -60 -40 -20 0 20 40 60 80 100 120 -60 -40 -20 0 20 40 60 80 100 120 **TEMPERATURE (°C)** TEMPERATURE (°C) SUPPLY CURRENT vs SUPPLY VOLTAGE 28 26 lcc 24 22 +I<sub>CC</sub> SUPPLY CURRENT (mA) 20 18 16 14 12 10 8 6 4 2 0 2 4 10 12 14 16 18 20 6 8 SUPPLY VOLTAGE (±V)

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

## Application Information

## **Theory of Operation**

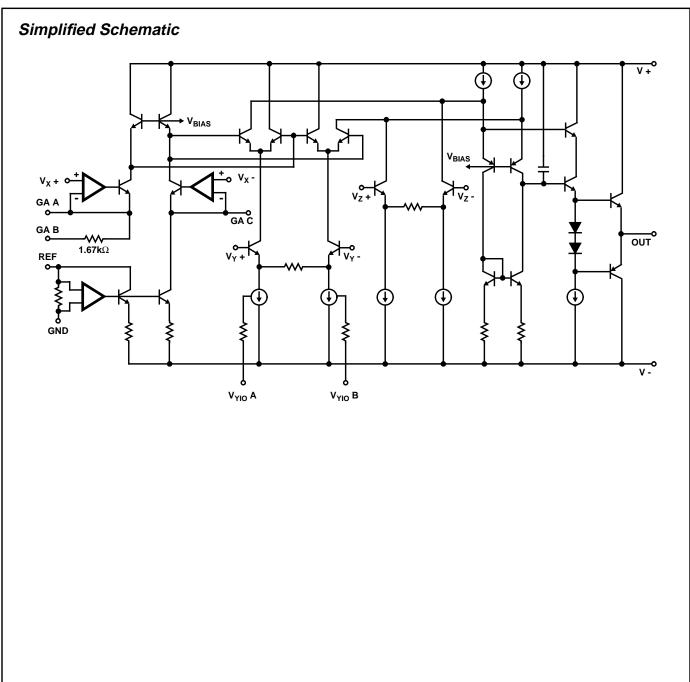

The HA-2546 is a two quadrant multiplier with the following three differential inputs; the signal channel,  $V_Y$ + and  $V_Y$ -, the control channel,  $V_X$ + and  $V_X$ -, and the summed channel,  $V_Z$ + and  $V_Z$ -, to complete the feedback of the output amplifier. The differential voltages of channel X and Y are converted to differential currents. These currents are then multiplied in a circuit similar to a Gilbert Cell multiplier, producing a differential current product. The differential voltage of the Z channel is converted into a differential current which then sums with the products currents. The differential "product/sum" currents are converted to a single-ended current and then converted to a voltage output by a transimpedance amplifier.

The open loop transfer equation for the HA-2546 is:

$$V_{OUT} = A \left[ \frac{(V_{X+} - V_{X-})(V_{Y+} - V_{Y-})}{SF} - (V_{Z+} - V_{Z-}) \right]$$

where;

A = Output Amplifier Open Loop Gain SF = Scale Factor  $V_X$ ,  $V_Y$ ,  $V_Z$  = Differential Inputs

The scale factor is used to maintain the output of the multiplier within the normal operating range of  $\pm$ 5V. The scale factor can be defined by the user by way of an optional external resistor, R<sub>EXT</sub>, and the Gain Adjust pins, Gain Adjust A (GA A), Gain Adjust B (GA B), and Gain Adjust C (GA C). The scale factor is determined as follows:

SF = 2, when GA B is shorted to GA C

- SF  $\cong$  1.2 R<sub>EXT</sub>, when R<sub>EXT</sub> is connected between GA A and GA C (R<sub>EXT</sub> is in  $k\Omega)$

- $\label{eq:star} SF\cong 1.2 \;(R_{EXT} + 1.667 k\Omega), \mbox{ when } R_{EXT} \mbox{ is } \\ \mbox{ connected to GA B and GA C } (R_{EXT} \mbox{ is in } k\Omega) \label{eq:star}$

The scale factor can be adjusted from 2 to 5. It should be noted that any adjustments to the scale factor will affect the AC performance of the control channel,  $V_X$ . The normal input operating range of  $V_X$  is equal to the scale factor voltage.

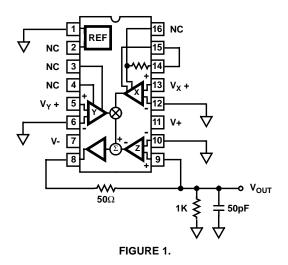

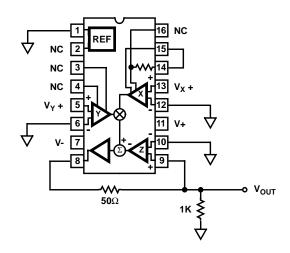

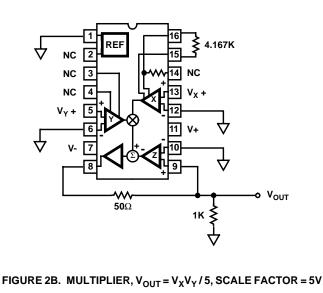

The typical multiplier configuration is shown in Figure 1. The ideal transfer function for this configuration is:

$$V_{OUT} = \begin{cases} \frac{(V_{X+} - V_{X-})(V_{Y+} - V_{Y-})}{2} + V_{Z-}, \text{ when } V_X \ge 0V\\ 0, \text{ when } V_X < 0V \end{cases}$$

The V<sub>X-</sub> pin is usually connected to ground so that when V<sub>X+</sub> is negative there is no signal at the output, i.e. two quadrant operation. If the V<sub>X</sub> input is a negative going signal the V<sub>X+</sub> pin maybe grounded and the V<sub>X-</sub> pin used as the control input.

The V<sub>Y-</sub> terminal is usually grounded allowing the V<sub>Y+</sub> to swing ±5V. The V<sub>Z+</sub> terminal is usually connected directly to V<sub>OUT</sub> to complete the feedback loop of the output amplifier while V<sub>Z-</sub> is grounded. The scale factor is normally set to 2 by connecting GA B to GA C. Therefore the transfer equation simplifies to V<sub>OUT</sub> = (V<sub>X</sub> V<sub>Y</sub>) / 2.

## **Offset Adjustment**

The signal channel offset voltage may be nulled by using a 20k $\Omega$  potentiometer between V<sub>YIO</sub> Adjust pins A and B and connecting the wiper to -V. Reducing the signal channel offset will reduce V<sub>X</sub> AC feedthrough. Output offset voltage can also be nulled by connecting V<sub>Z</sub> to the wiper of a 20k $\Omega$  potentiometer which is tied between +V and -V.

#### **Capacitive Drive Capability**

When driving capacitive loads >20pF, a 50 $\Omega$  resistor is recommended between V<sub>OUT</sub> and V<sub>Z+</sub>, using V<sub>Z+</sub> as the output (See Figure 1). This will prevent the multiplier from going unstable.

#### **Power Supply Decoupling**

Power supply decoupling is essential for high frequency circuits. A  $0.01\mu$ F high quality ceramic capacitor at each supply pin in parallel with a  $1\mu$ F tantalum capacitor will provide excellent decoupling. Chip capacitors produce the best results due to the close spacing with which they may be placed to the supply pins minimizing lead inductance.

## **Adjusting Scale Factor**

The HA-2546 two quadrant multiplier may be configured for many uses. Following are examples of a few typical applications.

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

Adjusting the scale factor will tailor the control signal,  $V_X$ , input voltage range to match your needs. Referring to the simplified schematic and looking for the  $V_X$  input stage, you will notice the unusual design. The internal reference sets up a 1.2mA current sink for the  $V_X$  differential pair. The control signal applied to this input will be forced across the scale factor setting resistor and set the current flowing in the  $V_{X+}$  side of the differential pair. When the current through this resistor reaches 1.2mA, all the current available is flowing in the one side and full scale has been reached. Normally the 1.67k $\Omega$  internal resistor sets the scale factor to 2V when the Gain Adjust pins B and C are connected together, but you may set this resistor to any convenient value using pins 16 (GA A) and 15 (GA C).

FIGURE 2A. MULTIPLIER,  $V_{OUT} = V_X V_Y / 2$ , SCALE FACTOR = 2V

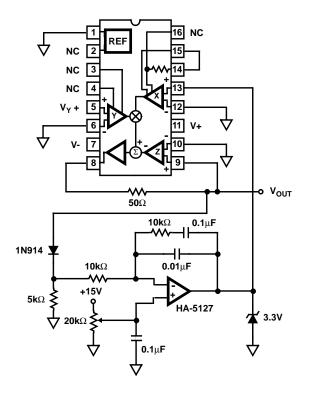

#### FIGURE 3. AUTOMATIC GAIN CONTROL

In Figure 3, the HA-2546 is configured in a true Automatic Gain Control or AGC application. The HA-5127, low noise op amp, provides the gain control level to the X input. This level will set the peak output voltage of the multiplier to match the reference level. The feedback network around the HA-5127 provides stability and a response time adjustment for the gain control circuit.

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

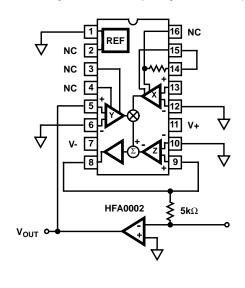

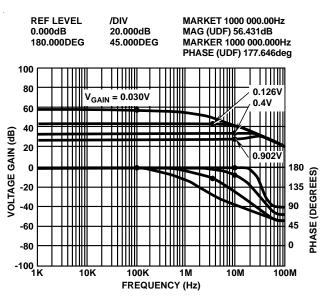

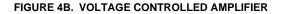

#### FIGURE 4A. VOLTAGE CONTROLLED AMPLIFIER

This multiplier has the advantage over other AGC circuits, in that the signal bandwidth is not affected by the control signal gain adjustment.

A wide range of gain adjustment is available with the Voltage Controlled Amplifier configuration shown in Figure 4A. and Figure 4B. Here the gain of the HFA0002 is swept from 20V/ V at a control voltage of 0.902V to a gain of almost 1000V/V with a control voltage of 0.03V.

The Video Fader circuit provides a unique function as shown in Figure 5. Here Ch B is applied to the minus Z input in addition to the minus Y input.  $V_{MIX}$  will control the percentage of Ch A and Ch B that are mixed together to produce a resulting video image or other signal.

Many other applications are possible including division, squaring, square-root, percentage calculations, etc. Please refer to the HA-2556 four quadrant multiplier for additional applications.

$$\begin{split} &V_{OUT} = Ch \ B + (Ch \ A - Ch \ B) \ V_{MIX} \ / \ Scale \ Factor \\ &Scale \ Factor = 2 \\ &V_{OUT} = All \ Ch \ B; \ if \ V_{MIX} = 0V \\ &V_{OUT} = All \ Ch \ A; \ if \ V_{MIX} = 2V \ (Full \ Scale) \\ &V_{OUT} = Mix \ of \ Ch \ A \ and \ Ch \ B; \ if \ 0V < V_{MIX} < 2V \end{split}$$

## FIGURE 5. VIDEO FADER

The information contained in this section has been developed through characterization by Intersil Semiconductor and is for use as application and design information only. No guarantee is implied.

## TYPICAL PERFORMANCE CHARACTERISTICS

Device Tested at: Supply Voltage =  $\pm 15V$ , R<sub>LOAD</sub> = 1k $\Omega$ , C<sub>LOAD</sub> = 50pF, Unless Otherwise Specified.

| PARAM                         | METER                  | CONDITIONS                                                         | TEMP  | ТҮР   | UNITS              |

|-------------------------------|------------------------|--------------------------------------------------------------------|-------|-------|--------------------|

| Multiplication Error          | Drift                  |                                                                    | Full  | 0.002 | %/°C               |

| Differential Gain             |                        | $V_X = 2V, V_Y = 300 \text{mV}_{P-P}, f_O = 3.58 \text{MHz}$       | +25°C | 0.1   | %                  |

| Differential Phase            |                        | $V_X = 2V$ , $V_Y = 300 \text{mV}_{P-P}$ , $f_O = 3.58 \text{MHz}$ | +25°C | 0.1   | Degrees            |

| Gain Tolerance                | DC to 5MHz             | V <sub>X</sub> = 2V                                                | +25°C | 0.1   | dB                 |

|                               | 5MHz to 8MHz           | 1                                                                  | +25°C | 0.18  | dB                 |

| 1% Amplitude Error            |                        |                                                                    | +25°C | 6     | MHz                |

| 1% Vector Error               |                        |                                                                    | +25°C | 260   | kHz                |

| THD+N                         |                        | $f_0 = 10$ kHz, $V_Y = 1$ Vrms, $V_X = 2$ V                        | +25°C | 0.03  | %                  |

| Voltage Noise                 | $f_{O} = 10Hz$         | $V_X = 0V, V_Y = 0V$                                               | +25°C | 400   | nV/Hz              |

|                               | f <sub>O</sub> = 100Hz | 1                                                                  | +25°C | 150   | nV/Hz              |

|                               | f <sub>O</sub> = 1kHz  | 1                                                                  | +25°C | 75    | nV/Hz              |

| Common Mode Rar               | nge                    |                                                                    | +25°C | ±9    | V                  |

| SIGNAL INPUT, V <sub>Y</sub>  |                        |                                                                    |       |       | •                  |

| Average Offset Volt           | age Drift              |                                                                    | Full  | 45    | μV/ºC              |

| Differential Input Resistance |                        |                                                                    | +25°C | 720   | KΩ                 |

| Small Signal Bandw            | vidth (-3dB)           | V <sub>X</sub> = 2V                                                | +25°C | 40    | MHz                |

| Feedthrough                   |                        | $f_0 = 5MHz, V_X = 0V, V_Y = 200mVrms$                             | +25°C | -52   | dB                 |

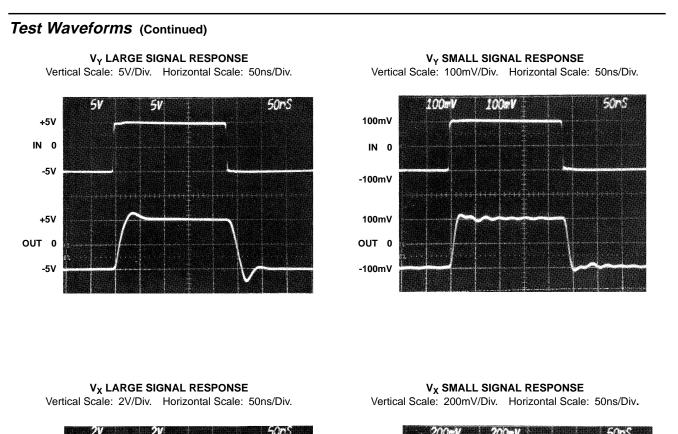

| V <sub>Y</sub> TRANSIENT RE   | SPONSE                 |                                                                    |       |       | •                  |

| Propagation Delay             |                        |                                                                    | +25°C | 25    | ns                 |

| Settling Time                 |                        | $V_Y = \pm 5V, V_X = 2V$                                           | +25°C | 200   | ns                 |

| CONTROL INPUT,                | V <sub>X</sub>         |                                                                    |       |       | •                  |

| Average Offset Volt           | age Drift              |                                                                    | Full  | 10    | μV/ <sup>o</sup> C |

| Differential Input Re         | esistance              |                                                                    | +25°C | 360   | kΩ                 |

| Small Signal Bandw            | vidth (-3dB)           | $V_{\rm Y} = 5V, V_{\rm X} = -1V$                                  | +25°C | 17    | MHz                |

| Feedthrough                   |                        | $f_O = 100$ kHz, $V_Y = 0$ V, $V_X = 200$ mVrms                    | +25°C | -40   | dB                 |

| Common Mode Rej               | ection Ratio           | $V_X = 0V$ to 2V, $V_Y = 5V$                                       | +25°C | 80    | dB                 |

| V <sub>X</sub> TRANSIENT RE   | SPONSE                 |                                                                    |       |       | •                  |

| Propagation Delay             |                        |                                                                    | +25°C | 50    | ns                 |

| Settling Time                 |                        | $V_X = 0$ to 2V, $V_Y = 5V$                                        | +25°C | 200   | ns                 |

| V <sub>Z</sub> CHARACTERIS    | TICS                   |                                                                    |       |       | •                  |

| Open Loop Gain                |                        |                                                                    | +25°C | 70    | dB                 |

| Differential Input Re         | esistance              |                                                                    | +25°C | 900   | kΩ                 |

| OUTPUT CHARAC                 | TERISTICS              |                                                                    |       |       | •                  |

| Output Resistance             |                        |                                                                    | +25°C | 1     | Ω                  |

#### All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com