High Speed Current Mode PWM Control IC for Switching Power Supply

## HITACHI

ADE-204-028A (Z) 2nd Edition Nov. 1999

#### **Description**

The HA17384S/H and HA17385H are PWM control switching regulator IC series suitable for highspeed, current-mode switching power supplies. With ICs from this series and a few external parts, a small, low cost flyback-transformer switching power supply can be constructed, which facilitates good line regulation by current mode control. Synchronous operation driven after an external signal can also be easily obtained which offers various applications such as a power supply for monitors small multi-output power supply.

The IC series are composed of circuits required for a switching regulator IC. That is a under-voltage lockout (UVL), a high precision reference voltage regulator (5.0 V  $\pm$  2%), a triangular wave oscillator for timing generation, a high-gain error amplifier, and as totem pole output driver circuit which directly drives the gate of power MOSFETs found in main switching devices. In addition, a pulse-by-pulse type, high-speed, current-detection comparator circuit with variable detection level is incorporated which is required for current mode control.

The HA17384SPS includes the above basic function circuits. In addition to these basic functions, the H Series incorporates thermal shut-down protection (TSD) and overvoltage protection (OVP) functions, for configuration of switching power supplies that meet the demand for high safety levels.

Between the HA17384 and HA17385, only the UVL threshold voltages differ as shown in the product lineup table. (See next page.)

This IC is pin compatible with the "3842 family" ICs made by other companies in the electronics industry. However, due to the characteristics of linear ICs, it is not possible to achieve ICs that offer full compatibility in every detail.

Therefore, when using one of these ICs to replace another manufacturer's IC, it must be recognized that it has different electrical characteristics, and it is necessary to confirm that there is no problem with the power supply (mounting) set used.

#### **Functions**

- Under-voltage lockout system

- Reference voltage regulator of 5.0 V  $\pm$  2%

- Triangular wave (sawtooth) oscillator

- Error amplifier

- Totem pole output driver circuit (direct driving for power MOSFETs)

- Current-detection comparator circuit for current mode

- OVP function (over voltage protection) \*1

- TSD function (thermal shut-down protection) \*1

- Protect function by zener diode (between power input and GND)

Note: 1. H series only.

#### **Features**

- High-safety UVL circuit is used (Both V<sub>IN</sub> and Vref are monitored)

- High speed operation:

- Current detection response time: 100 ns Typ

- Maximum oscillation frequency: 500 kHz

- Low standby current: 170 μA Typ

- Wide range dead band time

- (Discharge current of timing capacitance is constant 8.4 mA Typ)

- Able to drive power MOSFET directly

- (Absolute maximum rating of output current is  $\pm 1$  A peak)

- OVP function (over voltage protection) is included \*1

- (Output stops when FB terminal voltage is 7.0 V Typ or higher)

- TSD function (thermal shut-down protection) is included \*1

- (Output stops when the temperature is 160°C Typ or higher)

- · Zener protection is included

- (Clamp voltage between V<sub>IN</sub> and GND is 34 V Typ)

- Wide operating temperature range:

- Operating temperature: -20°C to +105°C

- Junction temperature: 150°C \*2

Note: 1. H series only.

2. S series only.

### **Product Line-up**

| Package      |               | Additional Functio                        | n                                   | UVL Power Sup<br>Threshold Volt | • •                         |

|--------------|---------------|-------------------------------------------|-------------------------------------|---------------------------------|-----------------------------|

| DILP8 (DP-8) | SOP8 (FP-8DC) | TSD<br>(Thermal shut-<br>down protection) | OVP<br>(Over voltage<br>protection) | V <sub>TH UVL</sub> (V) Typ     | V <sub>TL UVL</sub> (V) Typ |

| HA17384SPS   | HA17384SRP    | _                                         | _                                   | 16.0                            | 10.0                        |

| HA17384HPS   | HA17384HRP    | 0                                         | 0                                   | _                               |                             |

| HA17385HPS   | HA17385HRP    | 0                                         | О                                   | 8.4                             | 7.6                         |

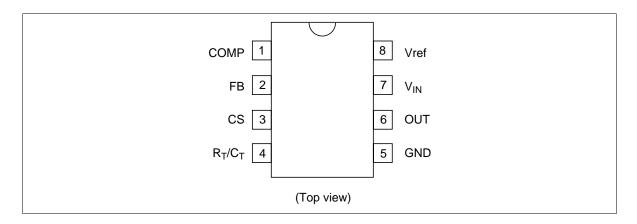

### **Pin Arrangement**

#### **Pin Function**

| Pin No. | Symbol                         | Function                                          | Note |

|---------|--------------------------------|---------------------------------------------------|------|

| 1       | COMP                           | Error amplifier output pin                        |      |

| 2       | FB                             | Inverting input of error amp./OVP input pin       | 1    |

| 3       | CS                             | Current sensing signal input pin                  |      |

| 4       | R <sub>T</sub> /C <sub>T</sub> | Timing resistance, timing capacitance connect pin |      |

| 5       | GND                            | Groung pin                                        |      |

| 6       | OUT                            | PWM Pulse output pin                              |      |

| 7       | V <sub>IN</sub>                | Power supply voltage input pin                    |      |

| 8       | Vref                           | Reference voltage 5V output pin                   |      |

Note: 1. Overvoltage protection (OVP) input is usable only for the HA17384H and HA17385H.

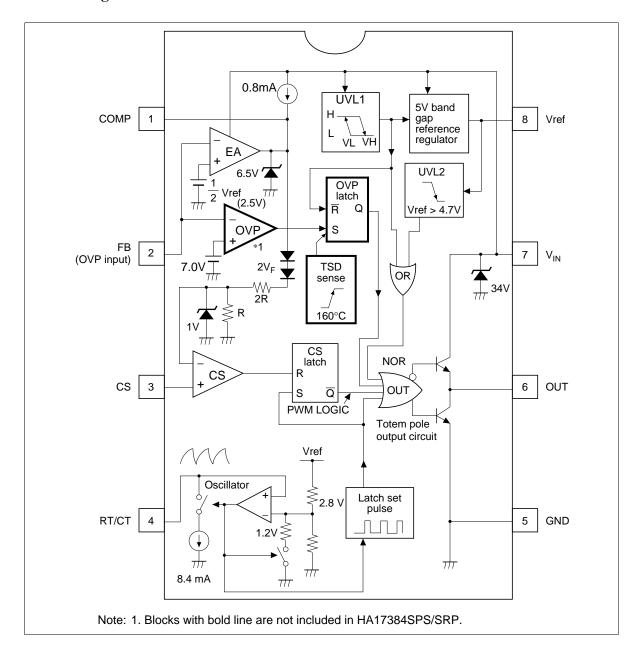

### **Block Diagram**

#### **Absolute Maximum Ratings**

| Item                          | Symbol              | Rating                  | Unit | Note |

|-------------------------------|---------------------|-------------------------|------|------|

| Supply voltage                | V <sub>IN</sub>     | 30                      | V    |      |

| DC output current             | Io                  | ±0.1                    | Α    |      |

| Peak output current           | I <sub>O PEAK</sub> | ±1.0                    | Α    |      |

| Error amplifier input voltage | $V_{\sf FB}$        | –0.3 to V <sub>IN</sub> | V    |      |

| COMP terminal input voltage   | V <sub>COMP</sub>   | -0.3 to +7.5            | V    |      |

| Error output sink current     | I <sub>OEA</sub>    | 10                      | mA   |      |

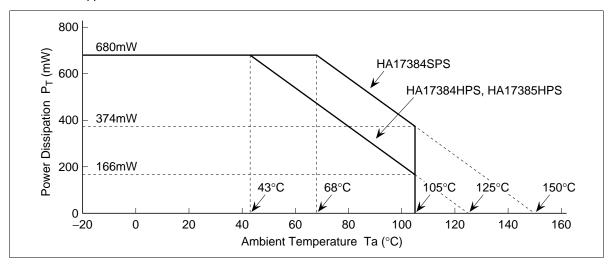

| Power dissipation             | P <sub>T</sub>      | 680                     | mW   | 1, 2 |

| Operating temperature         | Topr                | -20 to +105             | °C   |      |

| Junction temperature          | Tj                  | 125                     | °C   | 3    |

|                               |                     | 150                     | °C   | 4    |

| Storage temperature           | Tstg                | -55 to +125             | °C   | 3    |

|                               |                     | -55 to +150             | °C   | 4    |

Notes: 1. For the HA17384HPS and HA17385HPS,

This value applies up to  $Ta = 43^{\circ}C$ ; at temperatures above this, 8.3 mW/°C derating should be applied.

For the HA17384SPS,

This value applies up to  $Ta = 68^{\circ}C$ ; at temperatures above this, 8.3 mW/°C derating should be applied.

#### Absolute Maximum Ratings (cont)

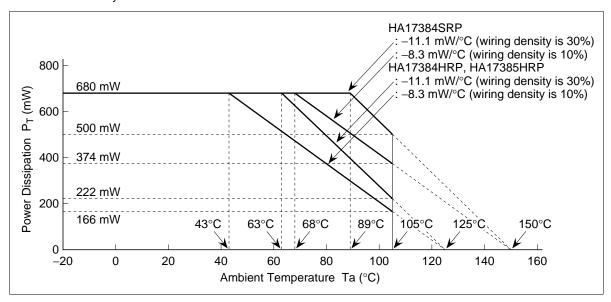

Notes: 2. This is the value when the device is mounted on a glass-epoxy substrate (40 mm  $\times$  40 mm  $\times$  1.6 mm). However,

For the HA17384HRP and HA17385HRP,

Derating should be performed with 8.3 mW/°C in the Ta  $\geq$  43°C range if the substrate wiring density is 10%.

Derating should be performed with 11.1 mW/°C in the  $Ta \ge 63$ °C range if the substrate wiring density is 30%.

For the HA17384SRP,

Derating should be performed with 8.3 mW/ $^{\circ}$ C in the Ta  $\geq$  68 $^{\circ}$ C range if the substrate wiring density is 10%.

Derating should be performed with 11.1 mW/°C in the Ta  $\geq$  89°C range if the substrate wiring density is 10%.

- 3. Applies to the HA17384HPS/HRP and HA17385HPS/HRP.

- 4. Applies to the HA17384SPS/SRP.

#### **Electrical Characteristics**

(The condition is: Ta = 25°C,  $V_{IN} = 15$  V,  $C_{T} = 3300$  pF,  $R_{T} = 10$  k $\Omega$  without notice)

#### **Reference Part**

| Item                     | Symbol         | Min | Тур  | Max  | Unit   | Test Condition                    | Note |

|--------------------------|----------------|-----|------|------|--------|-----------------------------------|------|

| Reference output voltage | Vref           | 4.9 | 5.0  | 5.1  | V      | lo = 1 mA                         |      |

| Line regulation          | Regline        |     | 20   | 50   | mV     | 12 V ≤ V <sub>IN</sub> ≤ 25 V     |      |

| Load regulation          | Regload        | _   | 10   | 25   | mV     | -1 mA ≥ lo ≥ -20 mA               |      |

| Output short current     | los            | -30 | -100 | -180 | mA     | Vref = 0V                         |      |

| Temperature stability    | ΔVref          | _   | 80   | _    | ppm/°C | Io = −1 mA,<br>−20°C ≤ Ta ≤ 105°C | 1    |

| Output noise voltage     | V <sub>N</sub> |     | 100  | _    | μV     | 10 Hz ≤ fnoise ≤ 10 kHz           | 1    |

Notes: 1. Reference value for design.

### **Triangular Wave Oscillator Part**

| Item                                               | Symbol                 | Min | Тур  | Max  | Unit | <b>Test Condition</b>                                    | Note |

|----------------------------------------------------|------------------------|-----|------|------|------|----------------------------------------------------------|------|

| Typical oscillating frequency                      | fosc Typ               | 47  | 52   | 57   | kHz  | $C_T = 3300 \text{ pF},$ $R_T = 10 \text{ k}\Omega$      |      |

| Maximum oscillating frequency                      | fosc Max               | 500 | _    | _    | kHz  |                                                          |      |

| Supply voltage dependency of oscillating frequency | ∆fosc 1                | _   | ±0.5 | ±2.0 | %    | $12~\text{V} \leq \text{V}_{\text{IN}} \leq 25~\text{V}$ |      |

| Temperature dependency of oscillating frequency    | ∆fosc 2                | _   | ±5.0 | _    | %    | –20°C ≤ Ta ≤ 105°C                                       | 1    |

| Discharge current of C <sub>⊤</sub>                | Isink <sub>CT</sub>    | 7.5 | 8.4  | 9.3  | mΑ   | V <sub>CT</sub> = 2.0 V                                  |      |

| Low level threshold voltage                        | V <sub>TLCT</sub>      | _   | 1.2  | _    | V    |                                                          | 1    |

| High level threshold voltage                       | $V_{\text{THCT}}$      | _   | 2.8  | _    | V    |                                                          | 1    |

| Triangular wave amplitude                          | $\Delta V_{\text{CT}}$ | _   | 1.6  | _    | V    | $\Delta V_{CT} = V_{THCT} - V_{TLCT}$                    | 1    |

Notes: 1. Reference value for design.

### **Electrical Characteristics** (cont)

#### **Error Amplifire Part / OVP Part**

| Item                                    | Symbol                   | Min  | Тур  | Max  | Unit | Test Condition                                                    | Note |

|-----------------------------------------|--------------------------|------|------|------|------|-------------------------------------------------------------------|------|

| Non-inverting input voltage             | $V_{\sf FB}$             | 2.42 | 2.50 | 2.58 | V    | $V_{COMP} = 2.5 \text{ V}$                                        |      |

| Input bias current                      | I <sub>IB</sub>          | _    | -0.2 | -2.0 | μΑ   | V <sub>FB</sub> = 5.0 V                                           |      |

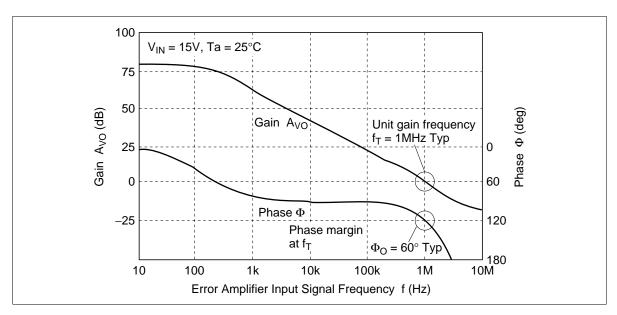

| Open loop voltage gain                  | A <sub>VOL</sub>         | 65   | 90   | _    | dB   | $2.0 \text{ V} \le \text{V}_{\text{O}} \le 4.0 \text{ V}$         |      |

| Unity gain bank width                   | BW                       | 0.7  | 1.0  | _    | MHz  |                                                                   |      |

| Power supply voltage rejection ratio    | PSRR                     | 60   | 70   | _    | dB   | 12 V ≤ V <sub>IN</sub> ≤ 25 V                                     |      |

| Output sink current                     | I <sub>Osink EA</sub>    | 3.0  | 9.0  | _    | mA   | $V_{FB} = 2.7 \text{ V}, V_{COMP} = 1.1 \text{ V}$                |      |

| Output source current                   | l <sub>Osource EA</sub>  | -0.5 | -0.8 | _    | mA   | $V_{FB} = 2.3 \text{ V}, V_{COMP} = 5.0 \text{ V}$                |      |

| High level output voltage               | $V_{OHEA}$               | 5.5  | 6.5  | 7.5  | V    | $V_{FB} = 2.3 \text{ V},$ $R_L = 15 \text{ k}\Omega(\text{GND})$  |      |

| Low level output voltage                | $V_{OLEA}$               | _    | 0.7  | 1.1  | V    | $V_{FB} = 2.7 \text{ V},$ $R_L = 15 \text{ k}\Omega(\text{Vref})$ |      |

| OVP latch threshold voltage             | $V_{\text{OVP}}$         | 6.0  | 7.0  | 8.0  | V    | Increase FB terminal voltage                                      | 1    |

| OVP (FB) terminal input current         | I <sub>FB(OVP)</sub>     | _    | 30   | 50   | μΑ   | V <sub>FB</sub> = 8.0 V                                           | 1    |

| OVP latch reset V <sub>IN</sub> voltage | V <sub>IN(OVP RES)</sub> | 6.0  | 7.0  | 8.0  | V    | Decreasing V <sub>IN</sub> after OVP latched                      | 1    |

Note: 1. These values are not prescribe to the HA17384SPS/SRP because OVP function is not included.

### **Electrical Characteristics** (cont)

#### **Current Sensing Part**

| Item                                 | Symbol            | Min  | Тур  | Max  | Unit | Test Condition                                                              | Note |

|--------------------------------------|-------------------|------|------|------|------|-----------------------------------------------------------------------------|------|

| Voltage gain                         | A <sub>VCS</sub>  | 2.85 | 3.00 | 3.15 | V/V  | $V_{FB} = 0 V$                                                              | 1    |

| Maximum sensing voltage              | Vth <sub>cs</sub> | 0.9  | 1.0  | 1.1  | V    |                                                                             |      |

| Power supply voltage rejection ratio | PSRR              | _    | 70   | _    | dB   | 12 V ≤ V <sub>IN</sub> ≤ 25 V                                               | 2    |

| Input bias current                   | I <sub>BCS</sub>  | _    | -2   | -10  | μΑ   | $V_{CS} = 2 V$                                                              |      |

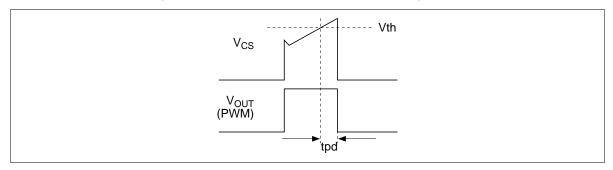

| Current sensing response time        | tpd               | 50   | 100  | 150  | ns   | Time from when V <sub>cs</sub> becomes 2 V to when output becomes "L" (2 V) | 3    |

Notes: 1. The gain this case is the ratio of error amplifier output change to the current-sensing threshold voltage change.

- 2. Reference value for design.

- 3. Current sensing response time tpd is definded a shown in the figure 1.

Figure 1 Definition of Current Sensing Response Time tpd

#### **PWM Output Part**

| Item                               | Symbol              | Min  | Тур  | Max | Unit | <b>Test Condition</b>          | Note |

|------------------------------------|---------------------|------|------|-----|------|--------------------------------|------|

| Output low voltage 1               | $V_{OL1}$           | _    | 0.7  | 1.5 | V    | losink = 20 mA                 |      |

| Output low voltage 2               | $V_{OL2}$           | _    | 1.5  | 2.2 | V    | losink = 200 mA                | 1    |

| Output high voltage 1              | V <sub>OH1</sub>    | 13.0 | 13.5 | _   | V    | losource = -20 mA              |      |

| Output high voltage 2              | $V_{OH2}$           | 12.0 | 13.3 | _   | V    | losource = -200 mA             | 1    |

| Output low voltage at standby mode | V <sub>OL STB</sub> | _    | 0.8  | 1.1 | V    | $V_{IN} = 5 V$ , losink = 1 mA |      |

| Rise time                          | t <sub>r</sub>      | _    | 80   | 150 | ns   | C <sub>L</sub> = 1000 pF       |      |

| Fall time                          | t <sub>f</sub>      | _    | 70   | 130 | ns   | C <sub>L</sub> = 1000 pF       |      |

| Maximum ON duty                    | Du max              | 94   | 96   | 100 | %    |                                |      |

| Minimum ON duty                    | Du min              | _    | _    | 0   | %    |                                |      |

Notes: 1. Pulse application test

#### **Electrical Characteristics (cont)**

#### **UVL Part**

| Item                                   | Symbol               | Min  | Тур  | Max  | Unit | Test Condition                       | Note |

|----------------------------------------|----------------------|------|------|------|------|--------------------------------------|------|

| Threshold voltage for                  | $V_{THUVL}$          | 14.5 | 16.0 | 17.5 | V    | Turn-ON voltage                      | 1    |

| high V <sub>IN</sub> level             |                      | 7.6  | 8.4  | 9.2  | V    | when V <sub>IN</sub> is rising       | 2    |

| Threshold voltage for                  | V <sub>TL UVL</sub>  | 9.0  | 10.0 | 11.0 | V    | Minimum operating                    | 1    |

| low V <sub>IN</sub> level              |                      | 6.8  | 7.6  | 8.4  | V    | voltage after turn-ON                | 2    |

| V <sub>IN</sub> UVL hysteresis voltage | V <sub>HYS UVL</sub> | 5.0  | 6.0  | 7.0  | V    | $V_{HYSUVL} = V_{THUVL} - V_{TLUVL}$ | 1    |

|                                        |                      | 0.6  | 8.0  | 1.0  | V    | -                                    | 2    |

| Vref UVL threshold voltage             | $V_{TVref}$          | 4.3  | 4.7  | Vref | V    | Voltage is forced toVref terminal    |      |

Notes: 1. For the HA17384S/H.

2. For the HA17385H.

#### **Total Characteristics**

| Item                                     | Symbol            | Min | Тур  | Max  | Unit | Test Condition                                         | Note |

|------------------------------------------|-------------------|-----|------|------|------|--------------------------------------------------------|------|

| Operating current                        | I <sub>IN</sub>   | 7.0 | 10.0 | 13.0 | mA   | $C_L = 1000 \text{ pF}, V_{FB} = V_{CS} = 0 \text{ V}$ |      |

| Standby current                          | I <sub>STBY</sub> | 120 | 170  | 230  | μΑ   | Current at start up                                    |      |

| Current of latch                         | LATCH             | 200 | 270  | 340  | μΑ   | $V_{FB} = 0 \text{ V after } V_{FB} = V_{OVP}$         | 1, 2 |

| Power supply zener voltage               | $V_{\text{INZ}}$  | 31  | 34   | 37   | V    | I <sub>IN</sub> + 2.5 mA                               |      |

| Overheat protection starting temperature | $Tj_{TSD}$        | _   | 160  | _    | °C   |                                                        | 3, 4 |

Notes: 1. These values are not prescribe to the HA17384SPS/SRP because OVP function is not included.

- 2.  $V_{IN} = 8.5 \text{ V}$  in case of the HA17384H.

- 2. These values are not prescribe to the HA17384SPS/SRP because TSD function is not included.

- 4. Reference value for design.

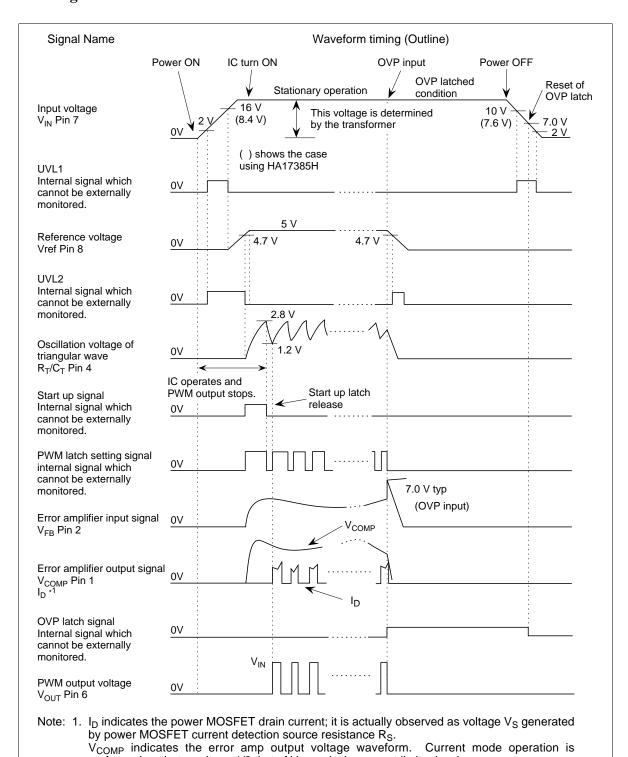

#### **Timing Chart**

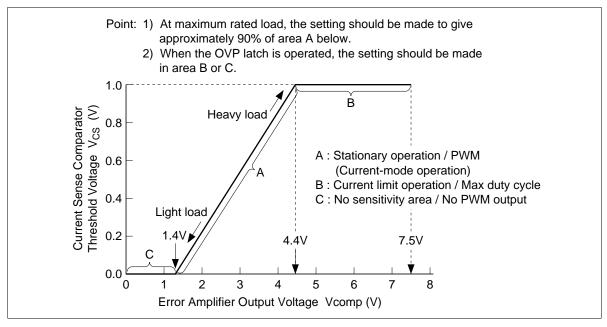

performed so that a voltage 1/3 that of V<sub>COMP</sub> is the current limiter level.

**Operation** (Description of Timing Chart)

#### From Power ON to Turn On

After the power is switched ON, the power supply terminal voltage ( $V_{IN}$ ) of this IC rises by charging through bleeder resistor  $R_B$ . At this time, when the power voltage is in the range of 2 V to 16 V\*\frac{1}{2}. The low-voltage, lock out UVL1 operates and accordingly the OUT voltage, that is, the gate voltage of the power MOSFET, is fixed at 1.3 V or a lower value, resulting in the power MOSFET remaining in the OFF state.

When the power supply voltage reaches 16 V, UVL1 of this IC is reset and the reference voltage (Vref) generating part turns ON. However, until Vref becomes 4.7 V, the low-voltage, lock out UVL2 operates to keep the OUT terminal voltage low. After Vref terminal voltage becomes 4.7 V or higher, OUT terminal outputs a PWM pulse.

Note: 1. The value is for the HA17384S/H.

The value is 8.4 V for the HA17385H.

#### **Generation of Triangular Wave and PWM Pulse**

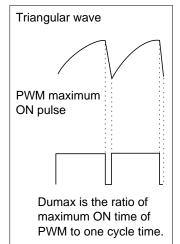

After the output of the Vref, each blocks begins to operate. The triangular wave is generated on the  $R_T/C_T$  terminal. For PWM pulses, the triangular wave rise time is taken as the variable on-duty on-time. The triangular wave fall time is taken as the dead-band time. The initial rise of the triangular wave starts from 0 V, and to prevent a large on-duty at this time, the initial PWM pulse is masked and not output. PWM pulses are outputted after the second triangular wave. The above operation is enabled by the charge energy which is charged through the bleeder resistor  $R_B$  into the capacitor  $C_B$  of  $V_{IN}$ .

#### **Stationary Operation**

PWM pulses are outputted after the second wave of the triangular wave and stationary operation as the switching power supply starts.

By switching operation from ON/OFF to OFF/ON in the switching device (power MOSFET), the transformer converts the voltage. The power supply of IC  $V_{IN}$  is fed by the back-up winding of the transformer.

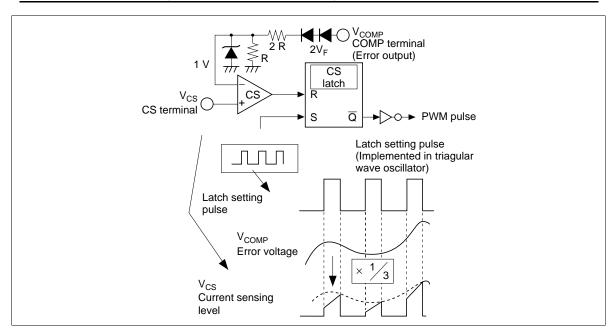

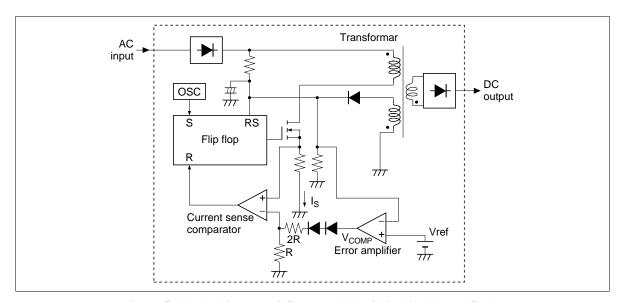

In the current mode of the IC, the current in the switcing device is always monitored by a source resistor  $R_{CS}$ . Then the current limiter level is varied according to the error voltage (COMP terminal voltage) for PWM control. One third of the error voltage level, which is divided by resistors "2R" and "R" in the IC, is used to sense the current ( $R = 25 \text{ k}\Omega$ ).

Two diodes between the error output and the 2R-R circuit act only as a DC level shifter. Actually, these diodes are connected between the 2R-R circuit and GND, and, the current sensing comparator and GND, respectively. Therefore, these blocks operate 1.4 V higher than the GND level. Accordingly, the error of the current sensing level caused by the switching noise on the GND voltage level is eliminated. The zener diode of 1 V symbolically indicates that the maximum sensing voltage level of the CS terminal is 1 V.

#### **Power OFF**

At power OFF, the input voltage of the transformer gradually decreases and then  $V_{IN}$  of IC also decreases according to the input voltage. When  $V_{IN}$  becomes lower than 10 V\*<sup>2</sup> or Vref becomes lower than 4.7 V, UVL1 (UVL2) operates again and the PWM pulse stops.

Note: 2. The value is for the HA17384S/H.

The value is 7.6 V for the HA17385H.

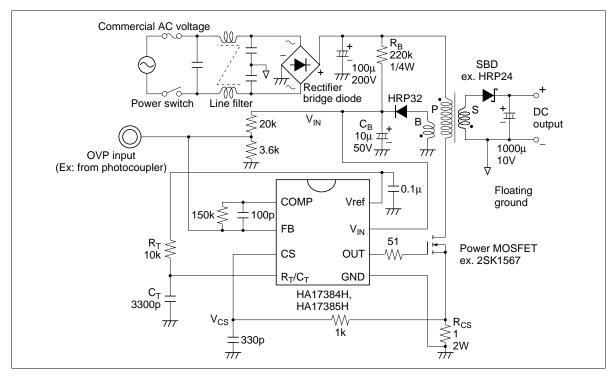

Figure 2 Mounting Circut Diagram for Operation Expression

Figure 3 Operation Diagram of Current Sensing Part

Figure 4 Current Sense Characteristics

#### **Features and Theory of Current Mode Control**

#### **Features of Current Mode Control**

- Switch element current detection is performed every cycle, giving a high feedback response speed.

- Operation with a constant transformer winding current gives a highly stable output voltage (with excellent line regulation characteristics, in particular).

- Suitable for flyback transformer use.

- External synchronous operation is easily achieved. (This feature, for example, is applicable to synchronization with a forizontal synchronizing signal of CRT monitor.)

#### **Theory of Current Mode Control**

In current mode control, a PWM pulse is generated not by comparing an error voltage with a triangular wave voltage in the voltage mode, but by changing the current limiter level in accordance with the error voltage (COMP terminal in this IC, that is,output of the error amplifier output) which is obtained by constantly monitoring the current of the switching device (power MOSFET) using source resistor R<sub>CS</sub>.

One of the features of current mode control is that the current limited operates in all cycles of PWM as described by the above theory.

In voltage mode, only one feedback loop is made by an output voltage. In current mode, on the other hand, two loops are used. One is an output voltage loop and the other is a loop of the switching device current itself. The current of the switching device can be controlled switch high speed. In current mode control, the current in the transformer winding is kept constant, resulting in high stability. An important consequence is that the line regulation in terms of total characteristics is better than that in voltage mode.

Figure 5 Block Diagram of Current Mode Switching Power Spply

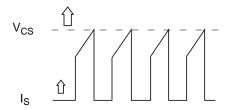

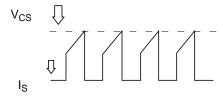

A. Control in the case of heavy load

B. Control in the case of light load

As the load becomes heavy and the DC output decreases, the current sensing level is raised as shown in A. above in order to increase the current in the switching device in each cycle. When the load decreases, inverse control is carried out as shown in B. above.

Figure 6 Primary Current Control of Transformer in Current Mode (Conceptual Diagram)

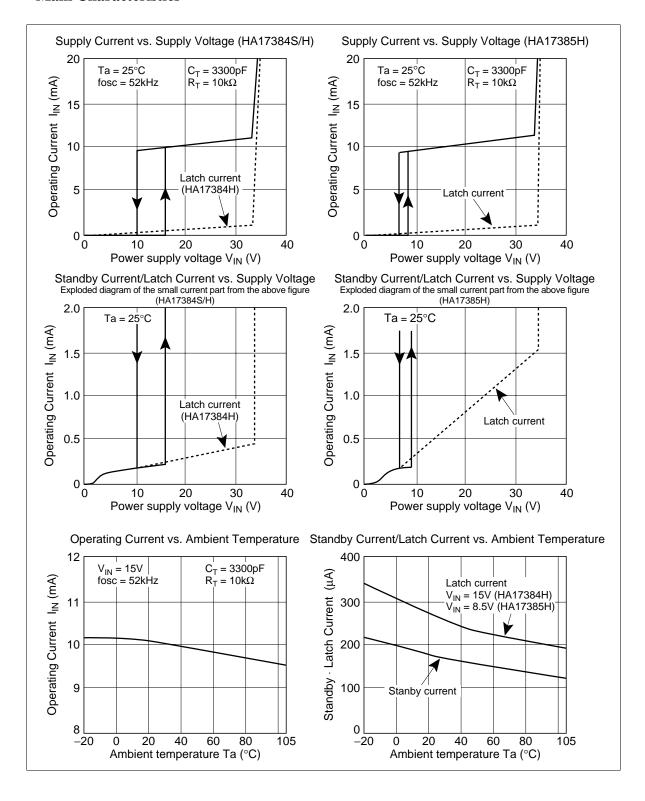

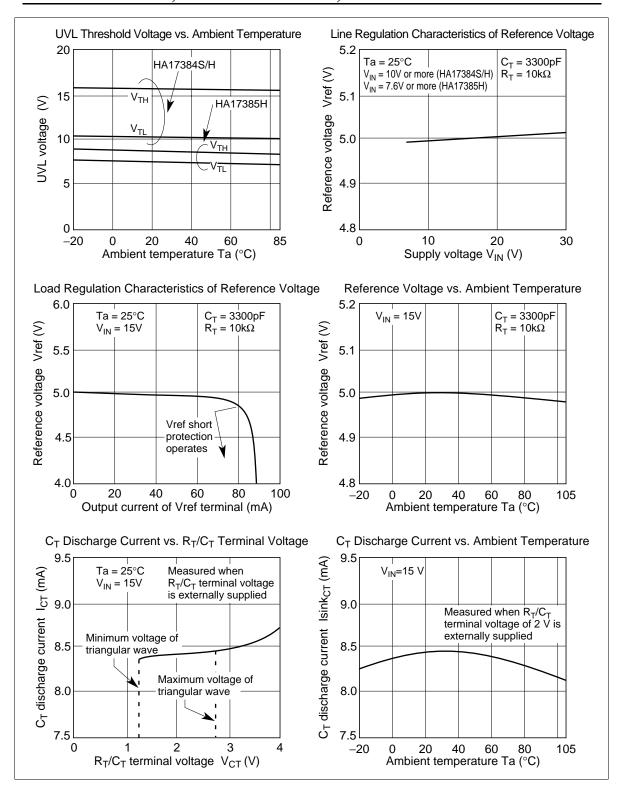

#### **Main Characteristics**

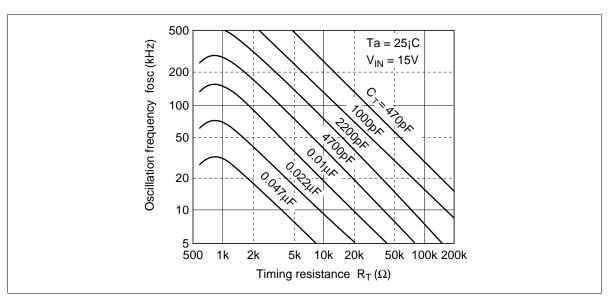

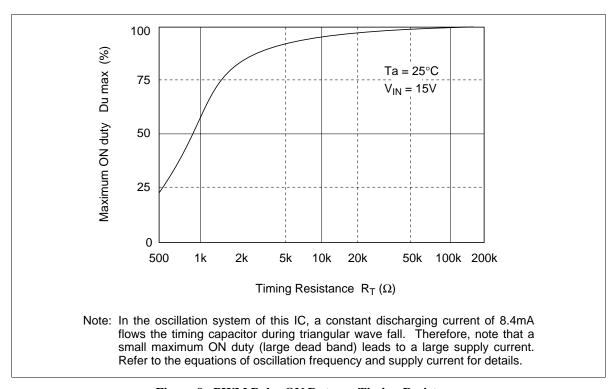

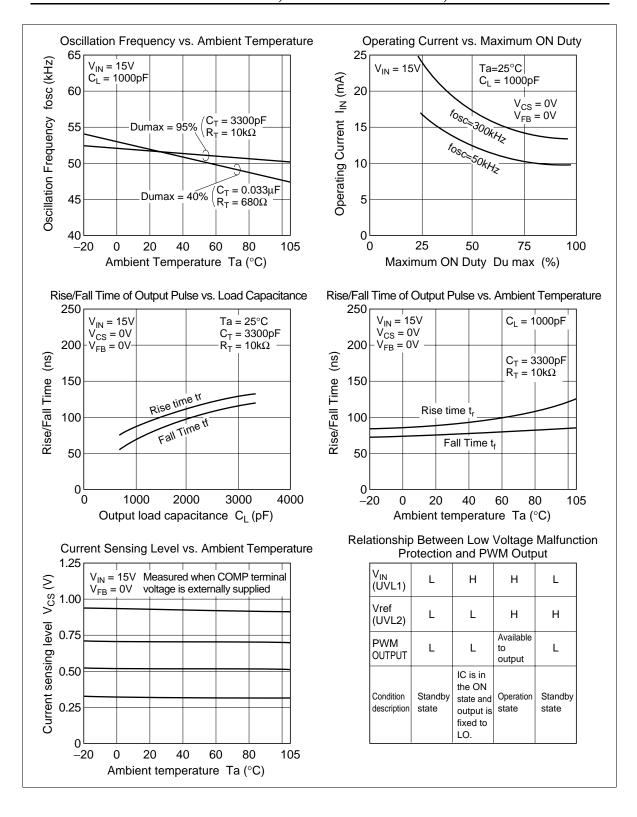

Figure 7 Oscillation Frequency vs. Timing Resistance

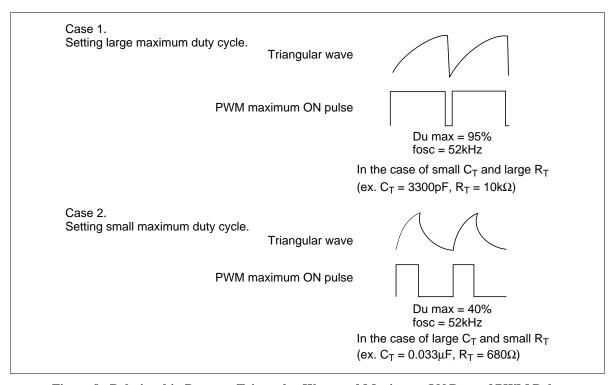

Figure 8 Relationship Between Triangular Wave and Maximum ON Duty of PWM Pulse

Figure 9 PWM Pulse ON Duty vs. Timing Resistance

Figure 10 Open Loop Gain Characterisrics of Error Amplifier

- Calculation of operation parameters

- 1. Maximum ON duty Du max (Refer to the right figure.)

Du max =

$$\frac{1}{1 + 1.78 \times \ln\left(1 + \frac{190\Omega}{R_T - 440\Omega}\right)}$$

2. Oscillation frequency fosc

$$\text{fosc} = \frac{1}{C_{\text{T}} \times R_{\text{T}} \times \left\{ 0.56 + \ln\left(1 + \frac{190\Omega}{R_{\text{T}} - 440\Omega}\right) \right\}}$$

From the above two equations, the following two equations are obtained.

3. Equalization to device R<sub>T</sub> from Du max

$$R_{T} = \frac{190\Omega}{e^{0.56 (1/Du \text{ max} - 1)} - 1} + 440\Omega$$

(e = 2.71828.base of natural logarithm)

4. Equation to device C<sub>T</sub> from fosc and R<sub>T</sub>

$$C_T = 1.78 \times \frac{Du \text{ max}}{\text{fosc} \times R_T}$$

5. Operating current I<sub>IN</sub>

$$I_{IN} = I_Q + Isink_{CT} \times (1 - Du max) + Ciss \times V_{IN} \times fosc$$

providing that  $I_Q$  = 8.4mA Typ (Supply current when oscillation in IC stops.) Ciss is the input gate capacitance of the power MOSFET which is connected and  $V_{IN}$  is the supply voltage of the IC.

Example 1: Calculation when  $R_T = 10k\Omega$  and  $C_T = 3300pF$

fosc = 52kHz, Du max = 95%,  $I_{IN} = 9.7mA$

Example 2: Calculation for 50% of Du max and 200 kHz of fosc

$$R_T = 693\Omega$$

,  $C_T = 6360 pF$ ,  $I_{IN} = 12.5 mA$

However, Ciss = 1000 pF,  $V_{IN} = 18 V$

Note that the actual value may differ from the calculated one because of the internal delay in operation and input characteristics of the POWER MOS FET. Check the value when mounting.

Additionally a small Dumax leads to a large supply current, even if the frequency is not changed, and start up may become difficult. In such a case, the following measure is recommended.

- (1) For an AC/DC converter, a small bleeder resistance is required.

- (2) The large capacitance between Vref and GND is required.

- (3) Use a large Dumax with a triangular wave and raise the current limit of the switching device to around the maximum value (1.0V Typ).

The current limit is expressed as  $ID_{max} = \frac{V_{THCS}}{R_{CS}}$

In the above case, Dumax = 95%

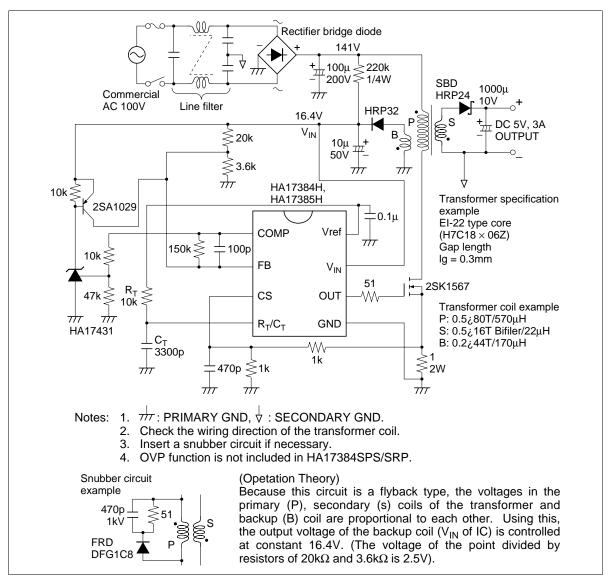

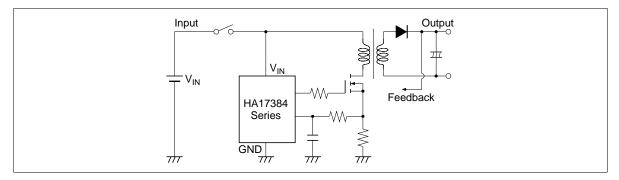

#### **Application Circuit Example (1)**

Figure 12 Primary Voltage Sensing Flyback Converter

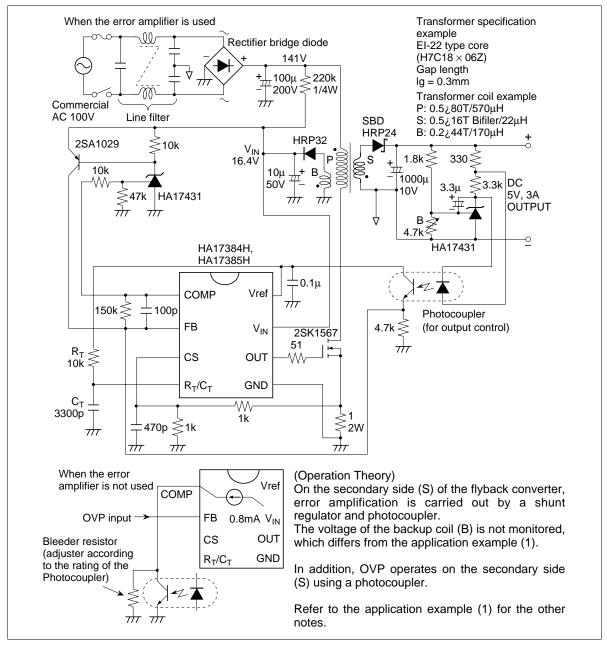

#### **Application Circuit Example (2)**

Figure 13 Secondary Voltage Sensing Flyback Converter

#### **Application Examples for Fuller Exploitation of Power Supply Functions**

A number of application examples are briefly described below.

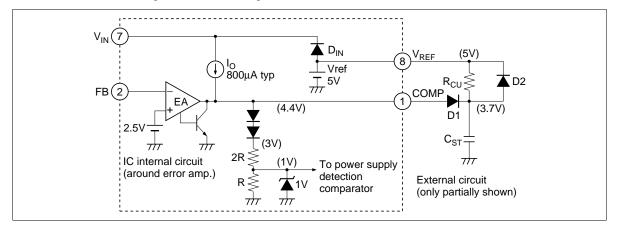

#### 1. Soft start

A soft start is a start method in which the PWM pulse width is gradually increased when the power supply is activated. This prevents the stress on the transformer and switch element caused by a rapid increase in the PWM pulse width, and also prevents overshoot when the secondary-side output voltage rises. The circuit diagram is shown in figure 14.

Figure 14 Circuit Diagram for Soft Start

Operation: In this circuit, error amp output source current  $I_{\rm O}$  (800  $\mu A$  typ.) gradually raises the switch element current detection level, using a voltage slope that charges soft start capacitance  $C_{\rm ST}$ . When the voltage at each node is at the value shown in parentheses in the figure, the soft start ends. The soft start time is thus given by the following formula:

$$T_{\text{ST}} = (3.7 \text{ V/800 } \mu\text{A}) \times C_{\text{ST}} \approx 4.62 \text{ C}_{\text{ST}} \text{ (ms)}$$

$$(C_{\text{ST}} \text{ unit: } \mu\text{F})$$

External parts other than C<sub>ST</sub> operate as follows:

• Diode D1 : Current detection level shift and current reverse-flow prevention.

• Diode D2 : Together with diode  $D_{IN}$  in the IC,  $C_{ST}$  charge drawing when power supply falls.

• Resistance  $R_{CU}$ : For  $C_{ST}$  charge-up at end of soft start. (Use a high resistance of the order of several hundred  $k\Omega$ .)

Note: During a soft start, since PWM pulses are not output for a while after the IC starts operating, there is a lack of energy during this time, and intermittent mode may be entered. In this case, the capacitance between Vref and GND should be increased to around 4.7 μF to 10 μF.

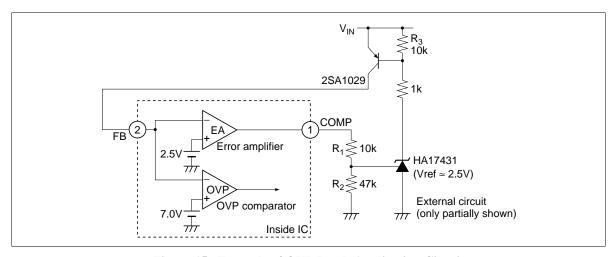

2. OVP latch output overvoltage protection (the HA17384H and HA17385H only)

The OVP latch is incorporated in the error amp input pin (FB). If the FB pin is pulled up to 7.0 V typ. just once when the power supply enters any kind of error state, IC operation can be halted and held as it is (latched). To reset the latch, drop the IC's supply voltage to 7.0 V typ. or below momentarily. An OVP latch application example is shown in figure 15.

Figure 15 Example of OVP Latch Application Circuit

This circuit protects the system by causing latch operation in the event of an overload or load short. In the steady state, the error amp input/output pins operate at 2.5 V typ., but if the load becomes heavy the FB pin level drops and the COMP pin level rises. As shown in the figure, this is detected by the HA17431 shunt regulator, and the FB pin level is pulled up, operating the OVP latch.

The operation parameters are as follows:

COMP pin voltage detection level: Vth =  $(R_1 + R_2) / R_2 \times 2.5 \text{ V}$

#### **Notice for Use**

#### 1. OVP Latch Block

#### Case

When DC power is applied directly as the power supply of the HA17384H, HA17385H, without using the transformer backup coil. Also, when high-frequency noise is superimposed on the  $V_{\rm IN}$  pin.

#### Problem

The IC may not be turn on in the case of a circuit in which  $V_{\rm IN}$  rises quickly (10 V/100  $\mu$ s or faster), such as that shown in figure 16. Also, the OVP latch may operate even though the FB pin is normally at  $V_{\rm OVP}$  or below after the IC is activated.

#### • Reason

Because of the IC circuit configuration, the timer latch block operates first.

#### • Remedy (counter measure)

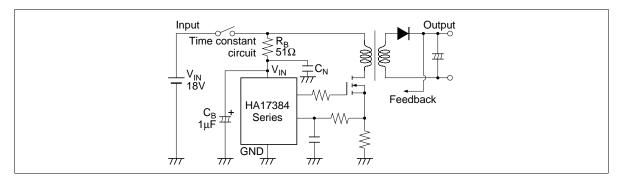

Take remedial action such as configuring a time constant circuit ( $R_B$ ,  $C_B$ ) as shown in figure 17, to keep the  $V_{IN}$  rise speed below 10 V/100  $\mu$ s. Also, if there is marked high-frequency noise on the  $V_{IN}$  pin, a noise cancellation capacitor ( $C_N$ ) with the best possible high-frequency characteristics (such as a ceramic capacitor) should be inserted between the  $V_{IN}$  pin and GND, and close to the  $V_{IN}$  pin.

When configuring an IC power supply with an activation resistance and backup winding, such as an AC/DC converter, the rise of  $V_{IN}$  will normally be around 1 V/100  $\mu$ s, and there is no risk of this problem occurring, but careful attention must be paid to high-frequency noise.

Also, this phenomenon is not occurring to the HA17384S, because OVP function is not built-in.

Figure 16 Example of Circuit with Fast V<sub>IN</sub> Rise Time

Figure 17 Sample Remedial Circuit

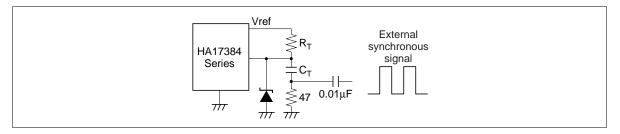

#### 2. Externally Synchronized Operation

Case

When, with a power supply using the HA17384S/H or HA17385H, externally synchronized operation is performed by applying an external syncronous signal to the  $R_T/C_T$  pin (pin 4).

- Problem

- Synchronized operation may not be possible if the amplitude of the external syncronous signal is too large.

- Reason

The  $R_T/C_T$  pin falls to a potential lower than the ground.

• Remedy (counter measure)

In this case, clamping is necessary using a diode with as small a  $V_F$  value as possible, such as a schottky barrier diode, as shown in figure 18.

Figure 18 Sample Remedial Circuit

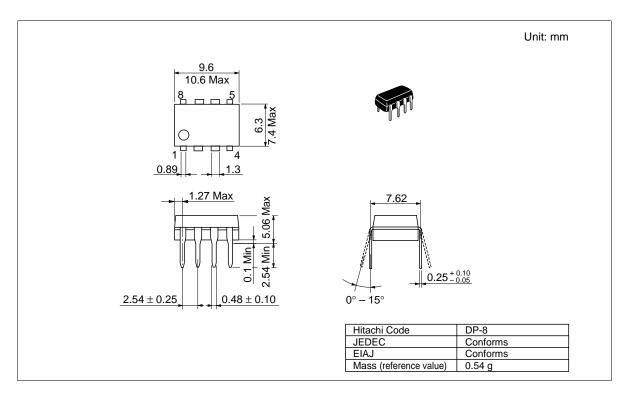

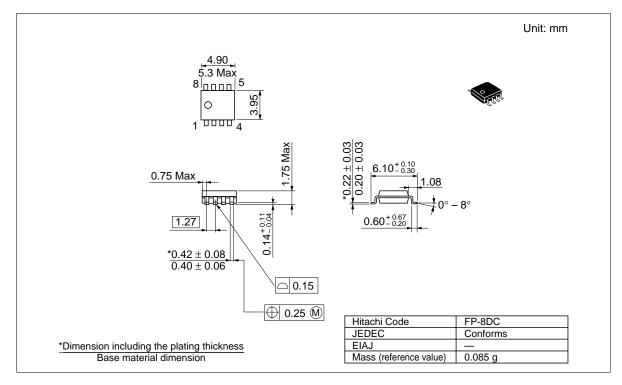

### **Package Dimensions**

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HTACH

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

NorthAmerica http:semiconductor.hitachi.com/

Europe Asia (Singapore) Asia (Taiwan) Asia (HongKong) http://www.hitachi-eu.com/hel/ecg http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm http://www.hitachi.com.hk/eng/bo/grp3/index.htm

Japan http://www.hitachi.co.jp/Sicd/indx.htm

#### For further information write to:

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Hitachi Europe GmbH Electronic components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany

Tel: <49 > (89) 9 9180-0 Fax: <49> (89) 9 29 30 00

Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead

Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167,

Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180

Copyright ' Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.

Hitachi Asia (Hong Kong) Ltd.

Kowloon, Hong Kong Tel: <852> (2) 735 9218

Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Group III (Electronic Components)

7/F., North Tower, World Finance Centre,

Harbour City, Canton Road, Tsim Sha Tsui,

HITACHI