# Dual Channel Line Receiver Hermetically Sealed Optocoupler

Technical Data

HCPL-1930 HCPL-1931 HCPL-193K 5962-89572

#### **Features**

- Dual Marked with Device Part Number and DSCC Standard Microcircuit Drawing

- Manufactured and Tested on a MIL-PRF-38534 Certified Line

- QML-38534, Class H and Class K

- Hermetically Sealed 16-pin Dual In-Line Package

- Performance Guaranteed Over -55°C to +125°C

- High Speed 10 Mb/s

- Accepts a Broad Range of Drive Conditions

- Adaptive Line Termination Included

- Internal Shield Provides Excellent Common Mode Rejection

- External Base Lead Allows "LED Peaking" and LED Current Adjustment

- 1500 Vdc Withstand Test Voltage

- High Radiation Immunity

- HCPL-2602 Function Compatibility

- Reliability Data Available

### **Applications**

- Military and Space

- High Reliability Systems

- Isolated Line Receiver

- Simplex/Multiplex Data Transmission

- Computer-Peripheral Interface

- Microprocessor System Interface

- Harsh Environmental Environments

- Digital Isolation for A/D, D/A Conversion

- Current Sensing

- Instrument Input/Output Isolation

- Ground Loop Elimination

- Pulse Transformer Replacement

## **Truth Table**

|   | (POSITIVE LOGIC) |        |        |  |  |  |  |

|---|------------------|--------|--------|--|--|--|--|

| ĺ | INPUT            | ENABLE | OUTPUT |  |  |  |  |

| ľ | ON               | Н      | L      |  |  |  |  |

| i | OFF              | Н      | н      |  |  |  |  |

| ľ | ON               | L      | н      |  |  |  |  |

| Ī | OFF              | L      | н      |  |  |  |  |

#### Description

The HCPL-193X devices are dual channel, hermetically sealed. high CMR, line receiver optocouplers. The products are capable of operation and storage over the full military temperature range and can be purchased as either a standard product or with full MIL-PRF-38534 Class Level H or K testing, or from the DSCC Standard Microcircuit Drawing (SMD) 5962-89572. This is a sixteen pin DIP which may be purchased with a variety of lead bend and plating options. See selection guide table for details. Standard Microcircuit Drawing (SMD) parts are available for each lead style.

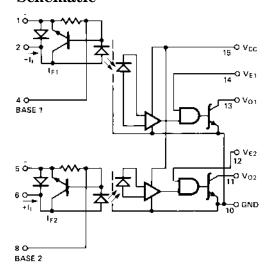

#### **Functional Diagram**

The connection of a 0.1 μF bypass capacitor between pins 15 and 10 is recommended.

All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DSCC Qualified Manufacturers List QML-38534 for Hybrid Microcircuits.

Each unit contains two independent channels, consisting of a GaAsP light emitting diode, an input current regulator, and an integrated high gain photon detector. The input regulator serves as a line termination for line receiver applications. It

clamps the line voltage and regulates the LED current so line reflections do not interfere with circuit performance. The regulator allows a typical LED current of 12.5 mA before it starts to shunt excess current. The output of the detector IC is an open collector Schottky clamped transistor. An enable input gates the detector. The internal detector shield provides a guaranteed common mode transient immunity specification of +1000 V/µsec.

DC specifications are compatible with TTL logic and are guaranteed from -55°C to +125°C allowing trouble-free interfacing with digital logic circuits. An input current of 10 mA will sink a six gate fan-out (TTL) at the output with a typical propagation delay from input to output of only 45 nsec.

### Selection Guide-Package Styles and Lead Configuration Options

| Add and Board # and Outleans |             |  |  |  |  |  |

|------------------------------|-------------|--|--|--|--|--|

| Agilent Part # and Options   |             |  |  |  |  |  |

| Commercial                   | HCPL-1930   |  |  |  |  |  |

| MIL-PRF-38534 Class H        | HCPL-1931   |  |  |  |  |  |

| MIL-PRF-38534 Class K        | HCPL-193K   |  |  |  |  |  |

| Standard Lead Finish         | Gold        |  |  |  |  |  |

| Solder Dipped                | Option #200 |  |  |  |  |  |

| Butt Joint/Gold Plate        | Option #100 |  |  |  |  |  |

| Gull Wing/Soldered           | Option #300 |  |  |  |  |  |

| Crew Cut/Gold Plate          | Option #600 |  |  |  |  |  |

| Class H SMD Part #           |             |  |  |  |  |  |

| Prescript for all below      | 5962-       |  |  |  |  |  |

| Either Gold or Soldered      | 8957201EX   |  |  |  |  |  |

| Gold Plate                   | 8957201EC   |  |  |  |  |  |

| Solder Dipped                | 8957201EA   |  |  |  |  |  |

| Butt Joint/Gold Plate        | 8957201YC   |  |  |  |  |  |

| Butt Joint/Soldered          | 8957201YA   |  |  |  |  |  |

| Gull Wing/Soldered           | 8957201XA   |  |  |  |  |  |

| Crew Cut/Gold Plate          | Available   |  |  |  |  |  |

| Crew Cut/Soldered            | Available   |  |  |  |  |  |

| Class K SMD Part #           |             |  |  |  |  |  |

| Prescript for all below      | 5962-       |  |  |  |  |  |

| Either Gold or Soldered      | 8957202KEX  |  |  |  |  |  |

| Gold Plate                   | 8957202KEC  |  |  |  |  |  |

| Solder Dipped                | 8957202KEA  |  |  |  |  |  |

| Butt Joint/Gold Plate        | 8957202KYC  |  |  |  |  |  |

| Butt Joint/Soldered          | 8957202KYA  |  |  |  |  |  |

| Gull Wing/Soldered           | 8957202KXA  |  |  |  |  |  |

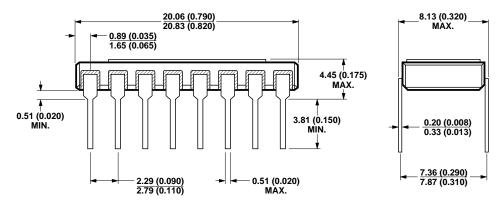

# Outline Drawings 16 Pin DIP Through Hole, 2 Channels

NOTE: DIMENSIONS IN MILLIMETERS (INCHES).

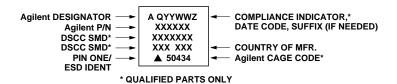

## **Device Marking**

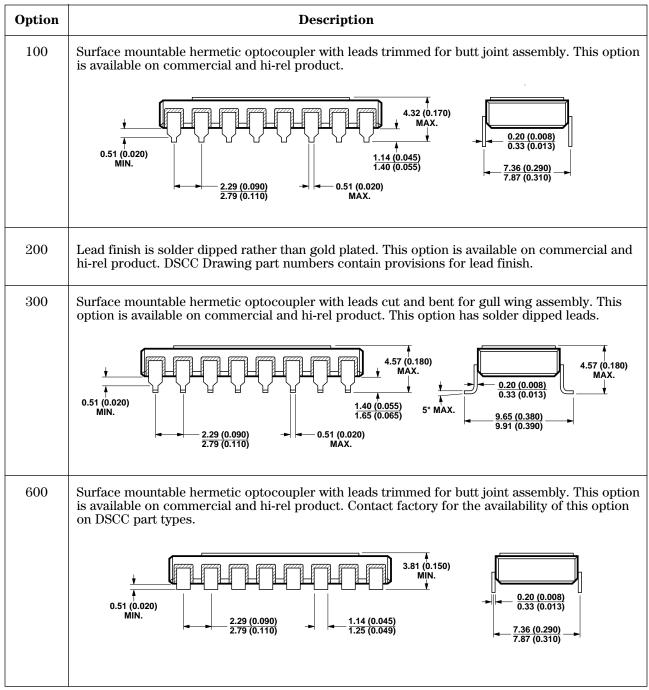

#### **Hermetic Optocoupler Options**

**Note:** Dimensions in millimeters (inches).

## **Absolute Maximum Ratings**

| Storage Temperature65°C to +150°C                        |

|----------------------------------------------------------|

| Operating Temperature55°C to +125°C                      |

| Lead Solder Temperature                                  |

| 1.6 mm below seating plane                               |

| Forward Input Current – I <sub>I</sub> (each channel)    |

| Reverse Input Current                                    |

| Supply Voltage – V <sub>CC</sub>                         |

| Enable Input Voltage – V <sub>E</sub> (each channel)     |

| Not to exceed $V_{CC}$ by more than 500 mV               |

| Output Collector Current – I <sub>O</sub> (each channel) |

| Output Collector Power Dissipation (each channel)        |

| Output Collector Voltage – $V_0$ (each channel)          |

| Total Package Power Dissipation564 mW                    |

| Input Power Dissipation (each channel)                   |

#### **Schematic**

A 0.1  $\mu\text{F}$  BYPASS CAPACITOR MUST BE CONNECTED BETWEEN PINS 10 AND 15 (SEE NOTE 1).

### **ESD Classification**

(MIL-STD-883, Method 3015) ......( $\Delta$ ), Class 1

## **Recommended Operating Conditions**

| Parameter                              | Symbol            | Min. | Max.         | Units                |

|----------------------------------------|-------------------|------|--------------|----------------------|

| Input Current, Low Level               | $I_{\mathrm{IL}}$ | 0    | 250          | μΑ                   |

| Input Current, High Level*             | $I_{\mathrm{IH}}$ | 12.5 | 60           | mA                   |

| Supply Voltage, Output                 | $V_{\rm CC}$      | 4.5  | 5.5          | V                    |

| High Level Enable Voltage              | $V_{\rm EH}$      | 2.0  | $V_{\rm CC}$ | V                    |

| Low Level Enable Voltage               | $V_{\rm EL}$      | 0    | 0.8          | V                    |

| Fan Out (@ $R_L = 4 \text{ k}\Omega$ ) | N                 |      | 5            | TTL<br>Loads         |

| Operating Temperature                  | $T_{A}$           | -55  | 125          | $^{\circ}\mathrm{C}$ |

$<sup>*12.5~\</sup>mathrm{mA}$  condition permits at least 20% guardband for optical coupling variation. Initial switching threshold is 10 mA or less.

# **Electrical Specifications** $T_A = -55$ °C to 125 °C unless otherwise stated. See note 15.

|                                                              |                        |                                                                                                                                                                                 | Group A        |      | Limits |      |       |      |              |

|--------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|--------|------|-------|------|--------------|

| Parameter                                                    |                        |                                                                                                                                                                                 | Sub-<br>groups | Min. | Typ.*  | Max. | Units | Fig. | Note         |

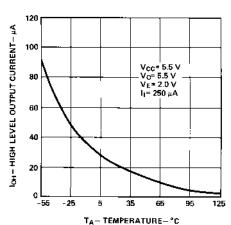

| High Level Output<br>Current                                 | $I_{OH}$               | $V_{CC} = 5.5 \text{ V}, V_{O} = 5.5 \text{ V}$ $I_{I} = 250  \mu\text{A}, V_{E} = 2.0 \text{ V}$                                                                               | 1, 2, 3        |      | 20     | 250  | μА    | 3    | 3            |

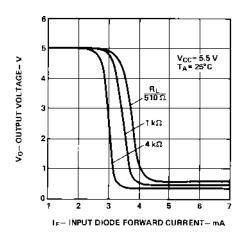

| Low Level<br>Output Voltage                                  | V <sub>OL</sub>        | $\begin{aligned} &V_{CC} = 5.5 \text{ V}; I_{I} = 10 \text{ mA} \\ &V_{E} = 2.0 \text{ V}, \\ &I_{OL} \text{ (Sinking)} = 10 \text{ mA} \end{aligned}$                          | 1, 2, 3        |      | 0.3    | 0.6  | V     | 1    | 3            |

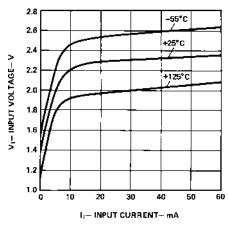

|                                                              |                        | $I_{\rm I} = 10 \text{ mA}$                                                                                                                                                     | 1.0.0          |      | 2.2    | 2.6  | **    | 2    |              |

| Input Voltage                                                | $V_{I}$                | $I_{\rm I} = 60 \text{ mA}$                                                                                                                                                     | 1, 2, 3        |      | 2.35   | 2.75 | V     |      | 3            |

| Input Reverse<br>Voltage                                     | $V_{R}$                | $I_R = 10 \text{ mA}$                                                                                                                                                           | 1, 2, 3        |      | 0.8    | 1.10 | V     |      | 3            |

| Low Level Enable<br>Current                                  | $I_{\mathrm{EL}}$      | $V_{CC} = 5.5 \text{ V}, V_{E} = 0.5 \text{ V}$                                                                                                                                 | 1, 2, 3        |      | -1.45  | -2.0 | mA    |      | 3            |

| High Level Enable<br>Voltage                                 | $V_{\rm EH}$           |                                                                                                                                                                                 | 1, 2, 3        | 2.0  |        |      | V     |      | 3, 12        |

| Low Level Enable<br>Voltage                                  | $ m V_{EL}$            |                                                                                                                                                                                 | 1, 2, 3        |      |        | 0.8  | V     |      | 3            |

| High Level<br>Supply Current                                 | $I_{CCH}$              | $V_{CC} = 5.5 \text{ V}; I_I = 0,$<br>$V_E = 0.5 \text{ V} \text{ both channels}$                                                                                               | 1, 2, 3        |      | 21     | 28   | mA    |      |              |

| Low Level<br>Supply Current                                  | I <sub>CCL</sub>       | $V_{CC} = 5.5 \text{ V}; I_I = 60 \text{ mA},$<br>$V_E = 0.5 \text{ V} \text{ both channels}$                                                                                   | 1, 2, 3        |      | 27     | 36   | mA    |      |              |

| Input-Output<br>Insulation<br>Leakage Current                | I <sub>I-O</sub>       | Relative Humidity = $45\%$<br>t = $5$ s,<br>$V_{LO}$ = $1500$ Vdc                                                                                                               | 1              |      |        | 1    | μА    |      | 4            |

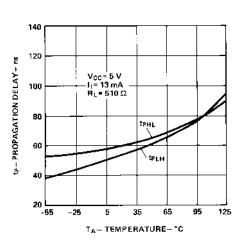

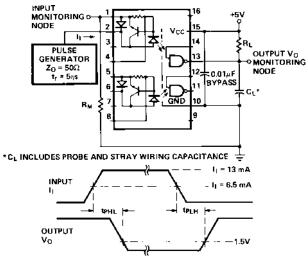

| Propagation Delay<br>Time to High                            | +                      | $R_{L} = 510 \ \Omega; C_{L} = 50 \ pF,$                                                                                                                                        | 9              |      | 55     | 100  | ne    | 4, 5 | 3, 5         |

| Output Level                                                 | ${ m t_{PLH}}$         | $I_{\rm L} = 510  \Omega_{\rm C}, C_{\rm L} = 50  \text{pr},$<br>$I_{\rm I} = 13  \text{mA}, V_{\rm CC} = 5.0  \text{V}$                                                        | 10, 11         |      |        | 140  | ns    | 4, 0 |              |

| Propagation Delay<br>Time to Low                             | Delay t <sub>PHL</sub> | $R_{L} = 510 \ \Omega; C_{L} = 50 \ pF,$<br>$I_{I} = 13 \ mA, V_{CC} = 5.0 \ V$                                                                                                 | 9              |      | 60     | 100  | ns    | 4, 5 | 3, 6         |

| Output Level                                                 |                        |                                                                                                                                                                                 | 10, 11         |      |        | 120  |       |      |              |

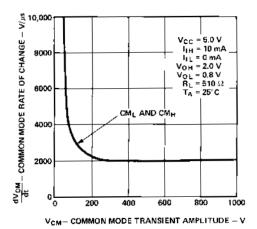

| Common Mode<br>Transient<br>Immunity at<br>High Output Level | $ \mathrm{CM_H} $      | $\begin{aligned} &V_{CM} = 50 \text{ V (peak)}, \\ &V_{O} \text{ (min.)} = 2 \text{ V}, \\ &R_{L} = 510 \Omega; I_{I} = 0 \text{ mA}, \\ &V_{CC} = 5.0 \text{ V} \end{aligned}$ | 9, 10, 11      | 1000 | 10,000 |      | V/µs  | 8, 9 | 3, 9,<br>14  |

| Common Mode<br>Transient<br>Immunity at<br>Low Output Level  | $ \mathrm{CM_L} $      | $\begin{split} &V_{CM} = 50 \ V \ (peak), \\ &V_{O} \ (max.) = 0.8 \ V, \\ &R_{L} = 510 \ \Omega; \ I_{I} = 10 \ mA, \\ &V_{CC} = 5.0 \ V \end{split}$                          | 9, 10, 11      | 1000 | 10,000 |      | V/μs  | 8, 9 | 3, 10,<br>14 |

<sup>\*</sup>All typical values are at  $V_{\rm CC}$  = 5 V,  $T_{\rm A}$  = 25°C.

#### **Typical Specifications**

$T_A = 25$ °C,  $V_{CC} = 5$  V

| Parameter                                                                                      | Symbol                    | Тур. | Units | Test Conditions                                                                                                                                           | Fig. | Note  |

|------------------------------------------------------------------------------------------------|---------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| Resistance (Input-Output)                                                                      | R <sub>I-O</sub>          | 1012 | Ω     | $V_{I-O} = 500 \text{ V dc}$                                                                                                                              |      | 3, 13 |

| Capacitance (Input-Output)                                                                     | C <sub>I-O</sub>          | 1.7  | pF    | f = 1 MHz                                                                                                                                                 |      | 3, 13 |

| Input-Input Insulation<br>Leakage Current                                                      | I <sub>I-I</sub>          | 0.5  | nA    | 45% Relative Humidity,<br>$V_{LI} = 500 \text{ Vdc}, t = 5 \text{ s}$                                                                                     |      | 11    |

| Resistance (Input-Input)                                                                       | R <sub>I-I</sub>          | 1012 | Ω     | $V_{IJ} = 500 \text{ Vdc}$                                                                                                                                |      | 11    |

| Capacitance (Input-Input)                                                                      | $C_{\text{\tiny I-I}}$    | 0.55 | pF    | f = 1 MHz                                                                                                                                                 |      | 11    |

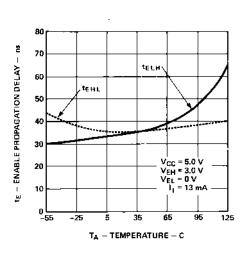

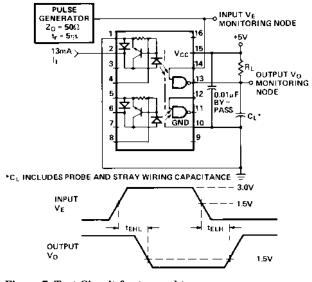

| Propagation Delay Time of Enable from $\mathbf{V}_{\text{EH}}$ to $\mathbf{V}_{\text{EL}}$     | t <sub>ELH</sub>          | 35   | ns    | D = 510 O C = 15 pF                                                                                                                                       | 6, 7 | 3, 7  |

| Propagation Delay Time of Enable from $\mathbf{V}_{\mathrm{EL}}$ to $\mathbf{V}_{\mathrm{EH}}$ | $t_{_{\rm EHL}}$          | 35   | ns    | $\begin{cases} R_{\rm L} = 510 \ \Omega, C_{\rm L} = 15 \ \rm pF, \\ I_{\rm I} = 13 \ \rm mA, V_{\rm EH} = 3 \ \rm V, V_{\rm EL} = 0 \ \rm V \end{cases}$ | 6, 7 | 3, 8  |

| Output Rise Time (10-90%)                                                                      | t <sub>r</sub>            | 30   | ns    | D = 510 O C = 15 pE I = 12 mA                                                                                                                             |      | 3     |

| Output Fall Time (90-10%)                                                                      | $\mathbf{t}_{\mathrm{f}}$ | 24   | ns    | $R_{L} = 510 \Omega, C_{L} = 15 pF, I_{I} = 13 mA$                                                                                                        |      | 3     |

| Input Capacitance                                                                              | $C_{I}$                   | 60   | pF    | $f = 1 \text{ MHz}, V_1 = 0,$<br>PINS 1 to 2 or 5 to 6                                                                                                    |      | 3     |

#### Notes:

- 1. Bypassing of the power supply line is required, with a 0.1 µF ceramic disc capacitor adjacent to each isolator. The power supply bus for the isolators should be separate from the bus for any active loads, otherwise additional bypass capacitance may be needed to suppress regenerative feedback via the power supply.

- 2. Derate linearly at 1.2 mA/°C above  $T_A = 100$ °C.

- 3. Each channel.

- 4. Device considered a two terminal device: pins 1 through 8 are shorted together, and pins 9 through 16 are shorted together.

- 5. The t<sub>PLH</sub> propagation delay is measured form the 6.5 mA point on the trailing edge of the input pulse to the 1.5 V point on the trailing edge of the output pulse.

- 6. The  $t_{\text{PHL}}$  propagation delay is measured from the 6.5 mA point on the leading edge of the input pulse to the 1.5 V point on the leading edge of the output pulse.

- 7. The  $t_{\text{ELH}}$  enable propagation delay is measured from the 1.5 V point on the trailing edge of the enable input pulse to the 1.5 V point on the trailing edge of the output pulse.

- 8. The  $t_{\text{EHL}}$  enable propagation delay is measured from the 1.5 V point on the leading edge of the enable input pulse to the 1.5 V point on the leading edge of the output pulse.

- $9.\,$  CM $_{

m H}$  is the maximum tolerable rate of rise of the common mode voltage to assure that the output will remain in a high logic state, i.e.  $V_{OUT}^{H} > 2.0 \text{ V}$ .

10.  $CM_{L}^{H}$  is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state, i.e.

- $V_{OUT}^{L} < 0.8 \text{ V}.$ 11. Measured between adjacent input leads shorted together, i.e. between 1, 2 and 4 shorted together and pins 5, 6 and 8 shorted

- together.

- 12. No external pull up is required for a high logic state on the enable input.

- 13. Measured between pins 1 and 2 or 5 and 6 shorted together, and pins 10 through 15 shorted together.

- 14. Parameters shall be tested as part of device initial characterization and after process changes. Parameters shall be guaranteed to the limits specified for all lots not specifically tested.

- 15. Standard parts receive 100% testing at 25℃ (Subgroups 1 and 9). Hi-Rel and SMD parts receive 100% testing at 25, 125, and -55℃ (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).

Figure 1. Input-Output Characteristics.

Figure 2. Input Characteristics.

Figure 3. High Level Output Current vs. Temperature.

Figure 4. Propagation Delay vs. Temperature.

Figure 5. Test Circuit for  $\boldsymbol{t}_{_{\boldsymbol{P}\boldsymbol{H}\boldsymbol{L}}}$  and  $\boldsymbol{t}_{_{\boldsymbol{P}\boldsymbol{L}\boldsymbol{H}}}.$

Figure 6. Enable Propagation Delay vs. Temperature.

Figure 7. Test Circuit for  $\boldsymbol{t}_{\scriptscriptstyle EHL}$  and  $\boldsymbol{t}_{\scriptscriptstyle ELH}.$

Figure 8. Typical Common Mode Transient Immunity.

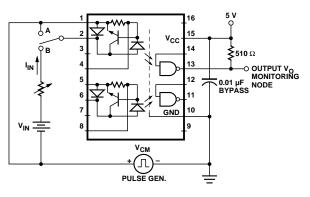

Figure 9. Test Circuit for Common Mode Transient Immunity and Typical Waveforms.

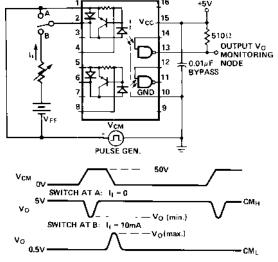

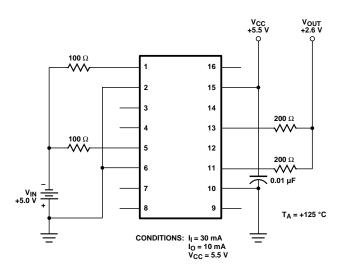

Figure 10. Burn In Circuit.

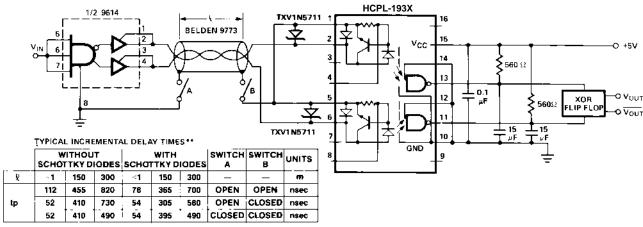

## **Application Circuits\***

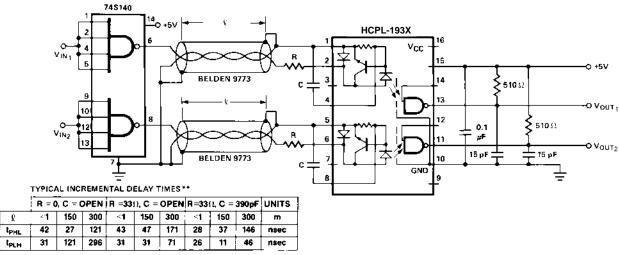

PROPAGATION DELAY TIMES SHOWN EXCLUDE DRIVER AND LINE DELAYS.

Figure A<sub>1</sub>. Polarity Non-Reversing.

PROPAGATION DELAY TIMES SHOWN EXCLUDE DRIVER AND LINE DELAYS USING 1/3 74LSO4 INVERTERS AND 74LSO0 QUAD NAND

Figure  $A_2$ . Polarity Reversing, Split Phase.

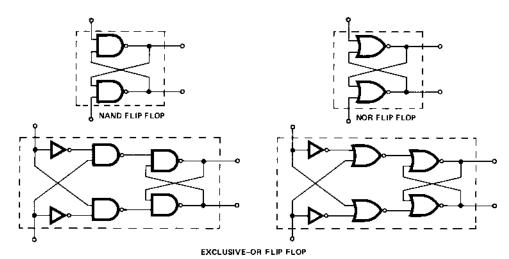

NAND flip flop tolerates simultaneously HIGH inputs; NOR flip flop tolerates simultaneously LOW inputs; EXCLUSIVEOR flip flop tolerates simultaneously HIGH OR LOW inputs without causing either of the outputs to change.

\*FOR A DESCRIPTION OF THESE CIRCUITS SEE HCPL-2602 DATA SHEET.

Figure  $A_3$ . Flop-Flop Configurations.

# MIL-PRF-38534 Class H, Class K, and DSCC SMD Test Program

Agilent Technologies' Hi-Rel Optocouplers are in compliance with MIL-PRF-38534 Class H and K. Class H and Class K devices are also in compliance with DSCC drawing 5962-89572.

Testing consists of 100% screening and quality conformance inspection to MIL-PRF-38534.