# intersil

# 捷多邦,专业PCB打样工厂,24小时加急出货 **HGTG12N60D1D**

12A, 600V N-Channel IGBT with Anti-Parallel Ultrafast Diode

**April 1995**

### Features

- 12A, 600V

- Latch Free Operation

- Typical Fall Time <500ns

- Low Conduction Loss

- With Anti-Parallel Diode

- t<sub>RR</sub> < 60ns</li>

### **Description**

The IGBT is a MOS gated high voltage switching device combining the best features of MOSFETs and bipolar transistors. The device has the high input impedance of a MOSFET and the low on-state conduction loss of a bipolar transistor. The much lower on-state voltage drop varies only moderately between +25°C and +150°C. The diode used in parallel with the IGBT is an ultrafast ( $t_{RR}$  < 60ns) with soft recovery characteristic.

The IGBTs are ideal for many high voltage switching applications operating at frequencies where low conduction losses are essential, such as: AC and DC motor controls, power supplies and drivers for solenoids, relays and contactors.

#### **PACKAGING AVAILABILITY**

| PART NUMBER  | PACKAGE  | BRAND     |

|--------------|----------|-----------|

| HGTG12N60D1D | TO-220AB | G12N60D1D |

NOTE: When ordering, use the entire part number

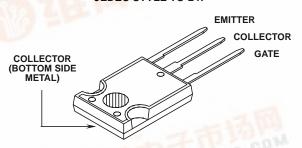

## Package

#### **JEDEC STYLE TO-247**

## Terminal Diagram

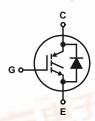

#### N-CHANNEL ENHANCEMENT MODE

#### Absolute Maximum Ratings T<sub>C</sub> = +25°C, Unless Otherwise Specified

|                                                           | HG I G12N60D1D               | UNITS |

|-----------------------------------------------------------|------------------------------|-------|

| Collector-Emitter Voltage                                 | 600                          | V     |

| Collector-Gate Voltage $R_{GE} = 1M\Omega \dots BV_{CGR}$ | 600                          | V     |

| Collector Current Continuous at T <sub>C</sub> = +25°C    | 21                           | Α     |

| at $T_C = +90^{\circ}C$                                   | 12                           | Α     |

| Collector Current Pulsed (Note 1)                         | 48                           | Α     |

| Gate-Emitter Voltage ContinuousV <sub>GES</sub>           | ±20                          | V     |

| Switching Safe Operating Area at T <sub>J</sub> = +150°C  | 30A at 0.8 BV <sub>CES</sub> | -     |

| Diode Forward Current at $T_C = +25^{\circ}C$ $I_{F25}$   | 21                           | Α     |

| at T <sub>C</sub> = +90°CI <sub>F90</sub>                 | 12                           | Α     |

| Power Dissipation Total at $T_C = +25^{\circ}C$ $P_D$     | 75                           | W     |

| Power Dissipation Derating T <sub>C</sub> > +25°C         | 0.6                          | W/°C  |

| Operating and Storage Junction Temperature Range          | -55 to +150                  | °C    |

| Maximum Lead Temperature for SolderingT <sub>L</sub>      | 260                          | °C    |

| (0.125 inches from case for 5s)                           |                              |       |

#### NOTE:

1. Repetitive Rating: Pulse width limited by maximum junction temperature.

#### INTERSIL CORPORATION IGBT PRODUCT IS COVERED BY ONE OR MORE OF THE FOLLOWING U.S. PATENTS:

| 4,364,073 | 4,417,385 | 4,430,792 | 4,443,931 | 4,466,176 | 4,516,143 | 4,532,534 | 4,567,641 |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 4,587,713 | 4,598,461 | 4,605,948 | 4,618,872 | 4,620,211 | 4,631,564 | 4,639,754 | 4,639,762 |

| 4,641,162 | 4,644,637 | 4,682,195 | 4,684,413 | 4,694,313 | 4,717,679 | 4,743,952 | 4,783,690 |

| 4,794,432 | 4,801,986 | 4,803,533 | 4,809,045 | 4,809,047 | 4,810,665 | 4,823,176 | 4,837,606 |

| 4,860,080 | 4,883,767 | 4,888,627 | 4,890,143 | 4,901,127 | 4,904,609 | 4,933,740 | 4,963,951 |

| 4 000 007 |           |           |           |           |           |           |           |

## Specifications HGTG12N60D1D

**Electrical Specifications**  $T_C = +25$ °C, Unless Otherwise Specified

|                                      |                      | TEST CONDITIONS                                                                                                     |                                       | LIMITS |     |      |       |

|--------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|-----|------|-------|

| PARAMETERS                           | SYMBOL               |                                                                                                                     |                                       | MIN    | TYP | MAX  | UNITS |

| Collector-Emitter Breakdown Voltage  | BV <sub>CES</sub>    | $I_C = 280 \mu A, V_{GE} = 0 V$                                                                                     |                                       | 600    | -   | -    | V     |

| Collector-Emitter Leakage Voltage    | I <sub>CES</sub>     | V <sub>CE</sub> = BV <sub>CES</sub>                                                                                 | $T_{\rm C} = +25^{\rm o}{\rm C}$      | -      | -   | 280  | μΑ    |

|                                      |                      | V <sub>CE</sub> = 0.8 BV <sub>CES</sub>                                                                             | $T_{\rm C} = +125^{\rm o}{\rm C}$     | -      | -   | 5.0  | mA    |

| Collector-Emitter Saturation Voltage | V <sub>CE(SAT)</sub> | $I_{C} = I_{C90}, V_{GE} = 15V$                                                                                     | $T_{\rm C} = +25^{\rm o}{\rm C}$      | -      | 1.9 | 2.5  | V     |

|                                      |                      |                                                                                                                     | $T_{\rm C} = +125^{\rm o}{\rm C}$     | -      | 2.1 | 2.7  | V     |

| Gate-Emitter Threshold Voltage       | V <sub>GE(TH)</sub>  | $I_{C} = 250 \mu A, V_{CE} = V_{G}$                                                                                 | <sub>E</sub> , T <sub>C</sub> = +25°C | 3.0    | 4.5 | 6.0  | V     |

| Gate-Emitter Leakage Current         | I <sub>GES</sub>     | V <sub>GE</sub> = ±20V                                                                                              |                                       | -      | -   | ±500 | nA    |

| Gate-Emitter Plateau Voltage         | V <sub>GEP</sub>     | $I_{C} = I_{C90}, V_{CE} = 0.5 \text{ BV}_{CES}$                                                                    |                                       | -      | 7.2 | -    | V     |

| On-State Gate Charge                 | Q <sub>G(ON)</sub>   | $V_{CE} = V_{CS}$ $V_{GE} = 15V$ $V_{GE} = 20V$                                                                     | V <sub>GE</sub> = 15V                 | -      | 45  | 60   | nC    |

|                                      |                      |                                                                                                                     | V <sub>GE</sub> = 20V                 | -      | 70  | 90   | nC    |

| Current Turn-On Delay Time           | t <sub>D(ON)I</sub>  | $L = 500 \mu H, I_C = I_{C90}, R_G = 25 V,$ $V_{GE} = 15 V, T_J = +150 ^{\circ} C,$ $V_{CE} = 0.8 \text{ BV}_{CES}$ |                                       | -      | 100 | -    | ns    |

| Current Rise Time                    | t <sub>RI</sub>      |                                                                                                                     |                                       | -      | 150 | -    | ns    |

| Current Turn-Off                     | t <sub>D(OFF)I</sub> |                                                                                                                     |                                       | -      | 430 | 600  | ns    |

| Current Fall Time                    | t <sub>Fl</sub>      |                                                                                                                     |                                       | -      | 430 | 600  | ns    |

| Turn-Off Energy (Note 1)             | W <sub>OFF</sub>     |                                                                                                                     |                                       | -      | 1.8 | -    | mJ    |

| Thermal Resistance IGBT              | $R_{\theta JC}$      |                                                                                                                     |                                       | -      | -   | 1.67 | °C/W  |

| Thermal Resistance Diode             | $R_{\theta JC}$      |                                                                                                                     |                                       | -      | -   | 1.5  | °C/W  |

| Diode Forward Voltage                | V <sub>EC</sub>      | I <sub>EC</sub> = 12A                                                                                               |                                       | -      | -   | 1.50 | V     |

| Diode Reverse Recovery Time          | t <sub>RR</sub>      | $I_{EC} = 12A, dI_{EC}/dt = 1$                                                                                      | 00A/μs                                | -      | -   | 60   | ns    |

#### NOTE:

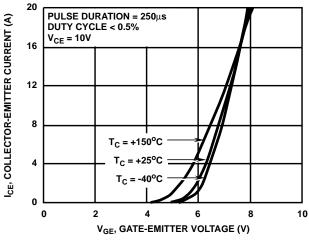

## **Typical Performance Curves**

FIGURE 1. TRANSFER CHARACTERISTICS (TYPICAL)

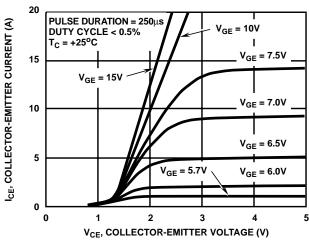

FIGURE 2. SATURATION CHARACTERISTICS (TYPICAL)

<sup>1.</sup> Turn-off Energy Loss (W<sub>OFF</sub>) is defined as the integral of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero (I<sub>CE</sub> = 0A). The HGTG12N60D1D was tested per JEDEC standard No. 24-1 Method for Measurement of Power Device Turn-off Switching Loss. This test method produces the true total Turn-off Energy Loss.

#### HGTG12N60D1D

## Typical Performance Curves (Continued)

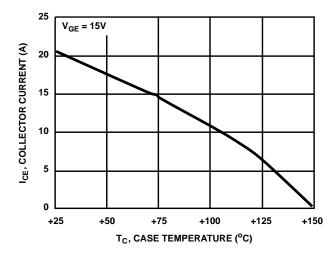

FIGURE 3. DC COLLECTOR CURRENT vs CASE TEMPERATURE

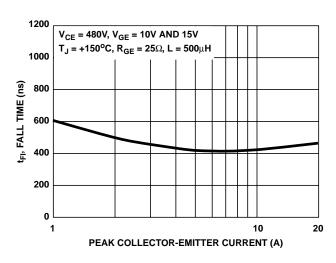

FIGURE 4. FALL TIME vs COLLECTOR-EMITTER CURRENT

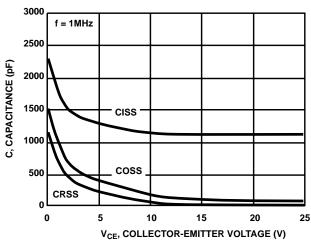

FIGURE 5. CAPACITANCE vs COLLECTOR-EMITTER VOLTAGE

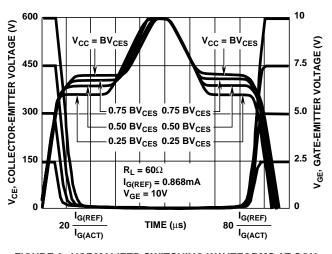

FIGURE 6. NORMALIZED SWITCHING WAVEFORMS AT CON-STANT GATE CURRENT. (REFER TO APPLICATION NOTES AN7254 AND AN7260)

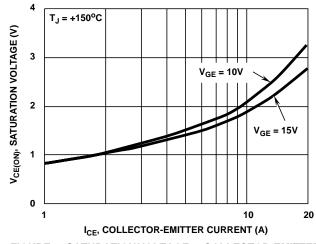

FIGURE 7. SATURATION VOLTAGE vs COLLECTOR-EMITTER CURRENT

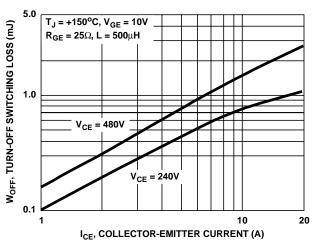

FIGURE 8. TURN-OFF SWITCHING LOSS vs COLLECTOR-EMITTER CURRENT

#### HGTG12N60D1D

## Typical Performance Curves (Continued)

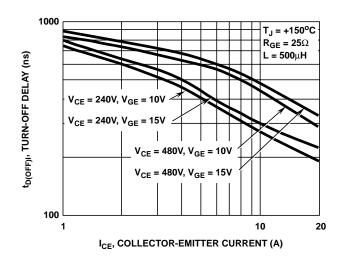

FIGURE 9. TURN-OFF DELAY vs COLLECTOR-EMITTER CURRENT

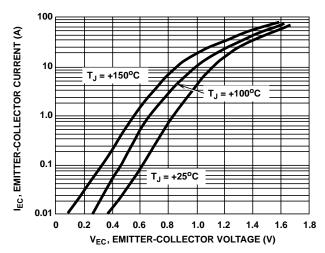

FIGURE 11. TYPICAL DIODE EMITTER-TO-COLLECTOR VOLTAGE

$P_D$  = ALLOWABLE DISSIPATION  $P_C$  = CONDUCTION DISSIPATION

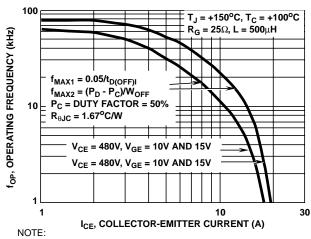

FIGURE 10. OPERATING FREQUENCY vs COLLECTOR-EMITTER CURRENT AND VOLTAGE

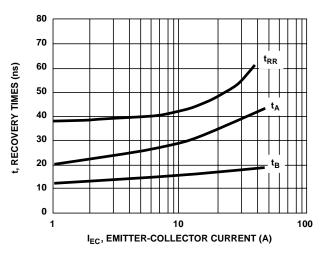

FIGURE 12. TYPICAL t<sub>RR</sub>, t<sub>A</sub>, t<sub>B</sub> vs FORWARD CURRENT

## Operating Frequency Information

Operating frequency information for a typical device (Figure 10) is presented as a guide for estimating device performance for a specific application. Other typical frequency vs collector current ( $I_{CE}$ ) plots are possible using the information shown for a typical unit in Figures 7, 8 and 9. The operating frequency plot (Figure 10) of a typical device shows  $f_{MAX1}$  or  $f_{MAX2}$  whichever is smaller at each point. The information is based on measurements of a typical device and is bounded by the maximum rated junction temperature.

$f_{MAX1}$  is defined by  $f_{MAX1}=0.05/t_{D(OFF)I}.\ t_{D(OFF)I}$  deadtime (the denominator) has been arbitrarily held to 10% of the onstate time for a 50% duty factor. Other definitions are possible.  $t_{D(OFF)I}$  is defined as the time between the 90% point of the trailing edge of the input pulse and the point where the collector current falls to 90% of its maximum value. Device turn-off delay can establish an additional

frequency limiting condition for an application other than  $T_{\text{JMAX}}$ .  $t_{\text{D(OFF)I}}$  is important when controlling output ripple under a lightly loaded condition.

$f_{MAX2}$  is defined by  $f_{MAX2}=(P_D-P_C)/W_{OFF}.$  The allowable dissipation  $(P_D)$  is defined by  $P_D=(T_{JMAX}-T_C)/R_{\theta JC}.$  The sum of device switching and conduction losses must not exceed  $P_D.$  A 50% duty factor was used (Figure 10) so that the conduction losses  $(P_C)$  can be approximated by  $P_C=(V_{CE}\ x\ I_{CE})/2.$   $W_{OFF}$  is defined as the sum of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero ( $I_{CE}$ -0A).

The switching power loss (Figure 10) is defined as  $f_{MAX1} \times W_{OFF}$ . Turn on switching losses are not included because they can be greatly influenced by external circuit conditions and components.

## HGTG12N60D1D

| All Intersil semiconductor p                                                   | products are manufactured, assemble                                                                           | ed and tested under <b>ISO9000</b> quality systems                                                                                                                                                                                                       | certification.      |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| notice. Accordingly, the reader is ca<br>and reliable. However, no responsible | utioned to verify that data sheets are current bef<br>ility is assumed by Intersil or its subsidiaries for it | to make changes in circuit design and/or specifications a<br>ore placing orders. Information furnished by Intersil is belie<br>s use; nor for any infringements of patents or other rights of<br>atent or patent rights of Intersil or its subsidiaries. | eved to be accurate |

| For i                                                                          | nformation regarding Intersil Corporation and its p                                                           |                                                                                                                                                                                                                                                          |                     |

| Sales Office Headq                                                             |                                                                                                               |                                                                                                                                                                                                                                                          |                     |

| NORTH AMERICA<br>Intersil Corporation                                          | EUROPE<br>Intersil SA                                                                                         | <b>ASIA</b><br>Intersil (Taiwan) Ltd.                                                                                                                                                                                                                    |                     |

Taiwan Limited

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

7F-6, No. 101 Fu Hsing North Road

Mercure Center

100, Rue de la Fusee

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

1130 Brussels, Belgium

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240