Data Sheet

April 1999 File Number

4047.2

<sup>24小时加急出</sup>件IP0045

## 1A/50V Octal Low Side Power Driver With Serial Bus Control and Fault Protection

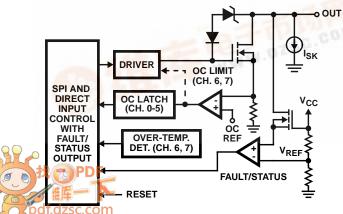

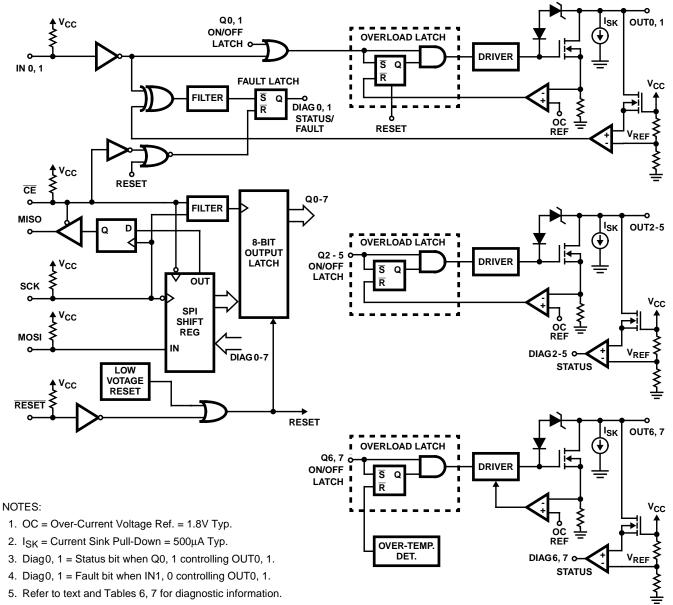

The HIP0045 is a logic controlled, eight channel Octal Serial Power Low Side Driver. The serial peripheral interface (SPI) utilized by the HIP0045 is a serial synchronous bus compatible with Intersil CDP68HC05, or equivalent, microcomputers. As shown in the Block Diagram for the HIP0045, each of the open drain MOS Output Drivers have individual protection for overvoltage and over-current. Each output channel has separate output latch control with fault unlatch and diagnostic or status feedback. Under normal ON conditions, each output driver is in a low voltage, high current state of saturated turn-on. Comparators in the diagnostic circuitry monitor the output drivers to determine if an out of saturation condition exists. If a fault is sensed, the respective output driver for Channels 0 - 5 have overcurrent latch-off. Channels 6 and 7 are configured for lamp drivers and have current limiting with over-temperature latch-off. Channels 0 and 1 have direct parallel drive control for PWM applications and are ORed with the SPI Bus control. All channels are SPI Bus controlled and sense the output states for diagnostic feedback.

The HIP0045 is fabricated in a Power BiMOS IC process, and is intended for use in automotive and other applications having a wide range of temperature and electrical stress conditions. It is particularly suited for driving relays, solenoids and lamps in applications where low standby power, high operating voltage, and high output current in high ambient temperature conditions is required.

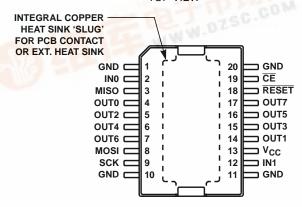

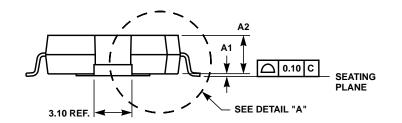

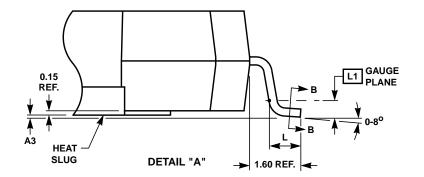

The HIP0045 is in a 20 lead plastic Power SOP (PSOP) Package with an integral copper 'slug' to conduct heat directly to a PCB interface or heat sink on the bottom of the package.

## **Ordering Information**

| PART NO.  | TEMP. RANGE ( <sup>o</sup> C) | MP. RANGE ( <sup>o</sup> C) PACKAGE |         |

|-----------|-------------------------------|-------------------------------------|---------|

| HIP0045AB | -40 to 125                    | 20 Ld PSOP                          | M20.433 |

## Driver Block Diagram

#### Features

- Octal NDMOS Output Drivers in a High Voltage Power **BiMOS Process**

- Over-Stress Protection Each Output:

专业PCB打样工厂

- Over-Current Protection ...... 1A Min

- Thermal Shutdown Protection (2 Channels)

- Open-Load Detection

- Power BiMOS Output Configuration

- Current Latch-Off Protection for 6 Channels: 2 with External Drive Input and ORed with SPI Bus Control

- 2 Channels Configured for Lamp Drivers with Current Limiting and Over-Temperature Latch-Off

- High Speed CMOS Logic Control

- SPI Bus Controlled Interface

- Individual Output Latch

- Individual Fault Unlatch and Feedback

- Common Reset Line

- Ambient Operating Temp. Range ..... -40°C to 125°C DZSC.COM

## Applications

- Automotive and Industrial Systems

- Solenoids, Relays and Lamp Drivers

- Logic and µP Controlled Drivers

- Robotic Controls

#### Pinout

#### HIP0045 (PSOP WITH HEAT SLUG) TOP VIEW

## **Detailed Block Diagram**

5. Refer to text and Tables 6, 7 for diagnostic information.

## Input to Output Control Tables

TABLE 1. OUTPUT 0

| SPI BIT 0 | INO | OUT0 |

|-----------|-----|------|

| 0         | 1   | OFF  |

| 0         | 0   | ON   |

| 1         | 0   | ON   |

| 1         | 1   | ON   |

| TABLE 2. | <b>OUTPUT 1</b> |

|----------|-----------------|

|          |                 |

| SPI BIT 1 | IN1 | OUT1 |

|-----------|-----|------|

| 0         | 1   | OFF  |

| 0         | 0   | ON   |

| 1         | 0   | ON   |

| 1         | 1   | ON   |

TABLE 3. OUTPUT 2 - 7

| SPI BIT 2 - 7 | OUT2 - 7 |

|---------------|----------|

| 0             | OFF      |

| 1             | ON       |

#### TABLE 4. OUTPUT CONTROL REGISTER, Q0 - 7

| (D7I) (D6I) (D5I) (D4I) (D3I) (D2I) (D |           |

|----------------------------------------|-----------|

|                                        | II) (D0I) |

| Q1 Q3 Q5 Q7 Q0 Q2 Q                    | 4 Q6      |

NOTE: The Output Control Register bits Q0 -7 have the same order as the Diagnostic Failure Register bits Diag0 - 7 as defined in Table 5. Data bits D0I - D7I give the MOSI SPI serial data input flow sequence.

#### **Absolute Maximum Ratings**

#### **Operating Conditions**

| Temperature Range                     | -40 <sup>o</sup> C to 125 <sup>o</sup> C |

|---------------------------------------|------------------------------------------|

| Logic Supply Voltage, V <sub>CC</sub> |                                          |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 6)         | $\theta_{JA}$ ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)  |

|----------------------------------------------|-----------------------------------|--------------------------------------|

| PSOP Package                                 | 40                                | 2                                    |

| Maximum Junction Temperature, T <sub>J</sub> |                                   |                                      |

| Maximum Storage Temperature Range, T         | STG55                             | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1        | 0s)                               | 265 <sup>0</sup> C                   |

|                                              |                                   |                                      |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

6.  $\theta_{JA}$  Rated with standard PC Board,  $\theta_{JC}$  rated with infinite heat sink.

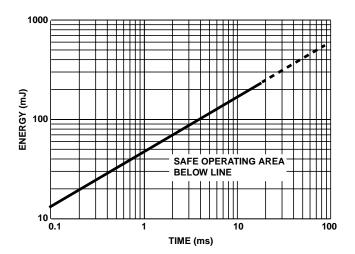

#### $V_{CC}$ = 4.5V to 5.5V, $T_A$ = -40 $^oC$ to 125 $^oC$ , Unless Otherwise Specified Electrical Specifications PARAMETER SYMBOL UNITS **TEST CONDITIONS** MIN TYP MAX Standby Current, No Load No Load 5 mΑ lcco \_ \_ Supply Current, Full Load lcc All Outputs ON, 0.5A Load Per Output --5 mΑ I<sub>LOAD</sub> = 0.5A, Output Programmed OFF Output Clamping Voltage (Note 7) 62 V Voc 45 Output Clamping Energy 1ms Single Pulse Width, $T_A = 25^{\circ}C$ , 45 EOC 20 mJ (Refer to Figure 4 for SOA) Output Leakage Current 1 (Note 8) V<sub>OUT</sub> = 25V, Outputs OFF 100 μA O LEAK1 Output Leakage Current 2 (Note 8) V<sub>OUT</sub> = 16V, Outputs OFF 100 μΑ O LEAK2 --Output Leakage Current 3 (Note 8) V<sub>OUT</sub> = 16V, Outputs OFF, V<sub>CC</sub> = 1V 10 μΑ O LEAK3 Drain-to-Source On Resistance, OUT0 - 7 $I_{LOAD} = 0.5A; T_{J} = 150^{\circ}C$ 1.5 Ω **r**DSON Output Capacitance V<sub>OUT</sub> = 16V, f = 1MHz 20 pF COUT Turn-On Delay, OUT0, 1 $\mathsf{R}_L$ = 500Ω, $\mathsf{V}_{CE}$ = 50% to $\mathsf{V}_{OUT}$ = 0.9 x $\mathsf{V}_{BATT},$ 5 us td(ON) $V_{IN0,1} = 50\%$ to $V_{OUT} = 0.9 \times V_{BATT}$ , $V_{BATT} = 16V$ $R_{I} = 500\Omega$ , $V_{CF} = 50\%$ to $V_{OUT} = 0.9 \times V_{BATT}$ , Turn-On Delay, OUT2 - 7 10 -\_ μs td(ON) $V_{BATT} = 16V$ Turn-Off Delay $R_L = 500\Omega$ , $V_{\overline{CE}} = 50\%$ to $V_{OUT} = 0.1 \times V_{BATT}$ , \_ 10 μs td(OFF) $V_{IN0,1} = 50\%$ to $V_{OUT} = 0.9 \times V_{BATT}$ , $V_{BATT} = 16V$ dV<sub>ON1</sub> Turn-On Voltage Slew-Rate, OUT2 - 7 For $V_{OUT}$ = 90% to 30% of $V_{BATT}$ : $V_{BATT}$ = 16V, -0.7 3.5 V/us $R_1 = 500\Omega$ dt $dV_{ON2}$ For $V_{OUT}$ = 90% to 30% of $V_{BATT}$ ; $V_{BATT}$ = 16V, Turn-On Voltage Slew-Rate, OUT0, 1 -2 10 V/µs $R_{I} = 500\Omega$ dt dV<sub>OFF1</sub> Turn-Off Voltage Slew-Rate, OUT0 - 7 For $V_{OUT} = 30\%$ to 90% of $V_{BATT}$ ; $V_{BATT} = 16V$ , 2 10 V/µs $R_L = 500\Omega$ dt dV<sub>OFF2</sub> Turn-Off Voltage Slew-Rate, OUT0 - 7 For $V_{OUT}$ = 30% to 80% of $V_{OC}$ : 2 15 V/µs \_ dt $V_{BATT} = 0.9 \times V_{OC}, R_L = 500\Omega$ FAULT PARAMETERS Reverse Current Drive, OUT0 - 7 -500 mΑ IRD V Reverse Voltage Drop, OUT0 - 7 VRD IOUT = -3A, t ≤2ms -1.5 --ΔI<sub>CC</sub> during Reverse Current Drive ∆lcc I<sub>OUT</sub> = -3A, t ≤2ms 100 mΑ -

## HIP0045

## **Electrical Specifications** $V_{CC} = 4.5V$ to 5.5V, $T_A = -40^{\circ}C$ to 125°C, Unless Otherwise Specified (Continued)

| PARAMETER                                                                       | SYMBOL TEST CONDITIONS   |                                                                                            | MIN                       | TYP | MAX                     | UNITS |

|---------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------|---------------------------|-----|-------------------------|-------|

| Open Load Threshold Voltage                                                     | V <sub>REF</sub>         | Open Load Fault Condition, Fault Detected If $V_{OUT} < V_{REF}$                           | 0.32 x<br>V <sub>CC</sub> | -   | 0.4x<br>V <sub>CC</sub> | V     |

| Open Load Pull-Down Current                                                     | I <sub>SK</sub>          | No Load, V <sub>OUT</sub> = V <sub>BATT</sub> = 16V                                        | 20                        | -   | 100                     | μA    |

| Over-Current Shutdown Threshold, OUT0 - 5                                       | I <sub>SC</sub>          | $V_{CC} = 5V$                                                                              | 1.05                      | 1.4 | 2                       | А     |

| Short Circuit Current Limit, OUT6, 7                                            | I <sub>LIM</sub>         | $V_{CC} = 5V$                                                                              | 1.05                      | 1.4 | 1.75                    | А     |

| Short Circuit Shutdown Delay, OUT0 - 5                                          | t <sub>SC</sub>          |                                                                                            | 0.2                       | -   | 12                      | μs    |

| Disable Fault Detection Time, Channel INO,<br>IN1 After Input Switch Transition | t <sub>DF</sub>          |                                                                                            | 15                        | -   | 50                      | μs    |

| Over-Temperature Detection Threshold                                            | T <sub>OFF</sub>         |                                                                                            | 155                       | 165 | 175                     | °C    |

| LOGIC INPUTS (IN0, IN1, MOSI, SCK, RE                                           | SET, CE)                 |                                                                                            |                           |     |                         |       |

| Threshold Voltage at Falling Edge                                               | V <sub>T</sub> -         |                                                                                            | 0.2xV <sub>CC</sub>       | -   | -                       | V     |

| Threshold Voltage at Rising Edge                                                | V <sub>T</sub> +         |                                                                                            | -                         | -   | 0.7xV <sub>CC</sub>     | V     |

| Hysteresis Voltage                                                              | V <sub>H</sub>           | V <sub>T</sub> + - V <sub>T</sub> -                                                        | 0.65                      | -   | -                       | V     |

| Input Current                                                                   | I <sub>IN</sub>          | V <sub>IN</sub> = V <sub>CC</sub>                                                          | -                         | -   | +10                     | μA    |

| Input Pull-Up Resistance                                                        | R <sub>IN</sub>          |                                                                                            | 50                        | 80  | 200                     | kΩ    |

| Input Capacitance                                                               | C <sub>IN</sub>          |                                                                                            | -                         | -   | 10                      | pF    |

| Input Frequency, IN0, IN15                                                      | f <sub>IN</sub>          |                                                                                            | DC                        | -   | 2                       | kHz   |

| Active Supply Range for Reset State<br>Change at RESET Pin                      | V <sub>HCC_RS</sub><br>T | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                     | 3.1                       | -   | 5.5                     | V     |

| Low V <sub>CC</sub> Active Reset Threshold                                      | V <sub>LCC_RST</sub>     | Low $V_{CC}$ Forced Reset, (Low Voltage Reset<br>Active for 0 < $V_{CC}$ < $V_{LCC_RST}$ ) | 3.1                       | -   | 4                       | V     |

| LOGIC OUTPUT (MISO)                                                             | 1                        | L                                                                                          |                           |     |                         |       |

| Data Output LOW Voltage                                                         | V <sub>SOL</sub>         | I <sub>SO</sub> = -3.2mA                                                                   | -                         | 0.2 | 0.4                     | V     |

| Data Output HIGH Voltage                                                        | V <sub>SOH</sub>         | I <sub>SO</sub> = -4mA                                                                     | V <sub>CC</sub> -<br>0.4V | -   | -                       | V     |

| Output Three-State Leakage Current                                              | I <sub>SOL</sub>         | $\overline{CE}$ = High, $0V \le V_{SO} \le V_{CC}$                                         | -10                       | -   | +10                     | μΑ    |

| Output Capacitance                                                              | C <sub>SO</sub>          | f <sub>OPER</sub> = 3MHz                                                                   | -                         | -   | 10                      | pF    |

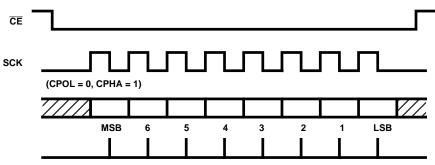

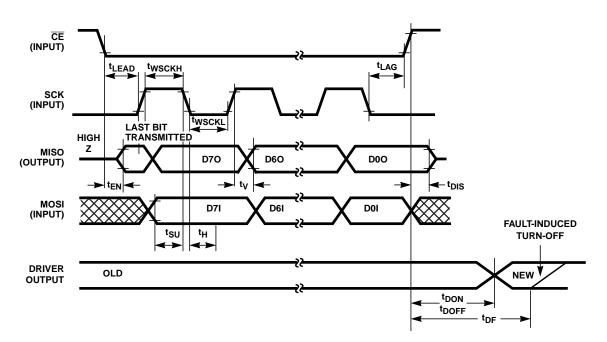

## Serial Peripheral Interface Timing (MOSI, MISO Load Capacitor = 100pF, See Figure 1)

| PARAMETER                                                             | SYMBOL             | TEST CONDITION | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------------|--------------------|----------------|-----|-----|-----|-------|

| Clock Frequency, 50% Duty Cycle                                       | f <sub>CLK</sub>   |                | 3   | -   | -   | MHz   |

| Enable Lead Time (SCK Change Low to High after $\overline{CE}$ = Low) | <sup>t</sup> LEAD  |                | 100 | -   | -   | ns    |

| Enable Lag Time (Time for SCK Low before $\overline{CE}$ goes High)   | <sup>t</sup> LAG   |                | 150 | -   | -   | ns    |

| Minimum Time SCK = High                                               | twsckh             |                | 160 | -   | -   | ns    |

| Minimum Time SCK = Low                                                | <sup>t</sup> WSCKL |                | 160 | -   | -   | ns    |

| Data Setup Time (SCK Change from High to Low after MOSI Data Valid)   | ts∪                |                | 20  | -   | -   | ns    |

| Data Hold Time (MOSI Data Hold Time SCK<br>Change from High to Low)   | tH                 |                |     | -   | 20  | ns    |

| Enable Time from $\overline{CE}$ = Low to Data at MISO                | t <sub>EN</sub>    |                | -   | -   | 100 | ns    |

| Disable Time<br>(Time for CE Low to High to Output Data Float)        | <sup>t</sup> DIS   |                | -   | -   | 100 | ns    |

## HIP0045

#### **Serial Peripheral Interface Timing** (MOSI, MISO Load Capacitor = 100pF, See Figure 1)

| PARAMETER                                                                                              | SYMBOL                | TEST CONDITION             | MIN | TYP    | MAX | UNITS |

|--------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|-----|--------|-----|-------|

| Data Valid Time, SCK to Data at MISO Valid                                                             | t <sub>V</sub>        | V <sub>CC</sub> = 5V ±0.1V | -   | -      | 100 | ns    |

| Time for SCK Low before $\overline{CE}$ Low (SCK Setup Time before $\overline{CE}$ High to Low Change) | <sup>t</sup> SCK_LEAD |                            | 100 | -      | -   | ns    |

| Time for SCK High after CE High                                                                        | <sup>t</sup> SCK_LAG  |                            | 150 | -      | -   | ns    |

| CE Pulse Filter Time                                                                                   |                       |                            | -   | Note 9 | -   | ns    |

NOTES:

7. The MOSFET Output Drain is internally clamped with a Drain-to-Gate zener diode that turns-on the MOSFET; holding the Drain at the Output Clamp Voltage, V<sub>OC</sub>.

8. The measurement of Output Leakage Current includes the Output Pull-Down Current, I<sub>SK</sub>. Each Output has a Current Pull-Down which is used to detect open load fault conditions.

9. The digital filter time for the output latch function determines if the output latch function will be enabled. The output latch function will only be enabled if a positive  $\overline{CE}$  slope occurs after 8 SCK clock cycles or a multiple of 8 SCK cycles since the last  $\overline{CE}$  negative slope change.

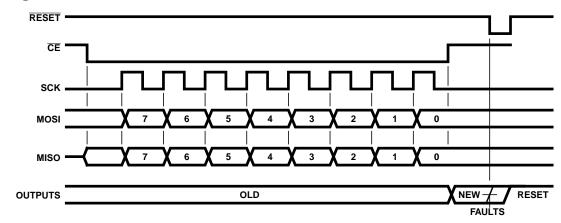

## **Timing Diagrams**

INTERNAL STROBE FOR DATA CAPTURE

FIGURE 1A. DATA AND CLOCK TIMING DIAGRAM

#### FIGURE 1B. SPI TIMING DIAGRAM

Timing Diagrams (Continued)

FIGURE 2. BYTE TIMING DIAGRAM WITH ASYNCHRONOUS RESET

## Signal Pin Descriptions

**Power Output Drivers, OUT0 - OUT7 -** The input and output bits corresponding to Output 0 thru Output 7 are transmitted and received most significant bit (MSB) first via the SPI bus. Outputs OUT0 - 5 are provided with overcurrent shutdown. Current Limiting and Thermal Shutdown are provided on OUT6, 7 for application use as Lamp Drivers. After a fault shutdown, the control lines remain active. The fault latches must be cleared by turning the output off and on to reset the output to an ON state. OUT1, 2 latches may be cleared by the RESET pin.

**RESET** - Active low reset input. An internal pull-up is provided on-chip. When this input line is low, all output drivers are turned-off and the OUT1, 2 fault latches are cleared. An internal low voltage reset is ORed with the **RESET** input. When  $V_{CC}$  is less than  $V_{LCC\_RST}$ , the internal reset is active.

**CE** - Active low chip enable. The falling edge of CE loads the shift register with the output status bits. Data is transferred from the shift register to the outputs on the rising edge of CE. The output driver for the MISO pin is enabled when CE goes low. CE must be a logic low prior to the first serial clock (SCK) and must remain low until after the last (eighth) serial clock cycle. All eight MOSI bits of input data must be loaded in the same sequence of SCK clock input. A digital filter is used in the  $\overline{CE}$  line to insure that 8 (or a multiple of 8) clock cycles occurs while CE is active low. After SCK is low for a short period, t<sub>I AG</sub>; CE may be changed from low to high to latch the input data. A low level on CE also activates an internal disable circuit used for unlatching output states that are in a fault mode as sensed by an out of saturation condition. A high on CE forces MISO to a high impedance state. Also, when CE is high, the octal driver ignores the SCK and MOSI signals.

**IN0, 1 - I**N0 and IN1 are Channels 0 and 1 direct parallel input controls. Refer to 'Special Input Conditions for Channel 0, 1' in the following text.

**SCK, MISO, MOSI -** Refer to the 'Serial Peripheral Interface' (SPI) section in the following text.

#### Serial Peripheral Interface (SPI)

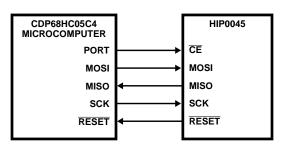

The Serial Peripheral Interface (SPI) is a serial synchronous bus for control and data transfers. The Clock (SCK), which is generated by the microcomputer, is active only during data transfers. In systems using CDP68HC05 family microcomputers, the inactive clock polarity is determined by the CPOL bit in the microcomputer's control register. The CPOL bit is used in conjunction with the clock phase bit, CPHA to produce the desired clock data relationship between the microcomputer and octal driver. The CPHA bit in general selects the clock edge which captures data and allows it to change states. For the HIP0045, the CPOL bit must be set to a logic zero and the CPHA bit to a logic one. Configured in this manner, MISO (output) data will appear with every rising edge of the SCK clock pulse, and MOSI (input) data will be latched into the shift register with every falling edge of the SCK clock pulse. Also, the steady state value of the inactive serial clock, SCK, will be at a low level. Timing diagrams for the serial peripheral interface are shown in Figure 1.

#### SPI Signal Descriptions

**MOSI (Master Out/Slave In) -** Serial data input. Data bytes are shifted in at this pin, most significant bit (MSB) first. The data is passed directly to the shift register which in turn controls the latches and output drivers.

**MISO (Master In/Slave Out) -** Serial data output. Data bytes are shifted out at this pin, most significant bit (MSB) first. This pin is the serial output from the shift register and is three stated when  $\overline{CE}$  is high. Diagnostic Failure Register information is given in Tables 6 and 7. Determination of the fault condition may be done as a software sequence, based on MOSI data latched into the shift register and subsequent data clocked out of the MISO pin.

**SCK** - Serial clock input. The SCK signal clocks the shift register and new MOSI (input) data will be latched into the shift register on every falling edge of SCK. The SCK phase bit, CPHA=1 and the polarity bit, CPOL=0, must be set in the microcomputer's control register.

## Functional Descriptions

The HIP0045 is a low quiescent power, high voltage, high current, octal, serial low side driver featuring eight channels of open drain MOS output drivers. Referring to the Detailed Block Diagram, the drivers have low r<sub>DSON</sub> and low saturation voltage with over-voltage drain-to-gate zener clamp circuits. Each output is short circuit protected and suited for driving resistive or inductive loads such as solenoids, relays and lamps. Data is transmitted to the device serially using the Serial Peripheral Interface (SPI) protocol. Each channel is independently controlled by an output latch and a common RESET line that disables all eight outputs. Byte timing with asynchronous reset is shown in Figure 2.

FIGURE 3. TYPICAL MICROCOMPUTER INTERFACE WITH THE HIP0045

The circuit receives 8-bit serial data by means of the serial input (MOSI), and stores this data in an internal register to control the output drivers. The serial output (MISO) provides 8-bit diagnostic data representing the voltage level at the driver output. This allows the microcomputer to diagnose the condition at the output drivers. The device is selected when the chip enable  $(\overline{CE})$  line is low. When  $(\overline{CE})$  is high, the device is deselected and the serial output (MISO) is placed in a threestate high impedance mode. The device shifts serial data on the rising edge of the serial clock (SCK), and latches data on the falling edge. On the rising edge of chip enable ( $\overline{CE}$ ), new input data from the shift register is latched to control the output drivers. The falling edge of chip enable ( $\overline{CE}$ ) transfers the output drivers fault information back to the shift register. The output drivers have low ON voltage at rated current, and are monitored by a comparator for an out of saturation condition, in which case the output driver with the fault becomes unlatched and diagnostic data is sent to the microcomputer via the MISO line. A typical microcomputer interface circuit is shown in Figure 3.

#### SPI Shift Register

The SPI shift register has both serial and parallel inputs and outputs. Serial output and input data are simultaneously transferred to and from the SPI bus. The serial input data is parallel latched into the 8-Bit Output Latch of the HIP0045 at the end of a data transfer. Diagnostic data, Diag0-7 is transferred to the shift register when  $\overline{CE}$  goes low at the beginning of a data transfer cycle.

#### 8-Bit Output Latch

The 8-Bit Output Latch is used to control the output drivers. New serial data is transferred from the shift register to the 8-Bit Output Latch when CE goes high. The 8-Bit Output Latch is cleared by an active low RESET signal.

#### **Output Drivers**

The output drivers provide an active low output of 500mA nominal with current limiting set to greater than 1.05A to allow for high inrush currents. In addition, each output is provided with a voltage drain-to-gate clamp circuit to limit inductive transients. Each output driver is also monitored by a comparator for an out of saturation condition. If the output voltage of an ON output pin exceeds the saturation voltage limit, a fault latch turns off the output. The threshold comparators are used to detect shorts to the power supply, shorts to ground and open loads. Each comparator provides status data to the shift register for diagnostic feedback. An internal pull-down current, ISK at each output will provide an indicator for low output voltage if the output is programmed OFF and the output line is open. Refer to Tables 6 and 7 for Fault information versus output control and V<sub>REF</sub>. Note that VRFF is the out-of-saturation threshold for an ON state. When the output is switched off and VREF is low, an openload or ground fault is indicated.

## CE High to Low Transition

When  $\overline{CE}$  is low the three-state MISO pin is enabled. On the falling edge of  $\overline{CE}$ , diagnostic and status data from the output voltage comparators will be latched into the shift register. During the time that  $\overline{CE}$  is low, data bytes controlling the output drivers are shifted in at the MOSI pin most significant bit (MSB) first. Tables 1, 2 and 3 define the logic state for control of each output and Table 4 defines the control bit structure.

## CE Low to High Transition

When the last serial data bit has been shifted into the MOSI pin,  $\overline{CE}$  pin is pulled high to transfer data from the shift register into the 8-bit parallel output latch to activate the outputs. The serial clock input pin (SCK) should be low during  $\overline{CE}$  transitions to avoid false clocking of the shift register. The SCK input is gated by  $\overline{CE}$  so that the SCK input is ignored when  $\overline{CE}$  is high.

#### **Detecting Fault Conditions**

Fault conditions may be checked as follows: SCK is always low when  $\overline{CE}$  is changing. When  $\overline{CE}$  goes low, the MISO output is taken out of the three-state mode and the Output status information is latched into the shift register. While  $\overline{CE}$  is low, data bits in the shift register are transferred to the MISO output on each positive SCK clock transition and data bits present at the MOSI input are transferred into the shift register on each negative transition of SCK. To verify Status and Diagnostic conditions, clock in a new control byte and wait approximately 150µs to allow the outputs to settle. Clock in the same control byte and compare this to the data output at the MISO pin. If there is a disparity, use Tables 5, 6 and 7 to determine the fault or status condition. (Use Tables 1, 2, 3 and 4 to establish the ON/OFF conditions for each output).

Based on the needs of the application, a software sequence should be programmed into the microcontroller to set the corrective action of each fault condition.

#### TABLE 5. DIAGNOSTIC FAILURE REGISTER STRUCTURE

| (D70) (D60) (D50) (D40) (D30) (D20) (D10) (D00) | Diag1<br>(D7O) |  |  |  |  |  |  |  |

|-------------------------------------------------|----------------|--|--|--|--|--|--|--|

|-------------------------------------------------|----------------|--|--|--|--|--|--|--|

NOTE:

The Diagnostic Failure Register bits Diag0 -7 have the same order as the Control Register bits Q0 - 7 as defined in Table 4. Data bits D00 - D7O give the MISO SPI serial output flow sequence.

# TABLE 6. DEFINITION OF Diag0, 1 FAULT BITS FOR OUT0,1 IN PARALLEL-CONTROLLED MODE

| OUTPUT<br>STATE | V <sub>REF</sub><br>STATUS | FAULT<br>BIT | FAULT<br>MODE              |

|-----------------|----------------------------|--------------|----------------------------|

| OFF             | >V <sub>REF</sub>          | Н            | No Fault                   |

| OFF             | <v<sub>REF</v<sub>         | L            | Open Load or GND Short     |

| ON              | <v<sub>REF</v<sub>         | Н            | No Fault                   |

| ON              | >V <sub>REF</sub>          | L            | Short to V <sub>BATT</sub> |

#### TABLE 7. DEFINITION OF Diag0-7 STATUS BITS FOR OUT0-7

| OUTPUT<br>STATE | V <sub>REF</sub><br>STATUS | STATUS<br>BIT | FAULT<br>MODE                                                                        |

|-----------------|----------------------------|---------------|--------------------------------------------------------------------------------------|

| OFF             | >V <sub>REF</sub>          | Н             | No Fault                                                                             |

| OFF             | <v<sub>REF</v<sub>         | L             | Open Load or GND Short                                                               |

| ON              | <v<sub>REF</v<sub>         | L             | No Fault                                                                             |

| ON              | >V <sub>REF</sub>          | Н             | Short to V <sub>BATT</sub> (Chan. 0-7);<br>or Over-Temperature Fault<br>(Chan. 6, 7) |

#### NOTES:

- 11. For Channel 0 (Diag0) and Channel 1 (Diag1): Fault Bit High = No Fault; Fault Bit Low = Fault Occurred.

- 12.  $V_{REF}$  is the threshold reference level for detecting an Open Load. Refer to the Electrical Specification for the  $V_{REF}$  voltage level.

#### Special Conditions for Channel 0, 1

Referring to the Detailed Block Diagram, Channel's 0, 1 are configured to externally provide control of the ON/OFF state. The inputs, IN0 and IN1, are ORed with the SPI ON/OFF control bit. In this configuration with IN0 and IN1 high, SPI control latches Diag0 and Diag1 as status bits. When the IN0 and IN1 inputs are active, a fault condition is detected by a comparison of IN0 and IN1 to OUT0 and OUT1 respectively causing the Fault Detector to latch a fault bit. The resulting Fault output is latched as diagnostic bit, Diag0 or Diag1. The Diag0 and Diag1 outputs give the status or fault condition of the output drivers as shown in Table 6. Fault detection is disabled during switching/settling time.

The Diag0 and Diag1 bits from Channel 0 and 1 respectively indicate a fault when the FAULT BIT is Low, given IN1 and IN0 control. Otherwise Diag0 and Diag1 are status bits when controlled by the SPI input. Note that the SPI Bit, given in Tables 1 and 2 overrides the ON state control from IN0 and IN1.

#### FIGURE 4. MAXIMUM SINGLE PULSE ENERGY SAFE OPERATING AREA FOR EACH CLAMPED OUTPUT DRIVER, $T_A = 25^{\circ}C$

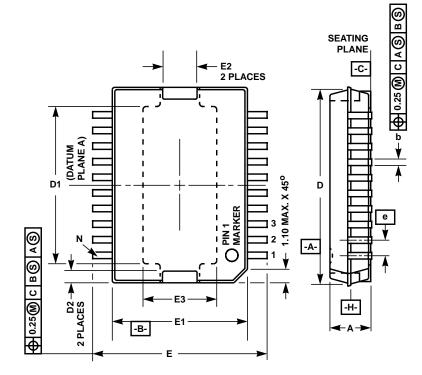

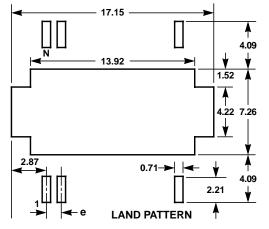

## Power Small Outline Plastic Package (PSOP)

#### 20 LEAD POWER SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES    |       | MILLIMETERS |       |       |

|--------|-----------|-------|-------------|-------|-------|

| SYMBOL | MIN       | MAX   | MIN         | MAX   | NOTES |

| A      | 0.122     | 0.142 | 3.10        | 3.60  | -     |

| A1     | 0.004     | 0.012 | 0.10        | 0.30  | -     |

| A2     | 0.118     | 0.130 | 3.00        | 3.30  | -     |

| A3     | 0.000     | 0.004 | 0.00        | 0.10  | -     |

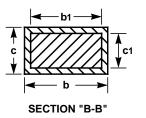

| b      | 0.016     | 0.021 | 0.40        | 0.53  | 6, 7  |

| b1     | 0.016     | 0.020 | 0.40        | 0.50  | 6, 7  |

| С      | 0.009     | 0.013 | 0.23        | 0.32  | 7     |

| c1     | 0.009     | 0.011 | 0.23        | 0.29  | 7     |

| D      | 0.622     | 0.630 | 15.80       | 16.00 | 3     |

| D1     | 0.496     | 0.512 | 12.60       | 13.00 | -     |

| D2     | -         | 0.043 | -           | 1.10  | -     |

| E      | 0.547     | 0.571 | 13.90       | 14.50 | -     |

| E1     | 0.429     | 0.437 | 10.90       | 11.10 | 4     |

| E2     | -         | 0.114 | -           | 2.90  | -     |

| E3     | 0.228     | 0.244 | 5.80        | 6.20  | -     |

| е      | 0.050     | BSC   | 1.27        | BSC   | -     |

| L      | 0.031     | 0.043 | 0.80        | 1.10  | 5     |

| L1     | 0.014 BSC |       | 0.35 BSC    |       | -     |

| Ν      | 2         | 0     | 2           | 20    | -     |

#### NOTES:

1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

Rev. 0 3/96

- "C" is a reference datum. Seating plane is defined by 2. lead tips only.

- 3. Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 per side. D measured at -H-.

- 4. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.15 per side. E1 measured at -H-.5. Dimension "L" is the length of terminal for soldering to

- a substrate.

- 6. The lead width dimension does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm total in excess of the lead width dimension at maximum material condition.

- 7. Section "B-B" to be determined at 0.10mm to 0.25mm from the lead tip.

- 8. Controlling dimension: MILLIMETER.

- 9. Dimensions conform with JEDEC Outline MO-166AA Issue B.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## Sales Office Headquarters

NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240

#### EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029