捷多邦,专业PCB打样工厂,24小时加急出货

# HMS39C7092

## Embedded Flash MCU

**Specification Ver 1.0**

System IC SBU, SP BU

MCU Business Division,

Flash Team

Released : February. 2001

ARM<sup>®</sup> is trademark of Advanced RISC Machine Ltd. ARM7TDMI is designed by ARM Ltd.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by Hynix for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hynix or others.

These Hynix products are intended for usage in general electronic equipment (office equipment, communication equipment, measuring equipment, domestic electrification, etc.).

Please make sure that you consult with us before you use these Hynix products in equipment which require high quality and / or reliability, and in equipment which could have major impact to the welfare of human life (atomic energy control, airplane, spaceship, traffic signal, combustion control, all types of safety devices, etc.). Hynix cannot accept liability to any damage which may occur in case these Hynix products were used in the mentioned equipment without prior consultation with Hynix.

Copyright 2000 Hynix Semiconductor, Inc. All Rights Reserved

### Contents

| Chapter 1 |                                                        | .13 |

|-----------|--------------------------------------------------------|-----|

| Introduct | ion                                                    |     |

| 1.1       | General Description                                    | .14 |

| 1.2       | Feature                                                | .15 |

| 1.3       | Pin Descriptions                                       | .16 |

| 1.4       | Operation Mode description                             | .21 |

| 1.5       | Memory Map                                             | .25 |

| Chapter 2 | · ·                                                    |     |

|           | MI Core                                                |     |

| 2.1       | General Description                                    | .28 |

| 2.2       | Feature                                                |     |

| 2.3       | Core Block Diagram                                     |     |

| 2.4       | Instruction Set                                        |     |

|           | 2.4.1 ARM Instruction                                  |     |

|           | 2.4.2 THUMB Instruction                                |     |

|           | 2.4.3 The Program Status Registers                     |     |

|           | 2.4.3.1 The condition code flags                       |     |

|           | 2.4.3.2 The control bits.                              |     |

|           | 2.4.4 ARM pseudo-instructions                          |     |

|           | 2.4.5 THUMB pseudo-instructions                        |     |

| Chapter 3 |                                                        |     |

|           | itroller                                               |     |

| 3.1       | Overview                                               |     |

| 3.1       | 3.1.1 Features                                         |     |

|           |                                                        |     |

| 2.2       | 3.1.2 Pin Configuration                                |     |

| 3.2       | Bus Controller Registers                               |     |

|           | 3.2.1 Configuration Registers                          |     |

| 3.3       | Operation                                              |     |

|           | 3.3.1 Area Division                                    |     |

|           | 3.3.2 Area Division                                    |     |

|           | 3.3.3 Chip Select Signals                              |     |

| 3.4       | Basic Bus Interface                                    |     |

|           | 3.4.1 Overview                                         |     |

|           | 3.4.2 Byte Lane Write Control                          |     |

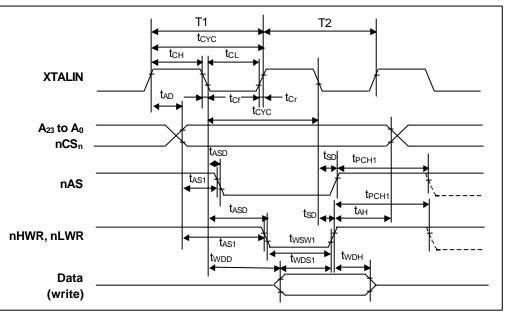

|           | 3.4.3 Basic Bus Control Signal Timing                  |     |

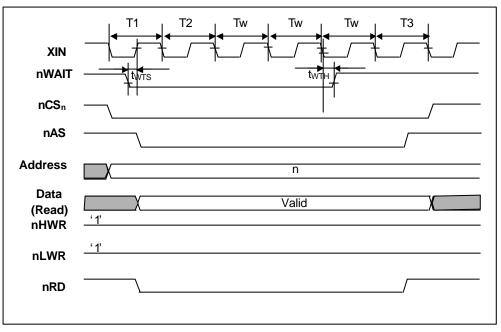

|           | 3.4.4 Wait Control                                     | .62 |

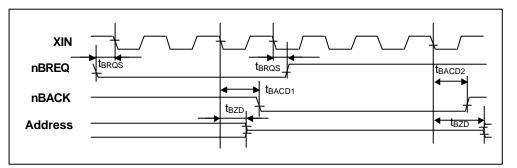

|           | 3.4.5 Bus Arbiter                                      |     |

| Chapter 4 |                                                        | .65 |

| MCU Co    | ntroller                                               | .65 |

| 4.1       | General Description                                    | .66 |

| 4.2       | Pin Function Description                               | .66 |

| 4.3       | Register Description                                   | .67 |

|           | 4.3.1 Register Memory Map                              |     |

|           | 4.3.2 PINMUX Register                                  |     |

|           | 4.3.3 MCU Device Code Register (0x0900_002C Read Only) |     |

| Chapter 5 |                                                                                                  | 73  |

|-----------|--------------------------------------------------------------------------------------------------|-----|

|           | anagement Unit                                                                                   |     |

| 5.1       | General Description                                                                              |     |

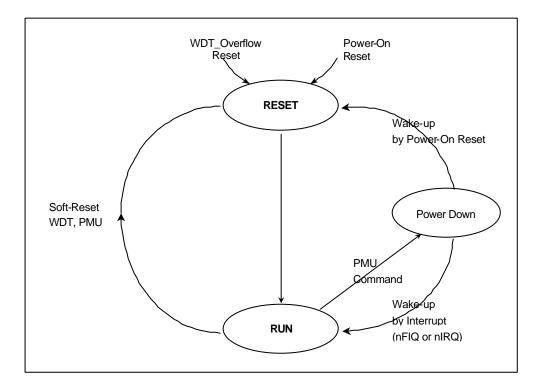

| 5.2       | Operation Modes                                                                                  |     |

| 0.2       | 5.2.1 Introduction                                                                               |     |

|           | 5.2.2 Reset and Operation Modes                                                                  |     |

| 5.3       | Power Management Unit Register Map                                                               |     |

| 5.4       | Register Description                                                                             |     |

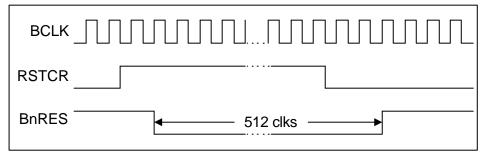

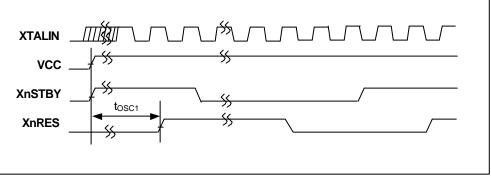

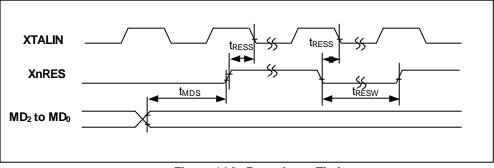

| 5.5       | Signal Timing Diagram                                                                            |     |

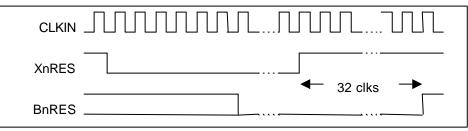

| 0.0       | 5.5.1 Power on Reset                                                                             |     |

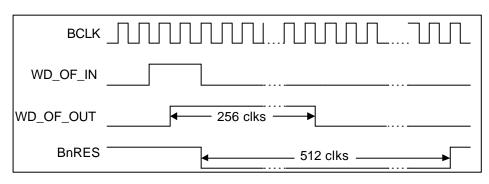

|           | 5.5.2 Watch Dog Timer Overflow                                                                   |     |

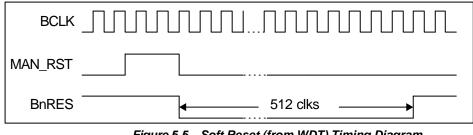

|           | 5.5.3 Soft-Reset                                                                                 |     |

| Chapter 6 |                                                                                                  |     |

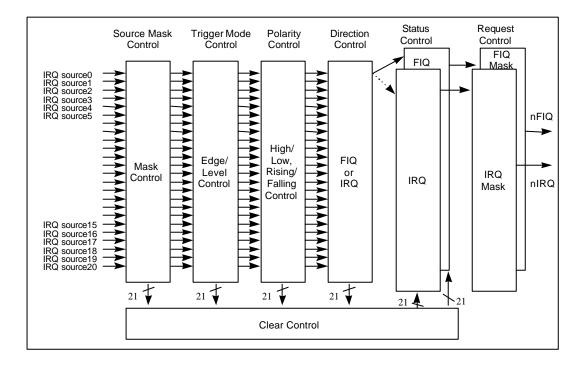

| •         | rupt Controller                                                                                  |     |

| 6.1       | About the Interrupt controller                                                                   |     |

| 0.1       | 6.1.1 Interrupt sources                                                                          |     |

|           | 6.1.2 Interrupt Control                                                                          |     |

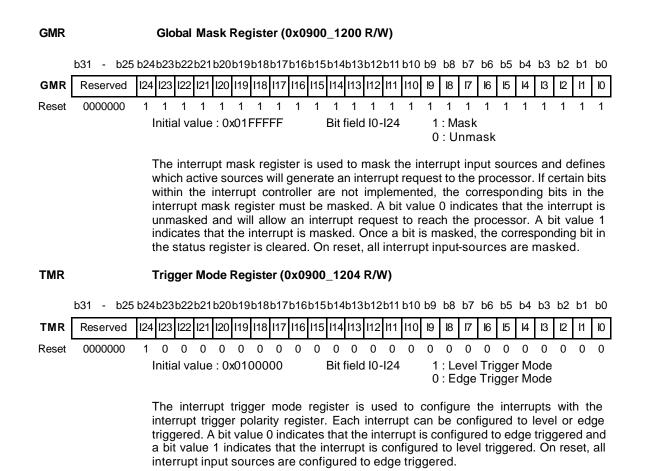

| 6.2       | Interrupt Controller Registers                                                                   |     |

|           |                                                                                                  |     |

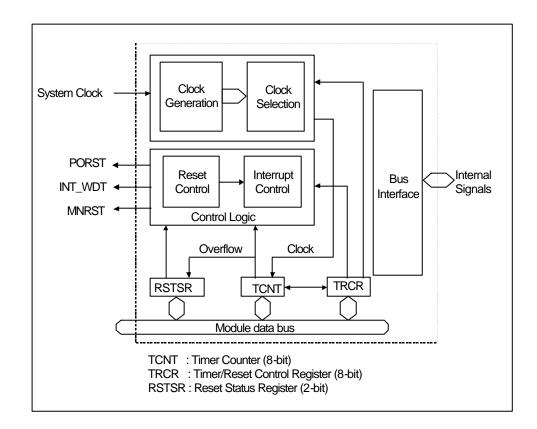

| •         | g Timer                                                                                          |     |

| 7.1       | General Description                                                                              |     |

| 7.1       |                                                                                                  |     |

| 7.2       | Watchdog Timer Operation                                                                         |     |

| 1.5       | 7.3.1 Timing of Setting and Clearing the Overflow Flag                                           |     |

| 7.4       | Watchdog Timer Memory Map                                                                        |     |

| 7.4       | Watchdog Timer Register Descriptions                                                             |     |

| 7.6       | Examples of Register Setting                                                                     |     |

| 7.0       | 7.6.1 Interval Timer Mode                                                                        |     |

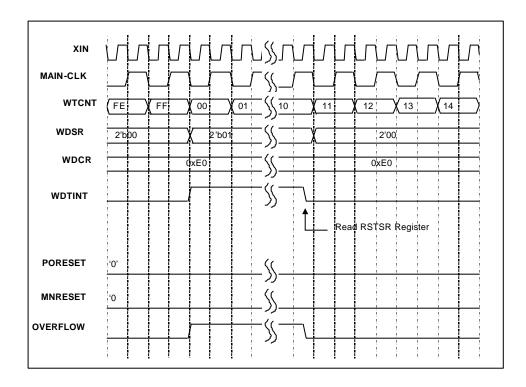

|           | 7.6.2 Watchdog Timer Mode with Internal Reset Disable                                            |     |

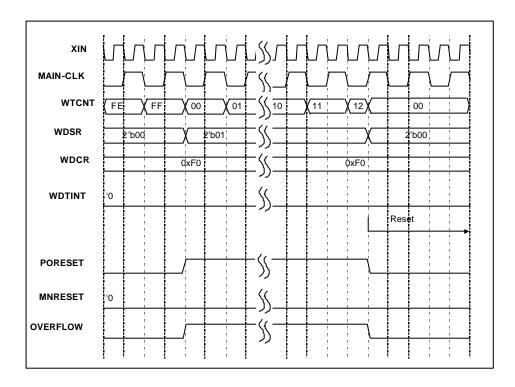

|           | 7.6.3 Watchdog Timer Mode with Power-on Reset                                                    |     |

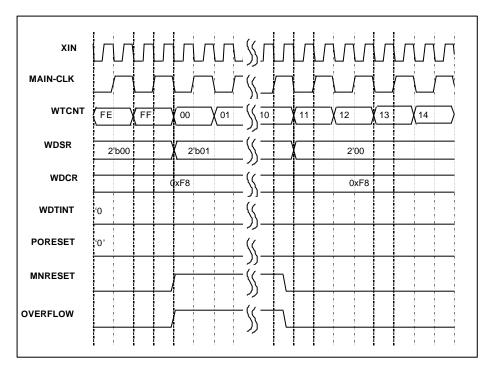

|           | 7.6.4 Watchdog Timer Mode with Manual Reset                                                      |     |

| Chapter 9 | · · · · · · · · · · · · · · · · · · ·                                                            |     |

|           | eral Purpose Timer                                                                               |     |

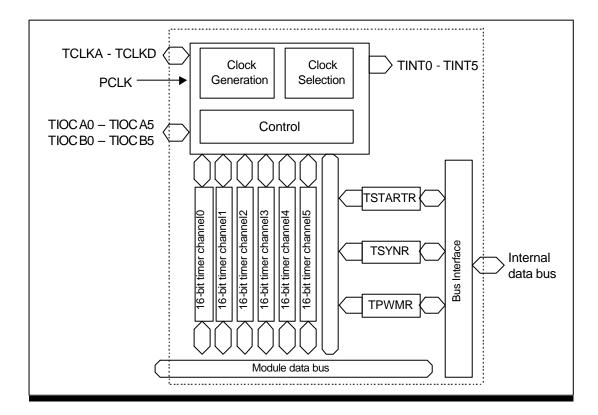

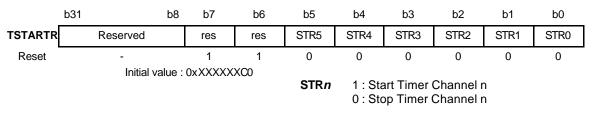

| 8.1       | About the General Purpose Timer Unit                                                             |     |

| 0.1       | 8.1.1 General Purpose Timer Unit Introduction                                                    |     |

| 8.2       | General Purpose Timer Unit Memory Map                                                            |     |

| 0.2       | 8.2.1 Register Assignment                                                                        |     |

|           | • •                                                                                              |     |

|           | 8.2.2 General Purpose Timer Unit Register Descriptions<br>8.2.2.1 Timer Global Control Registers |     |

|           |                                                                                                  |     |

| 0.0       | 8.2.2.2 Timer Channel Control Registers                                                          |     |

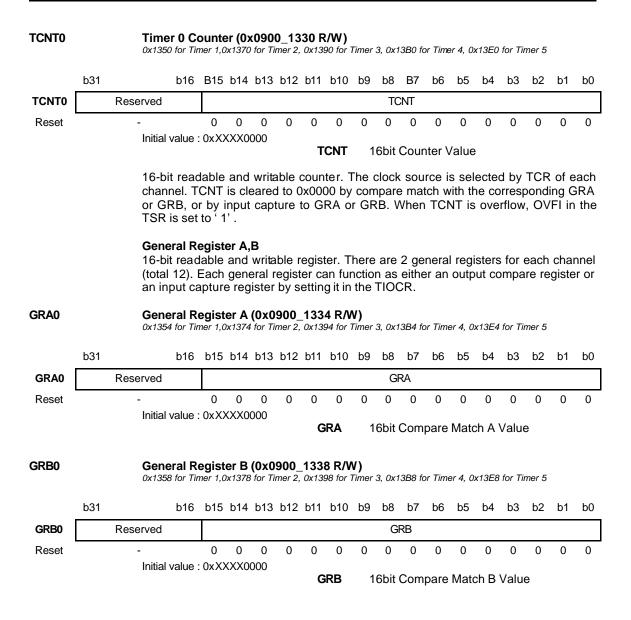

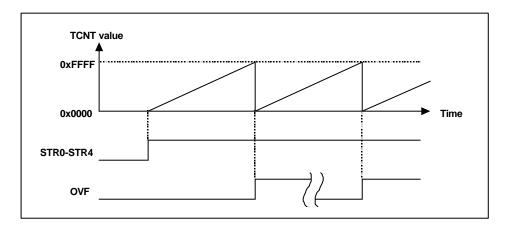

| 8.3       | General Purpose Timer Unit Operation                                                             |     |

|           | 8.3.1 Free Running Mode                                                                          |     |

|           | 8.3.2 Compare Match Mode                                                                         |     |

|           | 8.3.3 Input Capture Mode                                                                         |     |

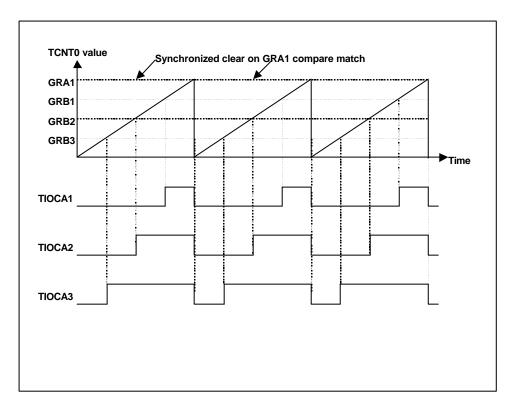

|           | 8.3.4 Synchronized Clear and Write Mode                                                          |     |

|           | 8.3.5 PWM Mode                                                                                   |     |

| Chapter 0 | 8.3.5.1 PWM Mode Operation                                                                       |     |

|           | laivered Asymphroneus Deseiver/Transmitter)                                                      |     |

| UART (L   | Iniversal Asynchronous Receiver/Transmitter)                                                     | 125 |

| ç          | 9.1 G       | eneral Description                       | 126 |

|------------|-------------|------------------------------------------|-----|

| ç          | 9.2 F       | eatures                                  | 127 |

| ç          | 9.3 S       | ignal Description                        | 127 |

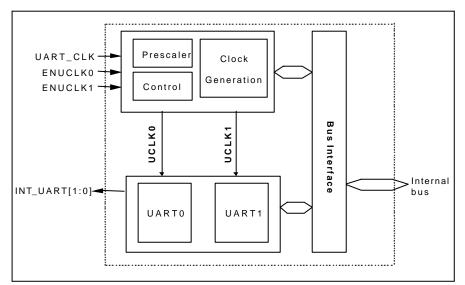

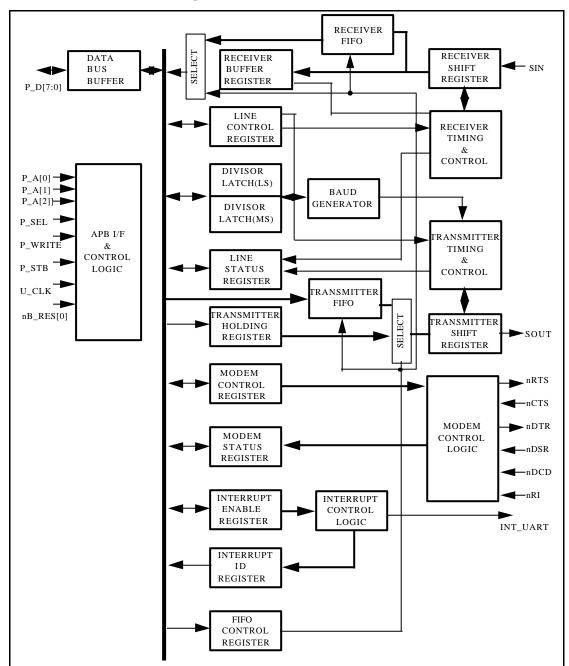

| ç          | 9.4 Ir      | iternal Block Diagram                    | 128 |

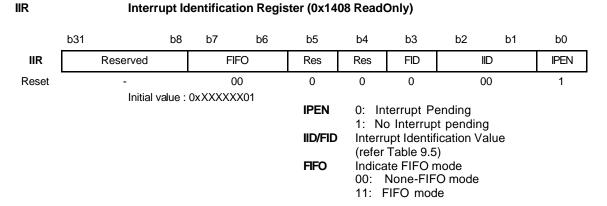

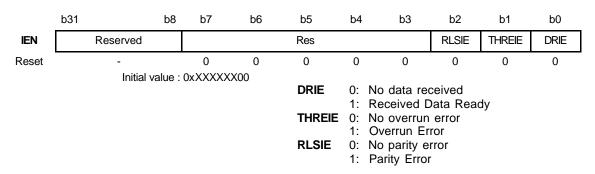

| ç          | 9.5 R       | egisters Description                     | 129 |

| ç          | 9.6 U       | ART Operations                           | 140 |

|            |             | FIFO Interrupt Mode Operation            |     |

|            | 9.6.2       | FIFO Polled Mode Operation               | 141 |

| ç          | 9.7 R       | egister Summary                          | 142 |

| Chapter 10 | )           |                                          | 143 |

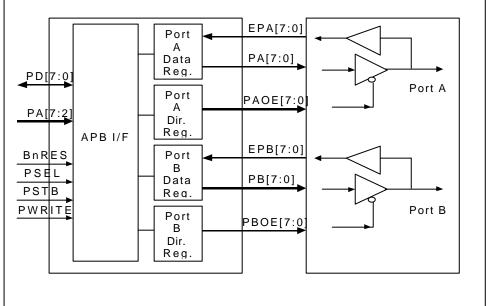

| GPIO       | (General    | Purpose Input Output)                    | 143 |

| 1          | 10.1 G      | eneral Description                       | 144 |

| 1          |             | PIO Registers                            |     |

|            | 10.2.1      | Register Memory Map                      | 145 |

|            |             | Register Description                     |     |

| 1          | 10.3 F      | unctional Description                    | 147 |

|            |             |                                          |     |

| On-Cl      |             |                                          |     |

| 1          |             | eneral Description                       |     |

|            | 11.2 F      | unction Description                      | 150 |

| Chapter 12 | 2           | ·                                        | 151 |

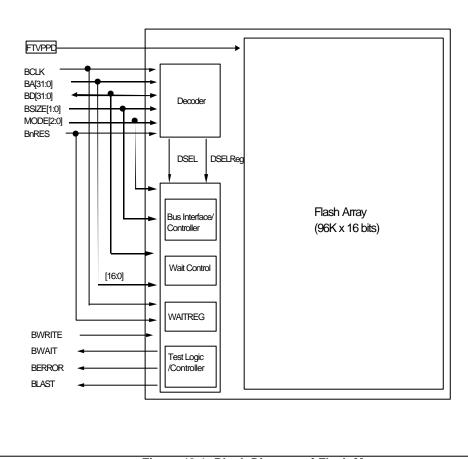

| On-ch      | nip Flash M | lemory                                   | 151 |

|            |             | eneral Description                       | 152 |

| 1          | 12.2 F      | eatures                                  | 152 |

| 1          | 12.3 B      | lock Diagram                             | 154 |

| 1          |             | lash Memory Register Description         |     |

| 1          | 12.5 O      | n-Board Programming Mode                 |     |

|            | 12.5.1      |                                          |     |

|            |             | User Program Mode                        |     |

| 1          |             | lash Memory Programming/Erasing          |     |

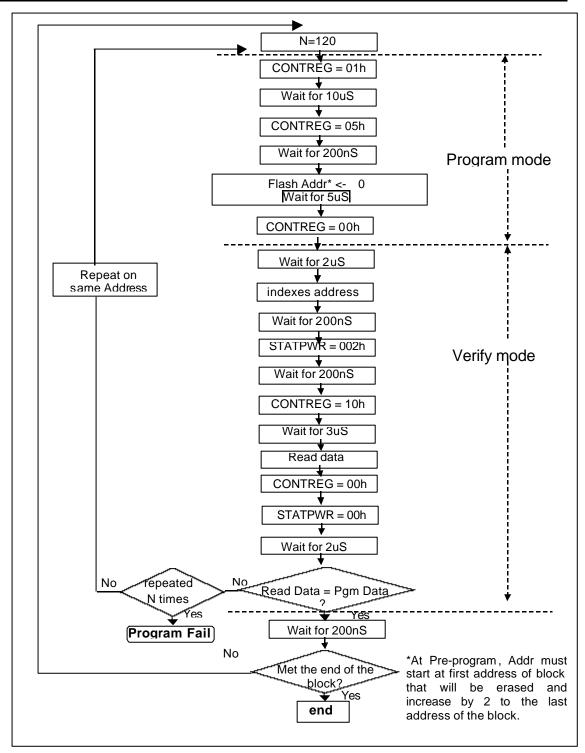

|            |             | Program & Program-Verify Mode            |     |

|            |             | Pre-program & Pre-program Verify Mode    |     |

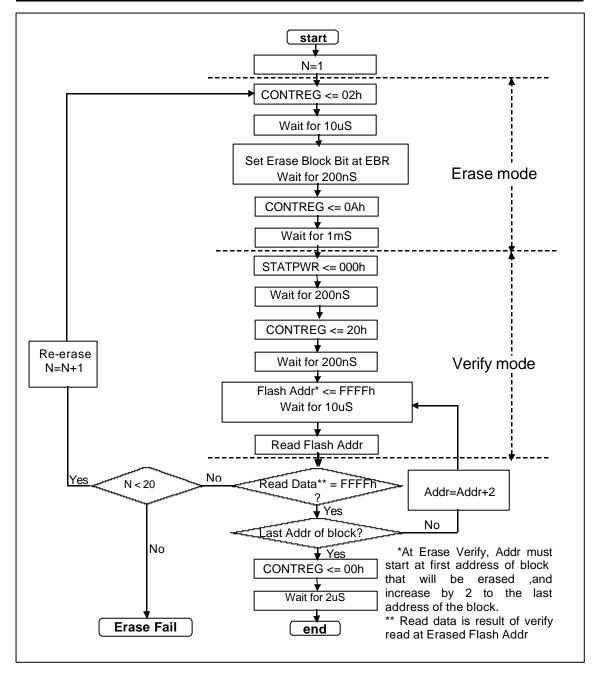

|            |             | Erase & Erase Verify Mode                |     |

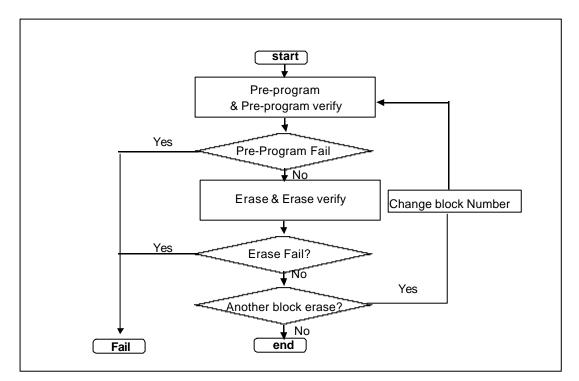

|            |             | Erase Algorithm                          |     |

| 1          | 12.7 F      | lash Memory PROM Mode                    |     |

|            | 12.7.1      |                                          |     |

|            | 12.7.2      | 2 - 1                                    |     |

|            |             | PROM Mode Operation                      |     |

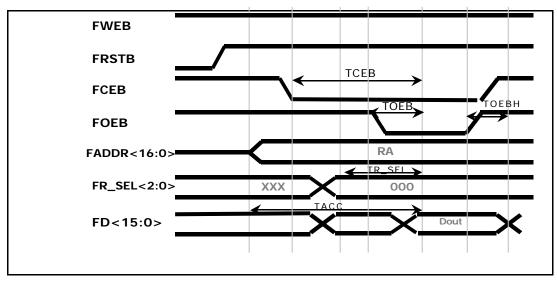

|            |             | Timing Diagram and AC/DC Characteristics |     |

|            |             |                                          |     |

|            |             |                                          |     |

| 1          |             | verview                                  |     |

|            |             | Features                                 |     |

|            |             | Pin Configuration                        |     |

| 1          |             | /D Converter Registers                   |     |

|            |             | Register Descriptions                    |     |

|            |             | peration                                 |     |

|            |             | terrupts                                 |     |

| 1          | 13.5 U      | sage Notes                               | 187 |

|           | 13.6      | Example                                     | 190 |

|-----------|-----------|---------------------------------------------|-----|

| Chapter 1 | 4         | ······                                      | 191 |

| Elect     | rical Cha | racteristics                                | 191 |

|           | 14.1      | Absolute Maximum Ratings                    | 192 |

|           | 14.2      | Recommended Operating Conditions:           | 192 |

|           | 14.3      | DC Characteristics                          | 193 |

|           | 14.4      | AC Characteristics                          | 194 |

|           | 14.4      | AD Conversion characteristics (Preliminary) | 196 |

|           | 14.5      | Operational Timing                          | 197 |

|           | 14.5      | .1 Clock Timing                             | 197 |

|           | 14.5      | .2 Reset Timing                             | 197 |

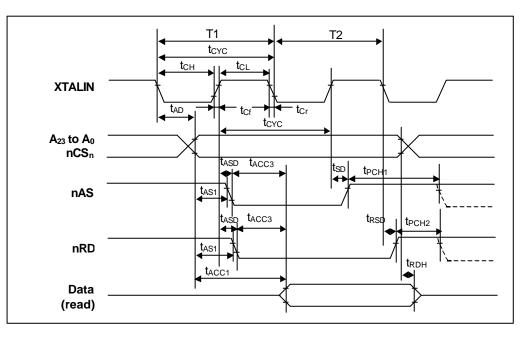

|           | 14.5      | .3 Bus Timing                               | 198 |

|           |           | -                                           |     |

### Appendix

- Peripheral Setting & Flash memory control Examples Package Dimension A-1

- A-2

## Figures

| Figure 1.1 | Package Outline                                                       | 14    |

|------------|-----------------------------------------------------------------------|-------|

| Figure 1.2 | HMS39C7092 Block Diagram                                              | 15    |

|            | HMS39C7092 Memory Map                                                 |       |

|            | Memory Map of Mode 3                                                  |       |

| Figure 1.5 |                                                                       |       |

|            | Memory Map of Mode 6 and Mode 7                                       | 26    |

|            | ARM7TDMI Core Block Diagram                                           |       |

|            | ARM instruction set formats.                                          |       |

|            | Register Organization in ARM state                                    |       |

| Figure 2.4 | THUMB instruction set formats                                         |       |

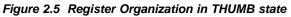

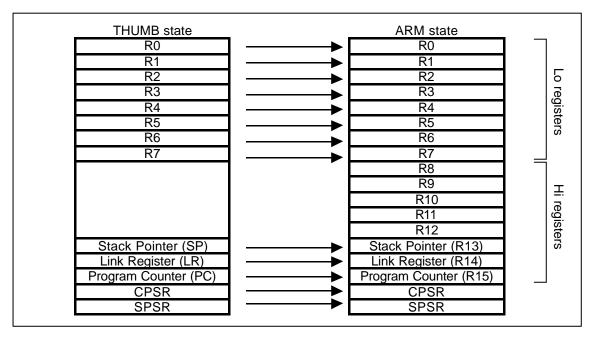

|            | Register Organization in THUMB state                                  | 35    |

| Figure 2.6 |                                                                       |       |

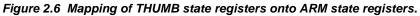

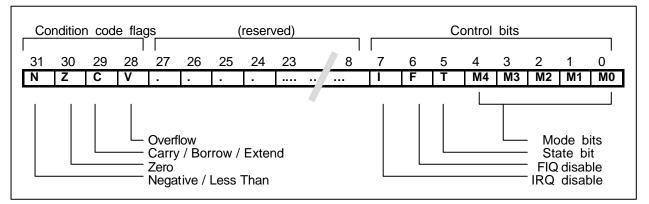

|            | Program status register format                                        |       |

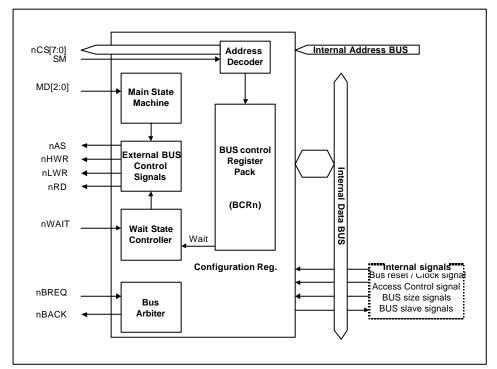

|            | Block Diagram of the Bus Controller                                   |       |

|            | Access Area Map for Each Operating Mode                               |       |

|            | Access Size and Data Alignment Control (8-Bit Access Area)            |       |

|            | Access Size and Data Alignment Control (16-Bit Access Area)           |       |

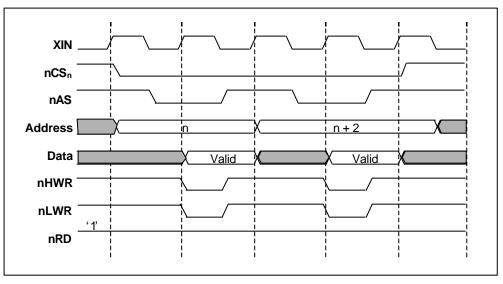

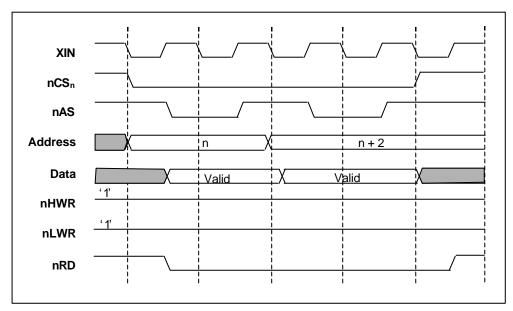

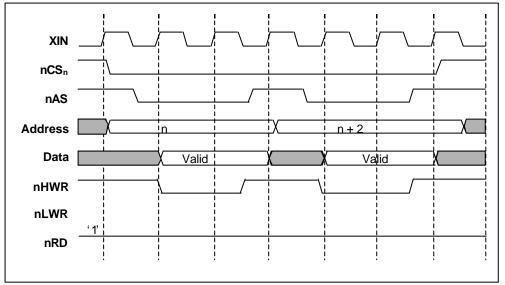

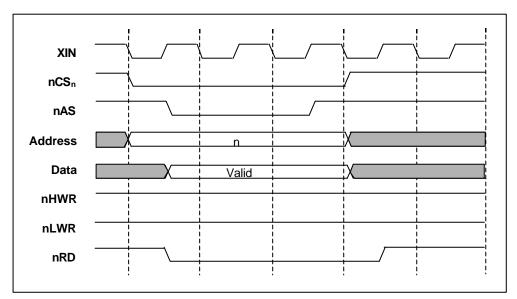

|            | Bus Control Signal Write Timing for 16-Bit, 1-Wait (Word Access)      |       |

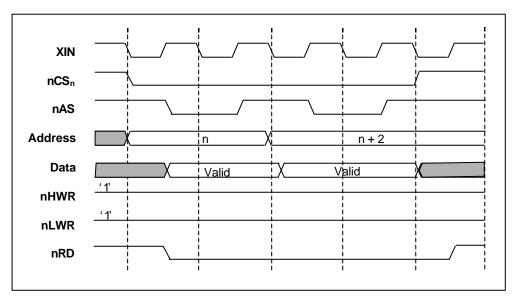

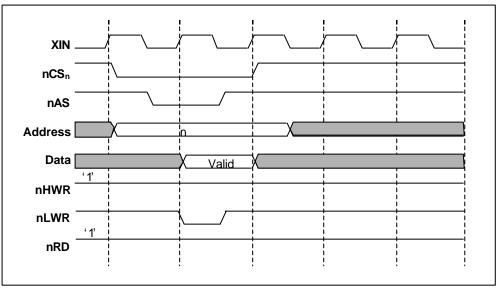

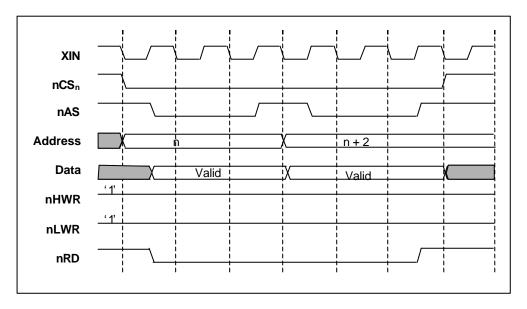

| 0          | Bus Control Signal Read Timing for 16-Bit, 1-Wait (Word Access)       |       |

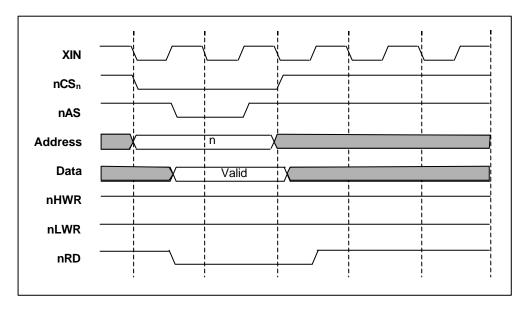

|            | Bus Control Signal Write Timing for 16-Bit, 1-Wait (Half-word Access) |       |

|            | Bus Control Signal Read Timing for 16-Bit, 1-Wait (Half-word Access)  |       |

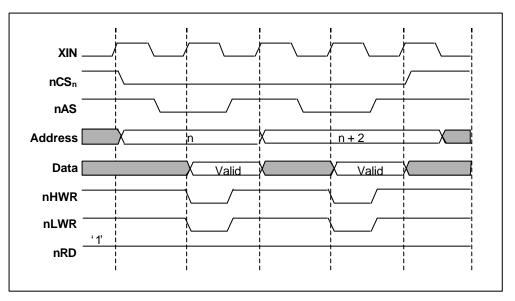

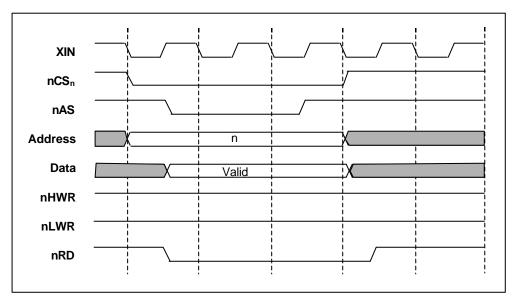

|            | Bus Control Signal Write Timing for 16-Bit, 1-Wait (Byte Access)      |       |

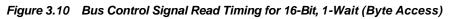

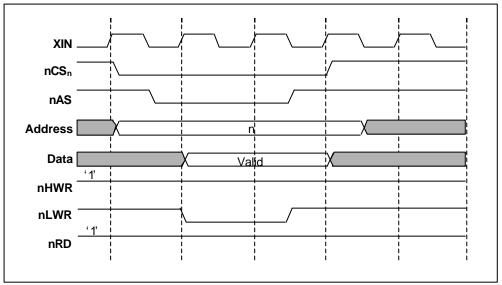

| •          | Bus Control Signal Read Timing for 16-Bit, 1-Wait (Byte Access)       |       |

|            | Bus Control Signal Write Timing for 16-Bit, 2-Wait (Word Access)      |       |

|            | Bus Control Signal Read Timing for 16-Bit, 2-Wait (Word Access)       |       |

|            | Bus Control Signal Write Timing for 16-Bit, 2-Wait (Word Recess)      |       |

|            | Bus Control Signal Read Timing for 16-Bit, 2-Wait (Half-Word Access)  |       |

|            | Bus Control Signal Write Timing for 16-Bit, 2-Wait (Byte Access)      |       |

|            | Bus Control Signal Read Timing for 16-Bit, 2-Wait (Byte Access)       |       |

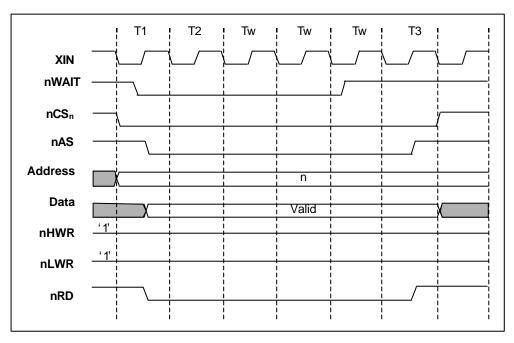

|            | Example of Wait State Insertion Timing.                               |       |

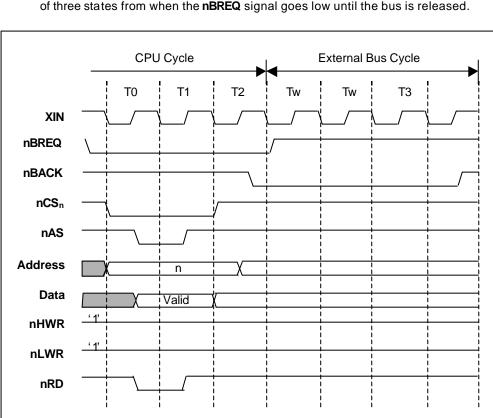

|            | B Example of External Bus Master Operation                            |       |

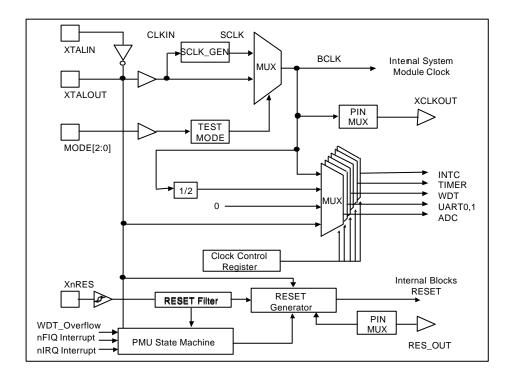

|            | PMU Block Diagram                                                     |       |

|            | Reset and Power Management State Machine.                             |       |

|            | Power on Reset Timing Diagram                                         |       |

|            | Watch Dog Timer Overflow Timing Diagram                               |       |

|            | Soft Reset (from WDT) Timing Diagram                                  |       |

|            | Soft Reset (from PMU) Timing Diagram                                  |       |

| Figure 6.1 | Interrupt Control Flow Diagram                                        |       |

| Figure 7.1 |                                                                       |       |

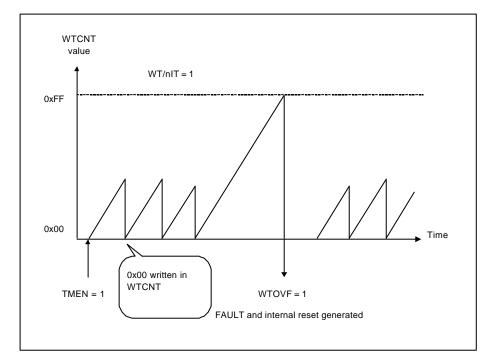

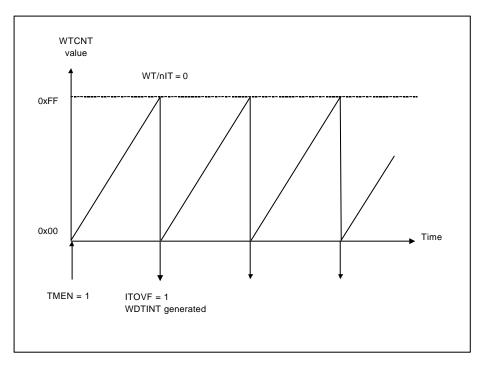

|            | Operation in the Watchdog Timer Mode                                  | 92    |

|            |                                                                       |       |

| Figure 7.3 |                                                                       |       |

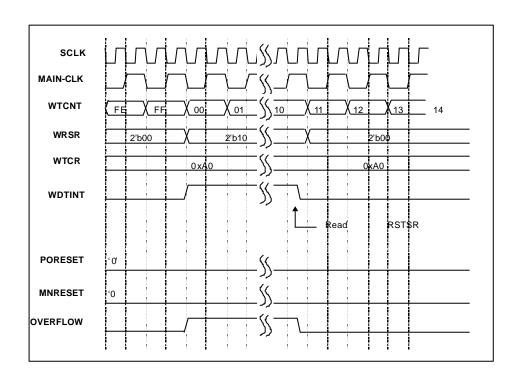

| Figure 7.4 | Interrupt Clear in the Interval Timer Mode                            |       |

| Figure 7.5 | Interrupt Clear in the Watchdog Timer Mode with Reset Disable         |       |

| Figure 7.6 |                                                                       |       |

| Figure 7.7 | Interrupt Clear in the Watchdog Timer Mode with Manual Reset          |       |

| Figure 8.1 | General-purpose Timer Unit Module Block Diagram                       | . 106 |

| Figure 8.2    Free-Running Counter Operation    115                                |

|------------------------------------------------------------------------------------|

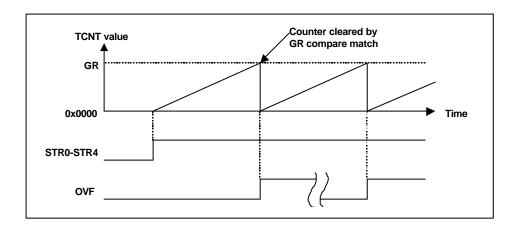

| Figure 8.3 Periodic Counter Operation116                                           |

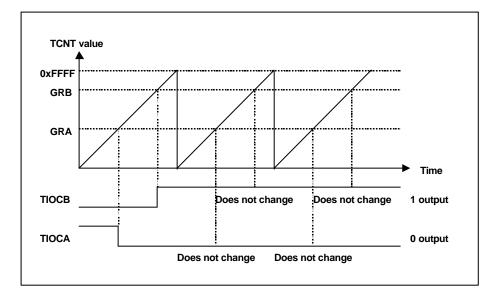

| Figure 8.4 Example of 0 Output/1 Output                                            |

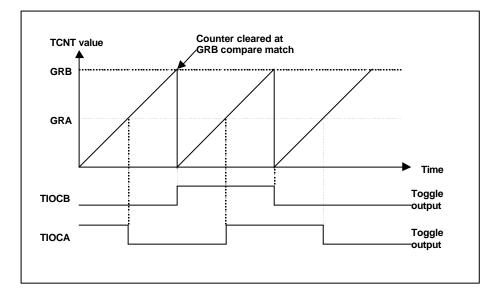

| Figure 8.5 Example of Toggle Output118                                             |

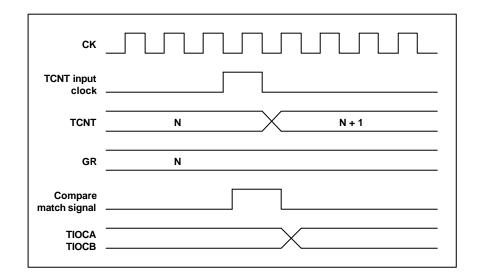

| Figure 8.6 Compare Match Signal Output Timing                                      |

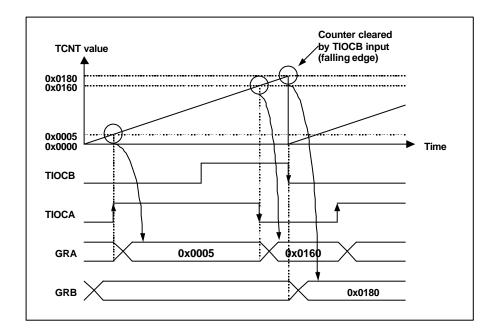

| Figure 8.7 Input Capture Operation                                                 |

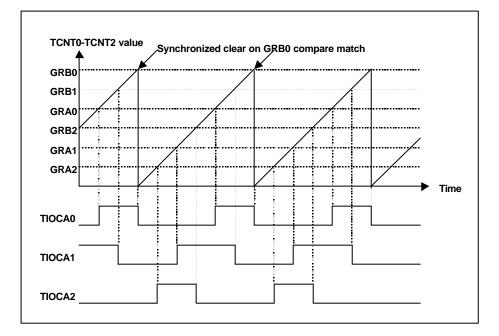

| Figure 8.8 Synchronized Operation Example                                          |

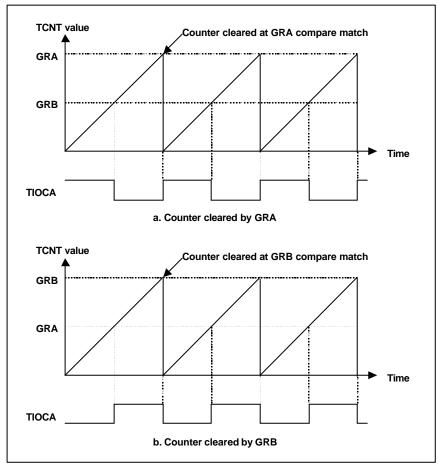

| Figure 8.9 PWM Mode Operation Example 1                                            |

| Figure 8.10 PWM Mode Operation Example 2122                                        |

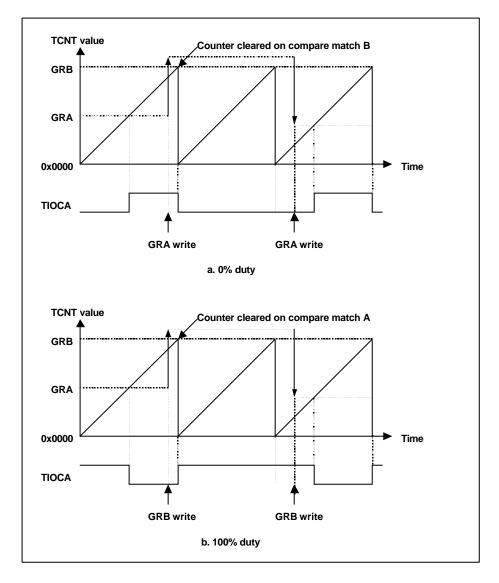

| Figure 8.11 Reset-Synchronized PWM Mode Operation Example                          |

| Figure 9.1 TOP BLOCK Diagram                                                       |

| Figure 9.2 Internal UART Diagram                                                   |

| Figure 10.1 GPIO Block Diagram and PADS Connections(example for Port A and Port B) |

|                                                                                    |

| Figure 12.1 Block Diagram of Flash Memory                                          |

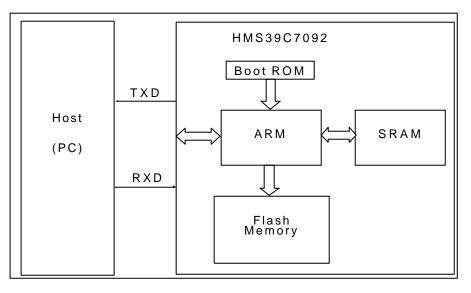

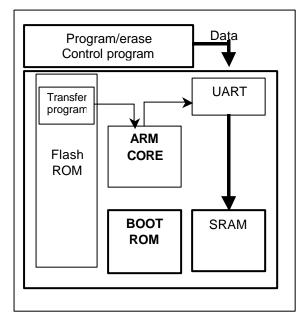

| Figure 12.2 System Configuration When Using On-Board Boot Mode                     |

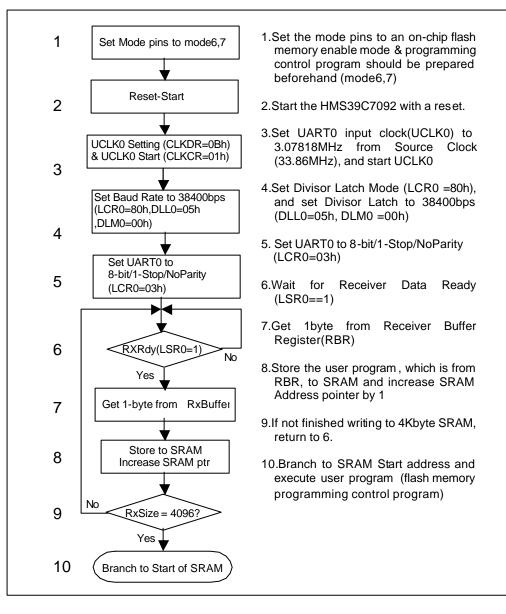

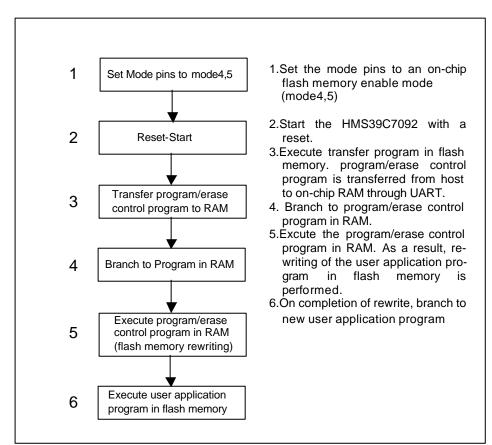

| Figure 12.3 Boot Mode Execution Procedure                                          |

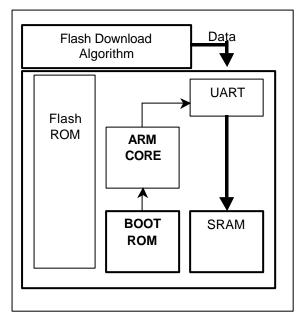

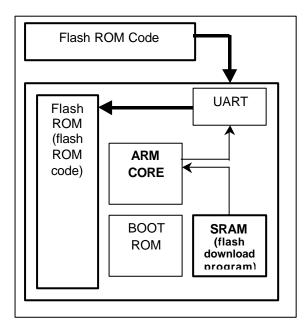

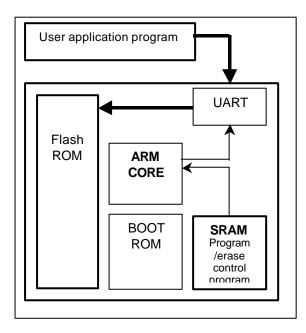

| Figure 12.4 User Mode Execution Procedure                                          |

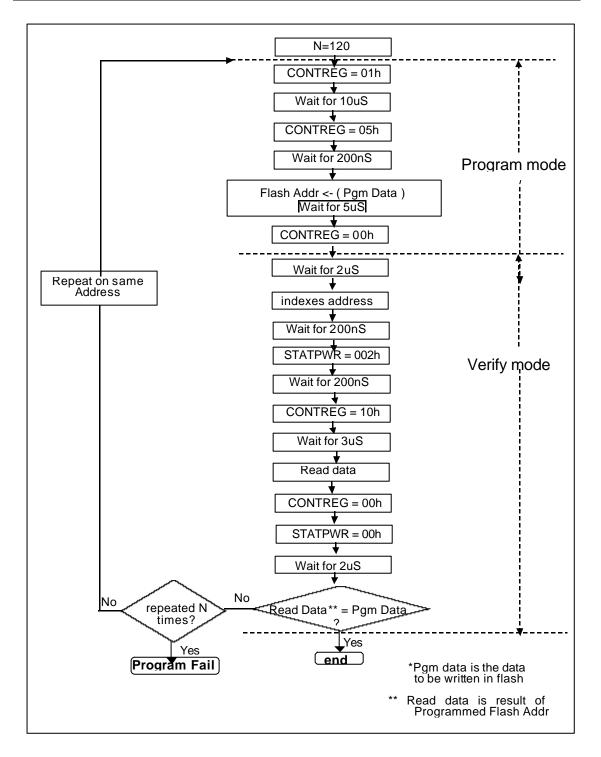

| Figure 12.5 Flash Program & Program Verify Sequence                                |

| Figure 12.6 Flash Pre-program & Pre-program Verify Sequence                        |

| Figure 12.7 Flash Erase & Erase Verify Sequence                                    |

| Figure 12.8 Flash Erase Algorithm                                                  |

| Figure 12.9 Timing Diagram of Read175                                              |

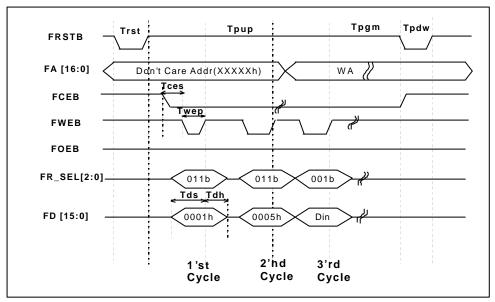

| Figure 12.10 Timing Diagram of Pre-Program/Program                                 |

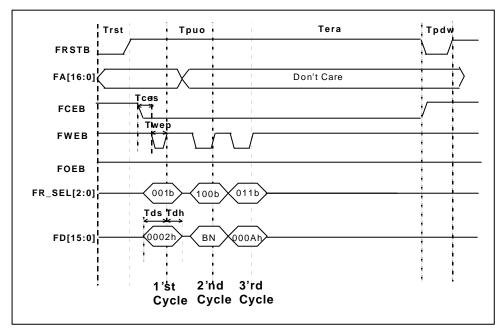

| Figure 12.11 Timing Diagram of Erase176                                            |

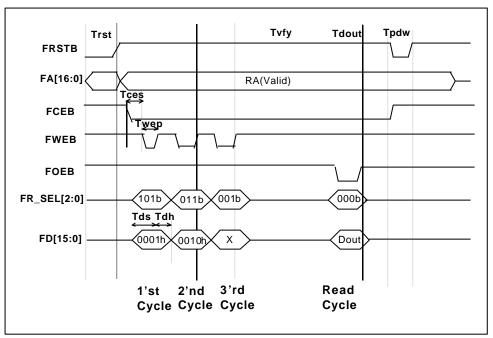

| Figure 12.12 Timing Diagram of Pre-Program/Program Verify                          |

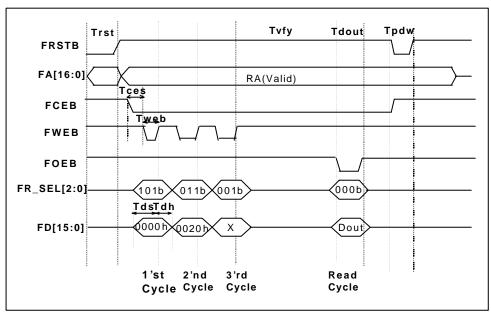

| Figure 12.13 Timing Diagram of Erase Verify177                                     |

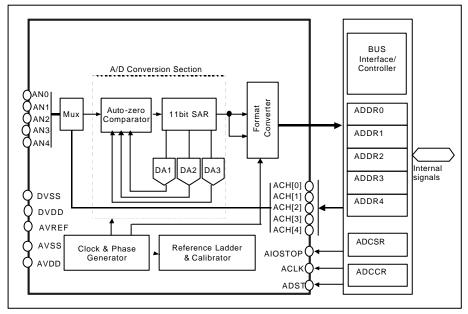

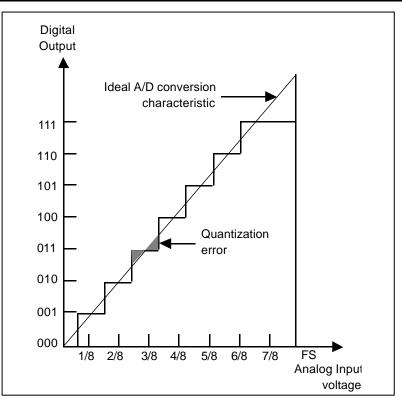

| Figure 13.1 Block Diagram of A/D Converter180                                      |

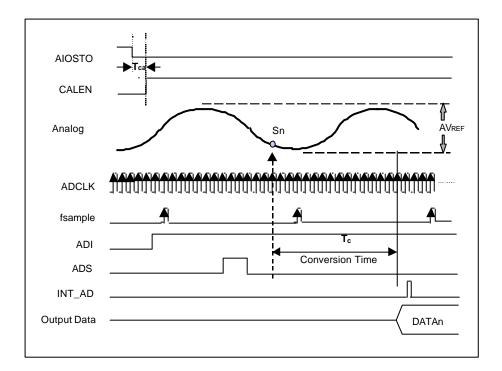

| Figure 13.2 A/D converter Operation                                                |

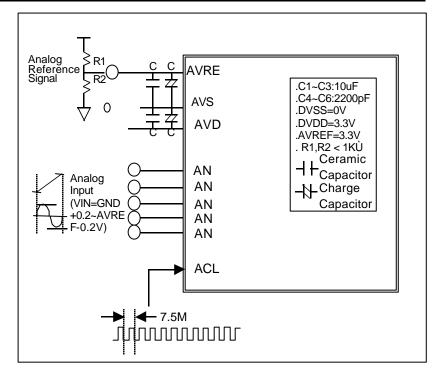

| Figure 13.3 Example of Analog Input Circuit                                        |

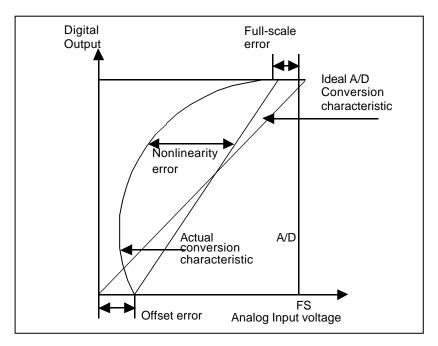

| Figure 13.4 A/D Converter Accuracy Definitions (1)188                              |

| Figure 13.5 A/D Converter Accuracy Definitions (2)189                              |

| Figure 14.1 The settling time of the crystal oscillator                            |

| Figure 14.2 Reset Input Timing                                                     |

| Figure 14.3 The Write Timing Diagram of the Bus Controller198                      |

| Figure 14.4 The Read Timing Diagram of the Bus Controller 198                      |

| Figure 14.5 Basic Bus Cycle with External Wait State                               |

| Figure 14.6 Bus Release Mode Timing 199                                            |

|                                                                                    |

### Tables

| Table 1.1  | Pin Descriptions                                    | . 16 |

|------------|-----------------------------------------------------|------|

| Table 1.1  | Pin Descriptions (Continued)                        | . 17 |

| Table 1.1  | Pin Descriptions (Continued)                        | . 18 |

| Table 1.1  |                                                     |      |

| Table 1.1  | Pin Descriptions (Continued)                        | 20   |

| Table 1.2  | HMS39C7092 Operation modes                          | 21   |

| Table 1.3  | Pin assignment by mode                              | 22   |

| Table 1.3  | Pin assignment by mode (continued)                  | 23   |

| Table 1.3  | Pin assignment by mode (continued)                  | 24   |

| Table 2.1  | The ARM Instruction set                             | 31   |

| Table 2.2  | THUMB instruction set opcodes                       | 34   |

| Table 2.3  | Condition code summary                              | 36   |

| Table 2.4  | PSR mode bit values                                 | 38   |

| Table 3.1  | Bus Controller Pins                                 |      |

| Table 3.2  | BUS Controller Register Map                         | . 50 |

| Table 3.3  | Byte Lane condition by XA[0]                        | . 55 |

| Table 4.1  | Pin Function Descriptions                           | . 66 |

| Table 4.2  |                                                     |      |

| Table 4.3  | MCU Controller Initial values in each mode          | 67   |

| Table 5.1  | Register Map of the PMU                             | 77   |

| Table 6.1  | Interrupt Controller Default Setting Value          |      |

| Table 6.2  | Memory Map of the Interrupt Controller              | . 87 |

| Table 6.3  | Interrupt Source Trigger Mode                       | . 88 |

| Table 7.1  | Memory Map of the Watchdog Timer APB Peripheral     |      |

| Table 7.2  | Internal Counter Clock Sources (SYSCLK = 40 MHz)    | . 98 |

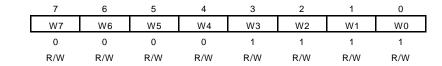

| Table 8.1  | Timer Global Control Register Map                   | 108  |

|            | Timer Channel Control Register Map                  |      |

| Table 8.3  | Timer Channel Starting Address                      | 108  |

| Table 9.1  | Signal Descriptions                                 | 127  |

| Table 9.2  | UART Register Address Map (0x1500 in UART1)         | 129  |

| Table 9.3  | UART Register Reset Values                          | 129  |

| Table 9.4a | a Divisor Values for each Baud rate (CLK=1.8432MHz) | 133  |

| Table 9.4b | Divisor Values for each Baud rate (CLK=3.6864MHz)   | 133  |

| Table 9.5  | Interrupt Control Functions                         | 138  |

| Table 9.6  | Summary of Registers                                | 142  |

| Table 10.1 | GPIO Register Memory Map                            | 145  |

| Table 12.1 | Operating mode                                      | 153  |

| Table 12.2 | 2 Signal description of Figure 12.1(BUS Interface)  | 155  |

|            | B Flash Memory Registers                            |      |

| Table 12.4 | Control Register                                    |      |

| Table 12.5 |                                                     | 159  |

| Table 12.6 | Status & Power Register                             |      |

| Table 12.7 | ' FR_SEL Value for access to internal Register      | 173  |

| Table 12.8 |                                                     |      |

| Table 12.9 |                                                     | 174  |

| Table 12.1 | 0 Setting for Flash PROM read/write                 | 175  |

| Table12.12Table13.1Table13.2Table14.1Table14.2Table14.3Table14.4Table14.5Table14.6Table14.7Table14.8Table14.9 | DC Characteristics | 178<br>181<br>182<br>- Preliminary |

|---------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------|

| Table 14.9                                                                                                    | 5                  |                                    |

Chapter 1 Introduction

#### Flash MCU(HMS39C7092)

#### 1.1 General Description

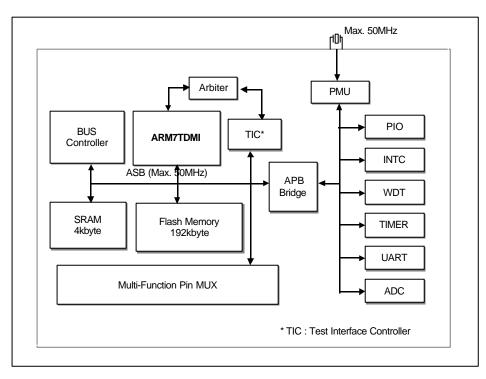

The 16bit MCU with embedded flash memory for optical storage is the first member of Hynix Micro Electronics 16/32bit MCU Family of high performance microcontroller units (MCUs). This family includes a series of peripherals from which numerous MCUs are assembled. This MCU contains extensive peripherals : 192Kbytes flash memory, 4K bytes SRAM, 6 channel 16bit Timer, Watch Dog Timer, 2 channel UART, Programmable Priority Interrupt Controller, 81bits PIO, BUS Controller including Chip select logic, which is On-Chip Modular Architecture (using AMBA).

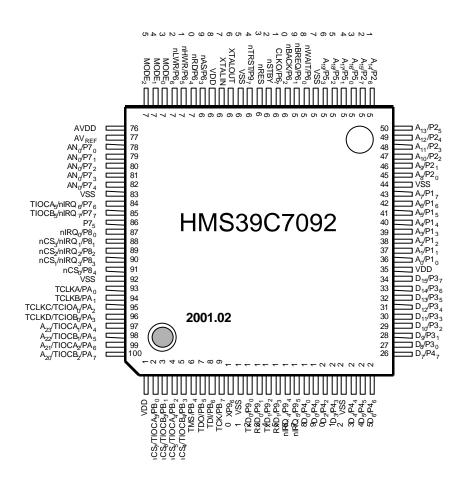

Figure 1.1 Package Outline

#### 1.2 Feature

- On-Chip Modular Architecture (using AMBA)

- Utilizes the ARM7TDMI 32/16bit RISC Family

- 192Kbyte flash memory

- 4Kbyte internal SRAM

- 8/16-bit external Data Bus

- Eight Programmable Chip Select Outputs with external wait input

- Low Power Consumption using Power Management Unit

- Fully static operation : Max. 50MHz

- Programmable Priority Interrupt Controller (8 external sources)

- Six 16bit Multi Function Timers/Counters for General Purpose Applications

- One 8bit Watch Dog Timer (WDT)

- Two UARTs (Universal Asynchronous Receiver Transmitter) compatible with 16C550 UART

- Programmable Input/Output ports (81-bits)

- 100 TQFP Package

Figure 1.2 HMS39C7092 Block Diagram

### Flash MCU(HMS39C7092)

#### 1.3 Pin Descriptions

| PIN  | SYMBOL             | DIR | DESCRIPTION                                                                     |

|------|--------------------|-----|---------------------------------------------------------------------------------|

| 1    | VDD                | -   | Power Supply 3.3V                                                               |

|      | nCS <sub>7</sub>   | 0   | External Chip Selection Number 7                                                |

| 2    | TCIOA <sub>3</sub> | I/O | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch3 |

|      | PB <sub>0</sub>    | I/O | General purpose input output of port B bit0                                     |

|      | nCS <sub>6</sub>   | 0   | External Chip Selection Number 6                                                |

| 3    | TCIOB <sub>3</sub> | I/O | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch3 |

|      | PB <sub>1</sub>    | I/O | General purpose input output of port B bit 1                                    |

|      | nCS₅               | 0   | External Chip Selection Number 5                                                |

| 4    | TIOCA <sub>4</sub> | I/O | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch4 |

|      | PB <sub>2</sub>    | I/O | General purpose input output of port B bit2                                     |

|      | nCS <sub>4</sub>   | 0   | External Chip Selection Number 4                                                |

| 5    | TIOCB <sub>4</sub> | I/O | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch4 |

| _    | PB <sub>3</sub>    | I/O | General purpose input output of port B bit3                                     |

| 0    | TMS                | I   | JTAG Test Mode Selection                                                        |

| 6 -  | PB <sub>4</sub>    | I/O | General purpose input output of port B bit4                                     |

| _    | TDO                | 0   | JTAG Test Data Output                                                           |

| 7 –  | PB₅                | I/O | General purpose input output of port B bit5                                     |

|      | TDI                | I   | JTAG Test Data Input                                                            |

| 8 —  | PB <sub>6</sub>    | I/O | General purpose input output of port B bit6                                     |

| •    | ТСК                | I   | JTAG Test Clock                                                                 |

| 9 _  | PB <sub>7</sub>    | I/O | General purpose input output of port B bit7                                     |

| 10   | TVPPD              | I   | 5Vinput for the use of Programming and Erasing of the Flash Memory              |

| 11   | VSS                | -   | Power ground                                                                    |

| 40   | TxD <sub>0</sub>   | 0   | Transmit Data of UART Ch0                                                       |

| 12 _ | P90                | I/O | General purpose input output of port 9 bit 0                                    |

| 4.0  | RxD <sub>0</sub>   | 0   | Receive Data of UART Ch0                                                        |

| 13 - | P91                | I/O | General purpose input output of port 9 bit 1                                    |

|      | TxD1               | 0   | Transmit Data of UART Ch1                                                       |

| 14 - | P92                | I/O | General purpose input output of port 9 bit 2                                    |

| 45   | RxD <sub>1</sub>   | 0   | Receive Data of UART Ch1                                                        |

| 15 _ | P93                | I/O | General purpose input output of port 9 bit 3                                    |

| 10   | nIRQ₄              | I   | External Interrupt Request number 4                                             |

| 16 _ | P94                | I/O | General purpose input output of port 9 bit 4                                    |

| 47   | nIRQ₅              | I   | External Interrupt Request number 5                                             |

| 17 _ | P95                | I/O | General purpose input output of port 9 bit 5                                    |

| 10   | D <sub>0</sub>     | I/O | External Data Bus bit 0                                                         |

| 18 _ | P40                | I/O | General purpose input output or port 4 bit 0                                    |

| 10   | D <sub>1</sub>     | I/O | External Data Bus bit 1                                                         |

| 19 — | P41                | I/O | General purpose input output or port 4 bit 1                                    |

| 20   | D <sub>2</sub>     | I/O | External Data Bus bit 2                                                         |

| 20 - | P42                | I/O | General purpose input output or port 4 bit 2                                    |

| 04   | D <sub>3</sub>     | I/O | External Data Bus bit 3                                                         |

| 21 - | P43                | I/O | General purpose input output or port 4 bit 3                                    |

### Introduction

| PIN  | SYMBOL          | DIR | DESCRIPTION                                  |

|------|-----------------|-----|----------------------------------------------|

| 22   | VSS             | -   | Power ground                                 |

| 23 _ | $D_4$           | I/O | External Data Bus bit 4                      |

| 23 _ | P44             | I/O | General purpose input output or port 4 bit 4 |

| 24   | D <sub>5</sub>  | I/O | External Data Bus bit 5                      |

| 24 - | P45             | I/O | General purpose input output or port 4 bit 5 |

| 25 _ | D <sub>6</sub>  | I/O | External Data Bus bit 6                      |

| 25   | P4 <sub>6</sub> | I/O | General purpose input output or port 4 bit 6 |

| 26 _ | D7              | I/O | External Data Bus bit 7                      |

| 20   | P47             | I/O | General purpose input output or port 4 bit 7 |

| 27 - | D <sub>8</sub>  | I/O | External Data Bus bit 8                      |

| 21 - | P30             | I/O | General purpose input output or port 3 bit 0 |

| 28 - | D <sub>9</sub>  | I/O | External Data Bus bit 9                      |

| 20   | P31             | I/O | General purpose input output or port 3 bit 1 |

| 29 _ | D <sub>10</sub> | I/O | External Data Bus bit 10                     |

| 29 - | P32             | I/O | General purpose input output or port 3 bit 2 |

| 30 _ | D <sub>11</sub> | I/O | External Data Bus bit 11                     |

| 30 _ | P33             | I/O | General purpose input output or port 3 bit 3 |

| 31 _ | D <sub>12</sub> | I/O | External Data Bus bit 12                     |

| 51 _ | P34             | I/O | General purpose input output or port 3 bit 4 |

| 32 _ | D <sub>13</sub> | I/O | External Data Bus bit 13                     |

| 52   | P3₅             | I/O | General purpose input output or port 3 bit 5 |

| 33 _ | D <sub>14</sub> | I/O | External Data Bus bit 14                     |

| 55 _ | P36             | I/O | General purpose input output or port 3 bit 6 |

| 34 - | D <sub>15</sub> | I/O | External Data Bus bit 15                     |

| 54 - | P37             | I/O | General purpose input output or port 3 bit 7 |

| 35   | VDD             | -   | Power Supply 3.3V                            |

| 36 _ | A <sub>0</sub>  | 0   | External Address Bus bit 0                   |

| 00 _ | P10             | I/O | General purpose input output or port 1 bit 0 |

| 37 - | A <sub>1</sub>  | 0   | External Address Bus bit 1                   |

| 51 - | P11             | I/O | General purpose input output or port 1 bit 1 |

| 38 - | A <sub>2</sub>  | 0   | External Address Bus bit 2                   |

| 00   | P1 <sub>2</sub> | I/O | General purpose input output or port 1 bit 2 |

| 39 _ | A <sub>3</sub>  | 0   | External Address Bus bit 3                   |

| 00 - | P1 <sub>3</sub> | I/O | General purpose input output or port 1 bit 3 |

| 40 _ | A <sub>4</sub>  | 0   | External Address Bus bit 4                   |

|      | P14             | I/O | General purpose input output or port 1 bit 4 |

| 41 - | A <sub>5</sub>  | 0   | External Address Bus bit 5                   |

|      | P1₅             | I/O | General purpose input output or port 1 bit 5 |

| 42   | A <sub>6</sub>  | 0   | External Address Bus bit 6                   |

|      | P1 <sub>6</sub> | I/O | General purpose input output or port 1 bit 6 |

| 43 - | A <sub>7</sub>  | 0   | External Address Bus bit 7                   |

| 10   | P17             | I/O | General purpose input output or port 1 bit 7 |

| 44   | VSS             | -   | Power ground                                 |

| 45 🗕 | A <sub>8</sub>  | 0   | External Address Bus bit 8                   |

| -5   | P20             | I/O | General purpose input output or port 2 bit 0 |

| 46 - | A9              | 0   | External Address Bus bit 9                   |

|      | P21             | I/O | General purpose input output or port 2 bit 1 |

| 47 _ | A <sub>10</sub> | 0   | External Address Bus bit 10                  |

| –    | P22             | I/O | General purpose input output or port 2 bit 2 |

### Flash MCU(HMS39C7092)

| 48        |                   |     |                                                 |

|-----------|-------------------|-----|-------------------------------------------------|

|           | A <sub>11</sub>   | 0   | External Address Bus bit 11                     |

| 40        | P23               | I/O | General purpose input output or port 2 bit 3    |

| 40        | A <sub>12</sub>   | 0   | External Address Bus bit 12                     |

| 49        | P24               | I/O | General purpose input output or port 2 bit 4    |

| 50        | A <sub>13</sub>   | 0   | External Address Bus bit 13                     |

| 50 —      | P25               | I/O | General purpose input output or port 2 bit 5    |

| <b>E4</b> | A <sub>14</sub>   | 0   | External Address Bus bit 14                     |

| 51 —      | P26               | I/O | General purpose input output or port 2 bit 6    |

| 50        | A <sub>15</sub>   | 0   | External Address Bus bit 15                     |

| 52        | P27               | I/O | General purpose input output or port 2 bit 7    |

| 50        | A <sub>16</sub>   | 0   | External Address Bus bit 16                     |

| 53 —      | P50               | I/O | General purpose input output of port 5 bit 0    |

| 54        | A <sub>17</sub>   | 0   | External Address Bus bit 17                     |

| 54        | P5₁               | I/O | General purpose input output of port 5 bit 1    |

| 55        | A <sub>18</sub>   | I   | External Address Bus bit 18                     |

| 55 —      | P52               | I/O | General purpose input output of port 5 bit 2    |

| 50        | A <sub>19</sub>   | 0   | External Address Bus bit 19                     |

| 56 —      | P53               | I/O | General purpose input output of port 5 bit 3    |

| 57        | VSS               | -   | Power ground                                    |

| 50        | nWAIT             | I   | External BUS cycle wait signal                  |

| 58 —      | P60               | I/O | General purpose input output of port 6 bit 0    |

| 50        | nBREQ             | I   | External BUS Request                            |

| 59 —      | P61               | I/O | General purpose input output of port 6 bit 1    |

|           | nBACK             | I   | External BUS Acknowledge                        |

| 60 —      | P62               | I/O | General purpose input output of port 6 bit 2    |

|           | CLKO              | 0   | BUS Clock Output                                |

| 61 —      | P67               | I/O | General purpose input output of port 6 bit 7    |

| 62        | nSTBY             | 0   | Standby mode signal. Power Down mode indicating |

| 63        | nRES              | I   | External Reset input                            |

| 64        | nTRST             | I   | JTAG Test Reset input                           |

| 64        | P97               | I/O | General purpose input output of port 9 bit 7    |

| 65        | VSS               | -   | Power ground                                    |

| 66        | XTALOUT           | 0   | Crystal feedback output                         |

| 67        | XTALIN            | I   | Crystal or External Oscillator input            |

| 68        | VDD               | -   | Power Supply 3.3V                               |

|           | nAS               | 0   | External Address Bus strobe                     |

| 69 🗕      | P63               | I/O | General purpose input output of port 6 bit 3    |

| 70        | nRD               | 0   | External Bus Read                               |

| 70        | P64               | I/O | General purpose input output of port 6 bit 4    |

|           | nHWR              | 0   | External upper 8 bit data bus write             |

| 71 —      | P65               | I/O | General purpose input output of port 6 bit 5    |

|           | nLWR              | 0   | External lower 8 bit data bus write             |

| 72 —      | P66               | I/O | - General purpose input output of port 6 bit 6  |

| 73        | MODE <sub>0</sub> | I   | MODE bit 0                                      |

| 74        | MODE <sub>1</sub> | I   | MODE bit 1                                      |

|           | MODE <sub>2</sub> | 1   | MODE bit 2                                      |

| 75        | IVIODE2           |     |                                                 |

| 75<br>76  | AVDD              | -   | Analog Power Supply 3.3V                        |

### Introduction

| PIN  | SYMBOL                   | DIR      | DESCRIPTION                                                                     |

|------|--------------------------|----------|---------------------------------------------------------------------------------|

| 78 _ | P70                      | 0        | General purpose output of port 7 bit 0                                          |

| 10 - | AN <sub>0</sub>          | I        | ADC Channel 0 input                                                             |

| 70   | P71                      | 0        | General purpose output of port 7 bit 1                                          |

| 79 🗕 | AN <sub>1</sub>          | I        | ADC Channel 1 input                                                             |

|      | P72                      | 0        | General purpose output of port 7 bit 2                                          |

| 80 - | AN <sub>2</sub>          | I        | ADC Channel 2 input                                                             |

|      | P73                      | 0        | General purpose output of port 7 bit 3                                          |

| 81 - | AN <sub>3</sub>          | I        | ADC Channel 3 input                                                             |

|      | P74                      | 0        | General purpose output of port 7 bit 4                                          |

| 82 _ | AN <sub>4</sub>          | I        | ADC Channel 4 input                                                             |

| 83   | VSS                      | -        | Power ground                                                                    |

|      | TIOCA₅                   | I/O      | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch5 |

| 84   | nIRQ <sub>6</sub>        | 1        | External Interrupt Request number 6                                             |

| -    | P76                      | I/O      | General purpose input output of port 7 bit 6                                    |

|      | TIOCB                    | I/O      | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch5 |

| 85   | nIRQ <sub>7</sub>        | 1        | External Interrupt Request number 7                                             |

| -    | P77                      | I/O      | General purpose input output of port 7 bit 7                                    |

| 86   | P75                      | I/O      | General purpose input output of port 7 bit 5                                    |

| 00   | nIRQ                     | 1,0      | External Interrupt Request number 0                                             |

| 87 - | P80                      | 1/0      | General purpose input output of port 8 bit 0                                    |

|      | nCS <sub>3</sub>         | 0        | External Chip Selection Number 3                                                |

| 88   | nIRQ <sub>1</sub>        | 1        | External Interrupt Request number 1                                             |

|      | P81                      | 1/0      | General purpose input output of port 8 bit 1                                    |

|      | nCS <sub>2</sub>         | 0        | External Chip Selection Number 2                                                |

| 89   | nIRQ <sub>2</sub>        | 1        | External Interrupt Request number 2                                             |

|      | P8 <sub>2</sub>          | I/O      | General purpose input output of port 8 bit 2                                    |

|      | nCS <sub>1</sub>         | 0        | External Chip Selection Number 1                                                |

| 90   | nIRQ <sub>3</sub>        | <u> </u> | External Interrupt Request number 3                                             |

| 30 - | P83                      | 1/0      | General purpose input output of port 8 bit 3                                    |

|      | nCS <sub>0</sub>         | 0        | External Chip Selection Number 0                                                |

| 91 _ | P84                      | 1/0      |                                                                                 |

| 92   | VSS                      | -        | General purpose input output of port 8 bit 4 Power ground                       |

| 52   | TCLKA                    | -        | External timer input clock A                                                    |

| 93 - |                          | I/O      |                                                                                 |

|      | PA <sub>0</sub><br>TCLKB | 1/0<br>I | General purpose input output of port A bit 0                                    |

| 94 🗕 |                          |          | External timer input clock B                                                    |

|      |                          | I/O<br>I | General purpose input output of port A bit 1                                    |

| 95   | TCLKC                    |          | External timer input clock C                                                    |

| 95   | TIOCA                    | I/O      | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch0 |

|      | PA <sub>2</sub>          | I/O      | General purpose input output of port A bit 2                                    |

|      | TCLKD                    | 1        | External timer input clock D                                                    |

| 96   | TIOCB <sub>0</sub>       | I/O      | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch0 |

|      | PA <sub>3</sub>          | I/O      | General purpose input output of port A bit 3                                    |

|      | A <sub>23</sub>          | 0        | External Address Bus bit 23                                                     |

| 97   | TIOCA <sub>1</sub>       | I/O      | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch1 |

|      | PA <sub>4</sub>          | I/O      | General purpose input output of port A bit 4                                    |

### Flash MCU(HMS39C7092)

| PIN | SYMBOL             | DIR | DESCRIPTION                                                                     |

|-----|--------------------|-----|---------------------------------------------------------------------------------|

|     | A <sub>22</sub>    | 0   | External Address Bus bit 22                                                     |

| 98  | TIOCB <sub>1</sub> | I/O | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch1 |

| -   | PA <sub>5</sub>    | I/O | General purpose input output of port A bit 5                                    |

|     | A <sub>21</sub>    | 0   | External Address Bus bit 21                                                     |

| 99  | TIOCA <sub>2</sub> | I/O | PWM output, Compare match output of Reg.A and signal capture input of Timer Ch2 |

| -   | PA <sub>6</sub>    | I/O | General purpose input output of port A bit 6                                    |

|     | A <sub>20</sub>    | 0   | External Address Bus bit 20                                                     |

| 100 | TIOCB <sub>2</sub> | I/O | PWM output, Compare match output of Reg.B and signal capture input of Timer Ch2 |

| -   | PA <sub>7</sub>    | I/O | General purpose input output of port A bit 7                                    |

#### 1.4 Operation Mode description

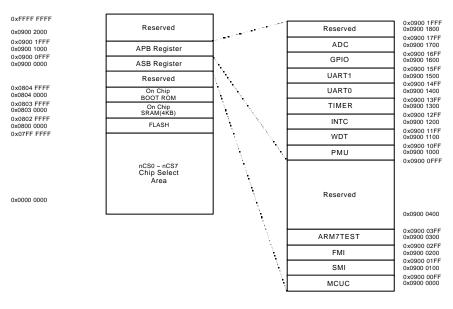

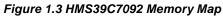

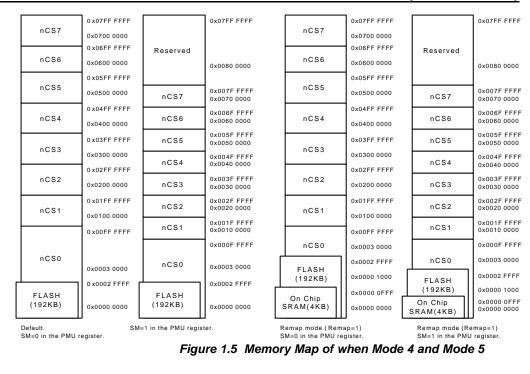

HMS39C7092 is Flash Memory-embedded ARM microcontroller. It has six-operation modes shown in **Table 1.2**. HMS39C7092 External pin function is changed by setting external MODE pin or configuring the PIN MUX registers. The pin assignment by mode is shown in **Table 1.3**. Especially changing mode causes memory remap for appropriate mode. *Figure 1.3* shows default memory map and the memory maps of respective modes are shown in *Figure 1.4*, *Figure 1.5* and *Figure 1.6*. The Mode definition is listed as follows:

| MODE | MODE DESCRIPTION                                        |

|------|---------------------------------------------------------|

| 0,1  | Reserved for Test                                       |

| 2    | External 8-bit data bus with 16MBytes of Address Range  |

| 3    | External 16-bit data bus with 16MBytes of Address Range |

| 4    | Flash-boot mode with 16-bit data bus                    |

| 5    | Flash-boot mode (micro-computer mode)                   |

| 6    | UART-boot mode with 16-bit data bus                     |

| 7    | UART-boot mode (micro-computer mode)                    |

| Table 1.2 HMS39C7092 Operation mode | Table 1.2 | HMS39C7092 | Operation | modes |

|-------------------------------------|-----------|------------|-----------|-------|

|-------------------------------------|-----------|------------|-----------|-------|

| PIN | MODE 2   | MODE 3    | MODE 4          | MODE 6         | MODE 5          | MODE 7         |

|-----|----------|-----------|-----------------|----------------|-----------------|----------------|

|     | External | External  | Flash boot mode | UART boot mode | Flash boot mode | UART boot mode |

|     | 8bit BUS | 16bit BUS | with 16bit BUS  | with 16bit BUS | (MICOM mode)    | (MICOM mode)   |

| 1   | VDD      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 2   | nCS7     | ÷         | ÷               | ÷              | TIOCA3          | ÷              |

| 3   | nCS6     | ÷         | ÷               | ÷              | TIOCB3          | ÷              |

| 4   | nCS5     | ÷         | ÷               | ÷              | TIOCA4          | ÷              |

| 5   | nCS4     | ÷         | ÷               | ÷              | TIOCB4          | ÷              |

| 6   | TMS      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 7   | TDO      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 8   | TDI      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 9   | TCK      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 10  | TVPPD    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 11  | VSS      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 12  | TxD0     | ÷         | ÷               | ÷              | ÷               | ÷              |

| 13  | RxD0     | ÷         | ÷               | ÷              | ÷               | ÷              |

| 14  | TxD1     | ÷         | ÷               | ÷              | ÷               | ÷              |

| 15  | RxD1     | ÷         | ÷               | ÷              | ÷               | ÷              |

| 16  | nIRQ4    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 17  | nIRQ5    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 18  | D0       | ÷         | ÷               | ÷              | P40             | ÷              |

| 19  | D1       | ÷         | ÷               | ÷              | P41             | ÷              |

| 20  | D2       | ÷         | ÷               | ÷              | P42             | ÷              |

| 21  | D3       | ÷         | ÷               | ÷              | P43             | ÷              |

| 22  | VSS      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 23  | D4       | ÷         | ÷               | ÷              | P44             | ÷              |

| 24  | D5       | ÷         | ÷               | ÷              | P45             | ÷              |

| 25  | D6       | ÷         | ÷               | ÷              | P46             | ÷              |

| 26  | D7       | ÷         | ÷               | ÷              | P47             | ÷              |

| 27  | P30      | D8        | ÷               | ÷              | P30             | ÷              |

| 28  | P31      | D9        | ÷               | ÷              | P31             | ÷              |

| 29  | P32      | D10       | ÷               | ÷              | P32             | ÷              |

| 30  | P33      | D11       | ÷               | ÷              | P33             | ÷              |

| 31  | P34      | D12       | ÷               | ÷              | P34             | ÷              |

| 32  | P35      | D13       | ÷               | ÷              | P35             | ÷              |

| 33  | P36      | D14       | ÷               | ÷              | P36             | ÷              |

| 34  | P37      | D15       | ÷               | ÷              | P37             | ÷              |

| 35  | VDD      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 36  | A0       | ÷         | ÷               | ÷              | P10             | ÷              |

| 37  | A1       | ÷         | ÷               | ÷              | P11             | ÷              |

| 38  | A2       | ÷         | ÷               | ÷              | P12             | ÷              |

| 39  | A3       | ÷         | ÷               | ÷              | P13             | ÷              |

| 40  | A4       | ÷         | ÷               | ÷              | P14             | ÷              |

### Introduction

| PIN | MODE2    | MODE3        | MODE4           | MODE6          | MODE5           | MODE7          |

|-----|----------|--------------|-----------------|----------------|-----------------|----------------|

| No. | External | External     | Flash boot mode | UART boot mode | Flash boot mode | UART boot mode |

|     | 8bit BUS | 16bit BUS    | with 16bit BUS  | with 16bit BUS | (MICOM mode)    | (MICOM mode)   |

| 41  | A5       | <del>(</del> | $\leftarrow$    | <del>~</del>   | P15             | ÷              |

| 42  | A6       | ÷            | ÷               | ÷              | P16             | ÷              |

| 43  | A7       | ÷            | ÷               | ÷              | P17             | ÷              |

| 44  | VSS      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 45  | A8       | ÷            | ÷               | ÷              | P20             | ÷              |

| 46  | A9       | ÷            | ÷               | ÷              | P21             | ÷              |

| 47  | A10      | ÷            | ÷               | ÷              | P22             | ÷              |

| 48  | A11      | ÷            | ÷               | ÷              | P23             | ÷              |

| 49  | A12      | ÷            | ÷               | ÷              | P24             | ÷              |

| 50  | A13      | ÷            | ÷               | ÷              | P25             | ÷              |

| 51  | A14      | ÷            | ÷               | ÷              | P26             | ÷              |

| 52  | A15      | ÷            | ÷               | ÷              | P27             | ÷              |

| 53  | A16      | ÷            | ÷               | ÷              | P50             | ÷              |

| 54  | A17      | ÷            | ÷               | ÷              | P51             | ÷              |

| 55  | A18      | ÷            | ÷               | ÷              | P52             | ÷              |

| 56  | A19      | ÷            | ÷               | ÷              | P53             | ÷              |

| 57  | VSS      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 58  | nWAIT    | ÷            | ÷               | ÷              | P60             | ÷              |

| 59  | nBREQ    | ÷            | ÷               | ÷              | P61             | ÷              |

| 60  | nBACK    | ÷            | ÷               | ÷              | P62             | ÷              |

| 61  | CLKO     | ÷            | ÷               | ÷              | P67             | ÷              |

| 62  | nSTBY    | ÷            | ÷               | <del>\</del>   | nSTBY           | ÷              |

| 63  | nRES     | ÷            | ÷               | ÷              | nRES            | ÷              |

| 64  | nTRST    | ÷            | ÷               | ÷              | nTRST           | ÷              |

| 65  | VSS      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 66  | XTALOUT  | ÷            | ÷               | ÷              | ÷               | ÷              |

| 67  | XTALIN   | ÷            | ÷               | ÷              | ÷               | ÷              |

| 68  | VDD      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 69  | nAS      | ÷            | ÷               | ÷              | P63             | ÷              |

| 70  | nRD      | ÷            | ÷               | ÷              | P64             | ÷              |

| 71  | nHWR     | ÷            | ÷               | ÷              | P65             | ÷              |

| 72  | nLWR     | ÷            | ÷               | ÷              | P66             | ÷              |

| 73  | MODE0    | ÷            | ÷               | ÷              | ÷               | ÷              |

| 73  | MODE1    | ÷            | ÷               | ÷              | ÷               | ÷              |

| 75  | MODE2    | ÷            | ÷               | ÷              | ÷               | ÷              |

| 76  | AVDD     | ÷            | ÷               | ÷              | ÷               | ÷              |

| 77  | AVREF    | ÷            | ÷               | ÷              | ÷               | ÷              |

| 78  | AN0      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 79  | AN1      | ÷            | ÷               | ÷              | ÷               | ÷              |

| 80  | AN2      | ÷            | ÷               | ÷              | ÷               | ÷              |

#### Table 1.3 Pin assignment by mode (continued)

| PIN | MODE2    | MODE3     | MODE4           | MODE6          | MODE5           | MODE7          |

|-----|----------|-----------|-----------------|----------------|-----------------|----------------|

| No. | External | External  | Flash boot mode | UART boot mode | Flash boot mode | UART boot mode |

|     | 8bit BUS | 16bit BUS | with 16bit BUS  | with 16bit BUS | (MICOM mode)    | (MICOM mode)   |

| 81  | AN3      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 82  | AN4      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 83  | VSS      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 84  | TIOC A5  | ÷         | ÷               | ÷              | ÷               | ÷              |

| 85  | TIOCB5   | ÷         | ÷               | ÷              | ÷               | ÷              |

| 86  | P75      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 87  | nIRQ0    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 88  | nCS3     | ÷         | ÷               | ÷              | P81             | ÷              |

| 89  | nCS2     | ÷         | ÷               | ÷              | P82             | ÷              |

| 90  | nCS1     | ÷         | ÷               | ÷              | P83             | ÷              |

| 91  | nCS0     | ÷         | ÷               | ÷              | P84             | ÷              |

| 92  | VSS      | ÷         | ÷               | ÷              | ÷               | ÷              |

| 93  | TCLKA    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 94  | TCLKB    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 95  | TCLKC    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 96  | TCLKD    | ÷         | ÷               | ÷              | ÷               | ÷              |

| 97  | A23      | ÷         | ÷               | TIOCA1         | ÷               | ÷              |

| 98  | A22      | ÷         | ÷               | TIOCB1         | ÷               | ÷              |

| 99  | A21      | ÷         | ÷               | TIOCA2         | ÷               | ÷              |

| 100 | A20      | ÷         | ÷               | TIOCB2         | ÷               | ÷              |

#### Introduction

#### 1.5 Memory Map

|       | 0x07FF FFFF |          | 0x07FF FFFF                |                 | 0x07FF FFFF |                 | 0x07FF           |

|-------|-------------|----------|----------------------------|-----------------|-------------|-----------------|------------------|

| nCS7  | 0x0700 0000 |          |                            | nCS7            | 0x0700 0000 |                 |                  |

|       | 0x06FF FFFF | Reserved |                            |                 | 0x06FF FFFF | Reserved        |                  |

| nCS6  | 0x0600 0000 |          | 0x0080 0000                | nCS6            | 0x0600 0000 |                 | 0x0080           |

|       | 0x05FF FFFF |          |                            |                 | 0x05FF FFFF |                 |                  |

| nCS5  | 0x0500 0000 | nCS7     | 0x007F FFFF<br>0x0070 0000 | nCS5            | 0x0500 0000 | nCS7            | 0x007F<br>0x0070 |

|       | 0x04FF FFFF |          | 0x006F FFFF                |                 | 0x04FF FFFF |                 | 0x006F           |

| nCS4  | 0x0400 0000 | nCS6     | 0x0060 0000                | nCS4            | 0x0400 0000 | nCS6            | 0x0060           |

|       | 0x03FF FFFF | nCS5     | 0x005F FFFF<br>0x0050 0000 |                 | 0x03FF FFFF | nCS5            | 0x005F<br>0x0050 |

| nCS3  | 0x0300 0000 |          | 0x004F FFFF                | nCS3            | 0x0300 0000 | -               | 0x004F           |

|       | 0x02FF FFFF | nCS4     | 0x0040 0000                |                 | 0x02FF FFFF | nCS4            | 0x0040           |

| nCS2  | 0x0200 0000 | nCS3     | 0x003F FFFF<br>0x0030 0000 | nCS2            | 0x0200 0000 | nCS3            | 0x003F<br>0x0030 |

|       | 0x01FF FFFF | nCS2     | 0x002F FFFF                |                 | 0x01FF FFFF | nCS2            | 0x002F<br>0x0020 |

| nCS1  | 0x0100 0000 | 110.32   |                            | nCS1            | 0x0100 0000 | 110.32          |                  |

|       | 0x00FF FFFF | nCS1     | 0x001F FFFF<br>0x0010 0000 |                 | 0x00FF FFFF | nCS1            | 0x001F<br>0x0010 |

| nCS0  |             |          | 0x000F FFFF                | nCS0            | 0x0000 1000 | nCS0            | 0x000F<br>0x0000 |

| 11030 | 0x0000 0000 | nCS0     | [                          | 001.:           | 0×0000 0FFF |                 | 0x0000           |

|       |             |          | 0x0000 0000                | On Chip<br>SRAM | 0x0000 0000 | On Chip<br>SRAM | 0x0000           |

Figure 1.4 Memory Map of Mode 3

|                             | Ox07FF FFFF  |                                      | Ox07FF FFFF                 |                                          | Ox07FF FFFF |                                       | 0x07FF FFFF                |

|-----------------------------|--------------|--------------------------------------|-----------------------------|------------------------------------------|-------------|---------------------------------------|----------------------------|

| nCS7                        |              |                                      | 0X07FF FFFF                 | nCS7                                     |             |                                       | 0x07FF FFFF                |

| 11001                       | 0x0700 0000  |                                      |                             | 1007                                     | 0x0700 0000 |                                       |                            |

|                             | 0 x06FF FFFF | Reserved                             |                             |                                          | 0x06FF FFFF | Reserved                              |                            |

| nCS6                        | 0x0600 0000  |                                      |                             | nCS6                                     | 0x0600 0000 |                                       |                            |

|                             | 0 x05FF FFFF |                                      | 0x0080 0000                 |                                          | 0x05FF FFFF |                                       | 0x0080 0000                |

| nCS5                        | 0x0500 0000  | nCS7                                 | 0 x007F FFFF<br>0x0070 0000 | nCS5                                     | 0x0500 0000 | nCS7                                  | 0x007F FFFF<br>0x0070 0000 |

|                             | 0x04FF FFFF  |                                      | 0x006F FFFF                 |                                          | 0x04FF FFFF |                                       | 0x006F FFFF                |

| nCS4                        | 0x0400 0000  | nCS6                                 | 0x0060 0000                 | nCS4                                     | 0x0400 0000 | nCS6                                  | 0x0060 0000                |

| nCS3                        | 0 x03FF FFFF | nCS5                                 | 0x005F FFFF<br>0x0050 0000  | nCS3                                     | 0x03FF FFFF | nCS5                                  | 0x005F FFFF<br>0x0050 0000 |

| 1000                        | 0x0300 0000  | nCS4                                 | 0x004F FFFF                 |                                          | 0x0300 0000 | nCS4                                  | 0x004F FFFF                |

|                             | 0 x02FF FFFF | 11004                                | 0x0040 0000                 |                                          | 0x02FF FFFF | 11004                                 | 0x0040 0000                |

| nCS2                        | 0x0200 0000  | nCS3                                 | 0 x003F FFFF<br>0x0030 0000 | nCS2                                     | 0x0200 0000 | nCS3                                  | 0x003F FFFF<br>0x0030 0000 |

|                             | 0 x01FF FFFF | nCS2                                 | 0x002F FFFF                 |                                          | 0x01FF FFFF | nCS2                                  | 0x002F FFFF                |

| nCS1                        | 0x0100 0000  | 11032                                | 0x0020 0000                 | nCS1                                     | 0x0100 0000 | 11032                                 | 0x0020 0000                |

|                             | 0 x00FF FFFF | nCS1                                 | 0 x001F FFFF<br>0x0010 0000 |                                          | 0x00FF FFFF | nCS1                                  | 0x001F FFFF<br>0x0010 0000 |

|                             |              |                                      | 0x000F FFFF                 | nCS0                                     | 0x0003 0000 |                                       | 0x000F FFFF                |

| nCS0                        | 0x0000 0100  | nCS0                                 | 0x0000 0100                 |                                          | 0x0002 FFFF | nCS0                                  | 0x0003 0000                |

|                             |              |                                      |                             | FLASH                                    | 0x0000 1000 |                                       | 0x0002 FFFF                |

| On Chip                     | 0 ×0000 00FF | On Chip                              | 0 x0000 00FF                | (192KB)                                  | 0x0000 0FFF | FLASH                                 | 0x0000 1000                |

| Boot ROM<br>(256Byte)       | 0x0000 0000  | Boot ROM<br>(256Byte)                | 0x0000 0000                 |                                          | 0x0000 0000 | (192KB)                               | 0x0000 0FFF<br>0x0000 0000 |

| Default.<br>SM=0 in the PMU |              | =1 and OnFLASH=0<br>ne PMU register. | 0                           | SM=0 and On FLAS<br>in the PMU register. |             | SM=1 and OnFLAS<br>in the PMU registe |                            |

Figure 1.6 Memory Map of Mode 6 and Mode 7

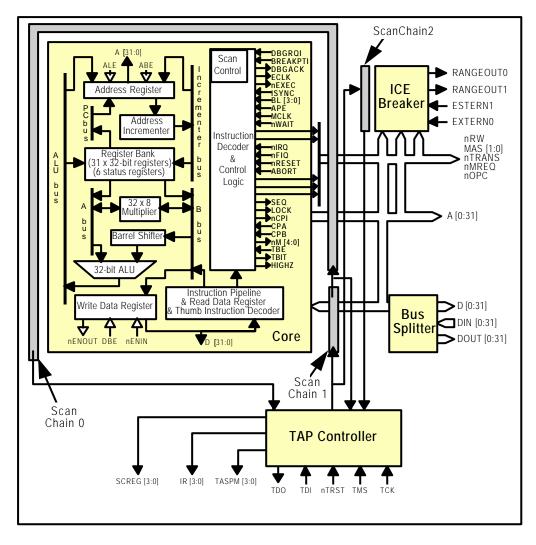

**ARM7TDMI Core**

## Chapter 2 ARM7TDMI Core

#### 2.1 General Description

The ARM7TDMI is a member of the ARM family of general-purpose 32bit microprocessors, which offers high performance for very low power consumption and price. This processor employs a unique architectural strategy known as THUMB, which makes it ideally suited to high volume applications with memory restrictions or applications where code density is an issue.

The key idea behind THUMB is a super reduced instruction set. Essentially, the ARM7TDMI has two instruction sets, the standard 32bit ARM set and 16bit THUMB set. The THUMB sets 16bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM' s performance advantage over a traditional 16bit processor by using 16bit registers. This is possible because THUMB code operates on the same 32bit register set as ARM code.

See also ARM7TDMI Datasheet (ARM DDI 0029E) for detail.

#### 2.2 Feature

- 32bit RISC architecture

- Low power consumption

- ARM7TDMI core with;

- On-chip ICEbreaker debug support

- 32bit x 8 hardware multiplier

- Thumb decompressor

- Utilizes the ARM7TDMI embedded processor

- High performance 32 bit RISC architecture

- High density 16 bit instruction set (THUMB code)

- Fully static operation : 0 ~ 80MHz

- 3-stage pipeline architecture (Fetch, decode, and execution stage)

- Enhanced ARM software toolkit

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16-bit memory system.

#### 2.3 Core Block Diagram

Figure 2.1 ARM7TDMI Core Block Diagram

#### **ARM7TDMI Core**

### Flash MCU(HMS39C7092)

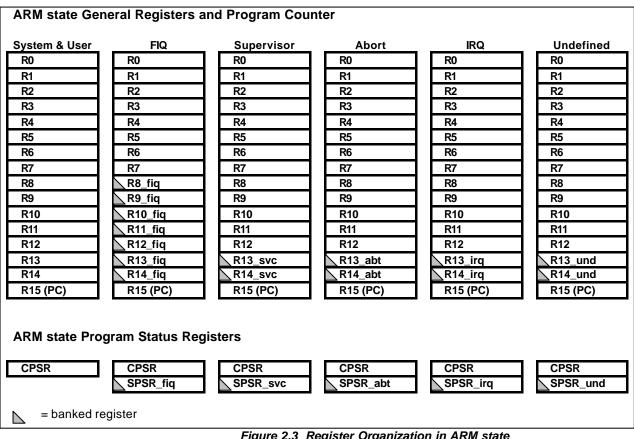

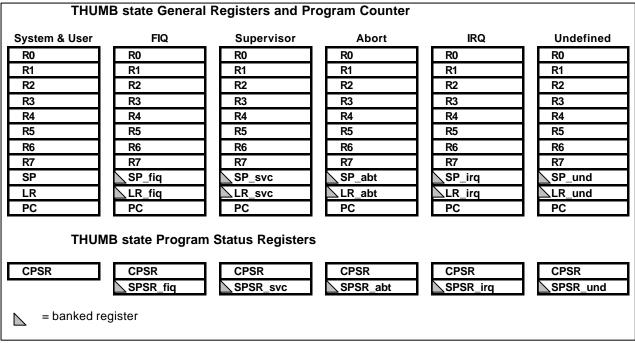

#### 2.4 Instruction Set

#### 2.4.1 ARM Instruction

| 31 30 29 28 | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |    |    |    |     |          |    |          |             |             |          |                    |     |      | 6  | 5                                      |   | 4   | 3210                                     |                                         |

|-------------|---------------------------------------------------------------------------------------|----|----|----|-----|----------|----|----------|-------------|-------------|----------|--------------------|-----|------|----|----------------------------------------|---|-----|------------------------------------------|-----------------------------------------|

| Cond        | 0                                                                                     | 0  | I  | С  | )pc | 00       | de | s        | Rn Rd       |             |          |                    |     | С    | pe | era                                    | n | d   |                                          | Data Processing / PSR Transfer          |

| Cond        | 0                                                                                     | 0  | 0  | 0  | 0   | 0        | A  | s        | Rd          | Rn          | Rs       |                    | 1   | 0    | 0  |                                        | 1 | Rm  | Multiply                                 |                                         |