# HT6264-70 CMOS 8K×8-Bit SRAM

### **Features**

- Single 5V power supply

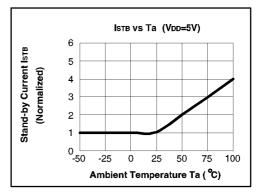

- Low power consumption

- Operating: 200mW (Typ.)

- Standby: 5μW (Typ.)

- 70ns (Max.) high speed access time

- Memory expansion by pin  $\overline{OE}$

- Common I/O using tri-state outputs

- TTL compatible interface levels

- Fully static operation

- Pin-compatible with standard 8K×8 bits of EPROM/MASK ROM

- 28-pin DIP/SDIP/SOP package

### **General Description**

The HT6264-70 is a 65,536-bit static random access memory organized as 8192 words by 8 bits and operates from a single 5-volt power supply. It is built with HOLTEK's high performance CMOS 0.8µm SPDM process.

Six-transistor full COMS memory cell provides low standby current and high-reliability. Inputs and tri-state outputs are TTL compatible and allow for direct interfacing with common system bus structures.

### **Pin Assignment**

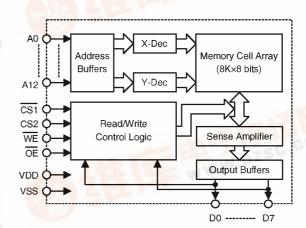

### **Block Diagram**

### **Pin Description**

| Pin No.                 | Pin Name              | I/O | Description                       |

|-------------------------|-----------------------|-----|-----------------------------------|

| 10~3, 25, 24, 21, 23, 2 | A0~A12                | I   | Address input pins                |

| 11~13, 15~19            | D0~D2, D3~D7          | I/O | Data input and output signal pins |

| 26, 20                  | $CS2, \overline{CS1}$ | I   | Chip select signal pin            |

| 22                      | ŌE                    | I   | Output enable signal pin          |

| 27                      | WE                    | I   | Write enable signal pin           |

| 28                      | VDD                   | I   | Positive power supply pin         |

| 14                      | GND                   | I   | Negative power supply pin         |

| 1                       | NC                    |     | No connection                     |

### **Absolute Maximum Ratings\***

| VDD to GND                                      | 0.3V to +7.0V                 |

|-------------------------------------------------|-------------------------------|

| IN, IN/OUT Voltage to GND, V <sub>T</sub>       | 0.3V to V <sub>CC</sub> +0.5V |

| Operating Temperature, Topr                     | 40°C to +85°C                 |

| Storage Temperature (Plastic), T <sub>stg</sub> | 55°C to +125°C                |

| Temperature Under Bias, T <sub>bias</sub>       | 10°C to +85°C                 |

| Power Dissipation, P <sub>T</sub>               | 1.0W                          |

<sup>\*</sup> Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C. Characteristics**

(VDD=5V±10%, GND=0V, Ta=-40°C to 85°C)

| Symbol             | Parameter           |                                                                                                                                                                                                                                                       | Min. | Тур.* | Max. | Unit |

|--------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| $ m V_{DD}$        | Operating Voltage   | _                                                                                                                                                                                                                                                     | 4.5  | 5.0   | 5.5  | V    |

| $ m I_{DD1}$       | Operating Current   | T <sub>CYC</sub> =Min. Cycle,<br>I <sub>OUT</sub> =0mA                                                                                                                                                                                                | _    | _     | 45   | mA   |

| $ m I_{DD2}$       |                     | T <sub>CYC</sub> =1µs, I <sub>OUT</sub> =0mA                                                                                                                                                                                                          | _    | _     | 15   | mA   |

| $I_{\mathrm{SB1}}$ |                     | $\overline{\mathrm{CS1}}$ =V $_{\mathrm{IH}}$ or $\mathrm{CS2}$ =V $_{\mathrm{IL}}$                                                                                                                                                                   | _    | _     | 10   | mA   |

| $ m I_{SB2}$       | Standby Current     | $\label{eq:csi} \begin{split} \overline{\mathrm{CS1}} = & \mathrm{CS2} {>} = & \mathrm{V_{DD}} {-}0.2\mathrm{V}, \\ & \mathrm{V_{IN}} {>} = & \mathrm{V_{DD}} {-}0.2\mathrm{V} \\ & \mathrm{or} \; \mathrm{V_{IN}} {<} = & 0.2\mathrm{V} \end{split}$ | _    | _     | 50   | μА   |

| $V_{\mathrm{OH}}$  | Output High Voltage | I <sub>OH</sub> =-1.0mA                                                                                                                                                                                                                               | 2.4  | _     | _    | V    |

| $ m V_{OL}$        | Output Low Voltage  | I <sub>OL</sub> =4mA                                                                                                                                                                                                                                  | _    | _     | 0.4  | V    |

| Symbol            | Parameter              |                                                                                                                                                                                                                                                                                                                | Min. | Тур.* | Max.                 | Unit |

|-------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------|------|

| $V_{\mathrm{IH}}$ | Input High Voltage     | _                                                                                                                                                                                                                                                                                                              | 2.2  | _     | V <sub>DD</sub> +0.3 | V    |

| $ m V_{IL}$       | Input Low Voltage      | _                                                                                                                                                                                                                                                                                                              | -0.3 | _     | 0.8                  | V    |

| $I_{ m LI}$       | Input Leakage Current  | $ m V_{DD}$ =5.5V, $ m V_{IN}$ =GND to $ m V_{DD}$                                                                                                                                                                                                                                                             | _    | _     | 1                    | μА   |

| $ m I_{LO}$       | Output Leakage Current | $ \begin{array}{c} \overline{\mathrm{CS1}}\text{=}\mathrm{V}_{\mathrm{IH}} \text{ or } \mathrm{CS2}\text{=}\mathrm{V}_{\mathrm{IL}} \\ \text{ or } \overline{\mathrm{OE}}\text{=}\mathrm{V}_{\mathrm{IH}}, \\ \mathrm{V}_{\mathrm{OUT}}\text{=}\mathrm{GND} \text{ to } \mathrm{V}_{\mathrm{DD}} \end{array} $ | _    | _     | 1                    | μА   |

$<sup>*</sup>V_{DD}=5V$ , Ta=25°C

### A.C. Characteristics

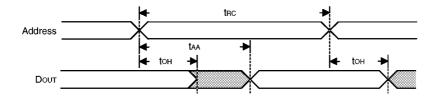

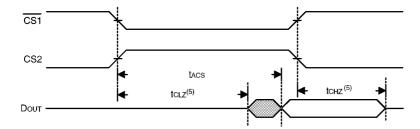

### Read cycle

(VDD=5V $\pm$ 10%, Ta=-40°C to 85°C)

| Symbol                              | Parameter                            | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------|------|------|------|------|

| $\mathbf{t}_{\mathrm{RC}}$          | Read Cycle Time                      | 70   | _    | _    | ns   |

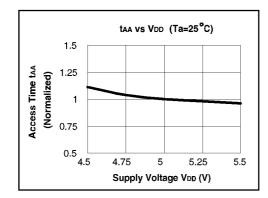

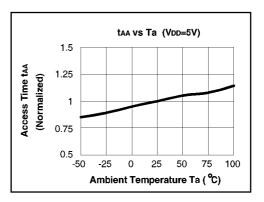

| $\mathbf{t}_{\mathbf{A}\mathbf{A}}$ | Address Access Time                  | _    | _    | 70   | ns   |

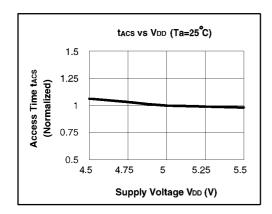

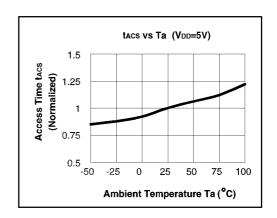

| $ m t_{ACS}$                        | Chip Selection Access Time           | _    | _    | 70   | ns   |

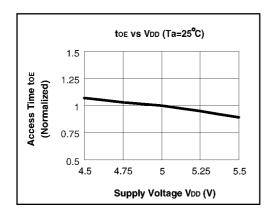

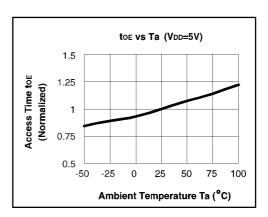

| toE                                 | Output Enabled to Outputs Valid      | _    | _    | 40   | ns   |

| $t_{ m OH}$                         | Outputs Hold from Address Change     | 5    | _    | _    | ns   |

| $\mathbf{t}_{\mathrm{CLZ}}$         | Chip select to Outputs in Low-Z      | 10   | _    | _    | ns   |

| tolz                                | Output Enabled to Outputs in Low-Z   | 10   | _    | _    | ns   |

| ${ m t_{CHZ}}$                      | Chip Disabled to Outputs in High-Z   | 0    | _    | 30   | ns   |

| $ m t_{OHZ}$                        | Output Disabled to Outputs in High-Z | 0    | _    | 30   | ns   |

Notes: 1. A read occurs during the overlap of a low  $\overline{CS1}$ , a high CS2, a low  $\overline{OE}$ , and a high  $\overline{WE}$ .

- 2.  $t_{CLZ}$  is specified from  $\overline{CS1}$  or  $\overline{CS2}$  whichever occurs last.

- 3.  $t_{CHZ}$  is specified from  $\overline{CS1}$  or CS2 whichever occurs first.

- $4.\ t_{\rm CHZ}$  and  $t_{\rm OHZ}$  are specified by the time when DATA OUT is floating

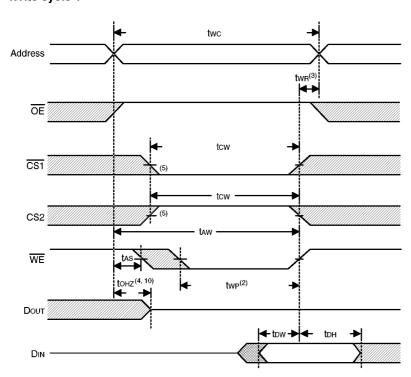

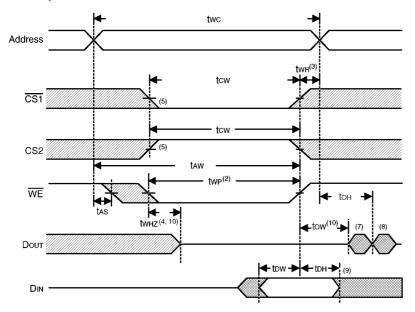

#### Write cycle

$(V_{DD}=5V\pm10\%, Ta=-40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbol                     | Parameter                            | Min. | Тур. | Max. | Unit |

|----------------------------|--------------------------------------|------|------|------|------|

| $\mathbf{t}_{\mathbf{WC}}$ | Write Cycle Time                     | 70   | _    |      | ns   |

| $\mathbf{t}_{\mathrm{CW}}$ | Chip Select to End of Write          | 35   | _    | _    | ns   |

| ${ m t}_{ m AW}$           | Address Valid to End of Write        | 50   | _    | _    | ns   |

| ${ m t_{AS}}$              | Address Setup Time                   | 0    | _    | _    | ns   |

| $\mathbf{t_{WP}}$          | Write Pulse Width                    | 25   | _    | _    | ns   |

| $t_{ m WR}$                | Write Recovery Time                  | 0    | _    | _    | ns   |

| $\mathbf{t}_{\mathrm{DW}}$ | Data to Write Time Overlap           | 20   | _    | _    | ns   |

| $\mathbf{t}_{\mathrm{DH}}$ | Data Hold from Write Time            | 0    | _    | _    | ns   |

| tow                        | Outputs Active from End of Write     | 5    | _    | _    | ns   |

| ${ m t}_{ m OHZ}$          | Outputs Disable to Outputs in High-Z | 0    | _    | 40   | ns   |

| ${ m t_{WHZ}}$             | Write to Outputs in High-Z           | 0    | _    | 50   | ns   |

Notes: 1. A write cycle occurs during the overlap of a low  $\overline{\text{CS1}}$ , a high CS2, and a low  $\overline{\text{WE}}$ .

- 2. OE may be both high and low in a write cycle.

- 3.  $t_{AS}$  is specified from  $\overline{CS1}$ , CS2, or  $\overline{WE}$ , whichever occurs last.

- 4. twp is an overlap time of a low  $\overline{\text{CS1}}$ , a high CS2, and a low  $\overline{\text{WE}}$ .

- 5.  $t_{WR}$ ,  $t_{DW}$  and  $t_{DH}$  is specified from  $\overline{CS1}$ ,  $\overline{CS2}$ , or  $\overline{WE}$ , whichever occurs first.

- 6. twhz is specified by the time when DATA OUT is floating, not defined by output level.

- 7. When I/O pins are data output mode, don't force inverse signals to those pins.

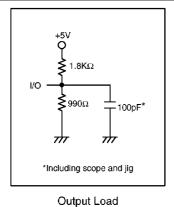

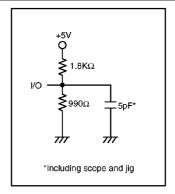

### A.C. Test Conditions

| Item                                     | Condition         |  |  |

|------------------------------------------|-------------------|--|--|

| Input Pluse Levels                       | 0V to 3.0V        |  |  |

| Input Rise and Fall Time                 | 5ns               |  |  |

| Input and Output Timing Reference Levels | 1.5V              |  |  |

| Output Load                              | See Figures below |  |  |

Output Load for tclz, tolz, tchz, tohz, twhz and tow

## **Operation Truth Table**

All relations between  $\overline{WE}, \overline{OE}, \overline{CS1}$  and CS2 can be described as the following truth table

| $\overline{\text{CS1}}$ | CS2     | ŌE     | WE     | Mode    | D0~D7  |

|-------------------------|---------|--------|--------|---------|--------|

| H<br>X                  | X*<br>L | X<br>X | X<br>X | Standby | High-Z |

| L                       | Н       | L      | Н      | Read    | Dout   |

| L                       | Н       | Н      | Н      | Read    | High-Z |

| L                       | Н       | X      | L      | Write   | Din    |

<sup>\*</sup>X: Don't Care, Logical High or Low

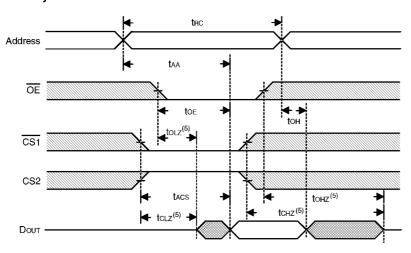

### **Timing Diagrams**

## Read cycle 1<sup>(1)</sup>

# Read cycle 2<sup>(1, 2, 4)</sup>

5

# Read cycle 3<sup>(1, 3, 4)</sup>

Notes: 1.  $\overline{\text{WE}}$  is High for Read Cycle

- 2. Device is continuously enabled,  $\overline{CS1}\text{=}V_{\mathrm{IL}}$  & CS2=V\_{\mathrm{IH}}

- 3. Address valid prior to or coincident with  $\overline{\text{CS1}}$  transition low & CS2 transition high

6

- 4.  $\overline{OE} = V_{IL}$

- 5. Transition is measured  $\pm\,500mV$  from steady state

### Write cycle 1<sup>(1)</sup>

## Write cycle 2<sup>(1, 6)</sup>

Notes: 1. WE must be high during all address transitions

- 2. A write occurs during the overlap (twp) of a low  $\overline{CS1}$ , a high CS2 and a low  $\overline{WE}$

- 3.  $t_{WR}$  is measured from the earlier of  $\overline{CS1}$  or  $\overline{WE}$  going high and CS2 going low to the end of write cycle

- 4. During this period, I/O pins are in the output state so the input signals of oppsite phase to the outputs must not be applied

- 5. If the  $\overline{\text{CS1}}$  low transition (or  $\overline{\text{CS2}}$  high transition) occurs simultaneously with the  $\overline{\text{WE}}$  low transitions or after the  $\overline{\text{WE}}$  transition, outputs remain in a high impedance state

- 6.  $\overline{OE}$  is continuously low ( $\overline{OE}$ =V<sub>IL</sub>)

- 7. DOUT is the same phase of write data of this write cycle

- 8. Dour is the read data of next address

- 9. If  $\overline{\text{CS1}}$  is low (or CS2 is high) during this period, I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them

- 10. Transition is measured  $\pm 500 \text{mV}$  from steady state

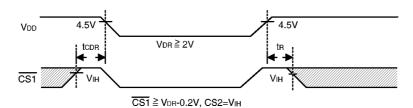

### **Data Rentention Characteristics**

(Ta=-40°C to 85°C)

| Symbol                      | Parameter                        | Conditions                                                                                                                                                          | Min.                | Max. | Unit |

|-----------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|

| $ m V_{DR}$                 | $ m V_{DD}$ for Data Retention   | $\overline{\mathrm{CS1}} = \mathrm{CS2} \geq \mathrm{V_{DD}} = 0.2\mathrm{V}$                                                                                       | 2                   | 5.5  | V    |

| $I_{CCDR}$                  | Data Retention Current           | $\begin{array}{l} V_{DD}\text{=-}3V\text{, }\overline{CS1}\text{=-}CS2\text{\ge}V_{DD}0.2V\\ V_{IN}\text{\ge}V_{DD}0.2V\text{ or }V_{IN}\text{\le}0.2V \end{array}$ | _                   | 50   | μА   |

| $\mathbf{t}_{\mathrm{CDR}}$ | Chip Disable Data Retention Time | See Retention Timing                                                                                                                                                | 0                   | _    | ns   |

| ${ m t_R}$                  | Operation Recovery Time          | See Retention Timing                                                                                                                                                | $\mathrm{t_{RC}}^*$ | _    | ns   |

8

## **Low VDD Data Retention Timing**

$<sup>*</sup>t_{RC}$ =Read Cycle Time

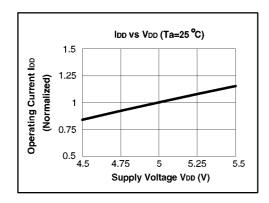

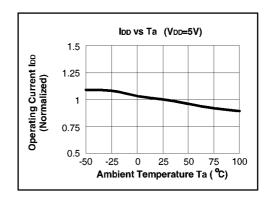

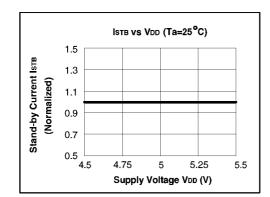

### **Characteristic Curves**

10