PI6C2504A

# Phase-Locked Loop Clock Driver with 4 Clock Outputs

#### **Product Features**

- High-Performance Phase-Locked-Loop Clock Distribution for Networking

- Registered DIMM Synchronous DRAM modules for server/workstation/PC applications

- Allows Clock Input to have Spread Spectrum modulation for EMI reduction

- Zero Input-to-Output delay

- Low jitter: Cycle-to-Cycle jitter ±75ps max.

- On-chip series damping resistor at clock output drivers for low noise and EMI reduction

- Operates at 3.3 V V<sub>CC</sub>

- Wide range of Clock Frequencies 80 to 134 MHz

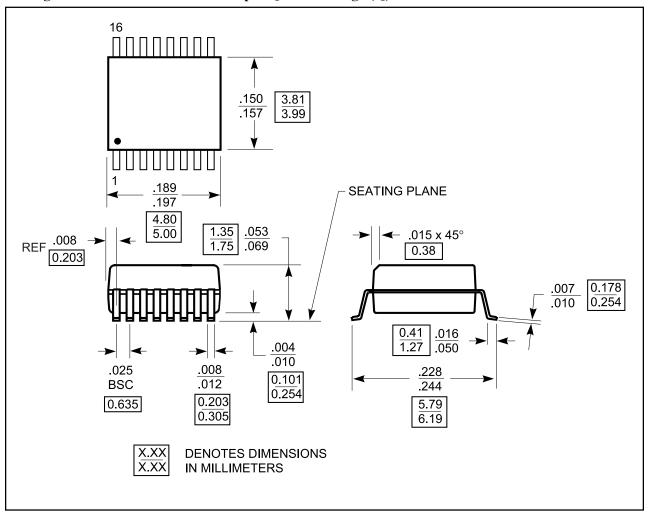

- Package: Plastic 16-pin QSOP Package (Q)

# **Product Description**

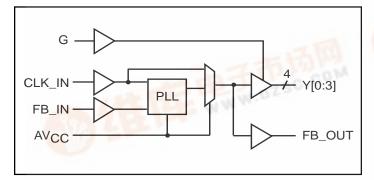

The PI6C2504A features a low-skew, low-jitter, phase-locked loop (PLL) clock driver, distributing high-frequency clock signals for SDRAM and server applications. By connecting the feedback FB OUT output to the feedback FB IN input, the propagation delay from the CLK IN input to any clock output will be nearly zero.

### Logic Block Diagram

### **Functional Table**

| Inputs | Ot     | ıtputs |

|--------|--------|--------|

| G      | Y[0:3] | FB_OUT |

| L      | L      | CLK_IN |

| Н      | CLK_IN | CLK_IN |

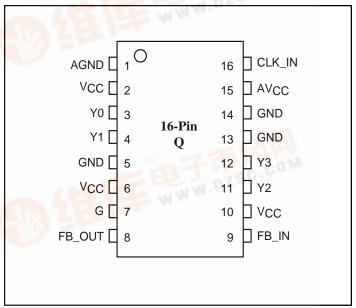

# **Product Pin Configuration**

#### **Pin Functions**

| Pin Name         | Pin No.   | Type   | Description                                                                                                                                                                                        |

|------------------|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_IN           | 16        | I      | Reference Clock input. CLK_IN allows spread spectrum clock input.                                                                                                                                  |

| FB_IN            | 9         | I      | Feedback input. FB_IN provides the feedback signal to the internal PLL.                                                                                                                            |

| G                | 7         | I      | Output bank enable. When G is LOW, outputs Y[0:3] are disabled to a logic low state.                                                                                                               |

| FB_OUT           | 8         | О      | Feedback output. FB_OUT is dedicated for external feedback. FB_OUT has an embedded series-damping resistor of the same value as the clock outputs Yx.                                              |

| Y[0:3]           | 3,4,11,12 | О      | Clock outputs. These outputs provide low-skew copies of CLK_IN Each output has an embedded series-damping resistor.                                                                                |

| AV <sub>CC</sub> | 15        | Power  | Analog power supply. For test purposes, $AV_{CC}$ can be also used to bypass the PLL. When $AV_{CC}$ is strapped to ground, PLL is bypassed and CLK_IN is buffered directly to the device outputs. |

| AGND             | 1         | Ground | Analog ground. AGND provides the ground reference for the analog circuitry.                                                                                                                        |

| V <sub>CC</sub>  | 2, 6, 10  | Power  | Power supply.                                                                                                                                                                                      |

| GND              | 5, 13, 14 | Ground | Ground                                                                                                                                                                                             |

# **DC Specifications** (Absolute maximum ratings over operating free-air temperature range)

| Symbol            | Parameter                                                     | Min. | Max.                 | Units |

|-------------------|---------------------------------------------------------------|------|----------------------|-------|

| VI                | Input voltage range                                           |      | V = = +0.5           |       |

| Vo                | Output voltage range                                          | -0.5 | V <sub>CC</sub> +0.5 | V     |

| V <sub>I_DC</sub> | DC input voltage                                              |      | 3.8                  |       |

| I <sub>O_DC</sub> | DC output current                                             |      | 100                  | mA    |

| Power             | Maximum power dissipation at $T_A = 55^{\circ}C$ in still air |      | 1.0                  | W     |

| $T_{STG}$         | Storage temperature                                           | -65  | 150                  | °C    |

#### Note:

Stress beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

| Parameter        | Test Conditions                                        | $V_{CC}$ | Min. | Тур. | Max. | Units |

|------------------|--------------------------------------------------------|----------|------|------|------|-------|

| $I_{CC}$         | $V_I = V_{CC}$ or GND; $I_O = 0^{(1)}$ Standby Current | 3.6V     |      |      | 10   | μΑ    |

| $C_{\mathrm{I}}$ | $V_{I} = V_{CC}$ or GND                                | 3.3V     |      | 4    |      | »E    |

| $C_{O}$          | V <sub>O</sub> =V <sub>CC</sub> or GND                 | 3.3 V    |      | 6    |      | pF    |

#### Note:

1. Continuous Output Current

# **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min. | Max.            | Units |

|-----------------|--------------------------------|------|-----------------|-------|

| $V_{CC}$        | Supply voltage                 | 3.0  | 3.6             |       |

| V <sub>IH</sub> | High level input voltage       | 2.0  |                 | V     |

| V <sub>IL</sub> | Low level input voltage        |      | 0.8             | V     |

| V <sub>I</sub>  | Input voltage                  | 0    | V <sub>CC</sub> |       |

| T <sub>A</sub>  | Operating free-air temperature | 0    | 70              | °C    |

# **Electrical Characteristics** (Over Recommended Operating Free-Air Temperature Range

Pull Up/Down Currents of PI6C2504A, V<sub>CC</sub>=3.0V)

| Symbol          | Parameter         | Condition    | Min. | Max.  | Units |

|-----------------|-------------------|--------------|------|-------|-------|

| I               | Pull-up current   | Vout = 2.4V  |      | -13.6 |       |

| I <sub>OH</sub> | Pull-up current   | Vout = 2.0V  |      | -22   |       |

| $ m I_{OL}$     | Pull-down current | Vout = 0.8V  | 19   |       | mA    |

|                 | Pull-down current | Vout = 0.55V | 13   |       |       |

### **AC** Specifications

(Timing requirements over recommended ranges of supply voltage and operating free-air temperature)

| Symbol           | Parameter                         | Min. | Max. | Units |

|------------------|-----------------------------------|------|------|-------|

| F <sub>CLK</sub> | Clock frequency PI6C2504A         | 80   | 134  | MHz   |

| $D_{CYI}$        | Input clock duty cycle            | 40   | 60   | %     |

|                  | Stabilization Time after power up |      | 1    | ms    |

# **Switching Characteristics**

(Over recommended ranges of supply voltage and operating free-air temperature, CL = 30pF)

| Parameter                   | Evom (Innut)            | To (Output) | $V_{CC} = 3.3V \pm 0.3V, 0-70^{\circ}C$ |      |      | Units |

|-----------------------------|-------------------------|-------------|-----------------------------------------|------|------|-------|

| rarameter                   | From (Input)            | 10 (Ծաւբաւ) | Min.                                    | Тур. | Max. | Units |

| tphase error without jitter | CLK_IN↑ at 100 & 66 MHz | FB_IN↑      | -150                                    |      | +150 | , ps  |

| Jitter, cycle-to-cycle      | At 100 & 66 MHz         |             | -75                                     |      | +75  | рз    |

| Duty cycle                  |                         | CLK OUT     | 45                                      |      | 55   | %     |

| tr, rise-time, 0.4V to 2.0V |                         | CLK_OUT     |                                         | 1.0  |      | ma    |

| tf, fall-time, 2.0V to 0.4V |                         |             |                                         | 1.1  |      | ns    |

### Note:

These switching parameters are guaranteed by design.

### Package Mechanical Information: 16-pin QSOP Package (Q).

# **Ordering Information**

| Ordering Code | Package Name | Package Type | Operating Range |

|---------------|--------------|--------------|-----------------|

| PI6C2504AQ    | Q16          | 16-pin QSOP  | Commercial      |