Data Sheet November 3, 2004 FN9193.0

# Triple Output, Low-Noise LDO Regulator with Integrated Reset Circuit

The ISL6416 is an ultra low noise triple output LDO regulator with microprocessor reset circuit and is optimized for powering wireless chip sets. The IC accepts an input voltage range of 3.0V to 3.6V and provides three regulated output voltages: 1.8V (LDO1), 2.8V (LDO2), and another ultra-clean 2.8V (LDO3). On chip logic provides sequencing between LDO1 and LDO2 for the BBP/MAC and the I/O supply voltage outputs. LDO3 features ultra low noise that does not exceed  $30\mu V_{RMS}$  (typical) to aid VCO stability. High integration makes the ISL6416 an ideal choice to power many of today's small form factor industry standard wireless cards such as PCMCIA, mini-PCI and Cardbus-32.

The ISL6416 uses an internal PMOS transistor as the pass device. The ISL6416 also integrates a reset function, which eliminates the need for the additional reset IC required in WLAN applications. The IC asserts a RESET signal whenever the VIN supply voltage drops below a preset threshold, keeping it asserted for at least 25ms after Vin has risen above the reset threshold. FAULT indicates the loss of regulation on LDO1.

### Ordering Information

| PART NUMBER         | TEMP.<br>RANGE (°C) | PACKAGE                 | PKG.<br>DWG. # |

|---------------------|---------------------|-------------------------|----------------|

| ISL6416IA           | -40 to +85          | 16 Ld QSOP              | M16.15A        |

| ISL6416IAZ (Note 1) | -40 to +85          | 16 Ld QSOP<br>(Pb-free) | M16.15A        |

#### NOTES:

- Tape and Reel available. Add "-T" suffix for Tape and Reel Packing Option.

- Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C.

#### Features

- · Three LDOs and a RESET circuit

- · Low Output Voltage Noise

- <30µV<sub>RMS</sub> (typical) for LDO3 (VCO Supply)

- · Stable with Small Ceramic Output Capacitors

- Extensive Protection and Monitoring Features

- Overcurrent protection

- Short circuit protection

- Thermal shutdown

- FAULT indicator

- Logic-Controlled Shutdown Pin

- · Integrated Microprocessor Reset Circuit

- Programmable Reset Delay

- Proven Reference Design for a Total WLAN System Solution

- Pb-Free Available (RoHS Compliant)

## **Applications**

- WLAN Cards

- PCMCIA, Cardbus32, MiniPCI Cards

- Compact Flash Cards

- · Hand-Held Instruments

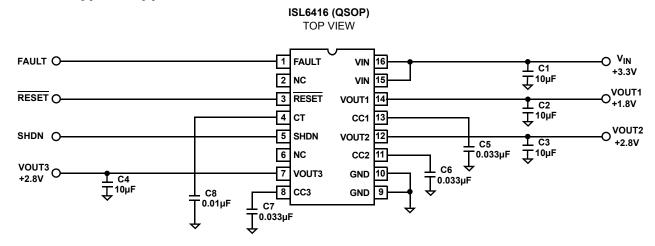

# Pinout and Typical Application Schematic

# Typical Bill Of Materials

| REFERENCE<br>DESIGNATOR | VALUE        | PACKAGE | MANUFACTURER | MANUFACTURER'S PART NUMBER |

|-------------------------|--------------|---------|--------------|----------------------------|

| C1, C2, C3, C4          | 10μF, X7R    | 1206    | TDK          | C3216X7R1A106M             |

| C5, C6, C7              | 0.033μF, X7R | 0603    | TDK/ANY      | C1608X7R1A333K             |

| C8                      | 0.01µF, X7R  | 0603    | TDK/ANY      | C1608X7R1A103K             |

| U1                      | ISL6416IA    | QSOP16  | Intersil     | ISL6416IA                  |

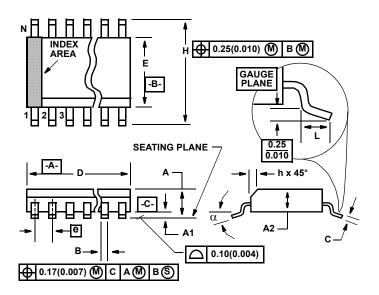

## Shrink Small Outline Plastic Packages (SSOP) Quarter Size Outline Plastic Packages (QSOP)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm (0.004 inch) total in excess of "B" dimension at maximum material condition.

- Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

M16.15A

16 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE

(0.150" WIDE BODY)

|        | INCHES    |        | MILLIMETERS |       |       |

|--------|-----------|--------|-------------|-------|-------|

| SYMBOL | MIN       | MAX    | MIN         | MAX   | NOTES |

| Α      | 0.061     | 0.068  | 1.55        | 1.73  | -     |

| A1     | 0.004     | 0.0098 | 0.102       | 0.249 | -     |

| A2     | 0.055     | 0.061  | 1.40        | 1.55  | -     |

| В      | 0.008     | 0.012  | 0.20        | 0.31  | 9     |

| С      | 0.0075    | 0.0098 | 0.191       | 0.249 | -     |

| D      | 0.189     | 0.196  | 4.80        | 4.98  | 3     |

| Е      | 0.150     | 0.157  | 3.81        | 3.99  | 4     |

| е      | 0.025 BSC |        | 0.635 BSC   |       | -     |

| Н      | 0.230     | 0.244  | 5.84        | 6.20  | -     |

| h      | 0.010     | 0.016  | 0.25        | 0.41  | 5     |

| L      | 0.016     | 0.035  | 0.41        | 0.89  | 6     |

| N      | 16        |        | 16          |       | 7     |

| α      | 0°        | 8°     | 0°          | 8°    | -     |

Rev. 2 6/04

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com