# ICE 1QS01

Controller for Quasiresonant Switch Mode Power Supplies Supporting Low Power Standby and Power Factor Correction

Power Management & Supply

| ICE1QS01<br>Revision<br>History: Current<br>Version: 2004-<br>04-27 |                                 |                                                                            |

|---------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------|

| Previous<br>Version: 2003-<br>11-28                                 |                                 |                                                                            |

| Page13 (in previous version)                                        | Page 13 (in current version)    | Diagram mains undervoltage lockout curent added                            |

| Page 16-18 (in previous version)                                    | Page 16-18 (in current version) | Min max values added, typ. values adapted, according to measuring results. |

| Page 20 (in previous version)                                       | Page 20 (in current version)    | Application circuit changed to new 250 W demo board with PFC current pump. |

#### Edition 2004-04-27

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München © Infineon Technologies AG 2004. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons

# Controller for Switch Mode Power Supplies Supporting Low Power Standby and Power Factor Correction (PFC)

#### **Features**

- · Quasiresonant Operation

- · Primary and Secondary Regulation

- · Primary Current Simulation

- Standby Input Power < 1 W

- · Low Power Consumption

- · Very Low Start-up Current

- · Soft-Start for noiseless Start-up

- Standby Burst Mode with and without Control Signal for lowered Output Voltages

- · Digital Frequency Reduction in small Steps at Decreasing Load

- · Over- and Undervoltage Lockout

- · Switch Off at Mains Undervoltage

- · Mains Voltage Dependent Fold Back Point Correction

- Ringing Suppression Time Controlled from Output Voltage

- Free usable Fault Comparator

# **Functional Description**

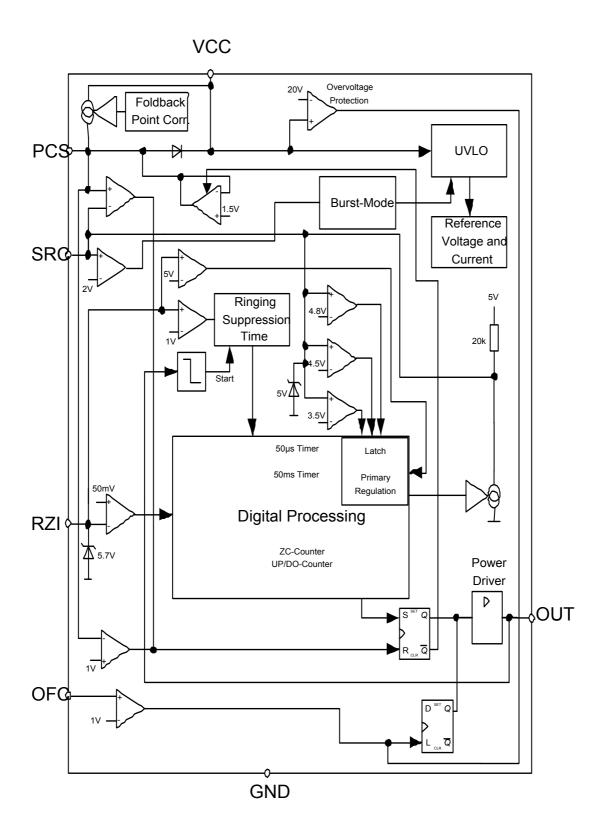

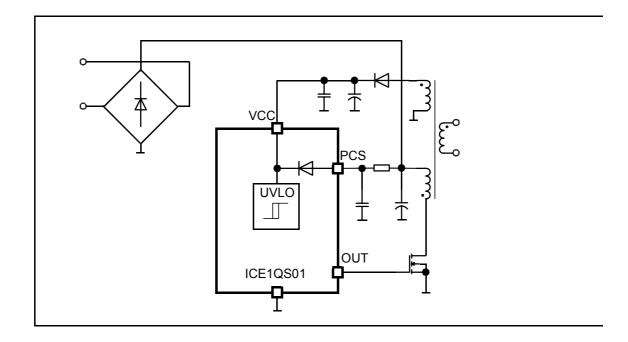

The ICE1QS01 is optimized to control free running flyback converters with and without Power Factor Correction (with PFC Charge Pump).

The switching frequency is reduced in small steps with decreasing load towards a minimum of 20 kHz in standby mode. This function is performed by a digital circuit to avoid any jitter also with periodically pulsed loads. To provide extremely low power consumption at light loads, this device can be switched into Standby Burst Mode. This is also possible without standby control signal (for adapter application).

Additionally, the start up current is very low. To avoid switching stresses of the power devices, the power transistor is always switched on at minimum voltage. The device has several protection functions:  $V_{\rm CC}$  overand undervoltage, mains undervoltage and current limiting. Regulation can be done by using the internal error amplifier or an opto coupler feedback. The output driver is ideally suited for driving a power MOSFET.

The ICE1QS01 is suited for TV-sets, DVD- sets, SAT- receivers and other consumer applications in the power range from 0 to app. 300 W.

| Туре      | Ordering Code | Package |

|-----------|---------------|---------|

| ICE1QS01  | Q67040-S4558  | P-DIP-8 |

| ICE1QS01G | Q67040-S4559  | P-DSO-8 |

| Version 1.4 | 3 | 27 Apr 2004 |

|-------------|---|-------------|

# **Block Diagram**

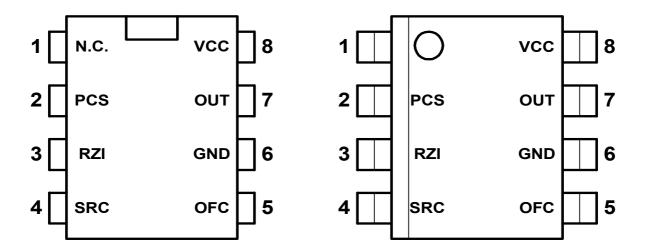

# **Pinning**

| Pin | Symbol | Function                            |

|-----|--------|-------------------------------------|

| 1   | N.C.   |                                     |

| 2   | PCS    | Primary Current Simulation          |

| 3   | RZI    | Regulation and Zero Crossing Input  |

| 4   | SRC    | Soft-Start and Regulation Capacitor |

| 5   | OFC    | Overvoltage Fault Comparator        |

| 6   | GND    | Ground                              |

| 7   | OUT    | Output                              |

| 8   | VCC    | Supply Voltage                      |

# Pin Configuration (top view)

# **Functional Description**

## Start up

An internal start up diode is connected between pin PCS and pin  $V_{CC}$ . Start up current is provided via this diode if  $V_{PCS}$  is higher than  $V_{CC}$  +  $V_{BE}$  ( $V_{BE}$  = Base-Emitter-Voltage).

During start up the internal reference of the IC is shut off and current consumption is about 60  $\mu$ A. There is only the start up circuitry working which determines the V<sub>CCon</sub> threshold. Gate driver OUT is switched to low. An active shut down circuitry ensures that OUT is held below the MOS gate threshold when the IC is in start up mode.

#### **Block Diagram: Start Up**

#### Soft start

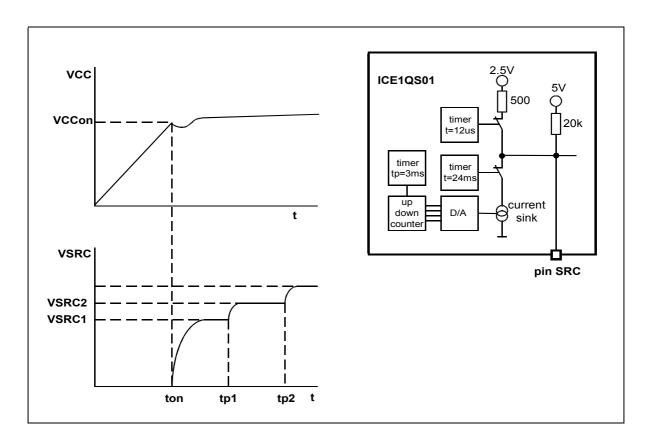

The internal reference of the IC is switched on when  $V_{CC}$  exceeds the  $V_{CCon}$  threshold. The IC begins to work with soft start mode. Soft start is realized with an internal soft start resistor, an internal current sink, a current source and the external feedback capacitor connected at pin SRC. The internal resistor is connected between the internal voltage reference and pin SRC. The current sink is connected between pin SRC and GND. The value of the current is set with a timer. Immediately after the IC is switched on the capacitor  $C_{SRC}$  is charged with a current source up to 2.5V. This current source is switched off 12 µsec after beginning of soft start. The current value of the current sink is set with a timer. Every three msec the current of the current sink is reduced and so  $V_{SRC}$  can increase stepwise. The soft start is finished 24 msec after the IC is switched on. At the end of the soft start the current sink is switched off.

Figure: Soft Start

#### **PCS** (primary current simulation)

A voltage proportional to the current of the power transistor is generated at Pin PCS by the RC-combination R2, C2. The voltage at Pin PCS is forced to 1.5V when the power transistor is switched off and during its switch on time C2 is charged by R2 from the rectified mains. The relation of V<sub>PCS</sub> and

| Version 1.4 | 7 | 27 Apr 2004 |

|-------------|---|-------------|

the current in the power transistor (Iprimary) is:

$$VPCS = 1,5V + \frac{Lprimary \times Iprimary}{R2 \times C2}$$

Lprimary: Primary inductance of the transformer

The advantage of primary current simulation is the elimination of the leading edge spike, which is generated when the power transistor is switched on.

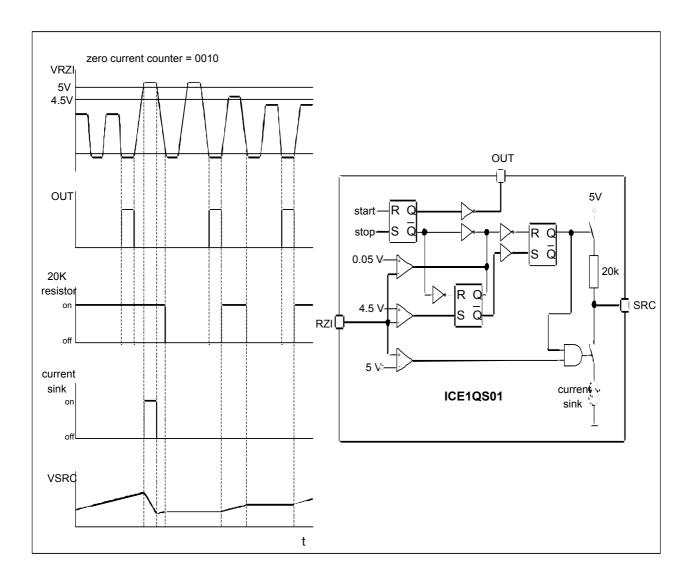

## RZI (zero crossing input and primary regulation)

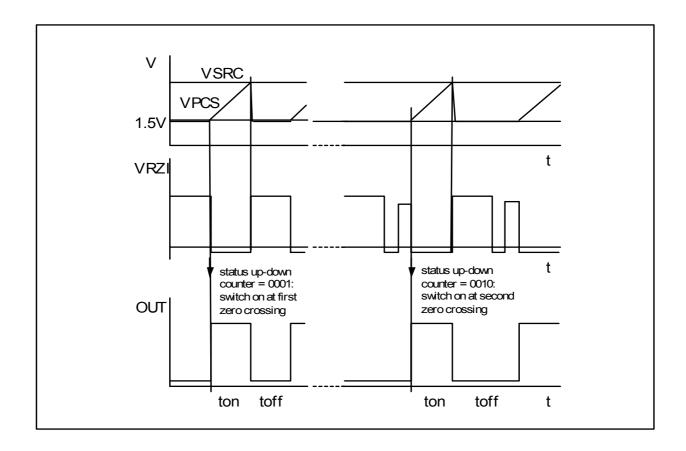

#### Zero current counter

Every time when the falling voltage ramp of  $V_{RZI}$  crosses the 50 mV threshold a pulse is sent to the zero-current-counter and increases the counter by one. If zero-current-counter and up-down-counter are equal the gate drive OUT is switched to high. Up-down counter is influenced via SRC voltage as described below. If  $V_{RZI}$  is greater than 50 mV gate drive OUT is always switched low.

Figure: Zero Crossing Switching Behaviour

| Version 1.4 |  | 8 |  | 27 Apr 2004 |

|-------------|--|---|--|-------------|

|-------------|--|---|--|-------------|

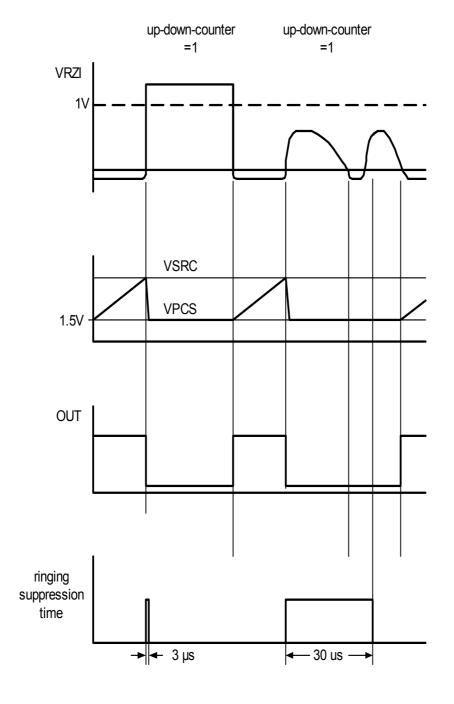

#### **Ringing suppression**

When  $V_{PCS}$  reaches the feedback voltage  $V_{SRC}$  the gate drive OUT is set to low and the ringing suppression timer is started. This timer ensures that the gate drive cannot be switched on until this ringing suppression time is passed. Duration of ringing suppression time depends on the  $V_{RZI}$  voltage. Suppression time is 3 µsec if  $V_{RZI}$  > 1V and it is 30 µsec if  $V_{RZI}$  < 1V.

**Figure: Ringing Suppression**

# **Primary regulation**

Primary regulation is achieved by activating the internal current sink. The current sink is connected between pin SRC and ground. If  $V_{RZI}$  exceeds the 5V threshold the current sink is switched on. It is switched off when  $V_{RZI}$  falls below 5V. The current sink discharges the  $C_{SRC}$  capacitor.  $C_{SRC}$  is charged via the internal 20k resistor. If  $V_{RZI}$  exceeds the 4.4V threshold a flip-flop is set and the resistor is switched off when  $V_{RZI}$  falls below 50 mV. The resistor is switched on again with the falling slope of gate drive OUT.

## **Diagram Primary Regulation**

## SRC (Regulation and soft start capacitor)

The feedback capacitor is connected to pin SRC. The feedback voltage  $V_{\mbox{\footnotesize SRC}}$  has two main functions.

Function I (MOS FET on time):  $V_{SRC}$  provides the switch off reference voltage. If  $V_{PCS}$  (which contains the primary current information) exceeds the  $V_{SRC}$  voltage the external MOS transistor is switched off.

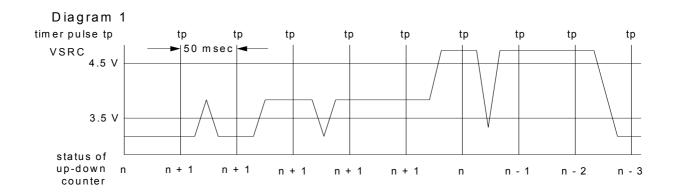

Function II (MOS FET off time for frequency reduction): At low load the frequency is reduced by ignoring zero crossing signals after the transformer demagnetization.  $V_{SRC}$  determines the action of the 4-bit up-down-counter which contains the number of zero crossings to be ignored. The content of the up-down-counter is compared with the number of zero-current crossings of  $V_{RZI}$ . If the number of zero-current crossings in each period after the transformer demagnetization is equal to the up-down-counter content the MOS is switched on. At low load conditions when  $V_{SRC}$  is below 3.5V the counter is increased by one every 50 msec. The result is that the MOS transistor off-time increases and duty cycle decreases. At high load conditions when  $V_{SRC}$  is higher than 4.4V the counter content is reduced by one every 50msec. So MOS transistor off-time will be reduced. With this off-time regulation switching jitter can be eliminated.

The up-down-counter is immediately set to 0001 if a load jump occurs and  $V_{SRC}$  exceeds 4.8 V. This ensures that full power can be provided instantaneously.

The following table shows the SRC voltage range and the corresponding up-down counter action.

| SRC voltage range                                       | up-down-counter action  |

|---------------------------------------------------------|-------------------------|

| 1: VSRC< 3.5V                                           | count forward           |

| 2: 3.5 <vsrc<4.4< td=""><td>stop count</td></vsrc<4.4<> | stop count              |

| 3: VSRC>4.4                                             | count backward          |

| 4: VSRC> 4.8                                            | set up-down-counter to1 |

The information provided by  $V_{SRC}$  is stored in two independent flip flops. An internal timer creates a trigger pulse with a period of 50 msec. Every time the pulse occures the up-down counter checks the status flip flops and acts depending on the flip flop information. After this pulse the flip flops are reset. So change of voltage range is noticed by the logic only once during the 50 ms period. In the diagram below the behaviour of the up-down counter is depicted in more detail.

| Version 1.4 |  | 11 |  | 27 Apr 2004 |

|-------------|--|----|--|-------------|

|-------------|--|----|--|-------------|

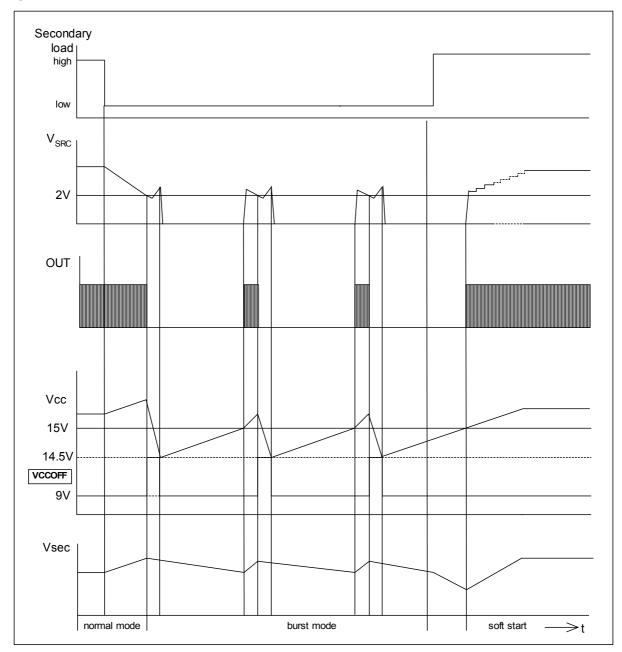

#### **Burst mode**

12 µsec after beginning of softstart the burst mode comparator is activated. If  $V_{SRC}$  falls below 2V after activating the comparator the gate drive OUT is switched to low and the  $V_{CCoff}$  threshold is changed to 14.5 V.  $V_{CC}$  decreases because gate drive is held low. If  $V_{CC}$  reaches the  $V_{CCoff}$  threshold the IC is going into start-up mode. At  $V_{CCon}$  threshold the IC is switched on again starting with soft start modus.  $V_{CCoff}$  threshold is set to the normal 9V.

**Figure: Burst Mode**

#### Restart timer

If voltage  $V_{RZI}$  is lower than 50 mV and gate drive OUT is low an internally created restart pulse will switch gate drive OUT high every 50  $\mu$ s and the minimum switching frequency is about 20 kHz.

Restart pulse is inhibited if  $V_{RZI}$  is higher than 50 mV. So the MOS transistor cannot be switched on until the transformer is discharged.

#### VCC overvoltage protection

If  $V_{CC}$  exceeds the  $V_{CCD}$  threshold a latch is set and the gate is disabled. Reset of latch occurs when  $V_{CC}$  is falling below  $V_{CCon}$ -  $V_{CCBHY}$ .

## Overvoltage fault comparator (OFC)

With an external sense resistor connected to pin OFC primary current can be sensed directly. If the sensed current exceeds the internal  $V_{OFC}$  threshold a latch is set and gate is disabled. Reset of latch occurs when  $V_{CC}$  is falling below  $V_{CCon}$ -  $V_{CCBHY}$ .

**Notice:** If this comparator is not used pin OFC has to be connected to ground.

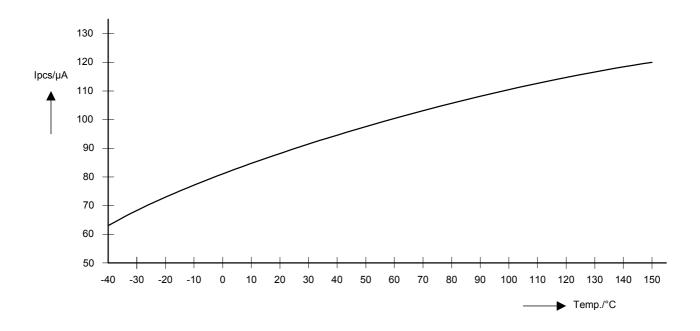

## Mains undervoltage

Power supplies must be shut down when mains voltage is below a certain limit to avoid too long ontime of MOS-FET switch, which would lead to a switching frequency in audible spheres. Mains undervoltage is sensed during the off-time of the MOS-FET switch. If the current flowing into pin PCS is smaller than 100 uA, then the output is latched and cannot be switched to high state.

#### **Diagram Mains Undervoltage Lockout Current**

| Version 1.4 |  | 13 |  | 27 Apr 2004 |

|-------------|--|----|--|-------------|

|-------------|--|----|--|-------------|

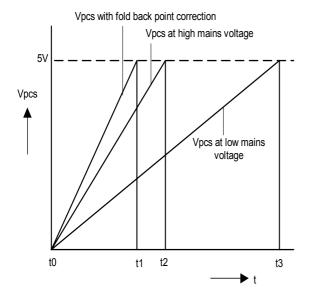

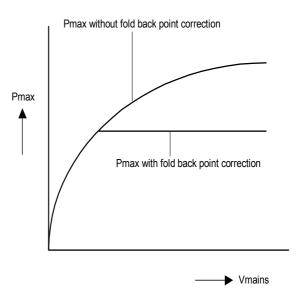

#### Fold back point correction

With increasing mains voltage the switch on time becomes shorter and so the frequency becomes higher. With higher frequency also the maximal possible output power becomes higher. With higher power the danger in case of failure increases.

To avoid this, the foldback point correction circuit senses main voltage to reduce the on-time of the switch. Mains voltage is sensed at the supply coil of  $V_{CC}$  voltage via a resistor connected to pin RZI. During on-time of the MOS-FET switch current is pulled out from pin RZI. When this current is higher than 500  $\mu$ A, one fifth of the current higher than this threshold is driven into pin PCS to increase the voltage slope charging the capacitor connected to this pin.

$$IPCSFO = \frac{IRZI - 0, 5mA}{5}, (IRZI > 500uA)$$

#### **Figure: Fold Back Point Correction**

Version 1.4 27 Apr 2004

# **Absolute Maximum Ratings**

| Parameter                              | Symbol                               | Min  | Max                | Unit     | Remark                                                                        |

|----------------------------------------|--------------------------------------|------|--------------------|----------|-------------------------------------------------------------------------------|

| Charge Current into Pin2               | I <sub>PCS</sub>                     |      | 500                | uA       | During start up                                                               |

| Voltage at Pin 2                       | V <sub>PCS</sub>                     | -0.3 | 21                 | V        |                                                                               |

| Current into Pin 3                     | I <sub>RZI</sub><br>I <sub>RZI</sub> | -10  | 10                 | mA<br>mA | V <sub>RZI</sub> >V <sub>RZICH</sub><br>V <sub>RZI</sub> <v<sub>RZICL</v<sub> |

| Voltage at Pin 4                       | V <sub>SRC</sub>                     | -0.3 | V <sub>SRCCL</sub> | V        | I <sub>SRC</sub> =100 μA                                                      |

| Voltage at Pin 5                       | V <sub>OFC</sub>                     | -0.3 | 6                  | V        |                                                                               |

| Current into Pin 7                     | I <sub>OUT</sub>                     | -500 | 500                | mA       | t<1ms                                                                         |

| Voltage at Pin 8                       | V <sub>CC</sub>                      | -0.3 | 21                 | V        |                                                                               |

|                                        |                                      |      |                    |          |                                                                               |

| ESD Protection                         |                                      |      | 4000               | V        | MIL STD 883C method 3015.6, 100pF,1500Ω                                       |

| Storage Temperature                    | T <sub>stg</sub>                     | -50  | 150                | °C       |                                                                               |

| Operating Junction Temperature         | TJ                                   | -25  | 150                | °C       |                                                                               |

| Thermal Resistance<br>Junction-Ambient | R <sub>thJA</sub>                    |      | 100                | K/W      | P-DIP-8                                                                       |

Characteristics (Unless otherwise stated, -25°C<Tj <150 °C, VCC = 16V)

| Parameter                          | Symbol              | min.      | typ.       | max.     | Unit      | Test Condition                                                                    |

|------------------------------------|---------------------|-----------|------------|----------|-----------|-----------------------------------------------------------------------------------|

| VCC start-up circuit               | 1                   |           |            |          |           | 1                                                                                 |

| Start-up supply current            | I <sub>CCL</sub>    |           | 60         | 100      | μA        | V <sub>CC</sub> =V <sub>CCon</sub> -0.5V                                          |

| Operating supply current           | I <sub>CCH</sub>    | 8         | 11         | 12.5     | mA        | Output low                                                                        |

| V <sub>CC</sub> Turn-On threshold  | V <sub>CC</sub> ON  | 14.1      | 15         | 15.5     | V         |                                                                                   |

| V <sub>CC</sub> Turn-Off threshold | V <sub>CC OFF</sub> | 8.5       | 9          | 9.5      | V         |                                                                                   |

| V <sub>CC</sub> Hysteresis         | V <sub>CCHY</sub>   | 5.4       | 6          | 6.5      | V         |                                                                                   |

| V <sub>CC</sub> Burst Hysteresis   | V <sub>CCBHY</sub>  | 0.2       | 0.4        | 0.6      | V         |                                                                                   |

| V <sub>CC</sub> Overvoltage        | V <sub>CCD</sub>    | 19        | 20         | 21       | V         |                                                                                   |

| SRC soft start mode                |                     |           |            |          |           |                                                                                   |

| Start Voltage                      | V <sub>SRC1</sub>   | 2.40      | 2.65       | 2.85     | V         | I <sub>optocoupler</sub> =0 μA                                                    |

| Digital voltage step               | V <sub>SRCST</sub>  |           | 360        |          | mV        | I <sub>optocoupler</sub> =0 μA                                                    |

| Step pulse rate                    | t <sub>SRCSTR</sub> |           | 3          |          | ms        |                                                                                   |

| Soft start time                    | t <sub>ST</sub>     | 19        | 24         | 32       | ms        |                                                                                   |

| Current source rise time           | t <sub>STRT</sub>   |           | 14         |          | μs        | V <sub>SRC</sub> =0.2V to 2.0V<br>C <sub>SRC</sub> =10nF                          |

| Current source on time             | t <sub>STOT</sub>   |           | 12         |          | μs        |                                                                                   |

| SRC normal mode                    |                     |           |            |          |           |                                                                                   |

| Source resistor                    | R <sub>SRC</sub>    | 17        | 21         | 28       | kOhm      |                                                                                   |

| Clamping threshold voltage         | V <sub>SRCCL</sub>  | 4.95      | 5.1        | 5.25     | V         | V <sub>PCS</sub> =V <sub>SRC</sub> , OUT switches to Low, I <sub>SRC</sub> =100μA |

| Reset counter to one               | V <sub>SRCR</sub>   | 4.75      | 4.9        | 5.05     | V         |                                                                                   |

| Distance clamping to reset         | V <sub>SRCH</sub>   | 150       | 200        | 250      | mV        |                                                                                   |

| Threshold downward count           | V <sub>SRCD</sub>   | 4.3       | 4.5        | 4.7      | V         |                                                                                   |

| Threshold upward count             | V <sub>SRCSU</sub>  | 3.4       | 3.5        | 3.7      | V         |                                                                                   |

| Burst mode latch threshold voltage | V <sub>SRCB</sub>   | 1.9       | 2.05       | 2.2      | V         | V <sub>SRC</sub> <v<sub>SRCB: OUT=Low</v<sub>                                     |

| Counter time 1)                    | tCOUNT              |           | 50         |          | msec      |                                                                                   |

| Sink current prim reg mode         | I <sub>SRCS</sub>   | 400       | 500        | 550      | μΑ        | V <sub>RZI</sub> > 5V                                                             |

| 1) The parameter is not sub        | iect to produc      | tion test | - verified | hv desig | n/charact | terization                                                                        |

| Version 1.4 |  | 16 |  | 27 Apr 2004 |

|-------------|--|----|--|-------------|

|-------------|--|----|--|-------------|

| Parameter                                          | Symbol             | min.      | typ.      | max.      | Unit         | Test Condition                                                                 |

|----------------------------------------------------|--------------------|-----------|-----------|-----------|--------------|--------------------------------------------------------------------------------|

| RZI (regulation and zero crossing input)           |                    |           |           |           |              |                                                                                |

| Zero crossing threshold voltage                    | V <sub>RZIT1</sub> | 25        | 50        | 80        | mV           | V <sub>RZI</sub> <v<sub>RZIT1: Out=High</v<sub>                                |

| Time delay switch on                               | t <sub>don</sub>   | 350       | 440       | 550       | nsec         |                                                                                |

| Leakage current                                    | I <sub>RZIB</sub>  | -1        | 25        | 110       | μΑ           | V <sub>RZI</sub> =5V                                                           |

| Clamping voltage low state                         | V <sub>RZICL</sub> | -0.5      | -0.3      | -0.2      | V            | I <sub>RZI</sub> = -1mA                                                        |

| Clamping voltage high state                        | V <sub>RZICH</sub> | 5.5       | 6.0       | 6.4       | V            | I <sub>RZI</sub> = 5mA                                                         |

| Primary regulation threshold for discharge current | V <sub>RZIDC</sub> | 4.95      | 5.1       | 5.25      | V            |                                                                                |

| Primary regulation threshold for charge current    | V <sub>RZICC</sub> | 4.2       | 4.4       | 4.65      | V            |                                                                                |

| Ringing suppression threshold voltage              | V <sub>RZIT2</sub> | 0.9       | 1.0       | 1.1       | V            |                                                                                |

| Ringing suppression time                           | t <sub>RZIPS</sub> | 1.5<br>20 | 2.5<br>29 | 3.2<br>37 | µsec<br>µsec | V <sub>RZI</sub> > V <sub>RZIT2</sub><br>V <sub>RZI</sub> < V <sub>RZIT2</sub> |

| Foldback point correction current threshold        | I <sub>PCSF</sub>  | 250       | 400       | 600       | μΑ           | -25°C <tj<120°c< td=""></tj<120°c<>                                            |

| PCS (primary current                               | simulation         | n)        |           |           | U.           | 1                                                                              |

| Gate enable threshold voltage                      | V <sub>PCSE</sub>  | 0.9       | 1.0       | 1.1       | V            | V <sub>PCS</sub> <v<sub>PCSE: Out=Low</v<sub>                                  |

| Basic voltage                                      | V <sub>PCSB</sub>  | 1.45      | 1.55      | 1.65      | V            | gate low                                                                       |

| Shut down delay                                    | t <sub>PCS</sub>   |           | 150       | 230       | nsec         |                                                                                |

| Mains undervoltage lock-<br>out current 2)         | I <sub>PCS</sub>   | 40        | 100       | 160       | μA           |                                                                                |

| Voltage drop startup diode                         | V <sub>PCSD</sub>  |           | 0.85      |           | V            | I <sub>PCS</sub> =300μA                                                        |

| Discharge current                                  | I <sub>PCSD</sub>  | 1.6       | 2.6       | 3.6       | mA           | V <sub>PCS</sub> =3V                                                           |

| OFC (overcurrent fault comparator)                 |                    |           |           |           |              |                                                                                |

| Bias Current                                       | I <sub>OFCB</sub>  | -1        |           |           | μΑ           |                                                                                |

| Gate drive disabled threshold voltage              | V <sub>OFC</sub>   | 0.93      | 1.0       | 1.05      | V            |                                                                                |

| Shut Down Delay                                    | t <sub>OFC</sub>   |           | 180       | 240       | ns           |                                                                                |

| See diagram mains undervolt. lockout current       |                    |           |           |           |              |                                                                                |

| Version 1.4 |  | 17 |  | 27 Apr 2004 |

|-------------|--|----|--|-------------|

|-------------|--|----|--|-------------|

| Parameter                       | Symbol           | min.       | typ.         | max.         | Unit   | Test Condition                                      |

|---------------------------------|------------------|------------|--------------|--------------|--------|-----------------------------------------------------|

| Restart Timer                   |                  |            |              |              |        |                                                     |

| Restart time                    | t <sub>RES</sub> | 33         | 42           | 55           | μs     | V <sub>RZI</sub> <25mV                              |

|                                 |                  |            |              |              |        |                                                     |

| Gate Drive                      | Gate Drive       |            |              |              |        |                                                     |

| Output voltage low              |                  |            | 0.7<br>0.8   | 1.1<br>1.4   | V<br>V | I <sub>OUT</sub> =20mA<br>I <sub>OUT</sub> =200mA   |

| Output voltage high             |                  | 9.5<br>9.5 | 10.6<br>10.5 | 11.0<br>11.0 | V<br>V | I <sub>OUT</sub> =-20mA<br>I <sub>OUT</sub> =-180mA |

| Output voltage active shut down |                  |            | 1.0          | 1.35         | V      | V <sub>CC</sub> =7V<br>I <sub>OUT</sub> =20mA       |

| Rise time                       |                  |            | 40           | 100          | ns     | C <sub>OUT</sub> =1nF                               |

| Fall time                       |                  |            | 60           | 120          | ns     | C <sub>OUT</sub> =1nF                               |

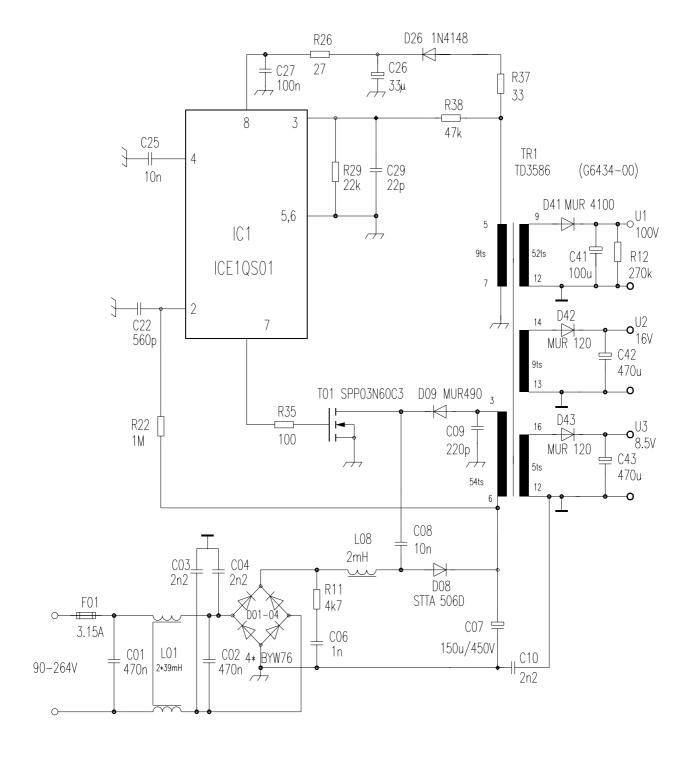

Figure: Circuit Diagram for Standard Application with PFC

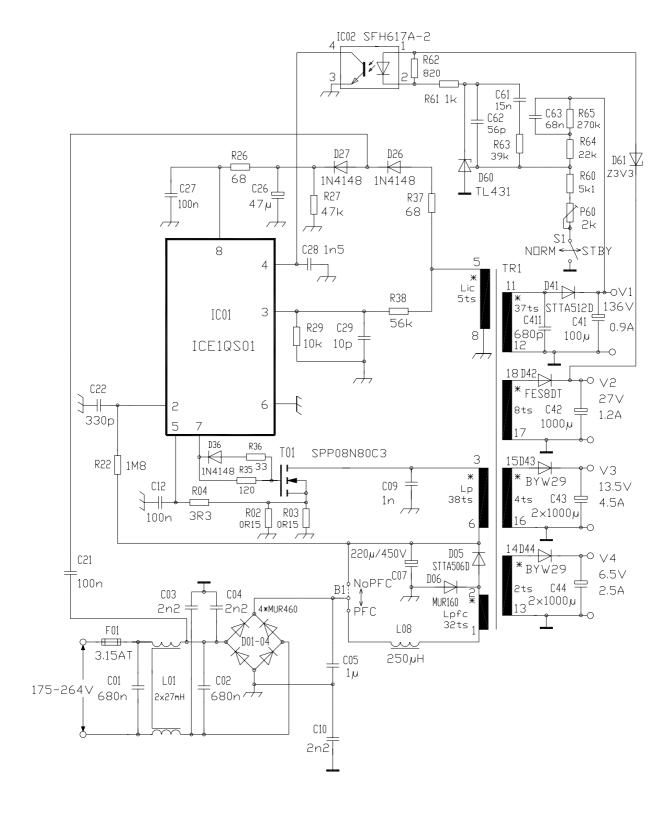

Figure: Circuit Diagram for Application with PFC and Low Voltage Standby Mode

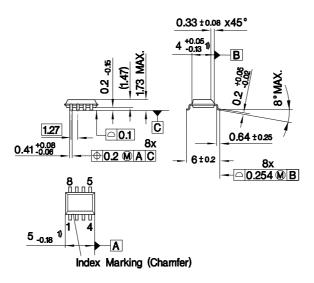

# Plastic Package, P-DSO-8-3

(Plastic Dual Small Outline Package)

1) Does not include plastic or metal protrusion of 0.15 max. per side

GPS05121

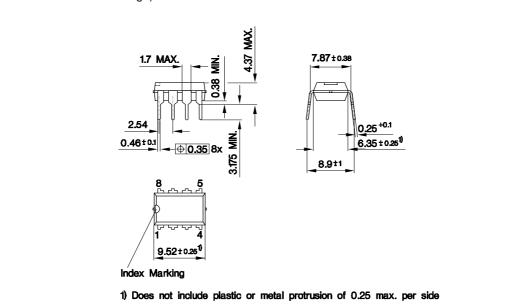

#### Plastic Package, P-DIP-8-4

(Plastic Dual In-line Package)

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm

| Version 1.4 |  | 21 |  | 27 Apr 2004 |

|-------------|--|----|--|-------------|

|-------------|--|----|--|-------------|