#### 查询THS3001供应商

# <u>捷多邦,专业PCB打样工厂,24小**町HS300**</u>1, THS3002 420-MHz HIGH-SPEED CURRENT-FEEDBACK AMPLIFIERS

SLOS217A - JULY 1998 - REVISED JUNE 1999

- High Speed

- 420 MHz Bandwidth (G = 1, –3 dB)

- 6500 V/µs Slew Rate

- 40-ns Settling Time (0.1%)

- High Output Drive, I<sub>O</sub> = 100 mA

- Excellent Video Performance

- 115 MHz Bandwidth (0.1 dB, G = 2)

- 0.01% Differential Gain

- 0.02° Differential Phase

- Low 3-mV (max) Input Offset Voltage

- Very Low Distortion

- THD = -96 dBc at f = 1 MHz

- THD = –80 dBc at f = 10 MHz

- Wide Range of Power Supplies

V<sub>CC</sub> = ±4.5 V to ±16 V

- Evaluation Module Available

#### description

The THS300x is a high-speed current-feedback operational amplifier, ideal for communication, imaging, and high-quality video applications. This device offers a very fast 6500-V/µs slew rate, a 420-MHz bandwidth, and 40-ns settling time for large-signal applications requiring excellent transient response. In addition, the THS300x operates with a very low distortion of –96 dBc, making it well suited for applications such as wireless communication basestations or ultrafast ADC or DAC buffers.

| D AND<br>(                                     | THS3001<br>DGNT PACKAO<br>TOP VIEW) |                                                       | THS3002<br>DGN PACKAGE<br>TOP VIEW) |

|------------------------------------------------|-------------------------------------|-------------------------------------------------------|-------------------------------------|

| NULL [<br>IN- [<br>IN+ [<br>V <sub>CC-</sub> [ | <b>E</b>                            | JLL 10UT<br>CC+ 1IN-<br>JT 1IN+<br>C -V <sub>CC</sub> | 4 5 21N+                            |

NC – No internal connection

<sup>†</sup>The THS3001 implemented in the DGN package is in the product preview stage of development. Contact your local TI sales office for availability.

| DEVICE     | ARCHITECTURE |     |     | SUPPLY<br>VOLTAGE |       | BW<br>(MHz) | SR<br>(V/μs) | THD<br>f = 1 MHz | t <sub>s</sub><br>0.1% | DIFF.<br>GAIN | DIFF. | V <sub>n</sub> |

|------------|--------------|-----|-----|-------------------|-------|-------------|--------------|------------------|------------------------|---------------|-------|----------------|

| - HAR      | VFB          | CFB | 5 V | ±5 V              | ±15 V | (11172)     | (ν/μ5)       | (dB)             | (ns)                   | GAIN          | FHASE | (nV/√Hz)       |

| THS3001/02 |              | •   |     | •                 | •     | 420         | 6500         | -96              | 40                     | 0.01%         | 0.02° | 1.6            |

| THS4001    | •            |     | ٠   | •                 | •     | 270         | 400          | -72              | 40                     | 0.04%         | 0.15° | 12.5           |

| THS4011/12 | •            |     |     | •                 | •     | 290         | 310          | -80              | 37                     | 0.006%        | 0.01° | 7.5            |

| THS4031/32 | •            |     |     | •                 |       | 100         | 100          | -72              | 60                     | 0.02%         | 0.03° | 1.6            |

| THS4061/62 | •            |     |     | •                 | •     | 180         | 400          | -72              | 40                     | 0.02%         | 0.02° | 14.5           |

CAUTION: The THS300x provides ESD protection circuitry. However, permanent damage can still occur if this device is subjected to high-energy electrostatic discharges. Proper ESD precautions are recommended to avoid any performance degradation or loss of functionality.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLOS217A - JULY 1998 - REVISED JUNE 1999

| AVAILABLE OPTIONS |                                     |                                                      |                |                                       |  |  |

|-------------------|-------------------------------------|------------------------------------------------------|----------------|---------------------------------------|--|--|

|                   | PA                                  | CKAGED DEVICE                                        |                |                                       |  |  |

| TA                | SOICT MSOP (DGN)                    |                                                      |                | EVALUATION<br>MODULE                  |  |  |

|                   | (D)                                 | DEVICE                                               | SYMBOL         | MODOLL                                |  |  |

| 0°C to 70°C       | THS3001CD<br>THS3002CD <sup>‡</sup> | THS3001CDGN <sup>‡</sup><br>THS3002CDGN <sup>‡</sup> | TIADP<br>TIADI | THS3001EVM<br>THS3002EVM <sup>‡</sup> |  |  |

| -40°C to 85°C     | THS3001ID<br>THS3002ID <sup>‡</sup> | THS3001IDGN <sup>‡</sup><br>THS3002IDGN <sup>‡</sup> | TIADQ<br>TIADJ | _                                     |  |  |

<sup>†</sup>The D package is available taped and reeled. Add an R suffix to the device type (i.e., THS3001CDR)

<sup>‡</sup> Product Preview

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC+</sub> to V <sub>CC-</sub>          |                                |

|---------------------------------------------------------------|--------------------------------|

| Input voltage, V <sub>1</sub>                                 |                                |

| Output Current, I <sub>O</sub>                                | 175 mÅ                         |

| Differential input voltage, V <sub>ID</sub>                   | ±6 V                           |

| Continuous total power dissipation                            | . See Dissipation Rating Table |

| Operating free-air temperature, T <sub>A</sub> , THS300xC     | 0°C to 70°C                    |

| THS300xI                                                      | –40°C to 85°C                  |

| Storage temperature, T <sub>stg</sub>                         |                                |

| Lead temperature, 1,6 mm (1/16 inch) from case for 10 seconds | 300°C                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| D       | 740 mW                | 6 mW/°C                     | 470 mW                | 380 mW                |

### recommended operating conditions

|                                                | MIN           | NOM MAX | UNIT |    |

|------------------------------------------------|---------------|---------|------|----|

| Supply voltage Vee, and Vee                    | Split supply  | ±4.5    | ±16  | V  |

| Supply voltage, $V_{CC+}$ and $V_{CC-}$        | Single supply | 9       | 32   | v  |

|                                                | THS300xC      | 0       | 70   |    |

| Operating free-air temperature, T <sub>A</sub> | THS300xI      | -40     | 85   | °C |

SLOS217A - JULY 1998 - REVISED JUNE 1999

|                | PARAMETER                      |                | TEST CONI                                                     | DITIONS <sup>†</sup>        | MIN                 | TYP   | MAX   | UNIT             |  |

|----------------|--------------------------------|----------------|---------------------------------------------------------------|-----------------------------|---------------------|-------|-------|------------------|--|

| .,             | Devention                      |                | Split supply                                                  |                             | ±4.5                |       | ±16.5 |                  |  |

| √cc            | Power supply operating ra      | nge            | Single supply                                                 |                             | 9                   |       | 33    | V                |  |

|                |                                |                |                                                               | T <sub>A</sub> = 25°C       |                     | 5.5   | 7.5   |                  |  |

|                |                                |                | $V_{CC} = \pm 5 V$                                            | T <sub>A</sub> = full range |                     |       | 8.5   | mA               |  |

| CC             | Quiescent current              |                | V <sub>CC</sub> = ±15 V                                       | $T_A = 25^{\circ}C$         |                     | 6.6   | 9     |                  |  |

|                |                                |                | $VCC = \pm 15 V$                                              | T <sub>A</sub> = full range |                     |       | 10    |                  |  |

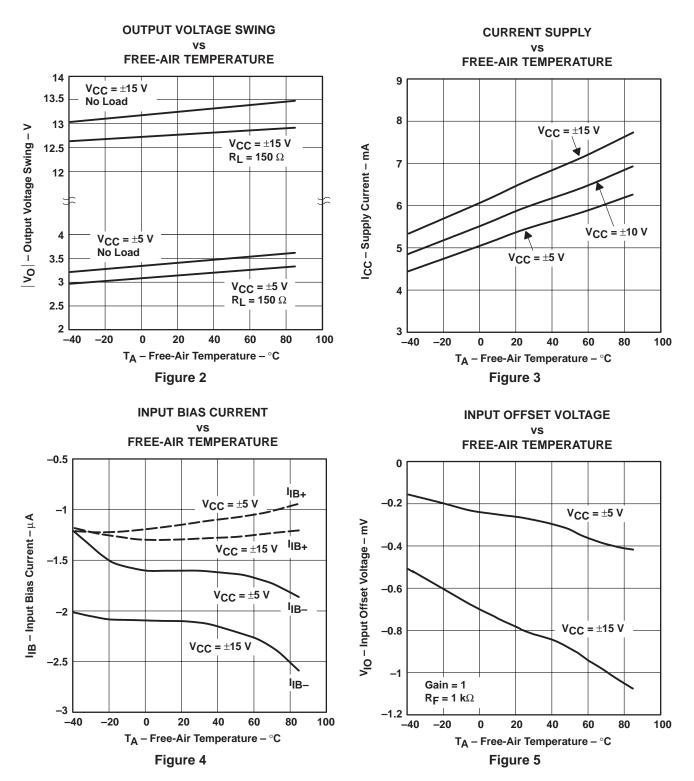

|                |                                |                | V <sub>CC</sub> = ±5 V                                        | R <sub>L</sub> = 150 Ω      | ±2.9                | ±3.2  |       |                  |  |

| 10             | Output voltage swing           |                | VCC = ±5 V                                                    | $R_L = 1 \ k\Omega$         | ±3                  | ±3.3  |       | v                |  |

| VO             | Output voltage swing           |                | V <sub>CC</sub> = ±15 V                                       | RL = 150 Ω                  | ±12.1               | ±12.8 |       | v                |  |

|                |                                |                | $VCC = \pm 15 V$                                              | $R_L = 1 \ k\Omega$         | ±12.8               | ±13.1 |       |                  |  |

| -              | Output current (see Note 1     | )              | $V_{CC} = \pm 5 V$ ,                                          | $R_L = 20 \Omega$           |                     | 100   |       | mA               |  |

| 0              | Oulput current (see Note 1     | )              | $V_{CC} = \pm 15 V,$                                          | RL = 75 Ω                   | 85                  | 120   |       | 1117             |  |

| VIO            | Input offset voltage           |                | V <sub>CC</sub> = ±5 V or ±15 V                               | $T_A = 25^{\circ}C$         |                     | 1     | 3     | 3<br>mV          |  |

| VIO            | input onset voltage            |                | $VCC = \pm 5 \vee 01 \pm 15 \vee$                             | T <sub>A</sub> = full range |                     |       | 4     |                  |  |

|                | Input offset voltage drift     |                | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$               |                             |                     | 5     |       | μV/ <sup>o</sup> |  |

|                |                                |                | lanut                                                         |                             | $T_A = 25^{\circ}C$ |       | 2     | 10               |  |

|                | Length because of              | -Input         |                                                               | T <sub>A</sub> = full range |                     |       | 15    |                  |  |

| IB             | Input bias current             |                | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$               | T <sub>A</sub> = 25°C       |                     | 1     | 10    | μA               |  |

|                |                                | +Input         |                                                               | T <sub>A</sub> = full range |                     |       | 15    |                  |  |

|                | O                              |                | V <sub>CC</sub> = ±5 V                                        | •                           | ±3                  | ±3.2  | V     |                  |  |

| VICR           | Common-mode input volta        | ge range       | V <sub>CC</sub> = ±15 V                                       |                             | ±12.9               | ±13.2 |       |                  |  |

|                |                                |                | $V_{CC} = \pm 5 V,$<br>R <sub>L</sub> = 1 k $\Omega$          | $V_{O} = \pm 2.5 V,$        |                     | 1.3   |       |                  |  |

|                | Open loop transresistance      |                | $V_{CC} = \pm 15 \text{ V},$<br>R <sub>L</sub> = 1 k $\Omega$ | $V_{O} = \pm 7.5 V,$        |                     | 2.4   |       | ΜΩ               |  |

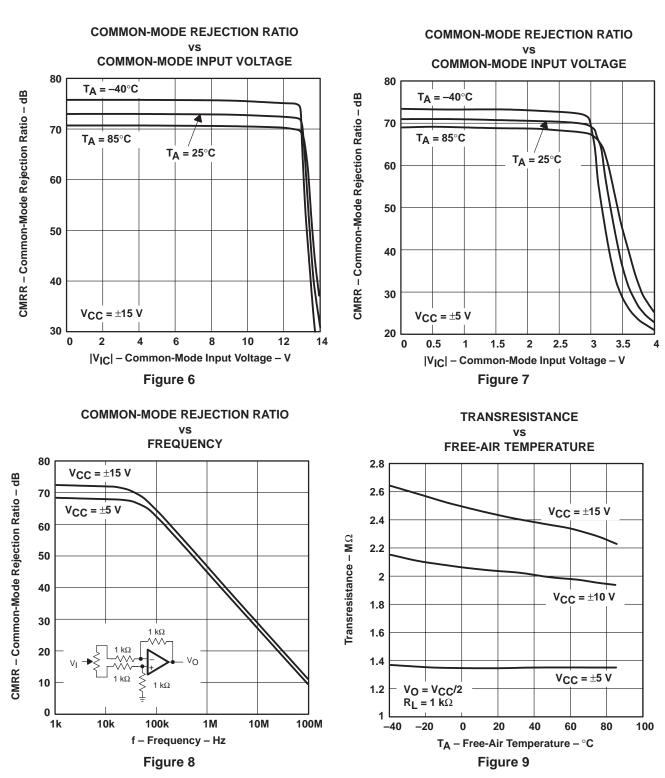

|                |                                |                | $V_{CC} = \pm 5 V,$                                           | $V_{CM} = \pm 2.5 V$        | 62                  | 70    |       |                  |  |

| CMRR           | Common-mode rejection r        | atio           | V <sub>CC</sub> = ±15 V,                                      | $V_{CM} = \pm 10 V$         | 65                  | 73    |       | dE               |  |

|                |                                |                |                                                               | $T_A = 25^{\circ}C$         | 65                  | 76    |       |                  |  |

|                |                                |                | $V_{CC} = \pm 5 V$                                            | $T_A = $ full range         | 63                  |       |       | dE               |  |

| PSRR           | Power supply rejection ration  | 0              |                                                               | T <sub>A</sub> = 25°C       | 69                  | 76    |       |                  |  |

|                |                                |                | $V_{CC} = \pm 15 V$                                           | T <sub>A</sub> = full range | 67                  |       |       | dB               |  |

|                |                                | +Input         |                                                               | •                           |                     | 1.5   |       | M                |  |

| RI             | Input resistance               | –Input         |                                                               |                             |                     | 15    |       | Ω                |  |

| CI             | Differential input capacitance |                |                                                               |                             |                     | 7.5   |       | pF               |  |

| RO             | Output resistance              |                | Open loop at 5 MHz                                            |                             |                     | 10    |       | Ω                |  |

| ∨ <sub>n</sub> | Input voltage noise            |                | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$<br>G = 2     | f = 10 kHz,                 |                     | 1.6   |       | nV/√             |  |

|                | land summary 1                 | Positive (IN+) | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$              | f = 10 kHz,                 | 1                   | 13    |       | pA/√             |  |

| n              | Input current noise            | Negative (IN-) | G = 2                                                         |                             |                     | 16    |       |                  |  |

<sup>†</sup> Full range =  $0^{\circ}$ C to 70°C for the THS300xC and -40°C to 85°C for the THS300xI.

NOTE 1: Observe power dissipation ratings to keep the junction temperature below absolute maximum when the output is heavily loaded or shorted. See absolute maximum ratings section.

SLOS217A - JULY 1998 - REVISED JUNE 1999

# operating characteristics, T\_A = 25°C, R\_L = 150 $\Omega,~R_F$ = 1 k $\Omega$ (unless otherwise noted)

|                | PARAMETER                         | TEST CON                                              | IDITIONS                    | MIN TYP MAX | UNIT   |

|----------------|-----------------------------------|-------------------------------------------------------|-----------------------------|-------------|--------|

|                |                                   | V <sub>CC</sub> = ±5 V,                               | G = -5                      | 1700        |        |

| 00             | Slew rate (see Note 2)            | $V_{O(PP)} = 4 V$                                     | G = 5                       | 1300        |        |

| SR             | Siew Tale (see Note 2)            | $V_{CC} = \pm 15 V,$                                  | G = -5                      | 6500        | V/μs   |

|                |                                   | V <sub>O(PP)</sub> = 20 V                             | G = 5                       | 6300        | ]      |

|                | Settling time to 0.1%             | V <sub>CC</sub> = ±15 V,<br>0 V to 10 V Step          | Gain = −1,                  | 40          |        |

| t <sub>S</sub> | Settling time to 0.1%             | V <sub>CC</sub> = ±5 V,<br>0 V to 2 V Step,           | Gain = −1,                  | 25          | ns     |

| THD            | Total harmonic distortion         | $V_{CC} = \pm 15 V,$<br>f <sub>C</sub> = 10 MHz,      | $V_{O(PP)} = 2 V,$<br>G = 2 | -80         | dBc    |

| AD             | Differential gain error           | G = 2,<br>40 IRE modulation,                          | V <sub>CC</sub> = ±5 V      | 0.015%      |        |

| ~D             |                                   | ±100 IRE Ramp,<br>NTSC and PAL                        | V <sub>CC</sub> = ±15 V     | 0.01%       |        |

| θD             | Differential phase error          | G = 2,<br>40 IRE modulation,                          | $V_{CC} = \pm 5 V$          | 0.01°       |        |

|                | Diferential phase choi            | ±100 IRE Ramp,<br>NTSC and PAL                        | $V_{CC} = \pm 15 V$         | 0.02°       |        |

|                |                                   | $G = 1, R_F = 1 k\Omega,$                             | $V_{CC} = \pm 5 V$ ,        | 330         | MHz    |

|                |                                   | $0 = 1,  n_F = 1, n_{22},$                            | $V_{CC} = \pm 15 V$ ,       | 420         | MHz    |

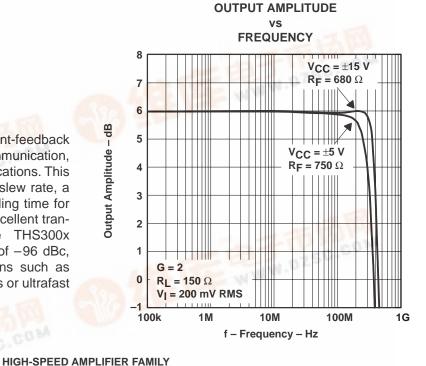

|                | Small signal bandwidth (-3 dB)    | $G = 2, R_F = 750 \Omega,$                            | $V_{CC} = \pm 5 V$          | 300         |        |

| BW             |                                   | $G = 2, R_F = 680 \Omega,$                            | $V_{CC} = \pm 15 V$         | 385         | MHz    |

|                |                                   | G = 5, R <sub>F</sub> = 560 Ω,                        | V <sub>CC</sub> = ±15 V     | 350         |        |

|                | Bandwidth for 0.1 dB flatness     | $G = 2, R_F = 750 \Omega,$                            | $V_{CC} = \pm 5 V$          | 85          | MHz    |

|                | Bandwidth for 0.1 dB natiless     | $G = 2, R_F = 680 \Omega,$                            | V <sub>CC</sub> = ±15 V     | 115         | 101112 |

|                |                                   | $V_{CC} = \pm 5 V,$                                   | G = -5                      | 65          | MHz    |

|                | Full power bandwidth (see Note 3) | $V_{O}(PP) = 4 V,$<br>R <sub>L</sub> = 500 Ω          | G = 5                       | 62          | MHz    |

|                |                                   | V <sub>CC</sub> = ±15 V,<br>V <sub>O(PP)</sub> = 20 V | G = -5                      | 32          | MHz    |

|                |                                   | $R_L = 500 \Omega$                                    | G = 5                       | 31          | MHz    |

|                | Crosstalk (THS3002 only)          |                                                       |                             | TBD         | dB     |

NOTES: 2. Slew rate is measured from an output level range of 25% to 75%.

3. Full power bandwidth is defined as the frequency at which the output has 3% THD.

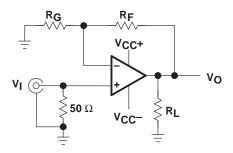

### PARAMETER MEASUREMENT INFORMATION

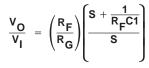

Figure 1. Test Circuit, Gain = 1 + (R<sub>F</sub>/R<sub>G</sub>)

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **TYPICAL CHARACTERISTICS**

### Table of Graphs

|                 |                                           |                                      | FIGURE  |

|-----------------|-------------------------------------------|--------------------------------------|---------|

| IVOI            | Output voltage swing                      | vs Free-air temperature              | 2       |

| ICC             | Current supply                            | vs Free-air temperature              | 3       |

| I <sub>IB</sub> | Input bias current                        | vs Free-air temperature              | 4       |

| VIO             | Input offset voltage                      | vs Free-air temperature              | 5       |

|                 |                                           | vs Common-mode input voltage         | 6       |

| CMRR            | Common-mode rejection ratio               | vs Common-mode input voltage         | 7       |

|                 |                                           | vs Frequency                         | 8       |

|                 | Transresistance                           | vs Free-air temperature              | 9       |

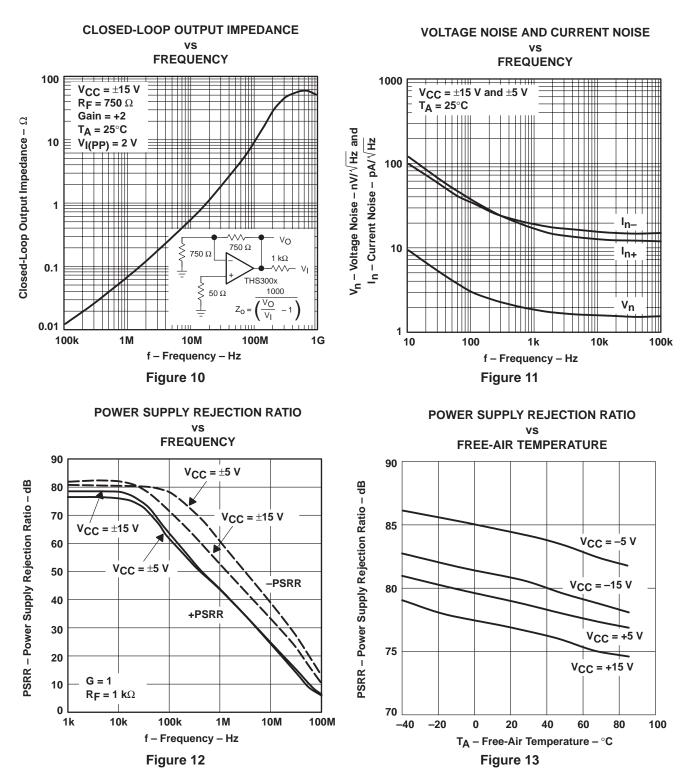

|                 | Closed-loop output impedance              | vs Frequency                         | 10      |

| Vn              | Voltage noise                             | vs Frequency                         | 11      |

| I <sub>n</sub>  | Current noise                             | vs Frequency                         | 11      |

| PSRR            | Dower oursely rejection ratio             | vs Frequency                         | 12      |

| PSRR            | Power supply rejection ratio              | vs Free-air temperature              | 13      |

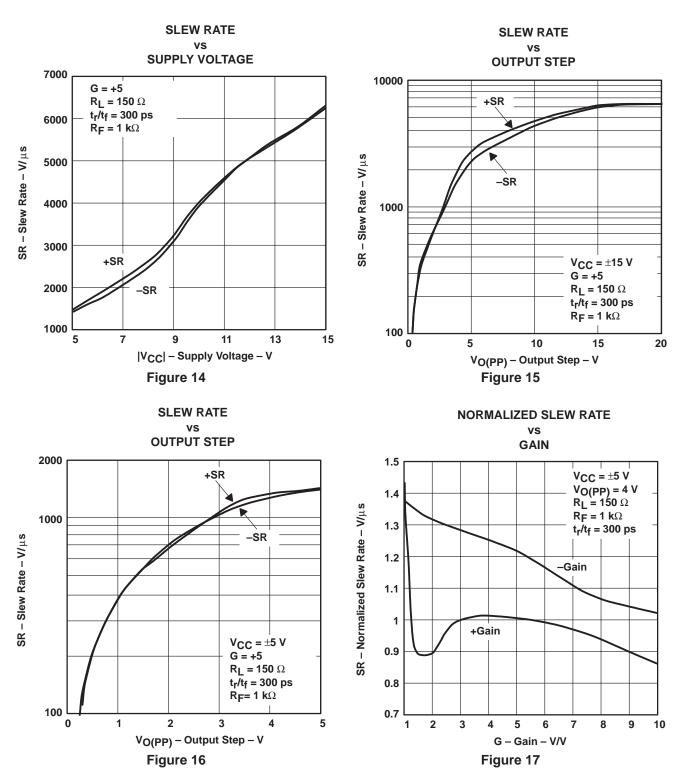

|                 | Slew rate                                 | vs Supply voltage                    | 14      |

| SR              | Siew fate                                 | vs Output step peak-to-peak          | 15, 16  |

|                 | Normalized slew rate                      | vs Gain                              | 17      |

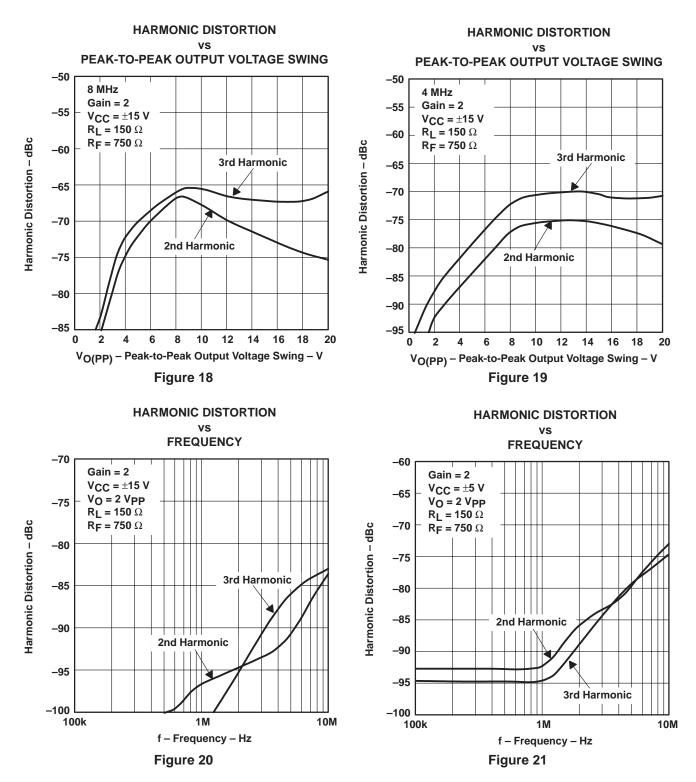

|                 | Harmonic distortion                       | vs Peak-to-peak output voltage swing | 18, 19  |

|                 | Harmonic distortion                       | vs Frequency                         | 20, 21  |

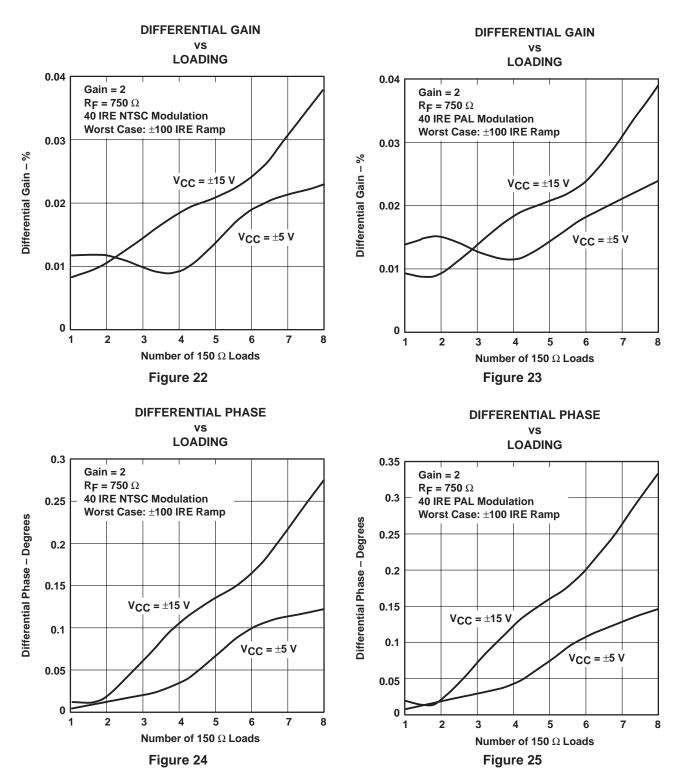

|                 | Differential gain                         | vs Loading                           | 22, 23  |

|                 | Differential phase                        | vs Loading                           | 24, 25  |

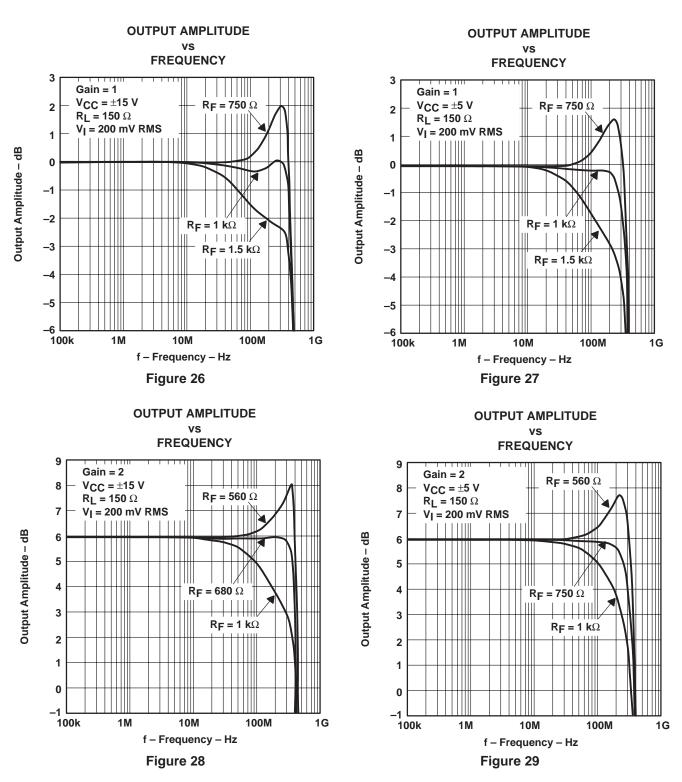

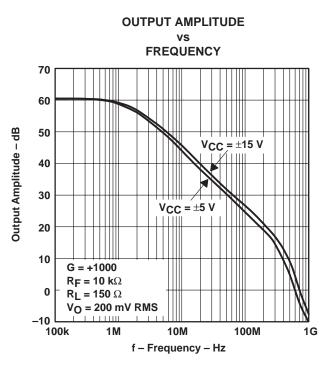

|                 | Output amplitude                          | vs Frequency                         | 26–30   |

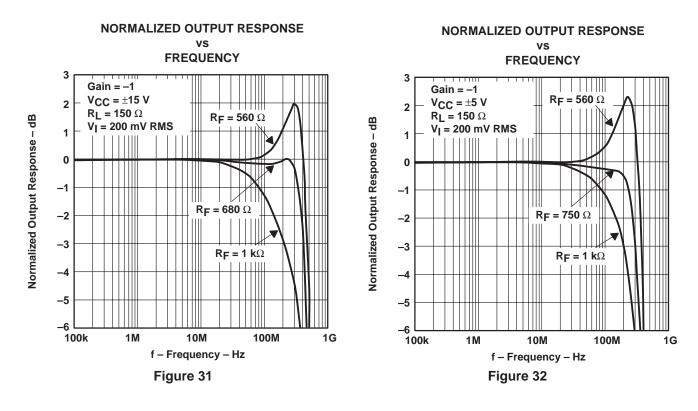

|                 | Normalized output response                | vs Frequency                         | 31–34   |

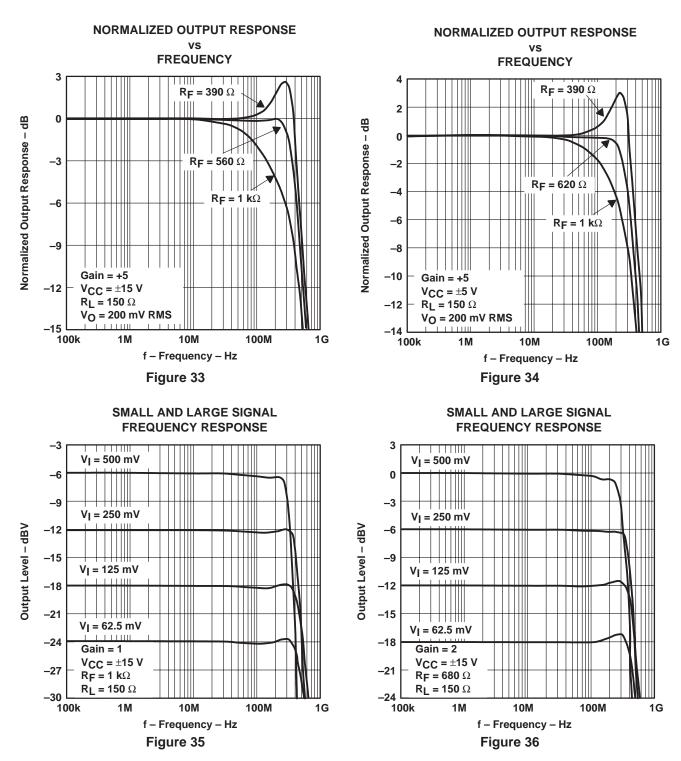

|                 | Small and large signal frequency response |                                      | 35, 36  |

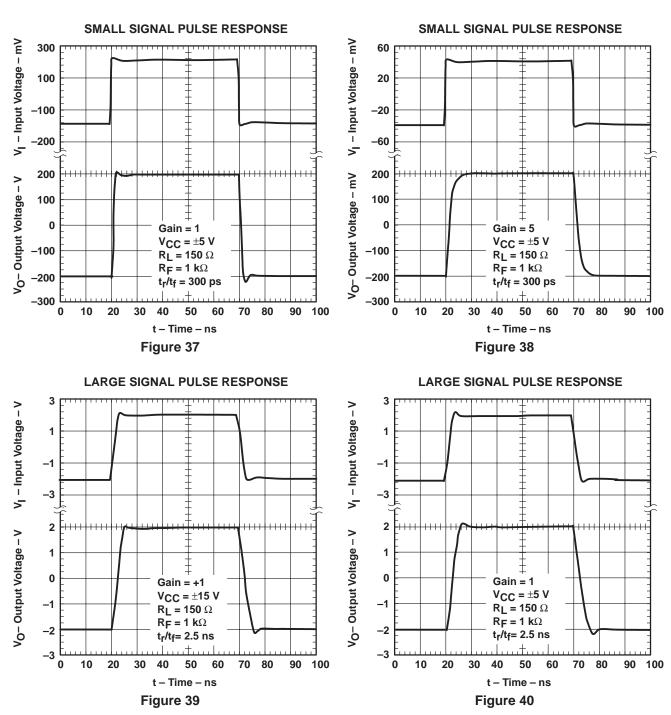

|                 | Small signal pulse response               |                                      | 37, 38  |

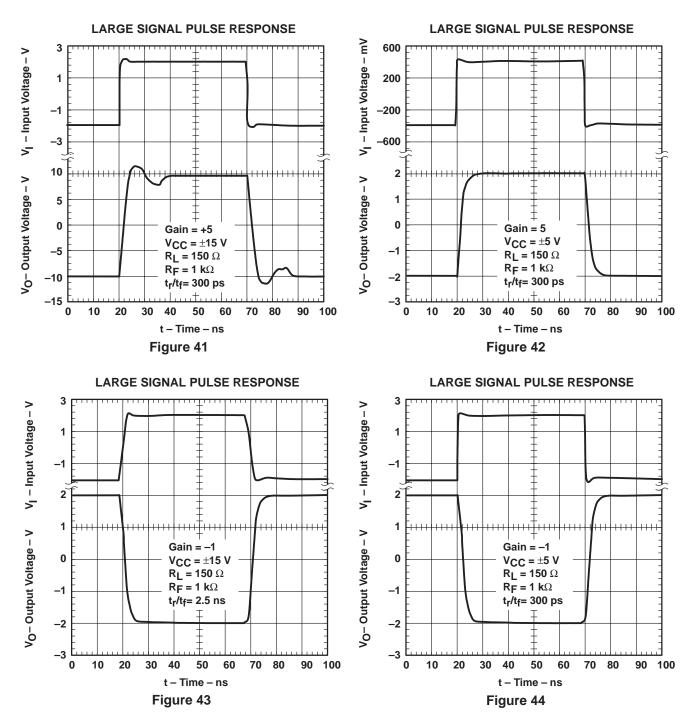

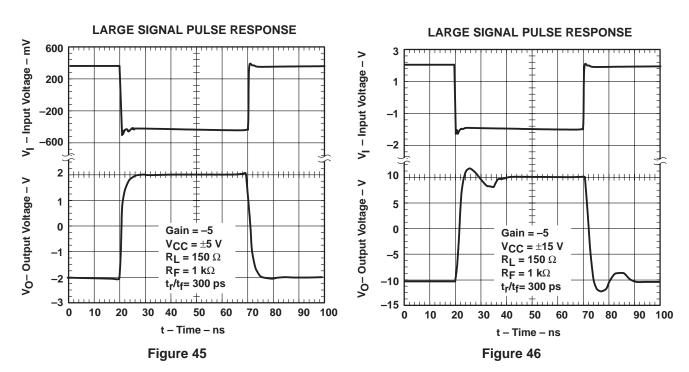

|                 | Large signal pulse response               |                                      | 39 – 46 |

SLOS217A – JULY 1998 – REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A – JULY 1998 – REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A – JULY 1998 – REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **APPLICATION INFORMATION**

### theory of operation

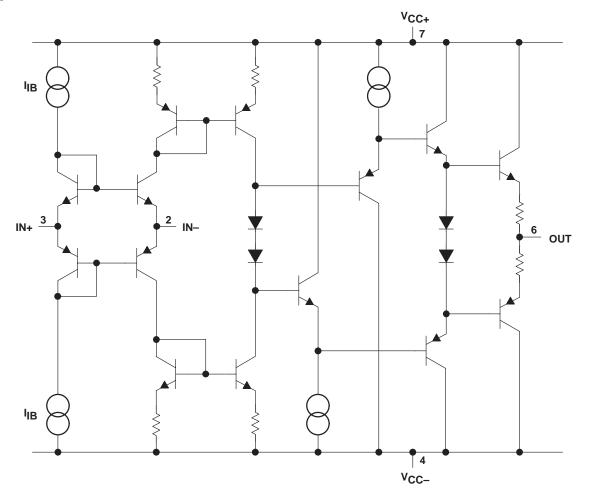

The THS300x is a high-speed, operational amplifier configured in a voltage-feedback architecture. The device is built using a 30-V, dielectrically isolated, complementary bipolar process with NPN and PNP transistors possessing  $f_{TS}$  of several GHz. This configuration implements an exceptionally high-performance amplifier that has a wide bandwidth, high slew rate, fast settling time, and low distortion. A simplified schematic is shown in Figure 47.

Figure 47. Simplified Schematic

SLOS217A - JULY 1998 - REVISED JUNE 1999

#### **APPLICATION INFORMATION**

#### recommended feedback and gain resistor values

The THS300x is fabricated using Texas Instruments 30-V complementary bipolar process, HVBiCOM. This process provides the excellent isolation and extremely high slew rates that result in superior distortion characteristics.

As with all current-feedback amplifiers, the bandwidth of the THS300x is an inversely proportional function of the value of the feedback resistor (see Figures 26 to 34). The recommended resistors for the optimum frequency response are shown in Table 1. These should be used as a starting point and once optimum values are found, 1% tolerance resistors should be used to maintain frequency response characteristics. For most applications, a feedback resistor value of 1 k $\Omega$  is recommended – a good compromise between bandwidth and phase margin that yields a very stable amplifier.

Consistent with current-feedback amplifiers, increasing the gain is best accomplished by changing the gain resistor, not the feedback resistor. This is because the bandwidth of the amplifier is dominated by the feedback resistor value and internal dominant-pole capacitor. The ability to control the amplifier gain independent of the bandwidth constitutes a major advantage of current-feedback amplifiers over conventional voltage-feedback amplifiers. Therefore, once a frequency response is found suitable to a particular application, adjust the value of the gain resistor to increase or decrease the overall amplifier gain.

Finally, it is important to realize the effects of the feedback resistance on distortion. Increasing the resistance decreases the loop gain and increases the distortion. It is also important to know that decreasing load impedance increases total harmonic distortion (THD). Typically, the third-order harmonic distortion increases more than the second-order harmonic distortion.

| GAIN  | $R_F$ for $V_{CC}$ = ±15 V | R <sub>F</sub> for V <sub>CC</sub> = $\pm$ 5 V |

|-------|----------------------------|------------------------------------------------|

| 1     | 1 kΩ                       | 1 kΩ                                           |

| 2, -1 | 680 Ω                      | 750 Ω                                          |

| -2    | 620 Ω                      | 620 Ω                                          |

| 5     | 560 Ω                      | 620 Ω                                          |

#### Table 1. Recommended Resistor Values for Optimum Frequency Response

#### offset voltage

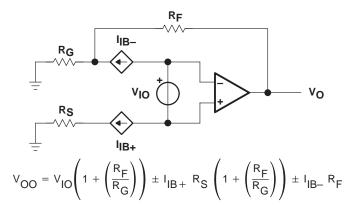

The output offset voltage, ( $V_{OO}$ ) is the sum of the input offset voltage ( $V_{IO}$ ) and both input bias currents ( $I_{IB}$ ) times the corresponding gains. The following schematic and formula can be used to calculate the output offset voltage:

Figure 48. Output Offset Voltage Model

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **APPLICATION INFORMATION**

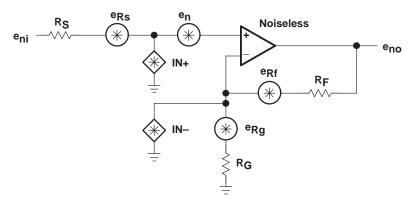

#### noise calculations and noise figure

Noise can cause errors on very small signals. This is especially true for amplifying small signals coming over a transmission line or an antenna. The noise model for current-feedback amplifiers (CFB) is the same as for voltage feedback amplifiers (VFB). The only difference between the two is that CFB amplifiers generally specify different current-noise parameters for each input, while VFB amplifiers usually only specify one noise-current parameter. The noise model is shown in Figure 49. This model includes all of the noise sources as follows:

- $e_n = amplifier internal voltage noise (nV/<math>\sqrt{Hz}$ )

- IN+ = noninverting current noise (pA/ $\sqrt{Hz}$ )

- IN- = inverting current noise (pA/ $\sqrt{Hz}$ )

- e<sub>Rx</sub> = thermal voltage noise associated with each resistor (e<sub>Rx</sub> = 4 kTR<sub>x</sub>)

#### Figure 49. Noise Model

The total equivalent input noise density (eni) is calculated by using the following equation:

$$\mathbf{e}_{ni} = \sqrt{\left(\mathbf{e}_{n}\right)^{2} + \left(\mathbf{IN} + \times \mathbf{R}_{S}\right)^{2} + \left(\mathbf{IN} - \times \left(\mathbf{R}_{F} \| \mathbf{R}_{G}\right)\right)^{2} + 4 \ \mathbf{kTR}_{s} + 4 \ \mathbf{kT}\left(\mathbf{R}_{F} \| \mathbf{R}_{G}\right)$$

Where:

$k = Boltzmann's \ constant = 1.380658 \times 10^{-23} \\ T = temperature \ in \ degrees \ Kelvin \ (273 + ^{\circ}C) \\ R_{F} \parallel R_{G} = parallel \ resistance \ of \ R_{F} \ and \ R_{G}$

To get the equivalent output noise of the amplifier, just multiply the equivalent input noise density  $(e_{ni})$  by the overall amplifier gain  $(A_V)$ .

$$e_{no} = e_{ni} A_V = e_{ni} \left( 1 + \frac{R_F}{R_G} \right)$$

(Noninverting Case)

SLOS217A - JULY 1998 - REVISED JUNE 1999

#### **APPLICATION INFORMATION**

#### noise calculations and noise figure (continued)

As the previous equations show, to keep noise at a minimum, small value resistors should be used. As the closed-loop gain is increased (by reducing  $R_G$ ), the input noise is reduced considerably because of the parallel resistance term. This leads to the general conclusion that the most dominant noise sources are the source resistor ( $R_S$ ) and the internal amplifier noise voltage ( $e_n$ ). Because noise is summed in a root-mean-squares method, noise sources smaller than 25% of the largest noise source can be effectively ignored. This can greatly simplify the formula and make noise calculations much easier.

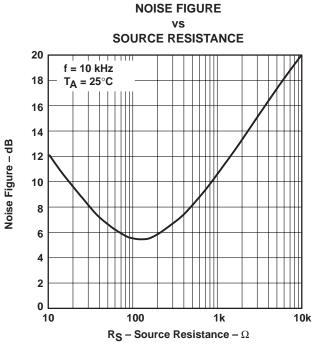

This brings up another noise measurement usually preferred in RF applications, the noise figure (NF). Noise figure is a measure of noise degradation caused by the amplifier. The value of the source resistance must be defined and is typically 50  $\Omega$  in RF applications.

NF = 10log

$$\left[ \frac{e_{ni}^2}{e_{Rs^2}} \right]$$

Because the dominant noise components are generally the source resistance and the internal amplifier noise voltage, we can approximate noise figure as:

$$NF = 10\log\left[1 + \frac{\left(\left(e_{n}\right)^{2} + \left(IN + \times R_{S}\right)^{2}\right)}{4 \text{ kTR}_{S}}\right]$$

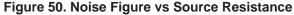

The Figure 50 shows the noise figure graph for the THS300x.

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **APPLICATION INFORMATION**

#### slew rate

The slew rate performance of a current-feedback amplifier, like the THS300x, is affected by many different factors. Some of these factors are external to the device, such as amplifier configuration and PCB parasitics, and others are internal to the device, such as available currents and node capacitance. Understanding some of these factors should help the PCB designer arrive at a more optimum circuit with fewer problems.

Whether the THS300x is used in an inverting amplifier configuration or a noninverting configuration can impact the output slew rate. As can be seen from the specification tables as well as some of the figures in this data sheet, slew-rate performance in the inverting configuration is faster than in the noninverting configuration. This is because in the inverting configuration the input terminals of the amplifier are at a virtual ground and do not significantly change voltage as the input changes. Consequently, the time to charge any capacitance on these input nodes is less than for the noninverting configuration, where the input nodes actually do change in voltage an amount equal to the size of the input step. In addition, any PCB parasitic capacitance on the input nodes degrades the slew rate further simply because there is more capacitance to charge. Also, if the supply voltage ( $V_{CC}$ ) to the amplifier is reduced, slew rate decreases because there is less current available within the amplifier to charge the capacitance on the input nodes as well as other internal nodes.

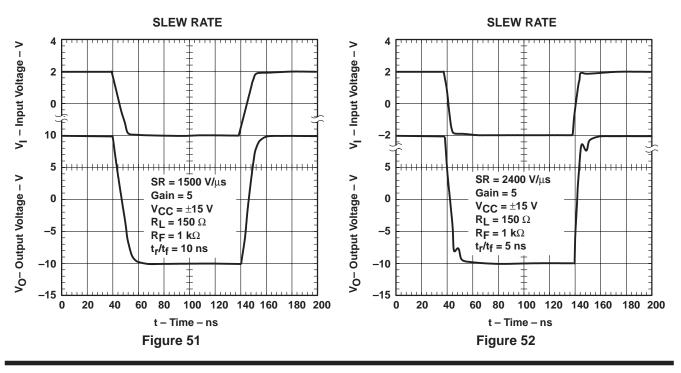

Internally, the THS300x has other factors that impact the slew rate. The amplifier's behavior during the slew-rate transition varies slightly depending upon the rise time of the input. This is because of the way the input stage handles faster and faster input edges. Slew rates (as measured at the amplifier output) of less than about 1500 V/ $\mu$ s are processed by the input stage in a very linear fashion. Consequently, the output waveform smoothly transitions between initial and final voltage levels. This is shown in Figure 51. For slew rates greater than 1500 V/ $\mu$ s, additional slew-enhancing transistors present in the input stage begin to turn on to support these faster signals. The result is an amplifier with extremely fast slew-rate capabilities. Figures 41 and 52 show waveforms for these faster slew rates. The additional aberrations present in the output waveform with these faster-slewing input signals are due to the brief saturation of the internal current mirrors. This phenomenon, which typically lasts less than 20 ns, is considered normal operation and is not detrimental to the device in any way. If for any reason this type of response is not desired, then increasing the feedback resistor or slowing down the input-signal slew rate reduces the effect.

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **APPLICATION INFORMATION**

#### driving a capacitive load

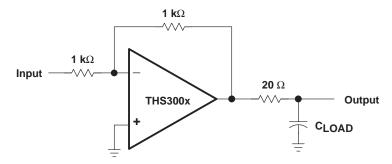

Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS300x has been internally compensated to maximize its bandwidth and slew-rate performance. When the amplifier is compensated in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high-frequency ringing or oscillations. Therefore, for capacitive loads of greater than 10 pF, it is recommended that a resistor be placed in series with the output of the amplifier, as shown in Figure 53. A minimum value of 20  $\Omega$  should work well for most applications. For example, in 75- $\Omega$  transmission systems, setting the series resistor value to 75  $\Omega$  both isolates any capacitance loading and provides the proper line impedance matching at the source end.

Figure 53. Driving a Capacitive Load

#### PCB design considerations

Proper PCB design techniques in two areas are important to assure proper operation of the THS300x. These areas are high-speed layout techniques and thermal-management techniques. Because the THS300x is a high-speed part, the following guidelines are recommended.

- Ground plane It is essential that a ground plane be used on the board to provide all components with a

low inductive ground connection. Although a ground connection directly to a terminal of the THS300x is not

necessarily required, it is recommended that the thermal pad of the package be tied to ground. This serves

two functions: it provides a low inductive ground to the device substrate to minimize internal crosstalk, and

it provides the path for heat removal.

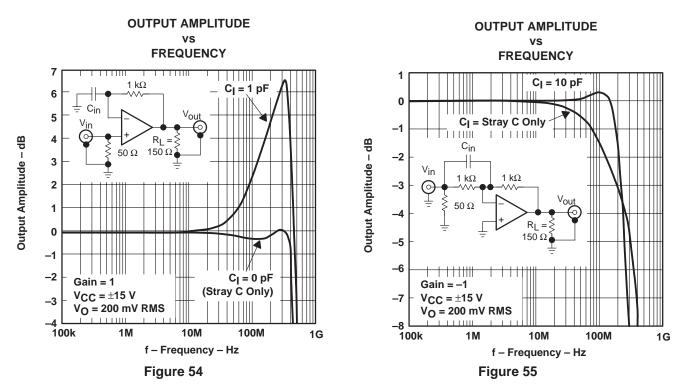

- Input stray capacitance To minimize potential problems with amplifier oscillation, the capacitance at the inverting input of the amplifiers must be kept to a minimum. To do this, PCB trace runs to the inverting input must be as short as possible, the ground plane must be removed under any etch runs connected to the inverting input, and external components should be placed as close as possible to the inverting input. This is especially true in the noninverting configuration. An example of this can be seen in Figure 54, which shows what happens when a 1-pF capacitor is added to the inverting input terminal. The bandwidth increases at the expense of peaking. This is because some of the error current is flowing through the stray capacitor instead of the inverting input has a minimal effect. This is because the inverting node is at a *virtual ground* and the voltage does not fluctuate nearly as much as in the noninverting configuration. This can be seen in Figure 55, where a 10-pF capacitor adds only 0.35 dB of peaking. In general, as the gain of the system increases, the output peaking due to this capacitor decreases. While this can initially look like a faster and better system, overshoot and ringing are more likely to occur under fast transient conditions. So proper analysis of adding a capacitor to the inverting input node should be performed for stable operation.

SLOS217A – JULY 1998 – REVISED JUNE 1999

### **APPLICATION INFORMATION**

### PCB design considerations (continued)

Proper power-supply decoupling – Use a minimum 6.8-μF tantalum capacitor in parallel with a 0.1-μF ceramic capacitor on each supply terminal. It may be possible to share the tantalum among several amplifiers depending on the application, but a 0.1-μF ceramic capacitor should always be used on the supply terminal of every amplifier. In addition, the 0.1-μF capacitor should be placed as close as possible to the supply terminal. As this distance increases, the inductance in the connecting etch makes the capacitor less effective. The designer should strive for distances of less than 0.1 inches between the device power terminal and the ceramic capacitors.

#### thermal information

The THS300x incorporates output-current-limiting protection. Should the output become shorted to ground, the output current is automatically limited to the value given in the data sheet. While this protects the output against excessive current, the device internal power dissipation increases due to the high current and large voltage drop across the output transistors. Continuous output shorts are not recommended and could damage the device. Additionally, connection of the amplifier output to one of the supply rails ( $\pm V_{CC}$ ) is not recommended. Failure of the device is possible under this condition and should be avoided. But, the THS300x does not incorporate thermal-shutdown protection. Because of this, special attention must be paid to the device's power dissipation or failure may result.

SLOS217A - JULY 1998 - REVISED JUNE 1999

#### **APPLICATION INFORMATION**

#### thermal information (continued)

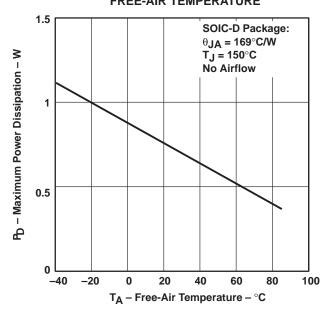

The thermal coefficient  $\theta_{JA}$  is approximately 169°C/W for the SOIC 8-pin D package. For a given  $\theta_{JA}$ , the maximum power dissipation, shown in Figure 56, is calculated by the following formula:

$$\mathsf{P}_{\mathsf{D}} = \left(\frac{\mathsf{T}_{\mathsf{MAX}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{JA}}}\right)$$

Where:

$\begin{array}{ll} \mathsf{P}_{\mathsf{D}} &= \mathsf{Maximum power dissipation of THS300x (watts)} \\ \mathsf{T}_{\mathsf{MAX}} &= \mathsf{Absolute maximum junction temperature (150°C)} \\ \mathsf{T}_{\mathsf{A}} &= \mathsf{Free-ambient air temperature (°C)} \\ \theta_{\mathsf{JA}} &= \mathsf{Thermal coefficient from die junction to ambient air (°C/W)} \end{array}$

MAXIMUM POWER DISSIPATION vs FREE-AIR TEMPERATURE

Figure 56. Maximum Power Dissipation vs Free-Air Temperature

SLOS217A – JULY 1998 – REVISED JUNE 1999

### **APPLICATION INFORMATION**

#### general configurations

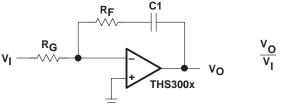

A common error for the first-time CFB user is the creation of a unity gain buffer amplifier by shorting the output directly to the inverting input. A CFB amplifier in this configuration will oscillate and is **not** recommended. The THS300x, like all CFB amplifiers, **must** have a feedback resistor for stable operation. Additionally, placing capacitors directly from the output to the inverting input is not recommended. This is because, at high frequencies, a capacitor has a very low impedance. This results in an unstable amplifier and should not be considered when using a current-feedback amplifier. Because of this, integrators and simple low-pass filters, which are easily implemented on a VFB amplifier, have to be designed slightly differently. If filtering is required, simply place an RC-filter at the noninverting terminal of the operational-amplifier (see Figure 57).

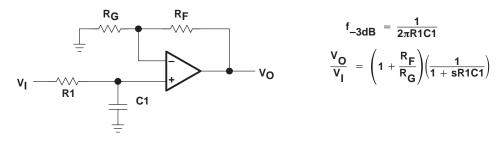

Figure 57. Single-Pole Low-Pass Filter

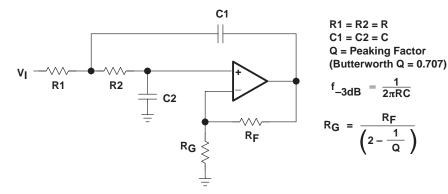

If a multiple-pole filter is required, the use of a Sallen-Key filter can work very well with CFB amplifiers. This is because the filtering elements are not in the negative feedback loop and stability is not compromised. Because of their high slew-rates and high bandwidths, CFB amplifiers can create very accurate signals and help minimize distortion. An example is shown in Figure 58.

Figure 58. 2-Pole Low-Pass Sallen-Key Filter

There are two simple ways to create an integrator with a CFB amplifier. The first, shown in Figure 59, adds a resistor in series with the capacitor. This is acceptable because at high frequencies, the resistor is dominant and the feedback impedance never drops below the resistor value. The second, shown in Figure 60, uses positive feedback to create the integration. Caution is advised because oscillations can occur due to the positive feedback.

SLOS217A - JULY 1998 - REVISED JUNE 1999

### **APPLICATION INFORMATION**

general configurations (continued)

Figure 59. Inverting CFB Integrator

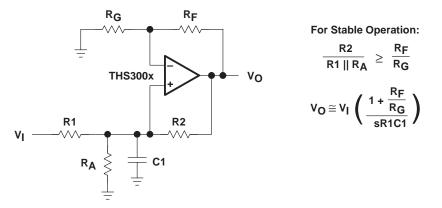

The THS300x may also be employed as a very good video distribution amplifier. One characteristic of distribution amplifiers is the fact that the differential phase (DP) and the differential gain (DG) are compromised as the number of lines increases and the closed-loop gain increases (see Figures 22 to 25 for more information). Be sure to use termination resistors throughout the distribution system to minimize reflections and capacitive loading.

Figure 61. Video Distribution Amplifier Application

SLOS217A – JULY 1998 – REVISED JUNE 1999

### **APPLICATION INFORMATION**

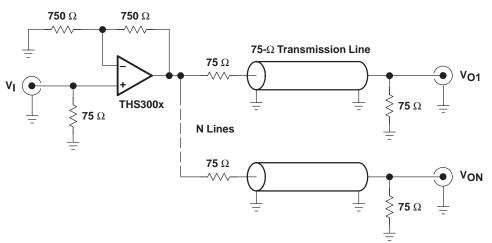

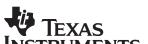

#### evaluation board

Evaluation boards are available for the THS3001 (literature #SLOP130) and the THS3002 (literature #SLOP241). The boards have been configured for very low parasitic capacitance in order to realize the full performance of the amplifier. Schematics of the evaluation boards are shown in Figures 62 and 63. The circuitry has been designed so that the amplifier may be used in either an inverting or noninverting configuration. To order the evaluation board contact your local TI sales office or distributor. For more detailed information, refer to the *THS3001 EVM User's Manual* (literature #SLOV021) or the *THS3002 EVM User's Guide* (literature #SLOVxxx). To order the evaluation board, contact your local TI sales office or distributor.

Figure 62. THS3001 Evaluation Board Schematic

SLOS217A - JULY 1998 - REVISED JUNE 1999

#### **APPLICATION INFORMATION**

### evaluation board (continued)

SLOS217A - JULY 1998 - REVISED JUNE 1999

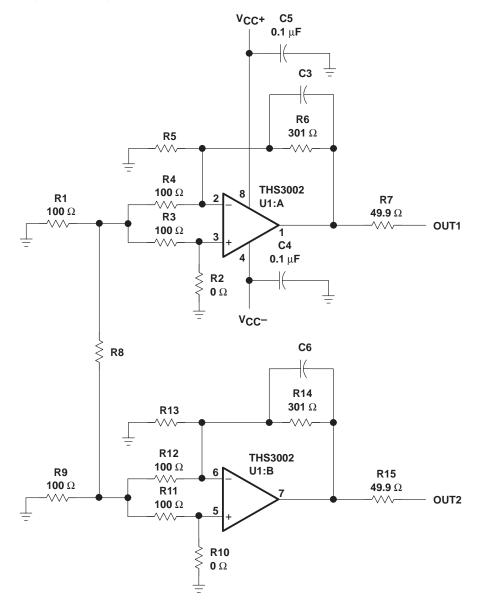

### **MECHANICAL INFORMATION**

### D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

SLOS217A - JULY 1998 - REVISED JUNE 1999

#### **MECHANICAL INFORMATION**

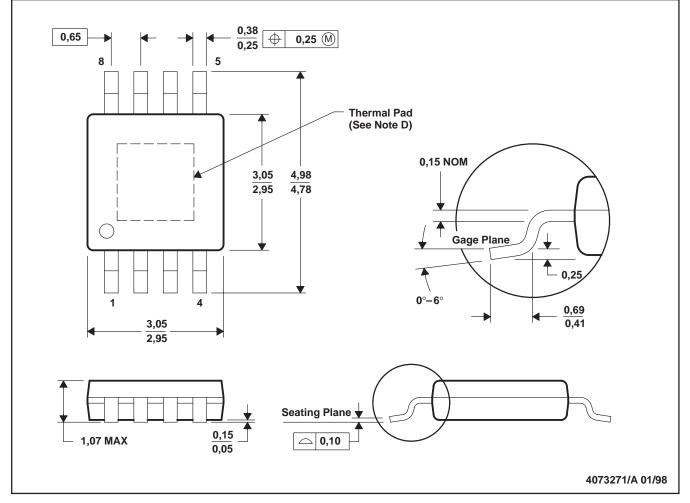

### DGN (S-PDSO-G8)

#### PowerPAD<sup>™</sup> PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusions.

- D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated