# International Rectifier

Data Sheet No. PD60223

Advance Information

## IRMCS2031

# Complete Sensorless Drive Design Platform iMOTION<sup>TM</sup> Development System

#### **Features**

- Low cost complete AC sensorless drive design platform

- IRMCK203 IC for complete sensorless control

- Simple design with IR2175 current sensing HVIC

- 230V/750W maximum output power with 600V/16A advanced Plug-N-Drive<sup>™</sup> IGBT module

- Wide speed range and high speed operation

- Support any permanent magnet AC motors

- Low loss/EMI Space Vector PWM

- No voltage feedback sensing

- Low cost A/D interface with multiplexer

- 4-channel D/A output for diagnostics/monitoring

- ServoDesigner<sup>TM</sup> tool for easy operation

- RS232C/RS422 and fast SPI interface

- Parallel interface for microcontroller expansion

- Over-current and ground fault protection

- Over-voltage / Under-voltage protection

- Dynamic Braking control with brake IGBT/FWD

- Discrete I/Os (START/STOP, FAULT, FLTCLR, SYNC ESTOP, PWMEN)

- Configuration data retention at power up/down

#### **Product Summary**

Speed operation range (typical) 5 to 100%

High speed operation 100,000rpm (2pole)

Speed accuracy 0.01%

Speed resolution 15bit

PWM carrier frequency 60 kHz max

Sensorless control computation time 10 usec

Continuous output current 5 Arms (750W)

Overload output current 15 Arms (750W)

Maximum modulation index 1.2

Max RS232C speed 57.6 kbps

Optional RS422 communication 1Mbps

#### Description

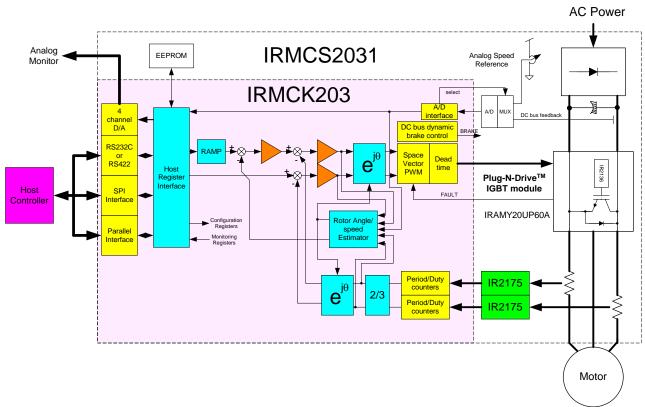

IRMCS2031 is a complete sensorless drive design platform for industrial/appliance applications up to 1.0 HP output power. The system contains the latest advanced motion control IC, IRMCK203, and the ServoDesigner<sup>TM</sup> software. The complete B/Ms and schematics are provided so that the user can adapt and tailor the design per application needs. The system does not requires any software code development due to unique Motion Control Engine implemented in the IRMCK203 IC. User can readily evaluate high performance sensorless control without spending development effort usually required in the traditional DSP or microcontroller based system. IRMCS2031 contains advanced iMOTION chipset such as IR2175 monolithic current sensing ICs and IRAMX16A60A intelligent power module, which enable simple and cost effective motion control design.

#### Overview

The IRMCS2031 is a design platform for a complete Sensorless drive system based on the IRMCK201 digital motion control IC. The system is based on configurable control engine implemented by hardware logics in the IRMCK203. The system has a simple and low cost structure, made possible by an advanced IR motion components including the IRAMX16UP60A IGBT module, and IR2175 monolithic current sensing high voltage IC. These components together with the IRMCK203 simplify hardware implementation. Since all control logic is implemented in hardware logic as opposed to programmed software, unmatched parallel computation is achieved resulting in higher bandwidth control and higher motor operating frequency (15 usec minimum PWM loop cycle).

Despite of hardware logic implementation, its design flexibility allows the user to configure Permanent Magnetic ac motors (Sinusoidal Back EMF) with different motor parameters and different types of communication protocols.

Figure 1. IRMCS2031 System Block Diagram

#### Safety Precautions

In addition to the precautions listed throughout this manual, you must read and understand the following statements regarding hazards associated with AC servo development system.

**ATTENTION:** Some ground potential of the IRMCS2031 system is biased to a negative DC bus voltage potential and kept high voltage potential while power is on. When measuring voltage waveform by oscilloscope, the scope ground needs to be isolated. Failure to do so may result in personal injury or death.

Darkened display LEDs is not an indication that capacitors have discharged to safe voltage levels.

**ATTENTION:** The IRMCS2031 system contains high voltage capacitors which take time to discharge after removal of main supply. Before working on drive system, ensure isolation of mains supply from line inputs [R, S, T]. Wait three minutes for capacitors to discharge to safe voltage levels. Failure to do so may result in personal injury or death.

Darkened display LEDs is not an indication that capacitors have discharged to safe voltage levels.

**ATTENTION:** Only personnel familiar with the drive and associated machinery should plan or implement the installation, start-up, and subsequent maintenance of the system. Failure to comply may result in personal injury and/or equipment damage.

**ATTENTION:** The surface temperatures of the drive may become hot, which may cause injury.

**ATTENTION:** The IRMCS2031 system contains ESD (Electrostatic Discharge) sensitive parts and assemblies. Static control precautions are required when installing, testing, servicing or repairing this assembly. Component damage may result if ESD control

procedures are not followed. If you are not familiar with static control procedures, reference applicable ESD protection handbook and guideline.

**ATTENTION:** An incorrectly applied or installed drive can result in component damage or reduction in product life. Wiring or application errors such as undersizing the motor, supplying an incorrect or inadequate AC supply, or excessive ambient temperatures may result in system malfunction.

**ATTENTION:** Remove and lock out power from the drive before you disconnect or reconnect wires or perform service. Wait three minutes after removing power to discharge the bus voltage. Do not attempt to service the drive until bus voltage has discharged to zero. Failure to do so may result in bodily injury or death.

**ATTENTION:** The drive is intended to be commanded by control input that will start and stop the motor. A device that routinely disconnects then reapplies input power to the drive for the purpose of starting and stopping the motor should not be used. Failure to follow this guideline may result in damage of equipment, and/or bodily injury or death.

**ATTENTION:** Do not connect power factor correction capacitors to drive output terminals U, V, and W. Failure to do so may result in equipment damage or bodily injury.

This document is the property of International Pactifier and may not be conied or distributed without expressed consent

#### Debris When Unpacking

The IRMCS2031 system is shipped with packing materials that need to be removed prior to installation.

**ATTENTION:** Failure to remove all debris and packing materials, which are unnecessary for system installation, may result in overheating or abnormal operating condition.

#### Hardware Installation

#### Check All Hardware

The following hardware pieces are contained in the IRMCS2031 system.

- IRMCS2031 board with integrated heat sink

- Serial RS232C cable with 9-pin Dsub connectors for ServoDesigner<sup>TM</sup> development tool

- Two 10 m Ohms shunt resistors

#### Step 1.

Connect motor power and ground cables to the IRMCS2031 board.

#### Step 2.

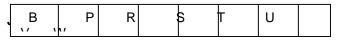

Connect AC115V or single phase 230V or three phase 230V power. For single phase 100V-230V AC power, use R and T for connection. For three phase 230V power, use R/S/T for connection. Insert a power contactor switch rated at 250V/30A in series with AC power cables.

Figure 2. Power Connector, J1

#### Step 3.

Connect motor power lead. Follow the color code connection below.

$\begin{aligned} RED &= U \\ WHITE &= V \\ BLACK &= W \end{aligned}$

Connect Earth Ground terminal to the heatsink.

Figure 3. Earth Ground Connection

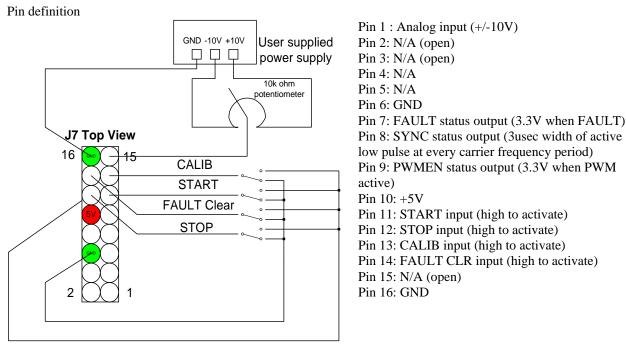

#### Step 5. (Optional) J7 Connector, External I/O

Connect External I/O Connector (J7) as needed. All inputs are 5V tolerant.

Figure 4. J7 Connector connection

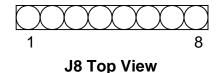

#### Step 6. (Optional) J8 Connector, Analog Output monitoring

Figure 5. J8 Connector connection

#### Pin Definition

Pin 1: Channel 1 Analog output (0-5V)

Pin 2: GND

Pin 3: Channel 2 Analog output (0-5V)

Pin 4: GND

Pin 5: Channel 3 Analog output (0-5V)

Pin 6: GND

Pin 7: Channel 4 Analog output (0-5V)

Pin 8: GND

#### Step 7.

Connect the RS232C cable between 9-pin D-sub connector and PC.

#### Installing the Software

The ServoDesigner<sup>TM</sup> tool is distributed on the CD-ROM. Load the CD into the CD-ROM drive on your PC and double-click "IRMCS2031.exe". It requires the password which also can be found in the same CD-ROM. The automated procedure installs all necessary software on your PC. The default location for the installation is "C:\Program Files\Accelerator".

#### Power-On the System

Apply AC115V – AC230V power to the system.

Immediately after power-on, the power supply RED LED (located at the bottom left corner of the board) will light indicating the on-board DC bus has been established. The second LED (surface mount LED located at the top side of the board) should also start blinking on/off RED.

#### **Getting Started**

For quick start with preconfigured parameters, the following motor is supported with a preconfigured motor file.

• Sanyo Denki motor (400W: type P30B06040DXS00M)

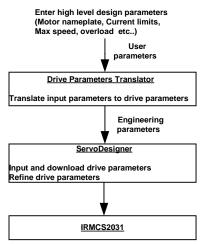

If any other motor is used, reconfiguration is required. Configurable parameters are required to tailor design to various applications (motor and load). These configurable parameters can be modified via the host register interface (using the ServoDesigner tool) through the communication interface. In the IRMCS2031 product, a design spreadsheet (Drive parameters translator) is provided to aid the user for ease of drive start-up. Using the spreadsheet, the user enters high-level parameters such as motor nameplate information, maximum application speed, current limit, speed and current regulator bandwidth. This high-level user information is translated to engineering parameters (directly used by the drive). Figure gives an overview of the commissioning steps. Please refer to the IRMCK203 Application Developer's Guide for detailed drive commissioning description.

Figure 6. Overview of Drive Commissioning

#### Shunt Resistor and Current Rating

Two 20m Ohms current sensing shunt resistors are equipped as default resistors at factory shipment (R34 and R36 located on the bottom side of PCB). With these resistors, IRMCS2031 can deliver up to  $\pm 13$ A maximum peak current to the motor including overshoot of current regulation.

When using any higher power motor with a rating greater than 3Arms and less than 6Arms continuous current, then 10m Ohm shunt resistors are recommended in place of the 20m Ohm shunt resistors.

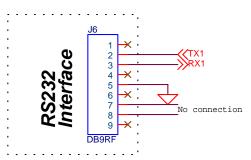

#### RS232C connector

IRMCS2031 has one serial RS232C connector (J6) on the board. The connector is D-sub 9 pin standard PC female connector and directly connectable to PC serial port. As shown in Figure 8, pin2 is send signal and pin3 is receive signal, and both are 10V signal level. The baud rate is fixed at 57.6kbps. The signal format is 8bit, no parity, 1 stop bit configuration.

Figure 5. RS232C connector

#### **RS-232 Register Access**

The IRMCK203 includes an RS-232 interface channel that provides a direct connection to the host PC. The software interface combines a basic "register map" control interface with a simple communication protocol to accommodate potential communication errors. For more detailed information, please refer to IRMCx201 Application Development Guide.doc

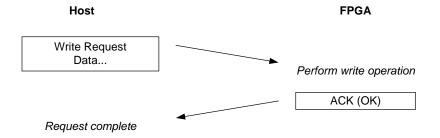

#### **RS-232 Register Write Access**

A Register write operation consists of a command/address byte, byte count, register data and checksum. When the IRMCK203 receives the register data, it validates the checksum, writes the register data, and transmits and acknowledgement to the host.

| Command / Address Byte Byte Count |                 | 1-6 bytes of register data | Checksum |  |  |  |

|-----------------------------------|-----------------|----------------------------|----------|--|--|--|

| Register Write Operation          |                 |                            |          |  |  |  |

|                                   |                 |                            |          |  |  |  |

| Command Acknow                    | vledgement Byte | Checksu                    | m        |  |  |  |

**Register Write Acknowledgement**

| Bit Position       |                               |   |   |   |   |   |   |

|--------------------|-------------------------------|---|---|---|---|---|---|

| 7                  | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |

| 1=Read/<br>0=Write | Register Map Starting Address |   |   |   |   |   |   |

#### **Command/Address Byte Format**

| Bit Position     |                               |   |   |   |   |   |   |  |

|------------------|-------------------------------|---|---|---|---|---|---|--|

| 7                | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 1=Error/<br>0=OK | Register Map Starting Address |   |   |   |   |   |   |  |

#### **Command Acknowledgement Byte Format**

The following example shows a command sequence sent from the host to the IRMCK203 requesting a two-byte register write operation:

0x2F Write operation beginning at offset 0x2F

0x02 Byte count of register data is 2

0x00 Data byte 1 0x04 Data byte 2

0x35 Checksum (sum of preceding bytes, overflow discarded)

A good reply from the IRMCK203 would appear as follows:

0x2F Write completed OK at offset 0x2F

0x2F Checksum

An error reply to the command would have the following format:

0xAF Write at offset 0x2F completed in error

0xAF Checksum

#### **RS-232 Register Read Access**

A register read operation consists of a command/address byte, byte count and checksum. When the IRMCK203 receives the command, it validates the checksum and transmits the register data to the host.

| Command / Address Byte | Byte Count | Checksum |

|------------------------|------------|----------|

|------------------------|------------|----------|

#### **Register Read Operation**

#### Register Read Acknowledgement (transfer OK)

| Command Acknowledgement Byte | Checksum |

|------------------------------|----------|

|------------------------------|----------|

#### Register Read Acknowledgement (error)

The following example shows a command sequence sent from the host to the IRMCK203 requesting four bytes of read register data:

| 0xA0 | Read operation beginning at offset 0x20 (high-order bit selects read operation) |

|------|---------------------------------------------------------------------------------|

| UXAU | Read operation degining at offset 0x20 (mgn-order bit selects read operation)   |

|      |                                                                                 |

0x04 Requested data byte count is 4

0xA4 Checksum

A good reply from the IRMCK203 might appear as follows:

| 0x20 | Read completed OK at offset 0x20 |

|------|----------------------------------|

| 0x11 | Data byte 1                      |

| 0x22 | Data byte 2                      |

| 0x33 | Data byte 3                      |

| 0x44 | Data byte 4                      |

| 0xCA | Checksum                         |

An error reply to the command would have the following format:

0xA0 Read at offset 0x20 completed in error

0xA0 Checksum

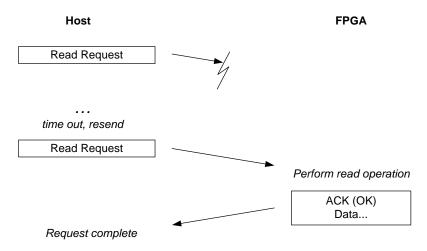

#### **RS-232 Timeout**

The IRMCK203 receiver includes a timer that automatically terminates transfers from the host to the IRMCK203 after a period of 32 msec.

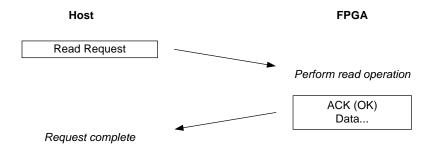

#### **RS-232 Transfer Examples**

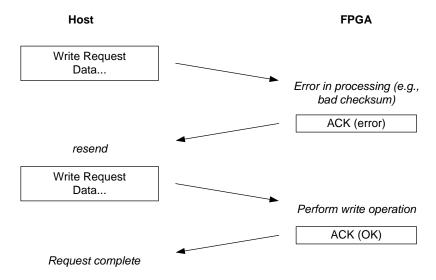

The following example shows a normal exchange executing a register write access.

The example below shows a normal register read access exchange.

The following example shows a register write request that is repeated by the host due to a negative acknowledgement from the IRMCK203.

In the final example, the host repeats a register read access request when it receives no response to its first attempt.

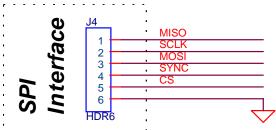

#### SPI interface connector

IRMCS2031 has one SPI interface connector (J4) on the board. The connector is a 6pin header and its pin assignment are shown below. The signal level is 3.3V with 5V tolerant input. Maximum transimission speed is 6MHz.

Figure 6 SPI interface connector

#### SPI Register Access

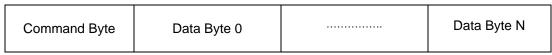

When configured as an SPI device read only and read/write operations are performed using the following transfer format:

**Data Transfer Format**

**Command Byte Format**

Data transfers begin at the address specified in the command byte and proceed sequentially until the SPI transfer completes. Note that accesses are read/write unless the "read only" bit is set.

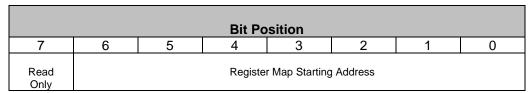

#### Parallel Interface Port

IRMCS2031 provides a 8bit parallel interface port to facilitate microprocessor interface. Interface is generic and be able to interface most common 8bit parallel interface such as MCS8051, some Motorola 8bit uP, MicroChp,etc. Figure 9 shows the connection diagram. The connector, J5, is an 2-by-10 header connector pins. Each signal is 3.3V level and data bus is multiplexed. Table 1 summarizes each signal definition.

Figure 7 Parallel Interface Port

| Signal  | I/O <sup>1</sup> | Description                                                         |

|---------|------------------|---------------------------------------------------------------------|

| HP_nCS  | ı                | Active low Host Port Chip Select                                    |

| HP_nOE  | I                | Active Low Host Port Output Enable                                  |

| HP_nWE  | 1                | Active low Host Port Write Enable                                   |

| HP_A    | 1                | Host Port Register Address. 1 = Address register, 0 = Data Register |

| HP_Data | I/O              | Bidirectional Host Port data bus                                    |

Table 2. Microprocessor Interface Module Signal Definitions

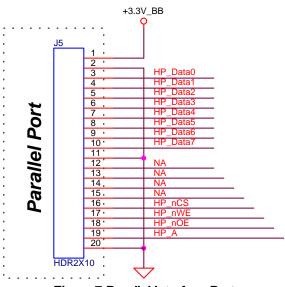

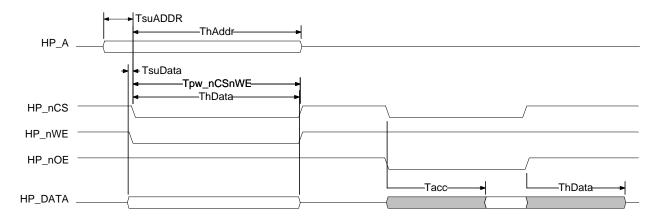

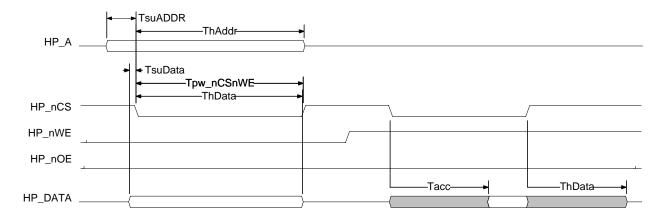

Figures 10 and 11 show detailed timing requirements for register read and write operations depending on the type of microprocessor (Intel or Motorola type). All values are in nanoseconds. The data bus output is activated by the logical combination (!nCS && !nOE && new), which allows read and write operations to be either nWe/nOE (Intel) or nCS (Motorola) driven. Figures 4 and 5 show example connections for Intel 8051 and Motorola 64K/Coldfire microprocessors.

| Row |   | Name       | Min | Max | Comment                                                                    |  |

|-----|---|------------|-----|-----|----------------------------------------------------------------------------|--|

| 1   | С | TsuADDR    | 10  |     | HP_A to HPnCS or HP_nWE (which ever occurs last) low setup time            |  |

| 2   | С | TsuData    | 0   |     | HP_D to HPnCS or HP_nWE (which ever occurs last) low setup time            |  |

| 3   | С | Tpw_nCSnWE | 60  |     | Minimum pulswidth for nCS and nWE                                          |  |

| 4   | С | ThData     | 60  |     | Minimum data hold time from HP_nWE or HPnCS (whichever occurs last) low    |  |

| 5   | С | ThAddr     |     |     | Minimum address hold time from HP_nWE or HPnCS (whichever occurs last) low |  |

| 6   | D | Tacc       | 0   | 35  | HP_nCS or HP_nOE (whichever occurs last) to Data access time               |  |

| 7   | D | ThData     | 0   | 35  | HP_nCS or HP_nOE (whichever occurs last) to Data invalid/Hi-               |  |

This document is the property of International Pactifier and may not be copied or distributed without expressed consent

Figure 8. Register Write/Read Timing (Intel)

| Row |   | Name       | Min | Max | Comment                                  |  |

|-----|---|------------|-----|-----|------------------------------------------|--|

| 1   | С | TsuADDR    | 10  |     | HP_A to HPnCS low setup time             |  |

| 2   | С | TsuData    | 0   |     | HP_D to HPnCS low setup time             |  |

| 3   | С | Tpw_nCSnWE | 60  |     | Minimum pulswidth for nCS                |  |

| 4   | С | ThData     | 60  |     | Minimum data hold time from HPnCS low    |  |

| 5   | С | ThAddr     |     |     | Minimum address hold time from HPnCS low |  |

| 6   | D | Tacc       | 0   | 35  | HP_nCS to Data access time               |  |

| 7   | D | ThData     | 0   | 35  | HP_nCS to Data invalid/Hi-Z              |  |

Figure 9. Register Write/Read Timing (Motorola)

This document is the property of International Pactifier and may not be conied or distributed without expressed consent

### **Specifications**

Tc=25°C unless specified

| Tc=25°C unless specified       |                                              |                                                                    |  |  |  |  |  |

|--------------------------------|----------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Parameters                     | Values                                       | Conditions                                                         |  |  |  |  |  |

| Input Power                    |                                              |                                                                    |  |  |  |  |  |

| Voltage                        | 115V-230Vrms, -20%, +10%                     |                                                                    |  |  |  |  |  |

| Frequency                      | 50/60 Hz                                     |                                                                    |  |  |  |  |  |

| Input current                  | 6A rms @nominal output                       | TA=40°C,RthSA=1.0 °C/W                                             |  |  |  |  |  |

| Input line impedance           | 4%~8% recommended                            |                                                                    |  |  |  |  |  |

| Output Power                   |                                              |                                                                    |  |  |  |  |  |

| kW                             | 750W continuous power                        | Vin=230V AC, fPWM=8kHz, fO=60Hz,<br>TA=40°C,RthSA=1.0 °C/W         |  |  |  |  |  |

| Current                        | 5 Arms nominal, 15 Arms Overload             | ZthSA limits $\Delta$ TC to 10°C during overload                   |  |  |  |  |  |

| Host interface (SPI)           | , , , , , , , , , , , , , , , , , , , ,      |                                                                    |  |  |  |  |  |

| SCLK,CS,MISO,MOSI, SYNC        | 3.3V logic level                             | Galvanic isolated, maximum 6MHz                                    |  |  |  |  |  |

| Host interface (RS232C)        | and regional series                          |                                                                    |  |  |  |  |  |

| SND,RCV                        | 10V                                          | Maximum 57.6k bps, single ended,                                   |  |  |  |  |  |

| Heat interfere (Penallal Bent) |                                              | configurable for RS422 up to 1Mbps                                 |  |  |  |  |  |

| Host interface (Parallel Port) | 2.21/                                        | O hit navellal interfers somewhile with 0054                       |  |  |  |  |  |

| HP_nCS,HP_nOE,HP_nWE,          | 3.3V                                         | 8 bit parallel interface compatible with 8051, Microchip,other uP. |  |  |  |  |  |

| HP_A,HP_DATA[8]                |                                              | Microchip,other up.                                                |  |  |  |  |  |

| D/A                            |                                              |                                                                    |  |  |  |  |  |

| 10 bit 4 Channel               | 0-5V output                                  | Output are buffered with 4mA drive capability                      |  |  |  |  |  |

| A/D                            |                                              |                                                                    |  |  |  |  |  |

| 12 bit 2 channel               | ±10V for reference input, 5V for DCbus input | 4 channel additional input available (optional)                    |  |  |  |  |  |

| Discrete I/O                   | ·                                            |                                                                    |  |  |  |  |  |

| Input                          | 4 bit, START, STOP, FLTCLR, CALIB            | 5V tolerant, Isolated, Active High logic                           |  |  |  |  |  |

| Output                         | 3 bit, PWMACTIVE, FAULT, SYNC                |                                                                    |  |  |  |  |  |

| Current feedback               |                                              |                                                                    |  |  |  |  |  |

| Current sensing device         | IR2175, direct interface                     |                                                                    |  |  |  |  |  |

| Resolution                     | 10 bit (7.5 nanoseconds counting             | 133 MHz internal IRMCK203 clock                                    |  |  |  |  |  |

|                                | resolution)                                  |                                                                    |  |  |  |  |  |

| Latency                        | 8.3 usec                                     | 2175 PWM output (120 kHz)                                          |  |  |  |  |  |

| Protection                     |                                              |                                                                    |  |  |  |  |  |

| Output current trip level      | 27.5A peak, ±10%                             | Fixed by IRAM16XUP60A module                                       |  |  |  |  |  |

| Ground fault trip level        | 35A peak, ±10%                               |                                                                    |  |  |  |  |  |

| Over-temperature trip level    | 110°C, ±5%                                   | Case temperature                                                   |  |  |  |  |  |

| Short circuit delay time       | 2.5 usec                                     | line-to-line short, line-to-DC bus (-) short                       |  |  |  |  |  |

| DC bus voltage                 |                                              | , , , , , , , , , , , , , , , , , , , ,                            |  |  |  |  |  |

| Maximum DC bus voltage         | 400V                                         | Should not exceed 400V for > 30 sec                                |  |  |  |  |  |

| Minimum DC bus voltage         | 85V                                          | VCC=15V ± 10%,VDD=5V ± 5%                                          |  |  |  |  |  |

| Power Module                   |                                              |                                                                    |  |  |  |  |  |

| IRAMX16UP60A                   | 6 IGBT/FRED + IR2136 gate driver,            | Bootstrap power supply for high side circuit                       |  |  |  |  |  |

| 3-phase HVIC                   | integrated overcurrent/overtemp protection   |                                                                    |  |  |  |  |  |

| System environment             | •                                            |                                                                    |  |  |  |  |  |

| Ambient temperature            | 0 to 40°C                                    | 95%RH max. (non-condensing)                                        |  |  |  |  |  |

Table 1. IRMCS2031 Electrical Specification

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 252-7105

<a href="http://www.irf.com">http://www.irf.com</a>

Data and specifications subject to change without notice

January 6, 2004

Sales Offices, Agents and Distributors in Major Cities Throughout the World.

This document is the property of International Pactifier and may not be copied or distributed without expressed consent

1 (