查询NJU3421A供应商

# VFD CONTROLLER DRIVER

WWW.DZSC.COM

## GENERAL DESCRIPTION

JRC

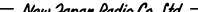

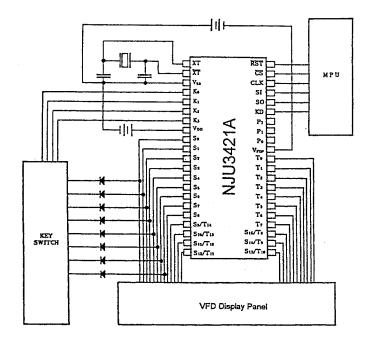

The NJU3421A is a VFD (Vacuum Fluorescent Display) Controller Driver with key scan function.

It contains display data RAM, address counter, command register, high voltage drivers, and serial interface circuit.

The display data, the command data and the key scanning data can be transmitted with the serial interface circuit, and VFD driving voltage can operate up to 45V. The NJU3421A is useful for car audio, VCR and other VFD application items.

#### FEATURES VED D.

|   | VFD Driving Voltage          | VDD-VFDP S45V                  |

|---|------------------------------|--------------------------------|

| ) | Display Mode                 | 9 Segments Display × 15 Digits |

|   |                              | 16 Segments Display × 8 Digits |

| ) | Serial Interface             |                                |

| ) | Display ON/OFF Function      |                                |

| ) | Key Scan Function            | $8 \times 4$ Keys max.         |

| ) | Display Data RAM             | $30 \times 8$ Bits             |

| ) | key Input Data RAM           | $8 \times 4$ Bits              |

| ) | Key Input Detecting Function |                                |

| ) | High Driving Current(1/0 Por | ts)lo=10mA max.                |

| ) | Oscillation Circuit on-chip  |                                |

| ) | Power On Initialization      |                                |

| ) | Operating Voltage            | 5V±10%                         |

| ) | Package Outline              | SDIP 42 / QFP 44-A1 🔜 🧰        |

| ) | C-MOS Technology             |                                |

|   |                              |                                |

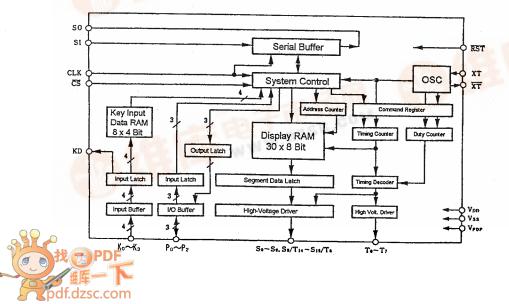

PACKAGE OUTLINE

捷多邦,专业PCB打样

24小时

1 A

8

NJU3421AL

NJU3421AF

### BLOCK DIAGRAM

PIN CONFIGURATION

8

|  | TERMINAL | DESCRIPTION |  |

|--|----------|-------------|--|

|--|----------|-------------|--|

| NO.<br>SD1P42 QFP44-A1 |                                | 0////DOI                                   |                                                                                                                                                          |  |  |  |

|------------------------|--------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                        |                                | SYMBOL                                     | FUNCTION                                                                                                                                                 |  |  |  |

| 8<br>3<br>33           | 3<br>42<br>29                  | V <sub>DD</sub><br>Vss<br>V <sub>fdP</sub> | POWER SOURCE<br>GND<br>VFD Driving Voltage                                                                                                               |  |  |  |

| 1, 2                   | 40, 41                         | XT, XT                                     | Oscillation Terminals. For external clock operation,<br>The clock should be input on XT terminal.                                                        |  |  |  |

| 4~7                    | 43, 44, 1, 2                   | K₀∼K₃                                      | Key Input Terminals(Pull-Down Resistance)                                                                                                                |  |  |  |

| 37                     | 33                             | KD                                         | Key Input Detecting Terminal. When key input, "H" level<br>is output from this terminal.                                                                 |  |  |  |

| 9~17<br>18~24<br>25~32 | 4~12<br>13~19<br>20, 21, 23~28 | So~S8<br>S9/T14~S15/T8<br>T7~T0            | Segment Output Terminals(Pull-Down Resistance)<br>Segment/Timing Output Terminals(Pull-Down Resistance)<br>Timing Output Terminals(Pull-Down Resistance) |  |  |  |

| 42                     | 39                             | RST                                        | Reset Terminal (Pull-UP Resistance) "L":Reset                                                                                                            |  |  |  |

| 34~36                  | 30~32                          | ₽₀∼₽₂                                      | I/O Ports (Pull-Up Resistance)<br>Output:High current Output(LED Display is available)<br>Input:Available by all "H" output setting.                     |  |  |  |

| 38                     | 35                             | SO                                         | Serial Data Output Terminal. The key scan data or<br>the I/O port output data is output.                                                                 |  |  |  |

| 39                     | 36                             | SI                                         | Serial Data (Address, I/O Ports, Command, Display)<br>input Terminal.                                                                                    |  |  |  |

| 40                     | 37                             | CLK                                        | Shift Clock Input Terminal.                                                                                                                              |  |  |  |

| 41                     | 38                             | CS                                         | Chip Select Input Terminal. "L":Activated.                                                                                                               |  |  |  |

|                        | 22, 34                         | NC                                         | Non Connection.                                                                                                                                          |  |  |  |

JRC

#### FUNCTION DESCRIPTION

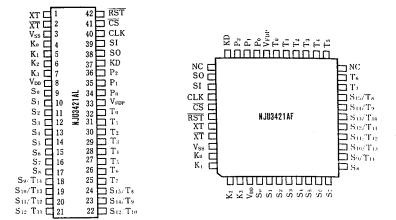

#### (1) Address Counter

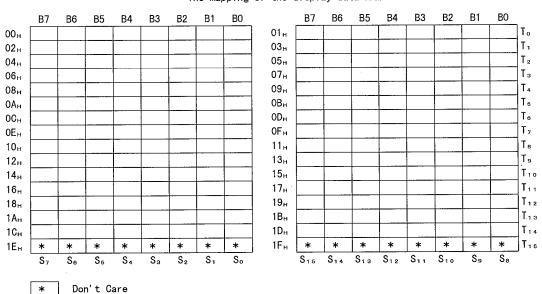

The address counter addresses the display data RAM which data are sent by the serial data transmission. When the first word of the serial data is recognized as the address of the display data RAM (The upper two bits of a byte must be "00".), the lower 5bits are set up into the address counter as the address of the display data RAM. The data of the display data RAM which are input sequentially are set into the specified address and the address counter increments.

Though the address counter consists of the 5-bit counter, the effective range is from "00000"  $(00_{H})$  to "11101"  $(1D_{H})$  and the invalid range is from "11110"  $(1E_{H})$  and "11111"  $(1F_{H})$ . The address of "11111"  $(1F_{H})$  is incremented to "00000"  $(00_{H})$ .

The mapping of the display data RAM

#### (2) COMMAND REGISTER

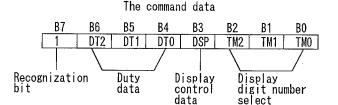

The Command Register is the register for setting the status of Display Duty, Display Digit Number and Display ON/OFF.

When the first word of serial transmmitted data is recognized as the command data (The upper one bit of a byte must be "1".), the lower 7 bits are set into the command register. After the command data are received the timing counter is initialized and then the input command is executed. During the initialization of the timing counter and the command execution, the display can be off. Therefore, the frequent command transmission causes the flicker of the display.

The default status of the display mode is display-off by the power on initialization function.

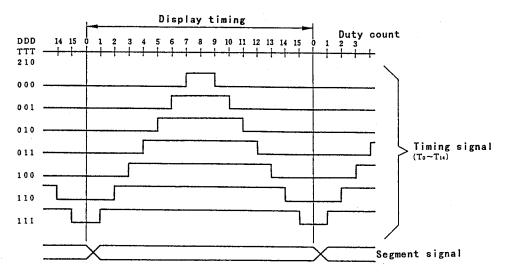

(2-1) Duty set

| DT2 | DT1 | DTO | Timing signal<br>Duty |

|-----|-----|-----|-----------------------|

| 0   | 0   | 0   | 2/16                  |

| 0   | 0   | 1   | 4/16                  |

| 0   | 1   | 0   | 6/16                  |

| 0   | 1   | 1   | 8/16                  |

| 1   | 0   | 0   | 10/16                 |

| 1   | 0   | 1   | 12/16                 |

| 1   | 1   | 0   | 14/16                 |

| 1   | 1   | 1   | 15/16                 |

(2-2) Display contorol set

| DSP | Display |

|-----|---------|

| 0   | OFF     |

| 1   | ON      |

(2-3) Display digit number set

| TM2 | TM1 | TMO | Digits |

|-----|-----|-----|--------|

| 0   | 0   | 0   | 8      |

| 0   | 0   | 1   | 9      |

| 0   | 1   | 0   | 10     |

| 0   | 1   | 1   | 11     |

| 1   | 0   | 0   | 12     |

| 1   | 0   | 1   | 13     |

| 1   | 1   | 0   | 14     |

| 1   | 1   | 1   | 15     |

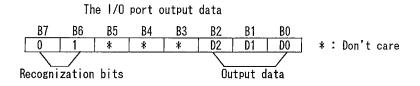

## (3) 1/0 Port

The NJU3421A incorporates three I/O ports. As the output type of these three ports is the constructed by the N-channel and open-drain type FET of the low on-resistance and the pull-up resistor, the output driver can drive the LED. When "H" level is set with the I/O port output data, these I/O ports can be used as the input mode.

When the first word of serial data is recognized as the I/O port output data (the upper two bits of a byte must be "01"), The status of the data of the lower three bits are output from the I/O port.

JRC

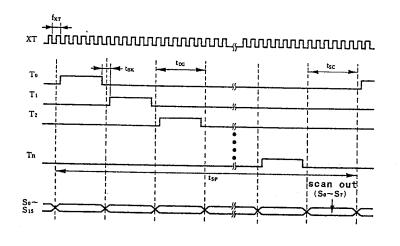

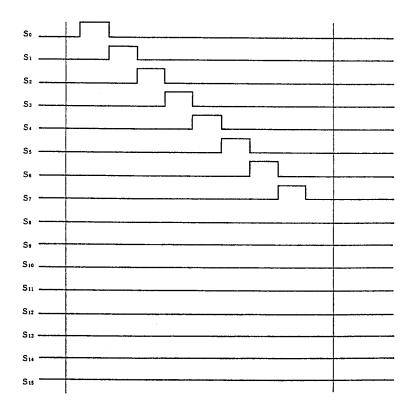

DISPLAY TIMING CHART

Oscillation frequency Minimum blanking time (Duty 15/16) 1character display time key scanning time 1cycle display time

:  $f_{XT}$ :  $t_{BK} = (1/f_{XT}) \times 96$ :  $t_{DG} = t_{BK} \times 16$ :  $t_{SC} = t_{DG}$ :  $t_{SP} = t_{DG} \times character + t_{SC}$

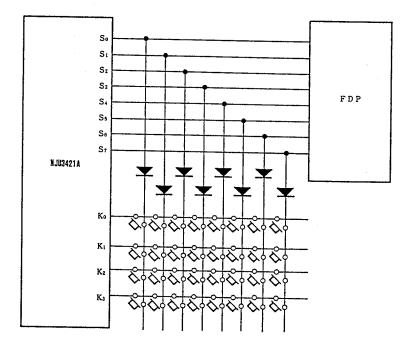

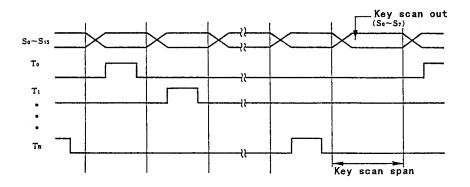

#### (4) KEY INPUT CIRCUIT

The key input circuit is constructed with the key scanning outputs (8 outputs) which are appropriated from the segment output ( $S_0$  to  $S_7$ ) for the display, the key input terminals (4 terminals) and the key switches as shown below. When the key scanning signal is output during the key pushed, the key input terminal receives the same level ("H") of the key scanning signal. If the keys are not pushed, the key input terminal receives "L" level at any time because of its pull-down resistor.

The received key data are stored in the key data RAM in sequence and the data can be get by the serial data transmmition .

The key input detecting function lets the key input detecting output terminal goes to "H" level when any key pushes. The "H" level output of the key input detecting output terminal is continued during the key pushed.

(4-1) Key condition vs Key input terminal level

| key condition  | input level |

|----------------|-------------|

| key pushed     | "H"         |

| not key pushed | "L"         |

key matrix

# FDP DISPLAY OUTPUT WAVEFORM

ENLARGED KEY SCAN SPAN

JRC

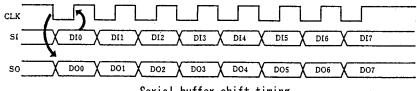

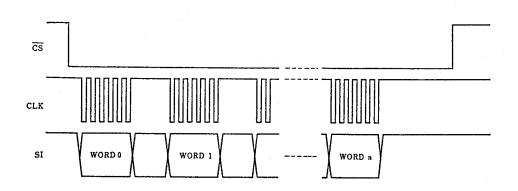

#### (5) SERIAL DATA TRANSMISSION

The data transmission with the external can be executed by the serial interface circuit only. This interface circuit requires the external shift clock input and can execute the bi-direction (input/output) action synchronously as shown below.

The serial data are grouped at a word which equalles to a byte (8 bits) for this device. The serial interface circuit is activated when the CS terminal is set to "L" level. While the CS is "L", the words of the serial data are able to transmitted using the shift clock ( the CLK terminal) and the serial data input or output (the SI or SO terminal) synchronously.

On the data input status, the first transmitted word must be the address, the command or the 1/0 port output data. When the first word is the address data, the following words should be the display data. When the first word is the command or 1/0 port output data, the following words, if transmitted, are ineffective.

On the data output status, the transmitted word incorporates the key data corresponding to the lower 4 bits and the I/O port input data corresponding to the upper 4 bits (The MSB is invalid). The key data of the first word means the data by scanning the  $S_0$ , these of the second word means the data by scanning the  $S_1$ , ... finally, these of the 8th word means the data by scanning the  $S_7$ . The I/O port input data means the last status data. For getting all key matrix data ( $8 \times 4 \mod 3$ ), the data transmission of the 8 words is required.

After the key data transmission is ignored at less than 8 words, the next key data transmission is reset to the first ( $S_0$  scanning) word.

CLK and SI/SO TIMING CHART

Serial buffer shift timing

JRC

#### (5-1) SERIAL INPUT DATA

|        |    |     | The    | addres | s data |        |     |      |                |

|--------|----|-----|--------|--------|--------|--------|-----|------|----------------|

|        | B7 | B6  | B5     | B4     | B3     | B2     | B1  | BO   |                |

|        | 0  | 0   | *      | AD4    | AD3    | AD2    | AD1 | ADO  | * : Don't care |

|        |    |     |        |        |        |        |     |      |                |

|        |    |     | The    | comma  | nd dat | а      |     |      |                |

| WORD O | B7 | B6  | B5     | B4     | B3     | B2     | B1  | B0   |                |

| HORD O | 1  | DT2 | DT1    | DTO    | DSP    | TM2    | TM1 | TMO  |                |

|        |    |     | The I/ | 0 port | outpu  | t data |     |      |                |

|        | B7 | B6  | B5     | B4     | B3     | B2     | B1  | - B0 |                |

|        | 0  | 1   | *      | *      | *      | D2     | D1  | DO   | ∗ : Don't care |

|        |    |     |        |        |        |        |     |      |                |

WORD 1~n Display data are required when WORD 0 = address data Any data are become ineffective when WORD 0 = not address data

(5-2) SERIAL OUTPUT DATA

|              | Serial output dataB7B6B5B4B3B2B1B0WORD 0~7*P2P1P0K3K2K1K0*<: Don't care |        |    |    |    |    |    |    |                |

|--------------|-------------------------------------------------------------------------|--------|----|----|----|----|----|----|----------------|

|              | Β7                                                                      | B6     | B5 | B4 | B3 | B2 | B1 | BO |                |

| ₩ORD 0~7     | *                                                                       | P2     | P1 | PO | K3 | K2 | K1 | KO | * : Don't care |

| (Key scannin | g data                                                                  | n:S₀~S | 7) |    |    |    |    |    |                |

WORD 8~n Ineffective data

#### M ABSOLUTE MAXIMUM RATINGS

| SOLUTE MAXIMUM RATINGS         |           |                                                           |                                                | 0.5°0 \        |

|--------------------------------|-----------|-----------------------------------------------------------|------------------------------------------------|----------------|

| PARAMETER                      | SYMBOL    | RATINGS                                                   | CONDITIONS                                     | a=25°C<br>UNIT |

| Operating Voltage              | Vpp       | -0.3 ~ +7.0                                               |                                                | V              |

| Input Voltage                  | VIN       | -0.3 ~ Vpp+0.3                                            |                                                | v              |

| Output Voltage                 | Vout      | -0.3 ~ Vpp+0.3                                            |                                                | V              |

| VFD Driving Voltage            | $V_{FDP}$ | V <sub>DD</sub> -45~V <sub>DD</sub> +0.3                  |                                                | v              |

|                                | Іон       | -5                                                        | For a terminal except<br>the display terminals |                |

| "H" level Output Current       | I ODH 1   | -15                                                       | For a terminal,<br>S₀~S⁊ Terminals only        | mA             |

|                                |           | For a terminal, T₀~T₂,<br>Sଃ/Tュ₅~Sı₅/Tଃ<br>Terminals only |                                                |                |

| "l" lovel Total Output Concert | ΣΙон      | 40                                                        |                                                | mA             |

| "H" level Total Output Current | ΣІорн     | -100                                                      | Sum of the<br>Display Terminals                | mA             |

| "L" level Output Current       | 1010      | 20                                                        | For a terminal,<br>P₀~P₁ Terminals only        | mA             |

| "L" level Total Output Current | ΣΙοι      | 100                                                       | Sum of the Output<br>terminals                 | mA             |

| Power Dissipation              | P₀        | SDIP: 250<br>QFP: 300                                     | · · · ·                                        | mW             |

| Operating Temperature Range    | Topr      | -30 ~ + 80                                                |                                                | °C             |

| Storage Temperature Range      | Tstg      | -55 ~ +125                                                |                                                | °C             |

#### ELECTRICAL CHARACTERISTICS

( Ta=25°C, V<sub>ss</sub>=0V )

| PARAMETER                    | SYMBOL             | CONDITIONS                                                                                                                                                                                           | MIN                 | TYP | MAX                 | UNIT |

|------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Operating Voltage            | VDD                | V <sub>DD</sub> Terminal                                                                                                                                                                             | 4. 5                |     | 5. 5                | V    |

| ″11″                         | V1H1               | XT, RST, CS, SI, CLK, P₀~P₂<br>Terminals                                                                                                                                                             | 0. 8V <sub>DD</sub> |     |                     | v    |

| "H" Level Input Voltage      | V1H2               | K₀~K₃ Terminals                                                                                                                                                                                      | 0. 4V <sub>DD</sub> |     |                     | v    |

| "L" Level Input Voltage      | V1L1               | XT, RST, CS, SI, CLK, P₀~P₂<br>Terminals                                                                                                                                                             |                     |     | 0. 2Vpd             | v    |

|                              | V 1 L 2            | K₀~K₃ Terminals                                                                                                                                                                                      |                     |     | 0.16V <sub>DD</sub> | V    |

| "H" Level Output Voltage     | V <sub>он 1</sub>  | KD, SO Terminals<br>V <sub>DD</sub> =4.5V, Іоні=-0.5mA                                                                                                                                               | 4. 0                |     |                     | v    |

| H Level Output Voltage       | VoH 2              | KD, SO Terminals<br>Vpp=4.5V, lон₂=−1.2mA                                                                                                                                                            | 3.5                 |     |                     | v    |

|                              | V <sub>ol1</sub>   | KD, SO Terminals<br>V <sub>DD</sub> =4.5V, I <sub>OL1</sub> =+1.8mA                                                                                                                                  |                     |     | 0. 4                |      |

| "L" Level Output Voltage     | V <sub>0 L 2</sub> | KD, SO Terminals<br>V <sub>DD</sub> =4.5V, l <sub>oL2</sub> =+3.6mA                                                                                                                                  |                     |     | 0.6                 | v    |

|                              | V <sub>013</sub>   | Po∼P₂ Terminals<br>Vpp=4.5V, lot3=+10mA                                                                                                                                                              |                     |     | 0. 4                |      |

| Input Off Leak Current       | l <sub>+z</sub>    | CS, CLK, SI Terminals   Vpp=5.5V, V1=0 or 5.5V                                                                                                                                                       |                     |     | ±1                  | uA   |

|                              | Іон                | S₀~S₀ Terminals<br>V₀₀=4.5V, V₀н=V₀₀-2.5V                                                                                                                                                            | -7                  |     |                     |      |

| Display Output Current       |                    | $S_9/T_{14} \sim S_{16}/T_8$ , $T_0 \sim T_7$ Term.<br>$V_{DD}=4.5V$ , $V_{CH}=V_{DD}-2.5V$                                                                                                          | -15                 |     |                     | mA   |

|                              | Rur                | RST Terminal<br>Vpp=5.0V, V₁=Vss                                                                                                                                                                     | 140                 |     | 260                 |      |

| Pull-Up Resistance           | Rup                | P₀~P₂ Terminals<br>V₀⊳=5.0V, V₁=V₅s                                                                                                                                                                  | 10                  |     | 20                  | kΩ   |

|                              | Rok                | K₀∼K₃ Terminals<br>Vɒɒ=5.0V, Vı=V₅s                                                                                                                                                                  | 20                  |     | 50                  |      |

| Pull-Down resistance         | Rost               | $S_0 \sim S_8, S_9/T_{14} \sim S_{15}/T_8, T_0 \sim T_7$<br>$V_{DD}=5.0V, V_0=V_{SS}, V_{FDP}=V_{DD}=40V$                                                                                            | 70                  |     | 200                 | kΩ   |

| Logic Operating Current      | I <sub>DD 1</sub>  | $V_{ss}$ Terminal, $V_{Do}{=}5.0V,~4MHz$ Ceramic resonator, $C_1{=}C_2{=}27pF$ Output Open, All Segment or Timing Output is OFF                                                                      |                     | 1   | 2                   | mA   |

| Display Operating<br>Current | 1002               | V <sub>FDP</sub> Terminal, V <sub>DD</sub> =5. OV, Outp-<br>ut Open except SO~S8, TO~T7<br>S <sub>9</sub> /T <sub>14</sub> ~S <sub>15</sub> /T <sub>8</sub><br>All Segment or<br>Timing Output is ON |                     | 7   | 10                  | mA   |

8

JRC

CLK

50%

tclk

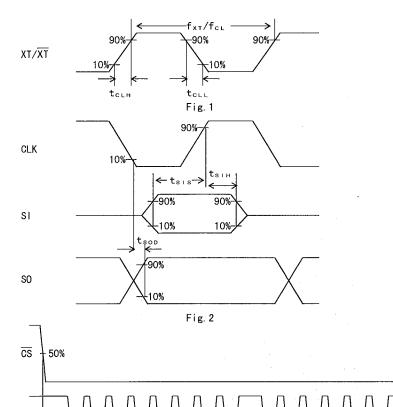

#### AC Characteristics

NJU3421A

( Ta=25°C,  $V_{DD}=5V\pm10\%$ ,  $V_{SS}=0V$  )

50%

50%

tolk1

| PARAMETER                                     | SYMBOL           | CONDITIONS                             | MIN  | TYP | MAX                | UNIT |

|-----------------------------------------------|------------------|----------------------------------------|------|-----|--------------------|------|

| Oscillation Frequency<br>External Clock Input | fx⊤<br>fc∟       | Fig. 1                                 | 1    | 4   | 5                  | MHz  |

| External Clock Rise Time                      | tclH             | Fig. I                                 |      |     | 20                 | ns   |

| External Clock Fall Time                      | tcll             | -                                      |      |     | 20                 | ns   |

| Serial Input Setup Time                       | tsis             | Fig. 2                                 | 60   |     |                    | ns   |

| Serial Input Hold Time                        | tsıн             | F1g. 2                                 | 10   |     |                    | ns   |

| Serial Output Delay Time                      | tsop             | Fig. 2, Load=50pF                      |      |     | 120                | ns   |

| Shift Clock Frequency                         | fclk             | E:- 2                                  |      |     | f <sub>x1</sub> /3 | MHz  |

| Shift Clock Interval Time                     | tclk             | — Fig. 3                               | 10   |     |                    | us   |

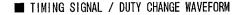

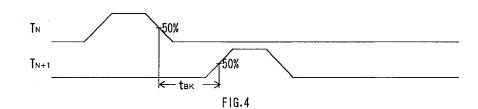

| Minimum Blanking Time                         | · tвк            | Fig.4, @f <sub>x⊤</sub> =4MHz          | 20   |     | 30                 | us   |

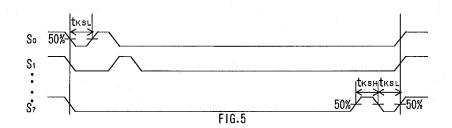

| "L" level Time                                | t <sub>ksl</sub> |                                        | 20   |     |                    | us   |

| "H" level Time                                | tksh             | Fig.5, @f <sub>x⊤</sub> =4MHz,Key scan | 20   |     | 30                 | us   |

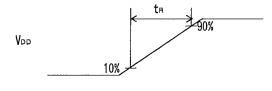

| Power Rise Time                               | t <sub>R</sub>   | Fig. 6                                 | 0.05 |     | 50                 | ms   |

| Reset Pulse Width                             | t <sub>RST</sub> |                                        | 10   |     |                    | us   |

Fig. 3

8

FIG.6

APPLICATION CIRCUIT

# MEMO

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.