## LOW INPUT OFFSET VOLTAGE C-MOS OPERATIONAL AMPLIFIER

#### **■ GENERAL DESCRIPTION**

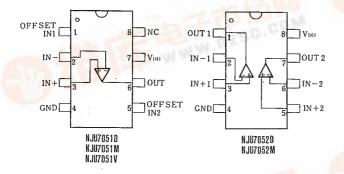

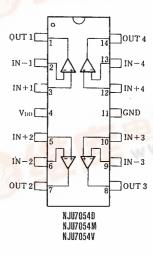

The NJU7051, 52 and 54 are single, dual and quad C-MOS Operational Amplifiers operated on a single-power-supply, low voltage and low operating current.

The input offset voltage is lower than 2mV, and the input bias current is as low as less than IpA, consequently the very small signal around the ground level can be amplified.

The minimum operating voltage is 1V and the output stage permits output signal to swing between both of the supply rails.

Furthermore, the operating current is also as low as 15  $\mu$ A(typ) per circuit, therefore it can be applied especially to battery operated items.

#### **FEATURES**

- Single-Power-Supply

- Low Input Offset Voltage

- Wide Operating Voltage

- Wide Output Swing Range

- Low Operating Current

- Low Bias Current

- Internal Compensation Capacitor

- External Offset Null Adjustment (Only NJU7051)

- Package Outline

DIP/DMP/SSOP 8 (NJU7051)

DIP/DMP 8 (NJU7052)

(Vom=2.94V typ. at VDD=3V)

$(V_{10}=2mVmax)$

$(V_{DD=1} \sim 16V)$

(15 µA/circuit)

(I<sub>IB</sub>=IpA)

DIP/DMP/SSOP 14 (NJU7054)

C-MOS Technology

## PIN CONFIGURATION

### ■ PACKAGE OUTLINE

\*IN1,IN2 are only for NJU7051(NJU7052/54 don't have these terminals).

4

### **■ ABSOLUTE MAXIMUM RATINGS**

(Ta=25℃)

| PARAMETER                  | SYMBOL           | RATINGS        | UNIT |

|----------------------------|------------------|----------------|------|

| Supply Voltage             | V <sub>DD</sub>  | 18             | V    |

| Differential Input Voltage | V <sub>ID</sub>  | ±18 *1         | V    |

| Common Mode Input Voitage  | Vic              | -0.3~18        | V    |

| Power Dissipation          | Po               | (DIP14) 700    | mW   |

|                            |                  | (DIP8) 500     |      |

|                            |                  | (DMP8,14) 300  |      |

|                            |                  | (SSOP8,14) 300 |      |

| Operating Temperature      | Topr             | 20~+75         | r    |

| Storage Temperature        | T <sub>stg</sub> | -40~+125       | °C   |

<sup>\*</sup> 1) If the supply voltage ( $V_{DD}$ ) is less than 18V, the input voltage must not over the  $V_{DD}$  level though 18V is limit specified.

### **■ ELECTRICAL CHARACTERISTICS**

$(Ta=25^{\circ}C, V_{DD}=10V, R_L=\infty)$

| PARAMETER                       | SYMBOL           | CONDITIONS                      | MIN. | TYP. | MAX. | UNIT  |

|---------------------------------|------------------|---------------------------------|------|------|------|-------|

| Input Offset Voltage            | Vio              | R <sub>S</sub> =50 Ω            |      |      | 2    | mV    |

| Input Offset Current            | .I <sub>IO</sub> |                                 |      | 1    |      | pA    |

| Input Bias Current              | I <sub>fB</sub>  |                                 |      | 1    |      | pA    |

| Input Impedance                 | Rin              |                                 |      | 1    |      | TΩ    |

| Large Signal Voltage Gain       | Av               |                                 | 80   | 90   |      | dB    |

| Input Common Mode Voltage Range | Viem             |                                 | 0~2  |      |      | V     |

| Maximum Output Swing Voltage    | Vом              | $R_L=1M\Omega$                  | 2.90 | 2.94 |      | V     |

| Common Mode Rejection Ratio     | CMR              |                                 | 60   | 70   |      | dB    |

| Supply Voltage Rejection Ratio  | SVR              |                                 | 60   | 70   |      | dB    |

| Operating Current / Circuit     | I <sub>DD</sub>  |                                 |      | 15   | 25   | μΑ    |

| Slew Rate                       | SR               |                                 |      | 0.05 |      | V/ μs |

| Unity Gain Bandwidth            | Fı               | Av=40dB<br>C <sub>L</sub> =10pF |      | 0.1  |      | MHz   |

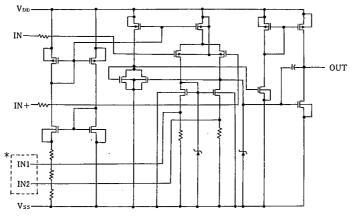

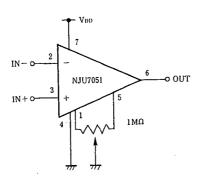

#### ■ OFFSET ADJUSTMENT CIRCUIT (ONLY FOR NJU7051)

# NJU7051/52/54

# **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.