- Open Drain Output

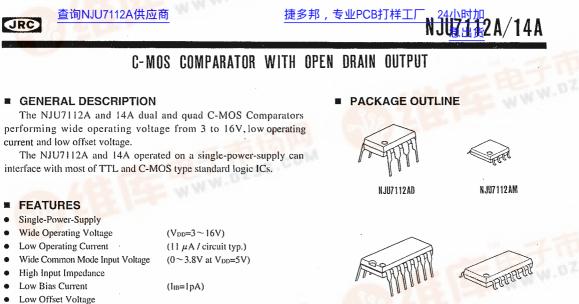

- Package Outline

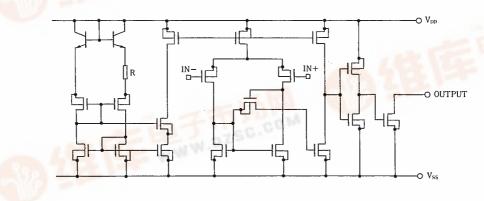

- C-MOS Technology

- **EQUIVALENT CIRCUIT**

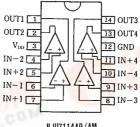

N.IU7114AD

NJU7112AD/AM

**PIN CONFIGURATION**

DIP/DMP 8 (NJU7112A) DIP/DMP 14 (NJU7114A)

NJU7114AM

5

# NJU7112A/14A

| PARAMETER                  | SYMBOL | RATINGS     | UNIT       |  |

|----------------------------|--------|-------------|------------|--|

| Supply Voltage             | VDD    | 18          | v          |  |

| Differential Input Voltage | Vid    | ±18 (Note1) | v          |  |

| Input Voltage              | Vı     | 18          | v          |  |

| Output Voltage             | Vo     | 18          | . <b>V</b> |  |

| Output Current             | Io     | 20          | mA         |  |

| Power Dissipation          | Ръ     | (DIP8) 500  | mW         |  |

|                            |        | (DIP14) 700 |            |  |

|                            |        | (DMP8) 300  |            |  |

|                            |        | (DMP14) 300 |            |  |

| Operating Temperature      | Topr   | 0~+70       | C          |  |

| Storage Temperature        | Tstg   | -40~+125    | °C         |  |

(Note1) If the supply voltage (VDD) is less than 18V, the input voltage must not over the VDD level though 18V is limit specified.

### ELECTRICAL CHARACTERISTICS

|                                 | SYMBOL | CONDITIONS                                 | NJU7112A |      |      | NJU7114A |      |      |      |

|---------------------------------|--------|--------------------------------------------|----------|------|------|----------|------|------|------|

| PARAMETER                       |        |                                            | MIN      | TYP  | MAX  | MIN      | TYP  | MAX  | UNIT |

| Operating Voltage               | VDD    |                                            | 3        | -    | 16   | 3        | -    | 16   | v    |

| Input Offset Voltage            | Vio    | VIC=VICMin (Note2)                         | -        | 1.4  | 12   |          | 1.4  | 12   | mV   |

| Input Offset Current            | Ію     |                                            | _        | 1    | —    | —        | 1    | -    | pА   |

| Input Bias Current              | Ів     |                                            | -        | 1    |      | -        | . 1  | -    | pA   |

| Input Common Mode Voltage Range | VICM   |                                            | 0        | -    | 3.8  | 0        | -    | 3.8  | v    |

| High Level Output Current       | Іон    | V <sub>1D</sub> =+1V, V <sub>OH</sub> =+5V | —        | 2    | 40   | -        | 2    | 40   | nA   |

| Low Level Output Voltage        | Vol    | VID=+1V, IoL=+6mA                          | -        | 0.35 | 0.40 | _        | 0.35 | 0.40 | v    |

| Common Mode Rejection Ratio     | CMR    | VIC=VICMin                                 |          | 71   | —    | 1        | 75   | —    | dB   |

| Supply Voltage Rejection Ratio  | SVR    | V <sub>DD</sub> =5~10V                     | -        | 80   | -    | -        | 85   | _    | dB   |

| Operating Current               | IDD    | No Load, Vo=0V                             |          | 22   | 40   | —        | 44   | 80   | μA   |

(Note2) This condition is available for operating voltage V<sub>DD</sub>=5~10V and driving voltage is over 4.5V or under 0.3V.

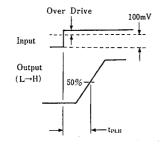

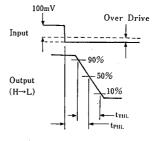

### SWITCHING CHARACTERISTICS

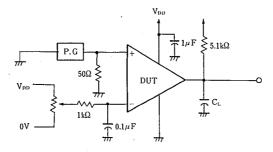

(Ta=25°C, VDD=5V f=10kHz, CL=15pF)

(Ta=25°C, VDD=5V)

| PARAMETER                     | CYMPOL | SYMBOL CONDITIONS   |                |                | NJU7112A |     | NJU7114A |      |     |      |

|-------------------------------|--------|---------------------|----------------|----------------|----------|-----|----------|------|-----|------|

|                               | SIMBOL |                     |                | MIN            | ТҮР      | MAX | MIN      | ТҮР  | MAX | UNIT |

| Propagation Delay             | tPHL   | V <sub>IC</sub> =0V | Over Drive≃5mV | -              | 2.7      | -   | -        | 2.9  |     | μs   |

| High to Low                   |        |                     | TTL level step | —              | 0.16     | -   |          | 0.16 | -   |      |

| Propagation Delay             |        | Vic=0V              | Over Drive=5mV | -              | 1.5      | -   | —        | 1.5  | _   |      |

| Low to High                   | tPLH . |                     | VIC=0V         | TTL level step | -        | 0.7 | -        |      | 0.8 | -    |

| Output Signal<br>Falling Time | ITHL   | Over Drive≍50mV     |                | -              | 20       | -   | _        | 20   | _   | ns   |

#### MEASUREMENT CIRCUIT

## TIMING WAVEFORM

15

# NJU7112A/14A

# MEMO

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

- Now Janan Padia Ca Std -