查询K4D263238F供应商

捷多邦,专业PCB打样工厂,24小时加急出货

# K4D263238F

# 128M DDR SDRAM

# 128Mbit DDR SDRAM

Double Data Rate Synchronous DRAM with Bi-directional Data Strobe and DLL

Revision 1.1

May 2003

Rev 1.1 (May 2003)

# 128M DDR SDRAM

# **Revision History**

Revision 1.1 (May 30, 2003) • Added Lead Free package part number in the datasheet.

Revision 1.0 (April 29, 2003) • Define DC spec.

Revision 0.0 (January 20, 2003)- Target spec

• Define target spec.

# 128M DDR SDRAM

# 1M x 32Bit x 4 Banks Double Data Rate Synchronous DRAM with Bi-directional Data Strobe and DLL

# FEATURES

- $2.5V \pm 5\%$  power supply for device operation

- + 2.5V  $\pm$  5% power supply for I/O interface

- SSTL\_2 compatible inputs/outputs

- 4 banks operation

- MRS cycle with address key programs

- -. Read latency 3 (clock)

- -. Burst length (2, 4, 8 and Full page)

- -. Burst type (sequential & interleave)

- Full page burst length for sequential burst type only

- Start address of the full page burst should be even

- All inputs except data & DM are sampled at the positive going edge of the system clock

- Differential clock input

- No Write Interrupted by Read function

- Data I/O transactions on both edges of Data strobe

- DLL aligns DQ and DQS transitions with Clock transition

- Edge aligned data & data strobe output

- Center aligned data & data strobe input

- DM for write masking only

- Auto & Self refresh

- 32ms refresh period (4K cycle)

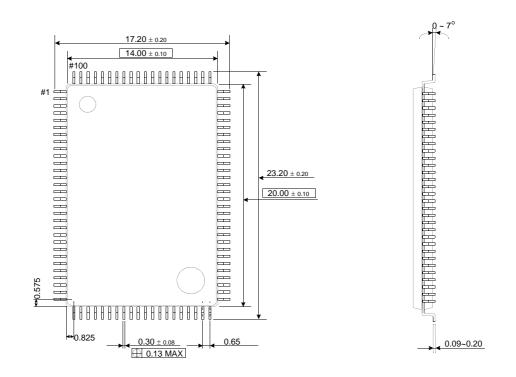

- 100pin TQFP package

- Maximum clock frequency up to 250MHz

- Maximum data rate up to 500Mbps/pin

#### **ORDERING INFORMATION**

| Part NO.        | Max Freq. | Max Data Rate | Interface | Package  |

|-----------------|-----------|---------------|-----------|----------|

| K4D263238F-QC40 | 250MHz    | 500Mbps/pin   |           | 100 TQFP |

| K4D263238F-QC50 | 200MHz    | 400Mbps/pin   | - SSTL_2  |          |

K4D263238F-UC is the Lead Free package part number.

# **GENERAL DESCRIPTION**

# FOR 1M x 32Bit x 4 Bank DDR SDRAM

The K4D263238F is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x 1,048,576 words by 32 bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 2.0GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

# 128M DDR SDRAM

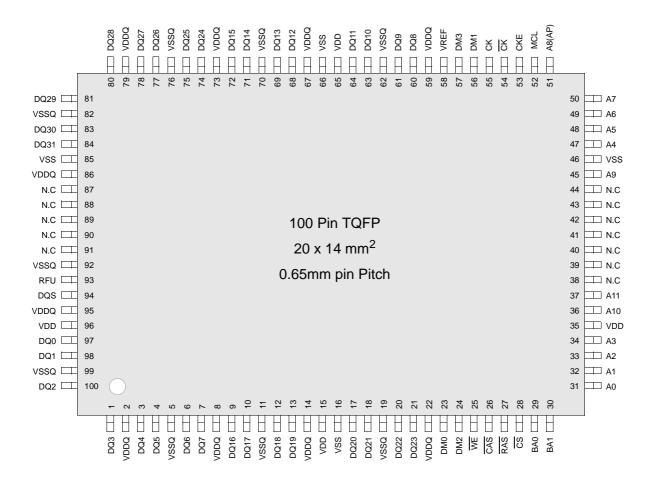

#### **PIN CONFIGURATION (Top View)**

#### **PIN DESCRIPTION**

| CK, CK | Differential Clock Input | BA0, BA1   | Bank Select Address |

|--------|--------------------------|------------|---------------------|

| CKE    | Clock Enable             | A0 ~A11    | Address Input       |

| CS     | Chip Select              | DQ0 ~ DQ31 | Data Input/Output   |

| RAS    | Row Address Strobe       | Vdd        | Power               |

| CAS    | Column Address Strobe    | Vss        | Ground              |

| WE     | Write Enable             | Vddq       | Power for DQ's      |

| DQS    | Data Strobe              | Vssq       | Ground for DQ's     |

| DMi    | Data Mask                | MCL        | Must Connect Low    |

| RFU    | Reserved for Future Use  |            |                     |

# 128M DDR SDRAM

# INPUT/OUTPUT FUNCTIONAL DESCRIPTION

| Symbol               | Туре             | Function                                                                                                                                                                                     |

|----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, <del>CK</del> *1 | Input            | The differential system clock Input.<br>All of the inputs are sampled on the rising edge of the clock except<br>DQ's and DM's that are sampled on both edges of the DQS.                     |

| CKE                  | Input            | Activates the CK signal when high and deactivates the CK signal when low. By deactivating the clock, CKE low indicates the Power down mode or Self refresh mode.                             |

| CS                   | Input            | CS enables the command decoder when low and disabled the com-<br>mand decoder when high. When the command decoder is disabled,<br>new commands are ignored but previous operations continue. |

| RAS                  | Input            | Latches row addresses on the positive going edge of the CK with RAS low. Enables row access & precharge.                                                                                     |

| CAS                  | Input            | Latches column addresses on the positive going edge of the CK with CAS low. Enables column access.                                                                                           |

| WE                   | Input            | Enables write operation and row precharge.<br>Latches data in starting from CAS, WE active.                                                                                                  |

| DQS                  | Input/Output     | Data input and output are synchronized with both edge of DQS.                                                                                                                                |

| DM0 ~ DM3            | Input            | Data In mask. Data In is masked by DM Latency=0 when DM is high<br>in burst write. DM0 for DQ0 ~ DQ7, DM1 for DQ8 ~ DQ15, DM2 for<br>DQ16 ~ DQ23, DM3 for DQ24 ~ DQ31.                       |

| DQ0 ~ DQ31           | Input/Output     | Data inputs/Outputs are multiplexed on the same pins.                                                                                                                                        |

| BA0, BA1             | Input            | Selects which bank is to be active.                                                                                                                                                          |

| A0 ~ A11             | Input            | Row/Column addresses are multiplexed on the same pins.<br>Row addresses : RA0 ~ RA11, Column addresses : CA0 ~ CA7.<br>Column address CA8 is used for auto precharge.                        |

| VDD/VSS              | Power Supply     | Power and ground for the input buffers and core logic.                                                                                                                                       |

| VDDQ/VSSQ            | Power Supply     | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                  |

| Vref                 | Power Supply     | Reference voltage for inputs, used for SSTL interface.                                                                                                                                       |

| MCL                  | Must Connect Low | Must connect Low                                                                                                                                                                             |

\*1 : The timing reference point for the differential clocking is the cross point of CK and  $\overline{CK}$ . For any applications using the single ended clocking, apply VREF to  $\overline{CK}$  pin.

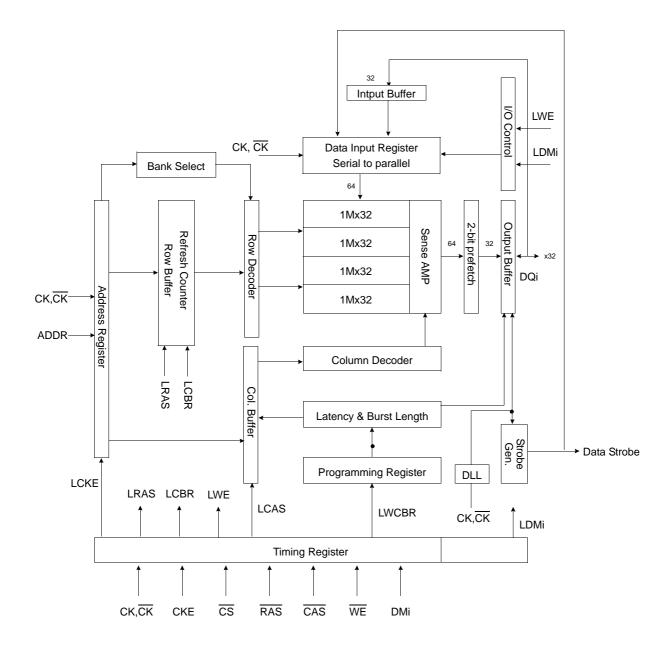

#### BLOCK DIAGRAM (1Mbit x 32I/O x 4 Bank)

# 128M DDR SDRAM

#### FUNCTIONAL DESCRIPTION

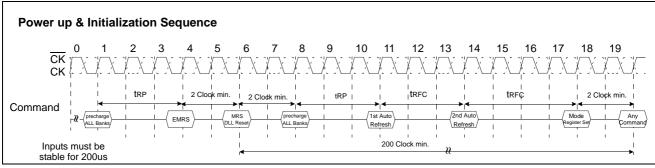

#### Power-Up Sequence

#### DDR SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations.

- 1. Apply power and keep CKE at low state (All other inputs may be undefined)

- Apply VDD before VDDQ .

- Apply VDDQ before VREF & VTT

- 2. Start clock and maintain stable condition for minimum 200us.

- 3. The minimum of 200us after stable power and clock(CK, CK), apply NOP and take CKE to be high.

- 4. Issue precharge command for all banks of the device.

- 5. Issue a EMRS command to enable DLL

- \*1 6. Issue a MRS command to reset DLL. The additional 200 clock cycles are required to lock the DLL.

- \*1,2 7. Issue precharge command for all banks of the device.

- 8. Issue at least 2 or more auto-refresh commands.

- 9. Issue a mode register set command with A8 to low to initialize the mode register.

- \*1 The additional 200cycles of clock input is required to lock the DLL after enabling DLL.

- \*2 Sequence of 6&7 is regardless of the order.

\* When the operating frequency is changed, DLL reset should be required again. After DLL reset again, the minimum 200 cycles of clock input is needed to lock the DLL.

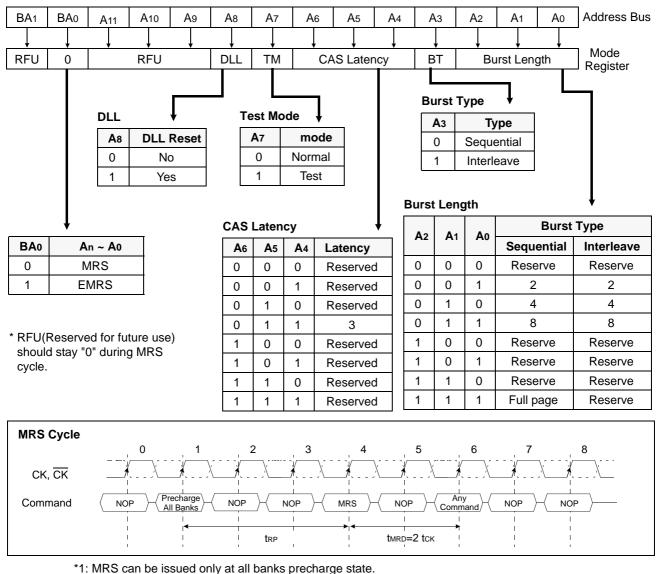

#### MODE REGISTER SET(MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs CAS latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper operation. The mode register is written by asserting low on CS, RAS, CAS and WE(The DDR SDRAM should be in active mode with CKE already high prior to writing into the mode register). The state of address pins A0 ~ A11 and BA0, BA1 in the same cycle as CS, RAS, CAS and WE going low is written in the mode register. Minimum two clock cycles are requested to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A0 ~ A2, addressing mode uses A3, CAS latency(read latency from column address) uses A4 ~ A6. A7 is used for test mode. A8 is used for DLL reset. A7,A8, BA0 and BA1 must be set to low for normal MRS operation. Refer to the table for specific codes for various burst length, addressing modes and CAS latencies.

\*2: Minimum tRP is required to issue MRS command.

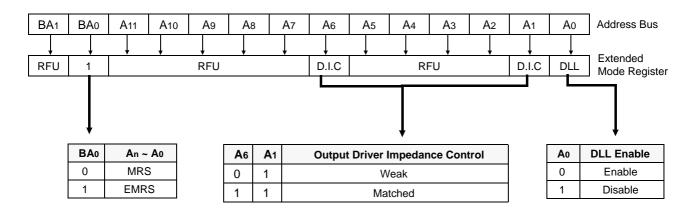

# EXTENDED MODE REGISTER SET(EMRS)

The extended mode register stores the data for enabling or disabling DLL and selecting output driver strength. The default value of the extended mode register is not defined, therefore the extend mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on CS, RAS, CAS, WE and high on BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins A0, A2 ~ A5, A7 ~ A11 and BA1 in the same cycle as CS, RAS, CAS and WE going low are written in the extended mode register. A1 and A6 are used for setting driver strength to weak or matched impedance. Two clock cycles are required to complete the write operation in the extended mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. "High" on BA0 is used for EMRS. All the other address pins except A0,A1,A6 and BA0 must be set to low for proper EMRS operation. Refer to the table for specific codes.

\* RFU(Reserved for future use) should stay "0" during EMRS cycle.

#### Figure 7. Extend Mode Register set

# 128M DDR SDRAM

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol    | Value      | Unit |

|---------------------------------------|-----------|------------|------|

| Voltage on any pin relative to Vss    | Vin, Vout | -0.5 ~ 3.6 | V    |

| Voltage on VDD supply relative to Vss | Vdd       | -1.0 ~ 3.6 | V    |

| Voltage on VDD supply relative to Vss | Vddq      | -0.5 ~ 3.6 | V    |

| Storage temperature                   | Тѕтс      | -55 ~ +150 | °C   |

| Power dissipation                     | Po        | 1.8        | W    |

| Short circuit current                 | los       | 50         | mA   |

Note : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

#### POWER & DC OPERATING CONDITIONS(SSTL\_2 In/Out)

Recommended operating conditions(Voltage referenced to Vss=0V, TA=0 to 65°C)

| Parameter                 | Symbol | Min       | Тур  | Max       | Unit | Note        |

|---------------------------|--------|-----------|------|-----------|------|-------------|

| Device Supply voltage     | Vdd    | 2.375     | 2.50 | 2.625     | V    | 1           |

| Output Supply voltage     | Vddq   | 2.375     | 2.50 | 2.625     | V    | 1           |

| Reference voltage         | Vref   | 0.49*Vddq | -    | 0.51*Vddq | V    | 2           |

| Termination voltage       | Vtt    | Vref-0.04 | Vref | Vref+0.04 | V    | 3           |

| Input logic high voltage  | Viн    | VREF+0.15 | -    | VDDQ+0.30 | V    | 4           |

| Input logic low voltage   | VIL    | -0.30     | -    | Vref-0.15 | V    | 5           |

| Output logic high voltage | Vон    | Vtt+0.76  | -    | -         | V    | Iон=-15.2mA |

| Output logic low voltage  | Vol    | -         | -    | Vtt-0.76  | V    | IOL=+15.2mA |

| Input leakage current     | lı∟    | -5        | -    | 5         | uA   | 6           |

| Output leakage current    | IOL    | -5        | -    | 5         | uA   | 6           |

Note: 1. Under all conditions VDDQ must be less than or equal to VDD.

- 2. VREF is expected to equal 0.50\*VDDQ of the transmitting device and to track variations in the DC level of the same. Peak to peak noise on the VREF may not exceed <u>+</u> 2% of the DC value. Thus, from 0.50\*VDDQ, VREF is allowed <u>+</u> 25mV for DC error and an additional <u>+</u> 25mV for AC noise.

- 3. Vtt of the transmitting device must track VREF of the receiving device.

- 4. VIH(max.)= VDDQ +1.5V for a pulse and it which can not be greater than 1/3 of the cycle rate.

- 5. VIL(min.)= -1.5V for a pulse width and it can not be greater than 1/3 of the cycle rate.

- 6. For any pin under test input of  $0V \le VIN \le VDD$  is acceptable. For all other pins that are not under test VIN=0V.

# 128M DDR SDRAM

#### **DC CHARACTERISTICS**

Recommended operating conditions Unless Otherwise Noted, TA=0 to 65°C)

| Devenueter                                          | 0h.al  | Test Osmalitism                                                                                                      | Vers | sion | Unit | Note |

|-----------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Parameter                                           | Symbol | Test Condition                                                                                                       | -40  | -50  |      |      |

| Operating Current<br>(One Bank Active)              | ICC1   | Burst Lenth=2 trc $\geq$ trc(min)<br>IoL=0mA, tcc= tcc(min)                                                          | 250  | 215  | mA   | 1    |

| Precharge Standby Current<br>in Power-down mode     | ICC2P  | $CKE \le VIL(max), tcc=tcc(min)$                                                                                     | 60   | 55   | mA   |      |

| Precharge Standby Current<br>in Non Power-down mode | ICC2N  | $\label{eq:cke} \begin{split} CKE &\geq ViH(min), \ \overline{CS} \geq ViH(min), \\ tcc &= tcc(min). \end{split}$    | 90   | 80   | mA   |      |

| Active Standby Current power-down mode              | ІссзР  | $CKE \le VIL(max), tcc=tcc(min)$                                                                                     | 110  | 95   | mA   |      |

| Active Standby Current in<br>in Non Power-down mode | Icc3N  | $\label{eq:cke} \begin{split} CKE &\geq VIH(min), \ \overline{CS} \geq VIH(min), \\ tcc &= tcc(min) \ . \end{split}$ | 200  | 170  | mA   |      |

| Operating Current<br>(Burst Mode)                   | ICC4   | IoL=0mA ,tcc= tcc(min), Page<br>Burst, All Banks activated.                                                          | 500  | 480  | mA   |      |

| Refresh Current                                     | ICC5   | $t_{RC} \ge t_{RFC}(min)$                                                                                            | 240  | 220  | mA   | 2    |

| Self Refresh Current                                | ICC6   | $CKE \leq 0.2V$                                                                                                      | 3    | 3    | mA   |      |

Note: 1. Measured with outputs open.

2. Refresh period is 32ms.

# AC INPUT OPERATING CONDITIONS

Recommended operating conditions(Voltage referenced to Vss=0V, VDD/ VDDQ=2.5V± 5%, TA=0 to 65°C)

| Parameter                                                  | Symbol | Min          | Тур | Max          | Unit | Note |

|------------------------------------------------------------|--------|--------------|-----|--------------|------|------|

| Input High (Logic 1) Voltage; DQ                           | Vih    | Vref+0.35    | -   | -            | V    |      |

| Input Low (Logic 0) Voltage; DQ                            | VIL    | -            | -   | Vref-0.35    | V    |      |

| Clock Input Differential Voltage; CK and CK                | Vid    | 0.7          | -   | VDDQ+0.6     | V    | 1    |

| Clock Input Crossing Point Voltage; CK and $\overline{CK}$ | Vix    | 0.5*Vddq-0.2 | -   | 0.5*Vddq+0.2 | V    | 2    |

Note : 1. VID is the magnitude of the difference between the input level on CK and the input level on  $\overline{CK}$

2. The value of Vix is expected to equal 0.5\*VDDQ of the transmitting device and must track variations in the DC level of the same

# 128M DDR SDRAM

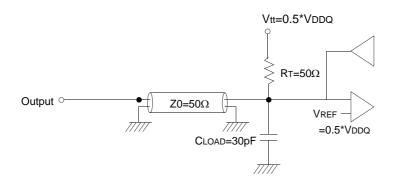

#### AC OPERATING TEST CONDITIONS (VDD/ VDDQ=2.5V±5%, TA= 0 to 65°C)

| Parameter                                        | Value               | Unit | Note |

|--------------------------------------------------|---------------------|------|------|

| Input reference voltage for CK(for single ended) | 0.50*VDDQ           | V    |      |

| CK and CK signal maximum peak swing              | 1.5                 | V    |      |

| CK signal minimum slew rate                      | 1.0                 | V/ns |      |

| Input Levels(VIH/VIL)                            | Vref+0.35/Vref-0.35 | V    |      |

| Input timing measurement reference level         | VREF                | V    |      |

| Output timing measurement reference level        | Vtt                 | V    |      |

| Output load condition                            | See Fig.1           |      |      |

(Fig. 1) Output Load Circuit

#### CAPACITANCE (VDD=2.5V, TA= 25°C, f=1MHz)

| Parameter                                     | Symbol | Min | Мах | Unit |

|-----------------------------------------------|--------|-----|-----|------|

| Input capacitance( CK, CK)                    | CIN1   | 1.0 | 5.0 | pF   |

| Input capacitance(Ao~A11, BAo~BA1)            | CIN2   | 1.0 | 4.0 | pF   |

| Input capacitance<br>( CKE, CS, RAS,CAS, WE ) | Сімз   | 1.0 | 4.0 | pF   |

| Data & DQS input/output capacitance(DQ0~DQ31) | Соит   | 1.0 | 6.0 | pF   |

| Input capacitance(DM0 ~ DM3)                  | CIN4   | 1.0 | 6.0 | pF   |

# **DECOUPLING CAPACITANCE GUIDE LINE**

Recommended decoupling capacitance added to power line at board.

| Parameter                                    | Symbol | Value      | Unit |

|----------------------------------------------|--------|------------|------|

| Decoupling Capacitance between VDD and Vss   | CDC1   | 0.1 + 0.01 | uF   |

| Decoupling Capacitance between VDDQ and VSSQ | CDC2   | 0.1 + 0.01 | uF   |

**Note :** 1. VDD and VDDQ pins are separated each other.

All VDD pins are connected in chip. All VDDQ pins are connected in chip.

2. Vss and Vssq pins are separated each other

All Vss pins are connected in chip. All Vssq pins are connected in chip.

# 128M DDR SDRAM

# AC CHARACTERISTICS

| Devenueter                      | Quert at | -            | 40   | -5           | 0     | 11                                                                                          |      |

|---------------------------------|----------|--------------|------|--------------|-------|---------------------------------------------------------------------------------------------|------|

| Parameter                       | Symbol   | Min          | Max  | Min          | Max   | Unit<br>ns<br>tCK<br>tCK<br>ns<br>ns<br>ns<br>tCK<br>tCK<br>tCK<br>tCK<br>tCK<br>tCK<br>tCK | Note |

| CK cycle time CL=3              | tCK      | 4.0          | 10   | 5.0          | 10    | ns                                                                                          |      |

| CK high level width             | tCH      | 0.45         | 0.55 | 0.45         | 0.55  | tCK                                                                                         |      |

| CK low level width              | tCL      | 0.45         | 0.55 | 0.45         | 0.55  | tCK                                                                                         |      |

| DQS out access time from CK     | tDQSCK   | -0.6         | 0.6  | -0.7         | +0.7  | ns                                                                                          |      |

| Output access time from CK      | tAC      | -0.6         | 0.6  | -0.7         | +0.7  | ns                                                                                          |      |

| Data strobe edge to Dout edge   | tDQSQ    | -            | 0.4  | -            | +0.45 | ns                                                                                          | 1    |

| Read preamble                   | tRPRE    | 0.9          | 1.1  | 0.9          | 1.1   | tCK                                                                                         |      |

| Read postamble                  | tRPST    | 0.4          | 0.6  | 0.4          | 0.6   | tCK                                                                                         |      |

| CK to valid DQS-in              | tDQSS    | 0.85         | 1.15 | 0.8          | 1.2   | tCK                                                                                         |      |

| DQS-In setup time               | tWPRES   | 0            | -    | 0            | -     | ns                                                                                          |      |

| DQS-in hold time                | tWPREH   | 0.35         | -    | 0.25         | -     | tCK                                                                                         |      |

| DQS write postamble             | tWPST    | 0.4          | 0.6  | 0.4          | 0.6   | tCK                                                                                         |      |

| DQS-In high level width         | tDQSH    | 0.4          | 0.6  | 0.4          | 0.6   | tCK                                                                                         |      |

| DQS-In low level width          | tDQSL    | 0.4          | 0.6  | 0.4          | 0.6   | tCK                                                                                         |      |

| Address and Control input setup | tIS      | 0.9          | -    | 1.0          | -     | ns                                                                                          |      |

| Address and Control input hold  | tIH      | 0.9          | -    | 1.0          | -     | ns                                                                                          |      |

| DQ and DM setup time to DQS     | tDS      | 0.4          | -    | 0.45         | -     | ns                                                                                          |      |

| DQ and DM hold time to DQS      | tDH      | 0.4          | -    | 0.45         | -     | ns                                                                                          |      |

|                                 |          | tCLmin       |      | tCLmin       |       |                                                                                             |      |

| Clock half period               | tHP      | or<br>tCHmin | -    | or<br>tCHmin | -     | ns                                                                                          | 1    |

| Data output hold time from DQS  | tQH      | tHP-0.4      | -    | tHP-0.45     | -     | ns                                                                                          | 1    |

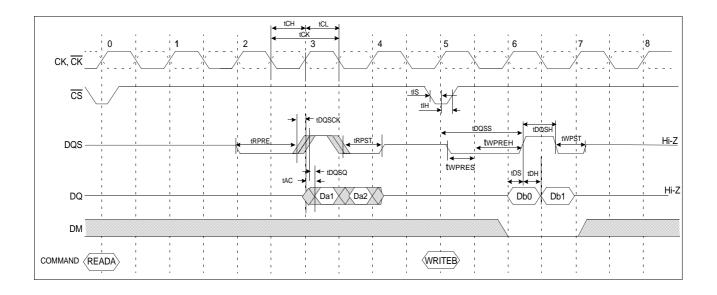

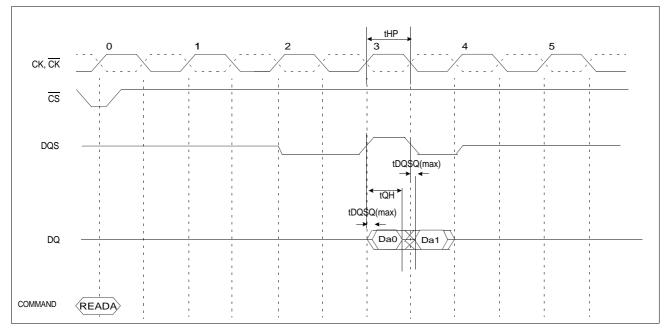

# Simplified Timing @ BL=2, CL=3

Note 1 :

- The JEDEC DDR specification currently defines the output data valid window(tDV) as the time period when the data strobe and all data associated with that data strobe are coincidentally valid.

- The previously used definition of tDV(=0.35tCK) artificially penalizes system timing budgets by assuming the worst case output valid window even then the clock duty cycle applied to the device is better than 45/55%

- A new AC timing term, tQH which stands for data output hold time from DQS is defined to account for clock duty cycle variation and replaces tDV

- tQHmin = tHP-X where

- . tHP=Minimum half clock period for any given cycle and is defined by clock high or clock low time(tCH,tCL)

- . X=A frequency dependent timing allowance account for tDQSQmax

# tQH Timing (CL3, BL2)

# 128M DDR SDRAM

# **AC CHARACTERISTICS (I)**

| Parameter                                      | Cumhal   | -4       | 10   |          | 50   | 11-24 | Nete |

|------------------------------------------------|----------|----------|------|----------|------|-------|------|

|                                                | Symbol - | Min      | Max  | Min      | Max  | Unit  | Note |

| Row cycle time                                 | tRC      | 15       | -    | 12       | -    | tCK   |      |

| Refresh row cycle time                         | tRFC     | 17       | -    | 14       | -    | tCK   |      |

| Row active time                                | tRAS     | 10       | 100K | 8        | 100K | tCK   |      |

| RAS to CAS delay for Read                      | tRCDRD   | 5        | -    | 4        | -    | tCK   |      |

| RAS to CAS delay for Write                     | tRCDWR   | 3        |      | 2        |      | tCK   |      |

| Row precharge time                             | tRP      | 5        | -    | 4        | -    | tCK   |      |

| Row active to Row active                       | tRRD     | 3        | -    | 2        | -    | tCK   |      |

| Last data in to Row precharge                  | tWR      | 3        | -    | 2        | -    | tCK   | 1    |

| Last data in to Read command                   | tCDLR    | 2        | -    | 2        | -    | tCK   | 1    |

| Col. address to Col. address                   | tCCD     | 1        | -    | 1        | -    | tCK   |      |

| Mode register set cycle time                   | tMRD     | 2        | -    | 2        | -    | tCK   |      |

| Auto precharge write recovery + Pre-<br>charge | tDAL     | 8        | -    | 6        | -    | tCK   |      |

| Exit self refresh to read command              | tXSR     | 200      | -    | 200      | -    | tCK   |      |

| Power down exit time                           | tPDEX    | 1tCK+tIS | -    | 1tCK+tIS | -    | ns    |      |

| Refresh interval time                          | tREF     | 7.8      | -    | 7.8      | -    | us    |      |

Note :1 For normal write operation, even numbers of Din are to be written inside DRAM

(Unit : Number of Clock)

# **AC CHARACTERISTICS (II)**

#### K4D263238F-QC40

| Frequency        | Cas Latency | tRC | tRFC | tRAS | tRCDRD | tRCDWR | tRP | tRRD | tDAL | Unit |

|------------------|-------------|-----|------|------|--------|--------|-----|------|------|------|

| 250MHz ( 4.0ns ) | 3           | 15  | 17   | 10   | 5      | 3      | 5   | 3    | 8    | tCK  |

| 200MHz ( 5.0ns ) | 3           | 12  | 14   | 8    | 4      | 2      | 4   | 2    | 6    | tCK  |

#### K4D623238F-QC50

| Frequency        | Cas Latency | tRC | tRFC | tRAS | tRCDRD | tRCDWR | tRP | tRRD | tDAL | Unit |

|------------------|-------------|-----|------|------|--------|--------|-----|------|------|------|

| 200MHz ( 5.0ns ) | 3           | 12  | 14   | 8    | 4      | 2      | 4   | 2    | 6    | tCK  |

| 183MHz ( 5.5ns ) | 3           | 12  | 14   | 8    | 4      | 2      | 4   | 2    | 6    | tCK  |

| 166MHz ( 6.0ns ) | 3           | 10  | 12   | 7    | 3      | 2      | 3   | 2    | 5    | tCK  |

\* 183/166MHz were supported in K4D263238F-QC50

# 128M DDR SDRAM

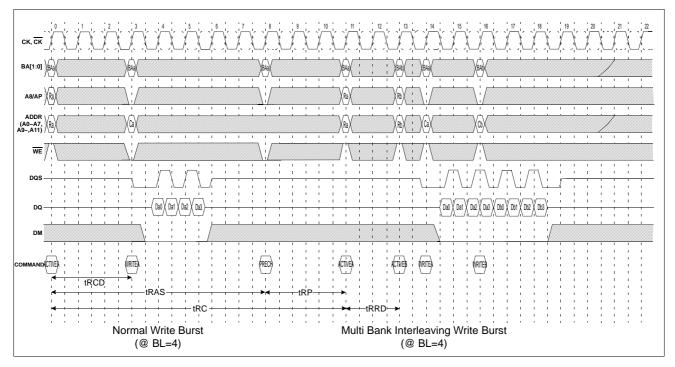

# Simplified Timing(2) @ BL=4, CL=3

# 128M DDR SDRAM

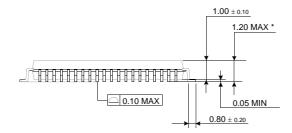

# PACKAGE DIMENSIONS (TQFP)

**Dimensions in Millimeters**