L4963 L4963D

## 1.5A SWITCHING REGULATOR

- 1.5A OUTPUT LOAD CURRENT

- 5.1 TO 36V OUTPUT VOLTAGE RANGE

- DISCONTINUOUS VARIABLE FREQUENCY MODE

- PRECISE (+/-2%) ON CHIP REFERENCE

- VERY HIGH EFFICIENCY

- VERY FEW EXTERNAL COMPONENTS

- NO FREQ. COMPENSATION REQUIRED

- RESET AND POWER FAIL OUTPUT FOR MI-CROPROCESSOR

- INTERNAL CURRENT LIMITING

- THERMAL SHUTDOWN

### **DESCRIPTION**

The L4963 is a monolithic power switching regulator delivering 1.5A at 5.1V. The output voltage is adjustable from 5.1V to 36V, working in discontinuous variable frequency mode. Features of the device include remote inhibit, internal current limiting and thermal protection, reset and power fail outputs for microprocessor.

The L4963 is mounted in a 12+3+3 lead Powerdip (L4963) and SO20 large (L4963D) plastic packages and requires very few external components.

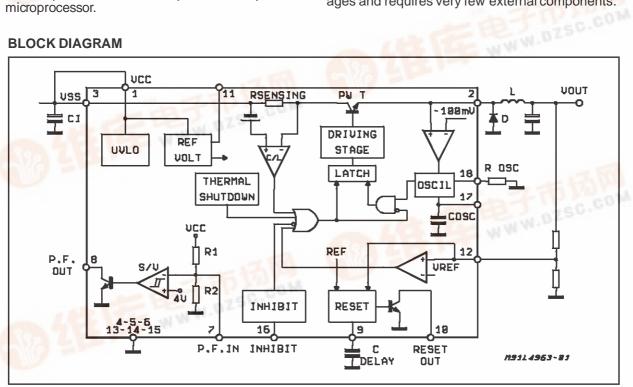

#### **BLOCK DIAGRAM**

June 2000 f.dzsc.com

### **ABSOLUTE MAXIMUM RATINGS**

| Syn                               | nbol                                                                                                              | Parameter                                                                                                                                                   | Value                                                                                                                               | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|

| SO20                              | Powerdip                                                                                                          | - Farameter                                                                                                                                                 | value                                                                                                                               | Onit |

| \                                 | J <sub>i</sub>                                                                                                    | Input Voltage (pin 1 and pin 3 connected togheter)                                                                                                          | 47                                                                                                                                  | V    |

| V <sub>3</sub> -                  | -V <sub>2</sub>                                                                                                   | Input to Output Voltage Difference                                                                                                                          | 47                                                                                                                                  | V    |

| \                                 | /2                                                                                                                | Negative Output DC Voltage                                                                                                                                  | -1                                                                                                                                  | V    |

| \                                 | /2                                                                                                                | Negative Output Peak Voltage at t=0.2 μs, f=50kHz                                                                                                           | <b>-</b> 5                                                                                                                          | V    |

| V <sub>8</sub>                    | V <sub>7</sub>                                                                                                    | Power Fail Input                                                                                                                                            | 25                                                                                                                                  | V    |

| V <sub>9</sub> , V <sub>11</sub>  | V <sub>8</sub> , V <sub>10</sub>                                                                                  | Reset and Power Fail Output                                                                                                                                 | Vi                                                                                                                                  |      |

| V <sub>10</sub>                   | V <sub>9</sub>                                                                                                    | Reset Delay Input                                                                                                                                           | 5.5                                                                                                                                 | V    |

| V <sub>13</sub> , V <sub>18</sub> | V <sub>12</sub> , V <sub>16</sub>                                                                                 | Feedback and Inhibit Inputs                                                                                                                                 | 7                                                                                                                                   | V    |

| V <sub>19</sub> , V <sub>20</sub> | V <sub>17</sub> , V <sub>18</sub>                                                                                 | Oscillator Inputs                                                                                                                                           | 5.5                                                                                                                                 | V    |

| Р                                 | tot                                                                                                               | Total Power Dissipation Tpins $\leq$ 90°C (Power DIP) $(T_{amb} = 70$ °C no copper area on PCB) $(T_{amb} = 70$ °C, $4$ cm <sup>2</sup> copper area on PCB) | al Power Dissipation Tpins ≤ 90°C (Power DIP)  blue = 70°C no copper area on PCB)  1.3  chapter = 70°C, 4cm² copper area on PCB)  2 |      |

| T <sub>ste</sub>                  | $T_{stg}, T_{j}$ Storage & Junction Temperature (Tamb = 70°C 6cm <sup>2</sup> copper area on PCB) -40 to 150 1.45 |                                                                                                                                                             | °C<br>W                                                                                                                             |      |

| Р                                 | tot                                                                                                               | Total Power Dissipation Tpins ≤90°C (SO20L)                                                                                                                 | 4                                                                                                                                   | W    |

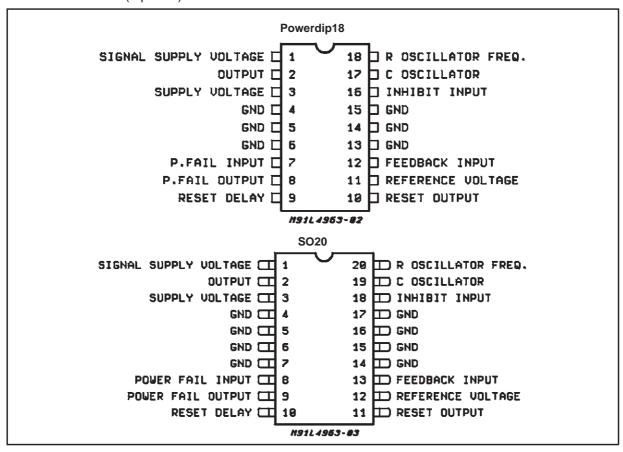

### **PIN CONNECTION** (top view)

### **PIN FUNCTIONS**

| SO20L                        | Power DIP             | Name                  | Description                                                                                                                                                        |

|------------------------------|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                            | 1                     | SIGNAL SUPPLY VOLTAGE | Must be Connected to pin 3                                                                                                                                         |

| 2                            | 2                     | OUTPUT                | Regulator output                                                                                                                                                   |

| 3                            | 3                     | SUPPLY VOLTAGE        | Unregulated voltage input. An internal regulator powers the internal logic.                                                                                        |

| 4, 5, 6, 7<br>14, 15, 16, 17 | 4, 5, 6<br>13, 14, 15 | GROUND                | Common ground terminal                                                                                                                                             |

| 8                            | 7                     | POWER FAILINPUT       | Input of the power fail circuit. The threshold can be modified introducing an external voltage divider between the Supply Voltage and GND.                         |

| 9                            | 8                     | POWER FAILOUTPUT      | Open collector power fail signal output. This output is high when the supply voltage is safe.                                                                      |

| 10                           | 9                     | RESET DELAY           | A capacitor connected between this terminal and ground determines the reset signal delay time.                                                                     |

| 11                           | 10                    | RESET OUTPUT          | Open collector reset signal output. This output is high when the output voltage value is correct.                                                                  |

| 12                           | 11                    | REFERENCE VOLTAGE     | Reference voltage output.                                                                                                                                          |

| 13                           | 12                    | FEEDBACK INPUT        | Feedback terminal of the regulation loop. The output is connected directly to this terminal for 5.1V operation; it is connected via a divider for higher voltages. |

| 18                           | 16                    | INHIBIT INPUT         | TTL level remote inhibit. A logic low level on this input disables the device.                                                                                     |

| 19                           | 17                    | C OSCILLATOR          | Oscillator waveform. A capacitor connected between this terminal and ground modifies the maximum oscillator frequency.                                             |

| 20                           | 18                    | R OSCILLATOR FREQ.    | A resistor connected between this terminal and ground defines the maximum switching frequency.                                                                     |

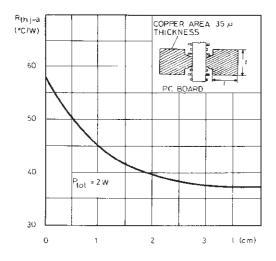

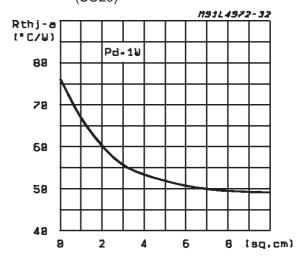

### THERMAL DATA

| Symbol                | Parameter                                  | SO20 | Powerdip | Unit |      |

|-----------------------|--------------------------------------------|------|----------|------|------|

| Rth j-pins            | Thermal Resistance Junction to Pins        | max. | 15       | 12   | °C/W |

| R <sub>th j-amb</sub> | Thermal Resistance Junction to Ambient (*) | max. | 85       | 80   | °C/W |

(\*) See Fig. 28

# CIRCUIT DESCRIPTION (Refer to Block Diagram)

The L4963 is a monolithic stepdown regulator providing 1.5A at 5.1V working in discontinuous variable frequency mode. In normal operation the device resonates at a frequency depending primarily on the inductance value, the input and output voltage and the load current. The maximum switching however can be limited by an internal oscillator, which can be programmed by only one external resistor.

The fondamental regulation loop consists of two comparators, a precision 5.1V on-chip reference and a drive latch. Briefly the operation is as follows: when the choke ends its discharge the catch freewheeling recirculation filter diode begins to come out of forward conduction so the output voltage of the device approaches ground. When the output voltage reaches –0.1V the internal comparator sets the latch and the power stage is turned on. Then the inductor current rises linearly until the voltage sensed at the feedback input reaches the 5.1V reference.

The second comparator then resets the latch and the output stage is turned off. The current in the choke falls linearly until it is fully discharged, then the cycle repeats. Closing the loop directly gives an output voltage of 5.1V. Higher output voltages are

obtained by inserting a voltage divider and this method of control requires no frequency compensation network. At output voltages greater than 5.1V the available output current must be derated due to the increased power dissipation of the device.

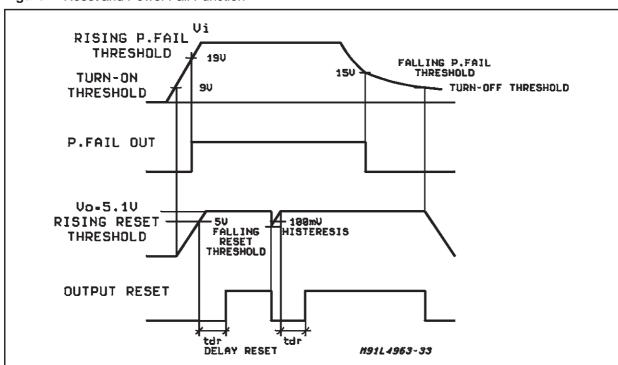

Output overload protection is provided by an internal current limiter. The load current is sensed by a on-chip metal resistor connected to a comparator which resets the latch and turns off the power stage in overload condition. The reset circuits (see fig. 1) generates an output high signal when the output voltage value is correct. It has an open collector output and the output signal delay time can be programmed with an external capacitor. A powerfail circuit is also available and is used to monitor the supply voltage. Its output goes high when the supply voltage reaches a pre-programmed treshold set by a voltage divider to its input from the supply to ground. With the input left open the threshold is approximately equal to 5.1V. The output of the power fail is an open collector.

A TTL level inhibit is provided for applications such as remote on/off control. This input is activated by a low logic level and disables circuits operation.

The thermal overload circuit disables the device when the junction temperature is about 150°C and has hysteresis to prevent unstable conditions.

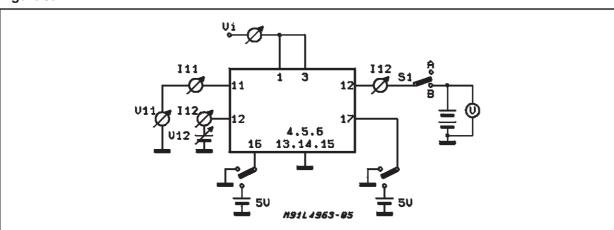

Figure 1: Reset and Power Fail Function

**ELECTRICAL CHARACTERISTIC** (Refer to the test circuit  $V_i = 30 \text{V T}_j = 25 ^{\circ}\text{C}$  unless otherwise specified)

|                         | Parameter                                     | Test Conditions                                           |                         | Min.             | Тур. | Max. | Unit  | Fig. |  |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|-------------------------|------------------|------|------|-------|------|--|

| DYNAMIC CHARACTERISTICS |                                               |                                                           |                         |                  |      |      |       |      |  |

| Vo                      | Output Voltage Range                          | V <sub>i</sub> = 46V I <sub>o</sub> :                     | = 0.5A                  | V <sub>ref</sub> |      | 36   | V     | 2    |  |

| Vi                      | Input Voltage Range                           | Vo = Vref to                                              | 9                       |                  | 46   | V    | 2     |      |  |

| V <sub>12</sub>         | Feedback Voltage                              | $V_i = 9 \text{ to } 46^\circ$                            | V I <sub>o</sub> = 0.5A | 5                | 5.1  | 5.2  | V     | 2    |  |

| I <sub>12</sub>         | Input Bias Current                            | $V_i = 15V V_1$<br>$V_{17f} = 5V$                         | <sub>2</sub> = 6V       |                  | 5    | 20   | μА    | 3a   |  |

| V <sub>OS12</sub>       | Input Offset Voltage                          |                                                           |                         |                  | 5    | 10   | mV    | 3a   |  |

| $\Delta V_{o}$          | Line Regulation                               | $V_i = 9 \text{ to } 46^{\circ}$<br>$I_0 = 0.5 A$         | $V V_0 = V_{ref}$       |                  | 15   | 50   | mV    | 2    |  |

| $\Delta V_{o}$          | Load Regulation                               | $V_o = V_{ref}$<br>$I_o = 0.5 \text{ to } 1$              | .5A                     |                  | 15   | 45   | mV    | 2    |  |

| $V_{d}$                 | Dropout Voltage Between pin 3 and pin 2       | $I_2 = 3A$ $V_i = 20V$                                    |                         |                  | 1.5  | 2    | V     | 2    |  |

| I <sub>2L</sub>         | Current Limiting                              | $V_i = 9 \text{ to } 46$<br>$V_o = V_{ref} \text{ to } 3$ |                         | 3.5              |      | 6.5  | А     | 2    |  |

| Io                      | Maximum Operating Load Current                | $V_i = 9 \text{ to } 46^\circ$                            | 1.5                     |                  |      | А    | 2     |      |  |

| SVR                     | Supply Voltage Ripple<br>Rejection            | V <sub>i</sub> = 2Vrms<br>fripple = 100                   | 50                      | 56               |      | dB   | 2     |      |  |

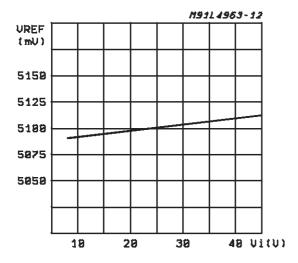

| V <sub>11</sub>         | Reference Voltage                             | V <sub>i</sub> = 9 to 46V<br>O < I <sub>11</sub> < 5mA    |                         | 5                | 5.1  | 5.2  | V     | 3a   |  |

|                         | Average Temperature Coefficient of Ref. Volt. | $T_j = 0 \text{ to } 125$                                 | 5 °C                    |                  | 0.4  |      | mV/°C | _    |  |

| $\Delta V_{11}$         | V <sub>ref</sub> Line Regulation              | $V_i = 9 \text{ to } 46^\circ$                            | V                       |                  | 10   | 20   | mV    | 3a   |  |

| $\Delta V_{11}$         | V <sub>ref</sub> Line Regulation              | $I_{ref} = 0 \text{ to } 5n$<br>$V_i = 46V R_o$           |                         | 65<br>69         | 7    | 15   | mV    | 3a   |  |

| η                       | Efficiency                                    | $I_0 = 1.5 A V_0$                                         | = V <sub>ref</sub>      | 65               | 75   |      | %     | 2    |  |

| $T_{sd}$                | Thermal Shutdown<br>Junction Temperature      |                                                           |                         | 145              | 150  |      | °C    | ı    |  |

|                         | Hysteresis                                    |                                                           |                         |                  | 30   |      | °C    | -    |  |

| DC CHARA                | ACTERISTICS                                   |                                                           |                         |                  |      |      |       |      |  |

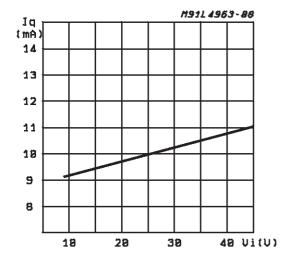

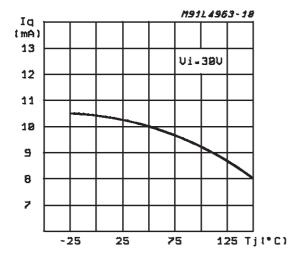

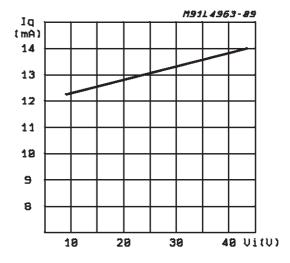

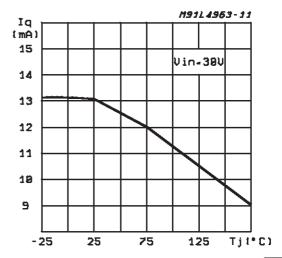

| Iq                      | Quescent Drain Current                        | $V_i = 46V$<br>$I_o = 0mA$                                | $V_{16} = V_{12} = 0$   |                  | 14   | 20   | mA    | За   |  |

|                         |                                               | $V_{16} = V_{ref}$<br>$V_{12} = 5.3V$                     |                         |                  | 11   | 16   | mA    | 3a   |  |

| INHIBIT                 |                                               |                                                           |                         | •                | •    | •    | •     |      |  |

| V <sub>16L</sub>        | Low Input Voltage                             | V <sub>i</sub> = 9 to 46                                  | V                       | 0.3              |      | 0.8  | V     | 2    |  |

| V <sub>16H</sub>        | High Input Voltage                            | V <sub>i</sub> = 9 to 46V                                 |                         | 2                |      | 5.5  | V     | 2    |  |

| I <sub>16L</sub>        | Input Current with Low Input Voltage          | V <sub>16</sub> = 0.8V                                    |                         | 50               | 100  | μА   | 2     |      |  |

| I <sub>16L</sub>        | Input Current with High Input Voltage         | V <sub>16</sub> = 2V                                      |                         |                  | 10   | 20   | μА    | 2    |  |

## L4963 - L4963D

# **ELECTRICAL CHARACTERISTIC** (Continued)

| Symbol            | Parameter                          | Test Conditions                                                | Min.                     | Тур.                     | Max.                     | Unit | Fig. |

|-------------------|------------------------------------|----------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|------|

| ESET              |                                    |                                                                | •                        | •                        |                          | •    |      |

| V <sub>12</sub>   | Rising Threshold Voltage           | V <sub>i</sub> = 9 to 46V                                      | V <sub>ref</sub><br>-150 | V <sub>ref</sub><br>-100 | V <sub>ref</sub><br>–50  | mV   | 3b   |

| V <sub>12</sub>   | Falling Threshold Voltage          | V <sub>i</sub> = 9 to 46V                                      | V <sub>ref</sub><br>-150 | V <sub>ref</sub><br>-200 | V <sub>ref</sub><br>-250 | mV   | 3b   |

| V <sub>9D</sub>   | Delay Rising Thereshold<br>Voltage | V <sub>7</sub> = OPEN                                          | 4.3                      | 4.5                      | 4.7                      | V    | 3b   |

| V <sub>9F</sub>   | Delay Falling Thereshold Voltage   |                                                                | 1                        | 1.5                      | 2                        | V    | 3b   |

| -l <sub>9SO</sub> | Delay Source Current               | $V_9 = 4.7 \text{V } V_{12} = 5.3 \text{V}$                    | 70                       | 110                      | 140                      | μΑ   | 3b   |

| I <sub>9SI</sub>  | Delay Sink Current                 | V <sub>9</sub> = 4.7V V <sub>12</sub> = 4.7V                   | 10                       |                          |                          | mA   | 3b   |

| I <sub>10</sub>   | Output Leakage Current             | V <sub>i</sub> = 46V V <sub>7</sub> = 8.5V                     | 50                       |                          |                          | μА   | 3b   |

| V <sub>10</sub>   | Output Saturation Volt.            | $I_{10} = 15 \text{mA}; V_1 = 3 \text{ to } 46 \text{V}$       |                          |                          | 0.4                      | V    | 3b   |

| OWER FA           | AIL                                |                                                                |                          |                          |                          |      |      |

| V <sub>R</sub>    | Rising Threshold Voltage           | Pin7 = open                                                    | 17.5                     | 19                       | 20.5                     | V    | 3C   |

| V <sub>F</sub>    | Falling Threshold Voltage          | Pin7 = open                                                    | 14.25                    | 15                       | 15.75                    | V    | 3c   |

| V <sub>7</sub>    | Rising Threshold Voltage           | V <sub>i</sub> = 20V                                           | 4.14                     | 4.5                      | 4.86                     | V    | _    |

| V <sub>7</sub>    | Falling Threshold Voltage          | V <sub>i</sub> = 20V                                           | 3.325                    | 3.5                      | 3.675                    | V    | _    |

| Vs                | Output Saturation Volt.            | $I_a = 5mA$                                                    |                          |                          | 0.4                      | V    | 3c   |

| Is                | Output Leakage Current             | V <sub>i</sub> = 46V                                           |                          |                          | 50                       | μА   | 3c   |

| SCILLAT           | OR                                 |                                                                |                          |                          |                          |      |      |

| f                 | Oscillator Frequency               | $R_T = 51K\Omega$                                              | 46                       | 60                       | 79                       | kHz  | _    |

| f                 | Oscillator Frequency               | $V_I$ = 9 to 46V<br>$T_j$ = 0 to 125°C<br>$R_T$ = 51K $\Omega$ | 42                       |                          | 83                       | kHz  | -    |

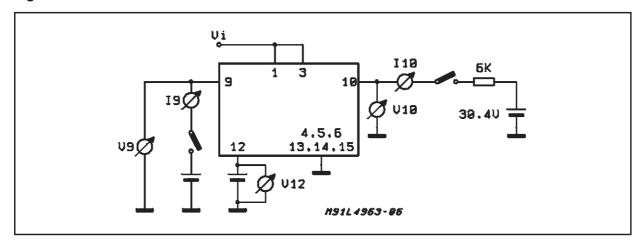

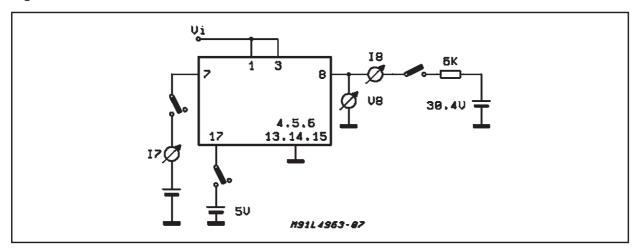

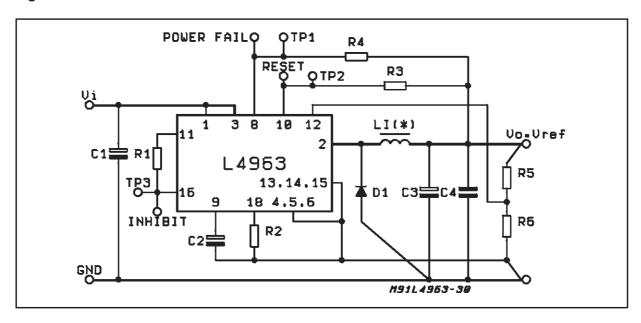

Figure 2: Test Circuit

Figure 3: DC Test Circuit

Figure 3a

Figure 3b

Figure 3c

Figure 4: Quiescent Drain Current vs. Supply Voltage (0% Duty Cycle)

Figure 6: Quiescent Drain Current vs. Junction Temperature (0% Duty Cycle)

Figure 5: Quiescent Drain Current vs. Supply Voltage (100% Duty Cycle)

Figure 7: Quiescent Drain Current vs. Junction Temperature (100% Duty Cycle)

Figure 8: Reference Voltage vs. Vi

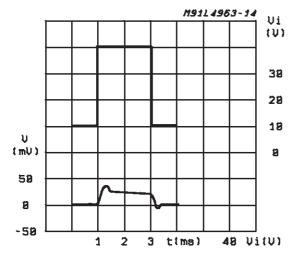

Figure 10: Line Transient Response

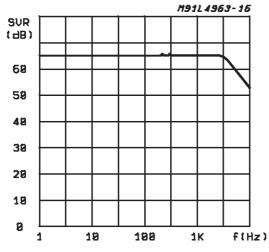

**Figure 12:** Supply Voltage Ripple Rejection vs. Frequency

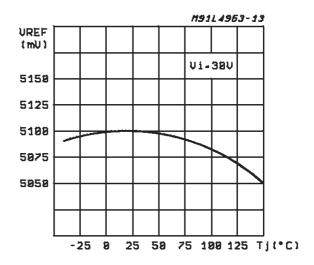

Figure 9: Reference Voltage vs. Ti

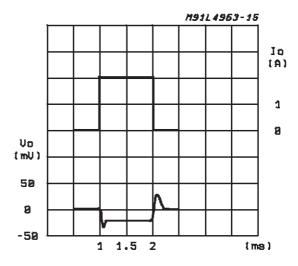

Figure 11: Load Transient

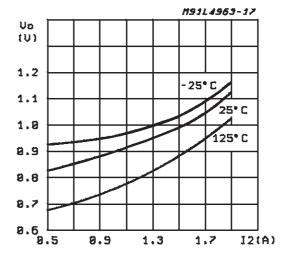

Figure 13: Dropout Voltage Between pi3 and 2 vs. Current at pin2

Figure 14: Dropout Voltage Between pin3 and 2 vs. Junction Temperature

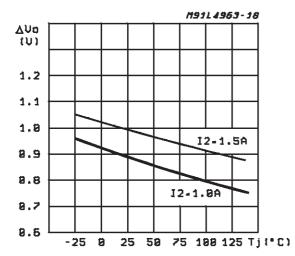

Figure 16: Power Dissipation (device only) vs. Input Voltage (Powerdip Package Only)

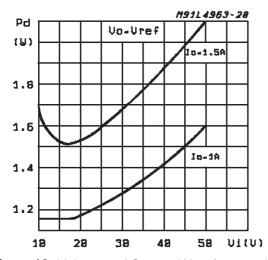

Figure 18: Voltage and Current Waveform at pin2

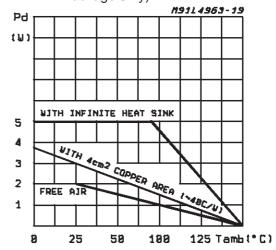

Figure 15: Maximum Allowable PowerDissipation vs. Ambient Temperature (Powerdip Package Only)

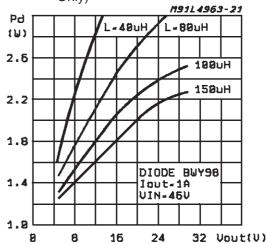

Figure 17: Power Dissipation (device only) vs.

Output Voltage (Powerdip Package

Only)

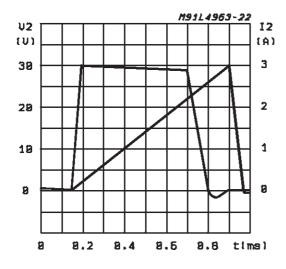

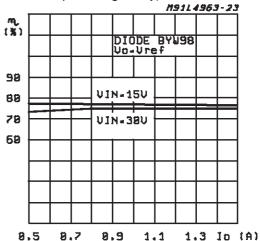

Figure 19: Efficiency vs. Output Current (Powerdip Package Only)

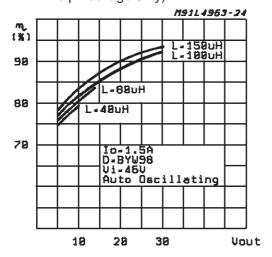

Figure 20: Efficiency vs. Output Voltage (Powerdip Package Only)

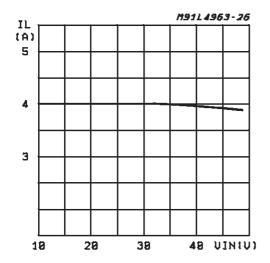

Figure 22: Current Limit vs. Input Voltage

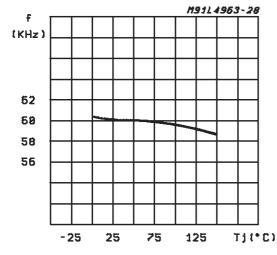

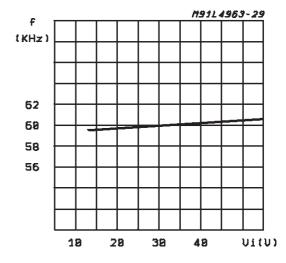

**Figure 24:** Oscillator Frequency vs. Junction Temperature

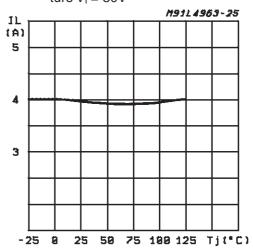

Figure 21: Current Limit vs. Junction Temperature  $V_i = 30V$

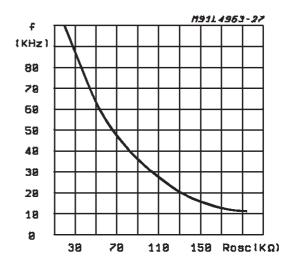

Figure 23: Oscillator Frequency vs. R2 (see fig. 26)

Figure 25: Oscillator Frequency vs. Input Voltage

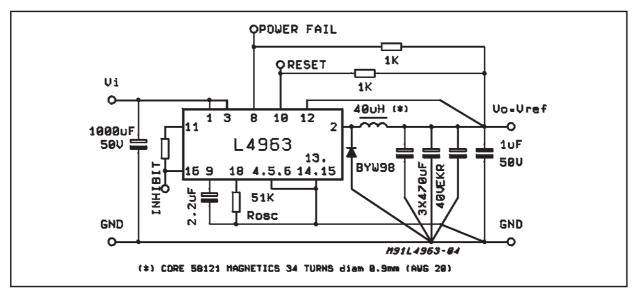

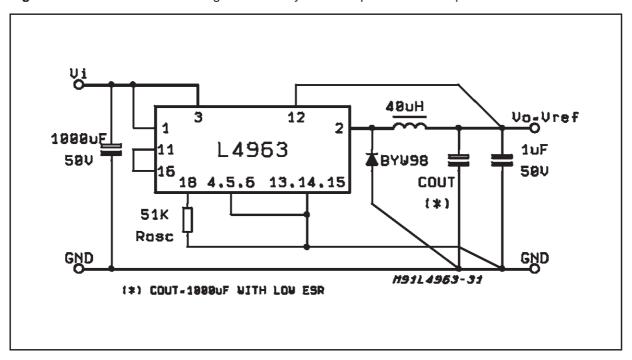

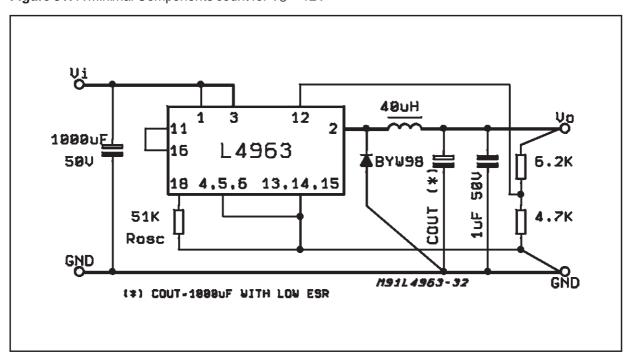

Figure 26: Evaluation Board Circuit

### **PART LIST**

| CAPACITOR    |                         |  |  |  |  |

|--------------|-------------------------|--|--|--|--|

| C1           | 1000μF 50V EKR (*)      |  |  |  |  |

| C2 2.2mF 16V |                         |  |  |  |  |

| C3           | 1000μF 40V with low ESR |  |  |  |  |

| C4           | 1μF 50V film            |  |  |  |  |

|              | RESISTOR                |  |  |  |  |

| R1           | 1ΚΩ                     |  |  |  |  |

| R2           | 51ΚΩ                    |  |  |  |  |

| R3           | 1ΚΩ                     |  |  |  |  |

| R4           | 1ΚΩ                     |  |  |  |  |

| R5, R6       | see table               |  |  |  |  |

| Resistor Values for Standard Output Voltages |       |       |  |  |  |  |  |  |

|----------------------------------------------|-------|-------|--|--|--|--|--|--|

| Vo                                           | R6    | R5    |  |  |  |  |  |  |

| 12                                           | 4.7ΚΩ | 6.2ΚΩ |  |  |  |  |  |  |

| 15                                           | 4.7ΚΩ | 9.1KW |  |  |  |  |  |  |

| 18                                           | 4.7ΚΩ | 12KW  |  |  |  |  |  |  |

| 24                                           | 4.7ΚΩ | 18KW  |  |  |  |  |  |  |

Diode: BYW98

Core: L= 40µH Magnetics 58121-A2MPP34 Turns

0.9mm (20AWG)

(\*) Minimum  $100\mu F$  if  $V_i$  is a preregulated offline SMPS output or  $1000\mu F$  if a 50Hz transformer plus rectifiers is used.

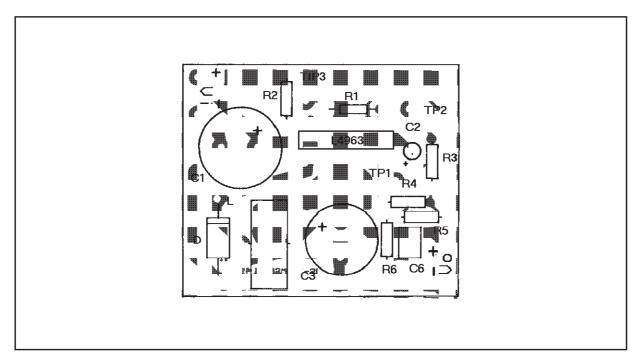

Figure 27: P.C. Board and Component Layout of the Circuit of fig. 26 (Powerdip Package) (1:1 scale).

Figure 28: Thermal Characteristics

Figure 29: Junction to Ambient Thermal Resistance vs. Area on Board Heatsink (SO20)

Figure 30: A Minimal 5.1 Fixed Regulator — Very Few Components are Required

**Figure 31:** A Minimal Components count for  $V_0 = 12V$

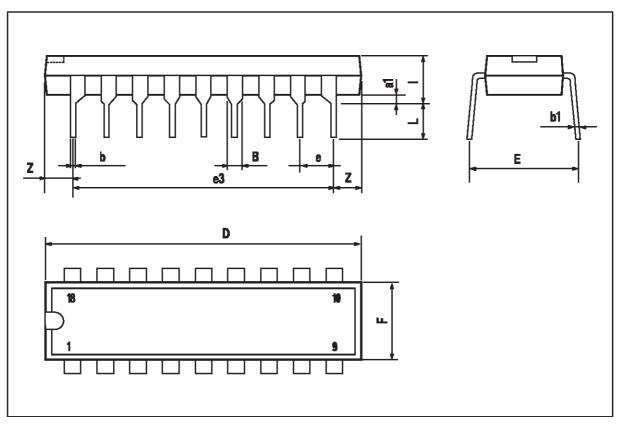

| DIM. |      | mm    |       | inch  |       |       |

|------|------|-------|-------|-------|-------|-------|

|      | MIN. | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| a1   | 0.51 |       |       | 0.020 |       |       |

| В    | 0.85 |       | 1.40  | 0.033 |       | 0.055 |

| b    |      | 0.50  |       |       | 0.020 |       |

| b1   | 0.38 |       | 0.50  | 0.015 |       | 0.020 |

| D    |      |       | 24.80 |       |       | 0.976 |

| Е    |      | 8.80  |       |       | 0.346 |       |

| е    |      | 2.54  |       |       | 0.100 |       |

| e3   |      | 20.32 |       |       | 0.800 |       |

| F    |      |       | 7.10  |       |       | 0.280 |

| ı    |      |       | 5.10  |       |       | 0.201 |

| L    |      | 3.30  |       |       | 0.130 |       |

| Z    |      |       | 2.54  |       |       | 0.100 |

# OUTLINE AND MECHANICAL DATA

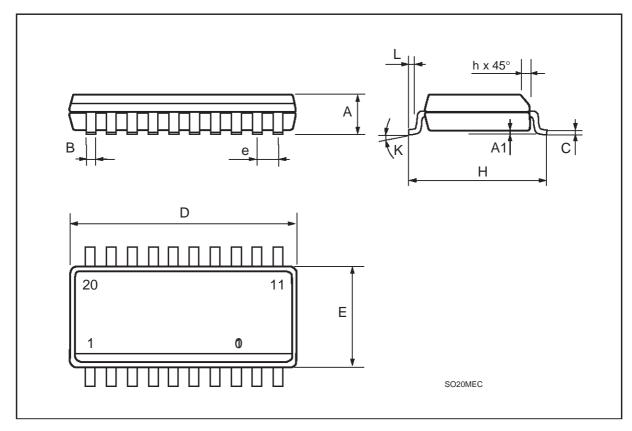

| DIM. |                    | mm   | mm inch |       |       |       |  |

|------|--------------------|------|---------|-------|-------|-------|--|

|      | MIN.               | TYP. | MAX.    | MIN.  | TYP.  | MAX.  |  |

| А    | 2.35               |      | 2.65    | 0.093 |       | 0.104 |  |

| A1   | 0.1                |      | 0.3     | 0.004 |       | 0.012 |  |

| В    | 0.33               |      | 0.51    | 0.013 |       | 0.020 |  |

| С    | 0.23               |      | 0.32    | 0.009 |       | 0.013 |  |

| D    | 12.6               |      | 13      | 0.496 |       | 0.512 |  |

| E    | 7.4                |      | 7.6     | 0.291 |       | 0.299 |  |

| е    |                    | 1.27 |         |       | 0.050 |       |  |

| Н    | 10                 |      | 10.65   | 0.394 |       | 0.419 |  |

| h    | 0.25               |      | 0.75    | 0.010 |       | 0.030 |  |

| L    | 0.4                |      | 1.27    | 0.016 |       | 0.050 |  |

| К    | 0° (min.)8° (max.) |      |         |       |       |       |  |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics - Printed in Italy - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com