# Á7/

# L9468

# ALL SILICON VOLTAGE REGULATOR

#### 1 Features

- FULLY MONOLITHIC DESIGN

- HIGH SIDE FIELD DRIVE

- THERMAL PROTECTION

- FIELD DRIVER SHORT CIRCUIT PROTECTION

- PROTECTED DIAGNOSTIC LAMP DRIVER

- REDUCED OUTPUT MODE

- COMPLEX DIAGNOSTICS

- LOAD RESPONSE CONTROL

#### 2 Description

.dzsc.com

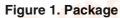

The L9468 is a monolithic multifunction generator Voltage regulator intended for use in automotive ap-

#### Figure 2. Block Diagram

#### Table 1. Order Codes

| Part Number | Package    |

|-------------|------------|

| L9468N      | Multiwatt8 |

| L9468N      | Multiwatt8 |

#### plications.

This device regulates the output of an automotive generator by controlling the field winding current by means of a variable frequency PWM high side driver.

#### Table 2. Pin Description

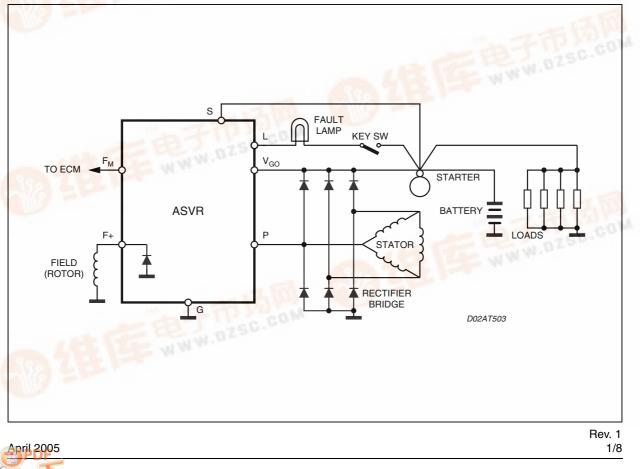

| N° | Pin            | Function                                           |  |

|----|----------------|----------------------------------------------------|--|

| 1  | $V_{GO}$       | Generator output sense and voltage supply to L9468 |  |

| 2  | F+             | ield high side driver output                       |  |

| 3  | G              | Ground for L9468                                   |  |

| 4  | S              | Battery sense input                                |  |

| 5  | GND            | Connected to the Tab through the frame             |  |

| 6  | F <sub>M</sub> | Field monitor output                               |  |

| 7  | L              | Lamp terminal low side driver                      |  |

| 8  | Р              | Phase sense input                                  |  |

#### Table 3. Absolute Maximum Ratings

| Symbol                                                                                  | Parameter                 | Value              | Unit |

|-----------------------------------------------------------------------------------------|---------------------------|--------------------|------|

| V <sub>S</sub> Thermal Supply Voltage (load dump)                                       |                           | 40                 | V    |

| Ι <sub>Ο</sub>                                                                          | Output Current Capability | internally limited | А    |

| $P_{tot}$ Total Power Dissipation (@T <sub>case</sub> = 150°C, I <sub>FIELD</sub> = 5A) |                           | 6                  | W    |

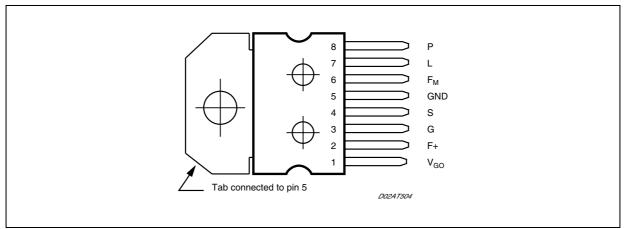

| V <sub>R</sub> Reverse Voltage (see figure 1)                                           |                           | -2.5/-6            | V    |

#### Figure 3. Pin Connection (Top view)

### Table 4. Thermal Data

| Symbol                                                   | Parameter                        | Value      | Unit |

|----------------------------------------------------------|----------------------------------|------------|------|

| R <sub>th j-case</sub>                                   | Thermal Resistance junction-case | -45 to 160 | °C   |

| T <sub>stg</sub>                                         | Storage Temperature              | -50 to 175 | °C   |

| R <sub>th sd</sub> Thermal Shut-Down                     |                                  | 175 ±15    | °C   |

| R <sub>th j-case</sub> Thermal Resistance junction -case |                                  | 1.5        | °C/W |

#### **Table 5. Electrical Characteristcs**

(T<sub>case</sub> = -35°C to 150°C unless otherwise specified)

| Symbol                                         | Parameter                    | Test Condition                                                                  | Min.              | Тур. | Max.              | Unit |

|------------------------------------------------|------------------------------|---------------------------------------------------------------------------------|-------------------|------|-------------------|------|

| V <sub>OS</sub>                                | Operating Supply Voltage     | T <sub>case</sub> = +25 to +150 °C                                              | 8                 |      | 20 <sup>1</sup>   | V    |

| V <sub>OS</sub> Operating Supply Voltage       |                              | T <sub>case</sub> = - 40 to +25 °C                                              | 10                |      | 20                | V    |

| I <sub>SB</sub>                                | Stand-by Current             | V <sub>GO</sub> = 12.6V, T <sub>case</sub> -35 to +80 °C                        |                   |      | 400               | μA   |

| I <sub>SB</sub>                                | Stand-by Current             | $V_{GO} = 12.6 \text{ V}, 80^{\circ}\text{C} < T_{case} < +150^{\circ}\text{C}$ |                   |      | 1                 | mA   |

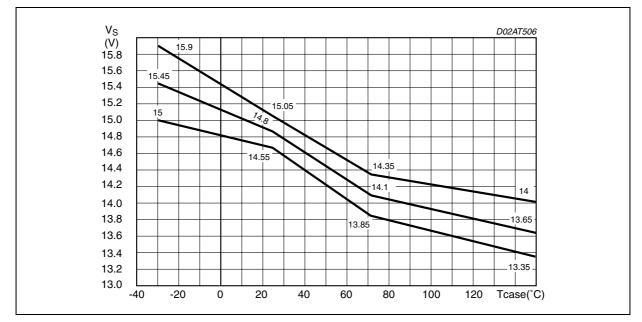

| Vs                                             | Regulator Set-Point          | @ 71°C ± 3°C                                                                    |                   | 14.1 |                   | V    |

| V <sub>NB</sub>                                | Generator output, no battery | No battery, I <sub>OUT</sub> =2A to 50% Max<br>Load                             | V <sub>S</sub> -2 |      | V <sub>S</sub> +2 | V    |

| T <sub>C</sub> Thermal compensation            |                              | Voltage @ V <sub>S</sub> or V <sub>GO</sub> $^2$ in failsoft                    |                   |      |                   | V    |

| V <sub>LR</sub> Load Regulation                |                              | 6500 grpm, 10% to 95% load                                                      |                   |      | 300               | mV   |

| V <sub>SR</sub> Speed Regulation               |                              | 15A load, 2,000 to 10,000 grpm                                                  |                   |      | 100               | mV   |

| V <sub>FON</sub> Output Saturation Voltage     |                              | $I_F = 6A, V_{GO} = 14.7V, T_{case} = 25^{\circ}C$                              |                   |      | 750               | mV   |

| V <sub>FON</sub> Output Saturation Voltage     |                              | $I_F = 5A, V_{GO} = 13.5V, T_{case} = 125^{\circ}C$                             |                   |      | 850               | mV   |

| I <sub>FLIM</sub>                              | Field limit current          | F terminal shorted to GND @ 25°C                                                | 8.3               |      |                   | А    |

|                                                |                              | F terminal shorted to GND @ 150°C                                               | 5                 |      |                   | А    |

| VF                                             | Field Discharge Rectifier    | $I_F = 6A, T_{case} = 25^{\circ}C$                                              |                   |      | 1.85              | V    |

| I <sub>R</sub> Diode Reverse Current           |                              | V <sub>R</sub> = 20V                                                            |                   |      | 1                 | mA   |

| f <sub>OSC</sub> Oscillation frequency         |                              | During LRC operation                                                            | 340               | 400  | 460               | Hz   |

| MFDC Minimum Field Duty-Cycle                  |                              | $V_{UV}$ < V(S or $V_{GO}$ ) < $V_{OV}$ <sup>3</sup>                            |                   | 6.25 |                   | %    |

| R <sub>FM</sub> Impedance @ F <sub>M</sub> pin |                              | Impedance between $F_M$ and $F_+$                                               | 5                 |      | 15                | KΩ   |

Notes:

20 Volts is the maximum operating voltage because above this level the FAILSAFE feature shuts down the output stage.

Thermal slopes are shown in fig. 2

This value is present when the voltage sensed at the "S" or "VGO" terminal is between VUV and VOV. When the voltage sensed at the "S" or "VGO" terminal is above VOV the Minimum Field Duty-Cycle will be 0 %.

#### Figure 4. Reverse B+ Test Circuit

## Figure 5. Setpoint Voltage vs. T<sub>case</sub> Temperature

| Symbol                                         | Parameter                         | Test Condition                                           | Min.              | Тур.                 | Max.                 | Unit |

|------------------------------------------------|-----------------------------------|----------------------------------------------------------|-------------------|----------------------|----------------------|------|

| V <sub>FSO</sub>                               | Failsafe Output Voltage           | Voltage measured at V <sub>GO</sub>                      | 20                | 20.48                | 21                   | V    |

| V <sub>FSL</sub>                               | Switch sensing from S to $V_{GO}$ | "S" Voltage falling into Fail Soft <sup>4</sup>          | 4                 | 4.2                  |                      | V    |

| V <sub>FSH</sub>                               | Switch sensing from $V_{GO}$ to S | "S" Voltage rising out of Fail Soft                      |                   | 7.6                  | 8                    | V    |

| IS                                             | Sink current @ "S" pin            | V <sub>S</sub> = 14 V                                    | 1                 | 1.75                 | 2.5                  | mA   |

| V <sub>UV</sub>                                | Undervoltage                      | grpm > 3100 ± 15%                                        | 10.95             | 11.35                | 11.6                 | V    |

| V <sub>OV</sub>                                | Overvoltage                       |                                                          | V <sub>S</sub> +1 | V <sub>S</sub> +1.25 | V <sub>S</sub> +1.55 | V    |

| V <sub>LSAT</sub>                              | Lamp saturation voltage           | I <sub>L</sub> = 0.5A                                    |                   | 1.33                 | 1.4                  | V    |

| V <sub>LSAT</sub> Lamp on Voltage <sup>5</sup> |                                   | I <sub>L</sub> < 0.5A,VGO=open, T <sub>case</sub> = 25°C |                   | 3.8                  | 5                    | V    |

| T <sub>DELAY</sub> Fault Indication Delay Time |                                   |                                                          | 0.935             | 1.1                  | 1.265                | s    |

Notes:

4. When Fail Soft operation is detected, regulation sensing will switch from the "S" terminal to the VGO terminal.5. This condition can happen when the connection between the battery and VGO or the output terminal of the generator is broken. In this case the delay of 1.1 seconds is not required.

57

### 3 FAULT

The following table lists the conditions that cause the fault lamp driver to function. To prevent lamp flicker, specific faults are required to be present for TDELAY seconds before the lamp driver is activated. This delay is indicated in the table.

#### Table 7.

| Conditions                                                                               | Delay |

|------------------------------------------------------------------------------------------|-------|

| 1. Key-on (wiring check), lamp stays on for $1 \pm 0.15$ sec regardless other conditions | No    |

| 2. V <sub>GO</sub> / S> V <sub>OV</sub>                                                  | Yes   |

| 3. $V_{GO}$ / S < undervoltage threshold voltage <b>AND</b> Phase frequency > $f_{LRC}$  | Yes   |

| 4. Phase Voltage < VP2 AND VGO / S < setpoint                                            | Yes   |

| 5. Phase frequency < f <sub>IFR</sub>                                                    | Yes   |

| 6. No connection between Battery and VGO                                                 | No    |

| 7. FAILSAFE                                                                              | Yes   |

#### **Table 8. Regulation Features**

| Symbol           | Parameter                                                               | Test Condition                                          | Min.                    | Тур.                    | Max.                | Unit |

|------------------|-------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|-------------------------|---------------------|------|

| V <sub>LON</sub> | Lamp term turn on threshold 6                                           |                                                         | 0.8                     | 1                       | 1.15                | V    |

| ILON             | Lamp term current sensitivity                                           | V <sub>L</sub> = 1 V to Vsp                             | 0.09                    |                         | 0.78                | mA   |

| V <sub>P1</sub>  | Initiation of regulation detection phase voltage threshold <sup>7</sup> | I <sub>P</sub> = 1mA (sinking current)                  | 2.5                     | 3                       | 3.5                 | V    |

| V <sub>P2</sub>  | Fault detection phase voltage threshold <sup>8</sup>                    |                                                         | 7                       | 8                       | 9                   | V    |

| lP               | Sinking current @ P terminal                                            | V <sub>P</sub> = 1.5V                                   | 0.5                     | 1                       | 1.8                 | mA   |

| fIFR             | Initiation of field regulation frequency                                |                                                         | 53.04                   | 61                      | 70.15               | Hz   |

| FSDF             | Field Strobe Duty Factor                                                | @ "power up" with f <sub>PHASE</sub> < f <sub>IFR</sub> |                         | 31.25                   |                     | %    |

| LRC              | Load Response Control rate 9                                            |                                                         | 2.125                   | 2.5                     | 2.875               | S    |

| f <sub>LRC</sub> | LRC transition frequency                                                | LRC is enabled below this value                         | 263.5                   | 310                     | 356.5               | Hz   |

| V <sub>LCB</sub> | "L" term. Cut-Back Setpoint                                             | "L" = 0V, "I" = 0V <sup>10</sup>                        | V <sub>S</sub> -<br>20% | V <sub>S</sub> -<br>25% | V <sub>S</sub> -30% | V    |

Notes:

7. This threshold on the phase signal is used to detect the phase frequency, fIFR, for the Initiation of field regulation.

8. This threshold on the phase signal is used to sense the presence of the phase for fault detection purposes.

<sup>10.</sup> Cut-back occurs when both the "L" and "I" terminals are LOW. If the "I" terminal is disconnected it will assume a logic LOW allowing the "L" terminal to perform the function alone. In cut-back, to prevent the loss of phase signal, a 31.25% duty cycle is applied to field output when phase drops below Vp2

<sup>6.</sup> Lamp and Ignition are cooperative. Either can turn on the device when the other is left open or held low. When both go below their minimum thresholds the L9468 goes into "L" Terminal Control (LTC). The L9468 will remain in LTC until the phase (P) voltage drops below VP2 and the frequency drops below fIRF at the VP1 threshold then the L9468 is disabled.

<sup>9.</sup> This is the time duration the L9468 takes to rump up from 0 % to 100% duty cycle in response to an increased load on the enerator. The LRC ratio is set 1:4 and the Vreg comparator status is latched at foundamental frequency rate.

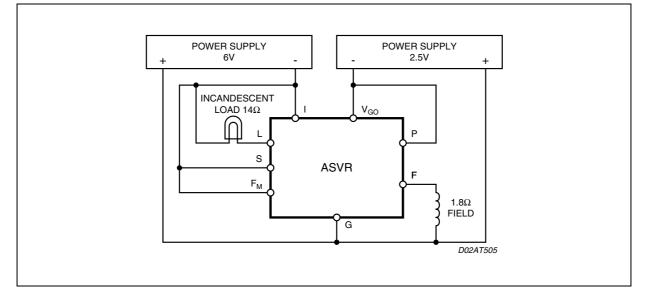

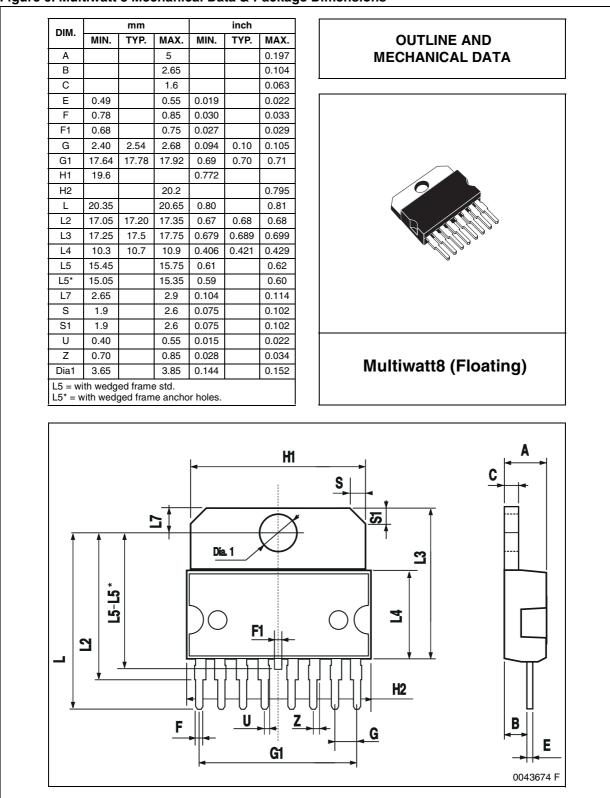

#### 4 Package Information

#### Figure 6. Multiwatt 8 Mechanical Data & Package Dimensions

57

# 5 Revision History

#### Table 9. Revision History

| Date       | Revision | Description of Changes |

|------------|----------|------------------------|

| April 2005 | 1        | First Issue            |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com