#### 捷多邦,专业PCB打样工厂,24小时加急出货

查询LA17000M供应商

## Ordering number: ENN6522

#### Monolithic Linear IC

LA17000M

## Tuner System IC with Built-in PLL for Car Audio Applications

## **Overview**

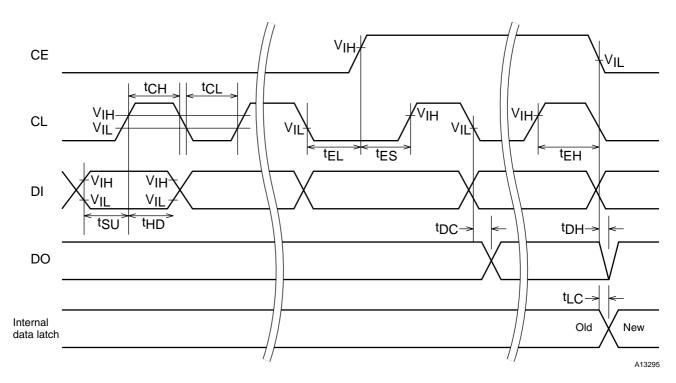

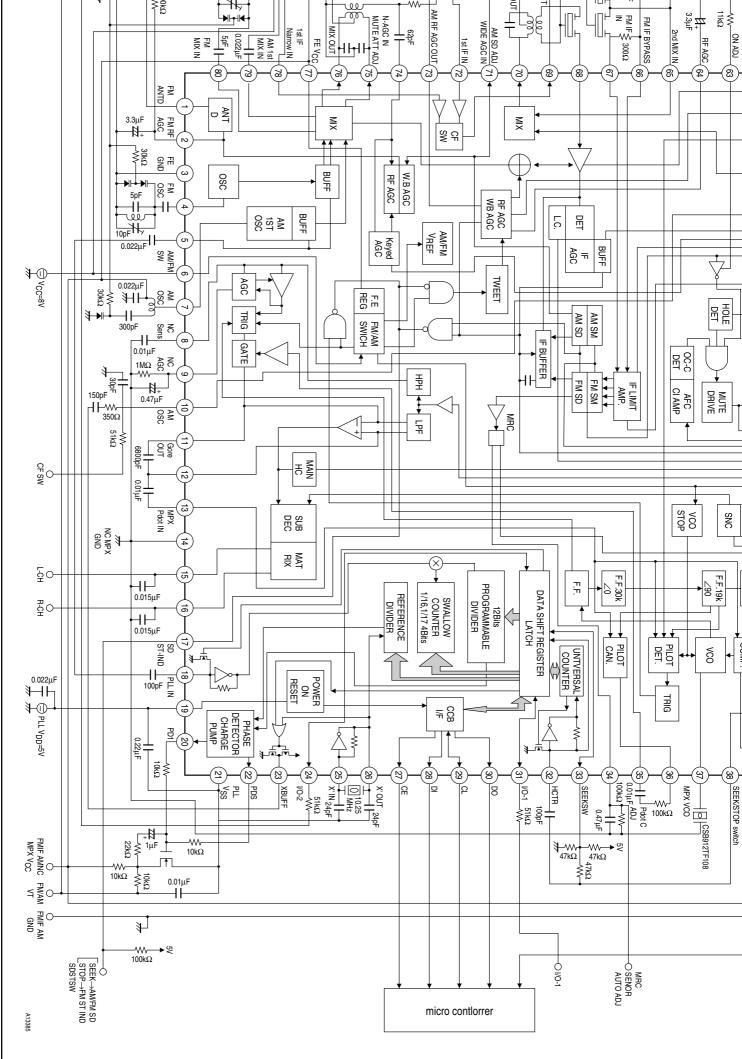

The LA17000M is an all-in-one car tuner IC that incorporates a PLL frequency synthesizer and all functions of an AM/FM tuner in a single chip. By combining two chips, a PLL (LC72144 equivalent) and an FM tuner IC (LA1781M equivalent) into a single chip (\*PLL + AM (up conversion) + FMFE + IF + NC + MCP + MRC), and as a result of optimal chip partitioning, the LA17000M improves the performance of car tuner systems, eliminates adjustments, and provides high reliability, all at a lower cost.

## **Features**

- PLL on chip

- ADC (6 bits, 1 channel)

- IF counter and I/O port on chip permit simplification of the interface.

- Supports AM double conversion.

- Enhanced noise countermeasures

- Excellent tri-signal characteristics

- Improved medium and weak electric field NC characteristics

- · Improved separation characteristics

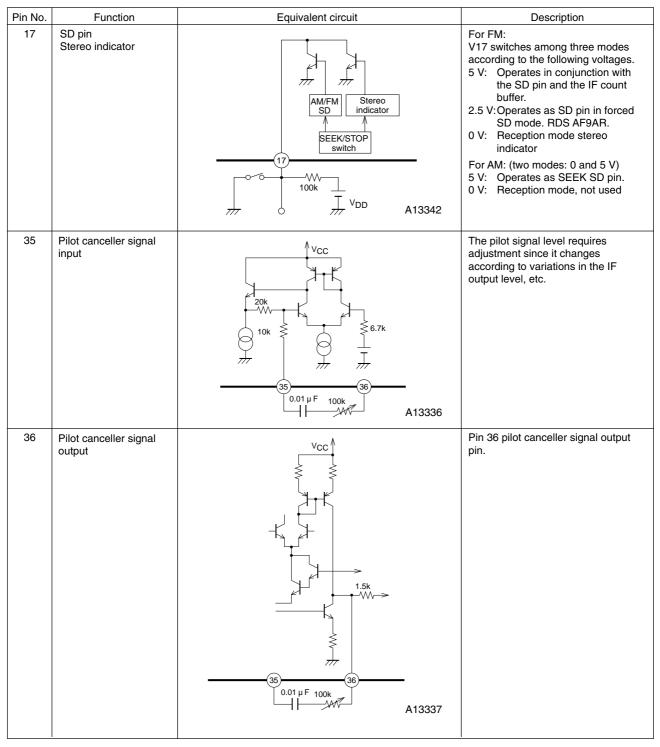

- Anti-birdie filter on chip (analog/digital output)

- Multipath sensor output (analog/digital output)

- · Cost-saving features

- AM double conversion (Up conversion method)

- Enhanced FM-IF circuit (When there is interference from adjacent frequencies, the software handles switching of the CF between wide and narrow automatically.)

- Because deviations in IF gain are only 1/3 that of earlier devices, adjustment is simplified when this IC is incorporated into a set; this IC also includes a shifter pin for VSM adjustment.

- · Suited for smaller devices

- · Permits high-frequency signal line processing in a tuner pack.

- · Easily conformes to FCC standards

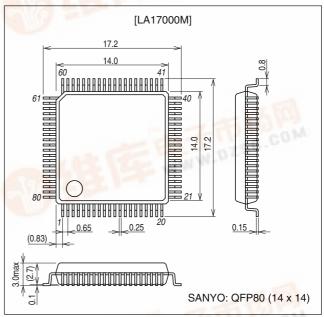

## W.DZSC.COM Package Dimensions

## unit: mm

#### 3255-QFP80

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

## Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol                | Conditions                   | Ratings    | Unit |

|-----------------------------|-----------------------|------------------------------|------------|------|

|                             | V <sub>CC</sub> 1 max | Pins 6, 56, and 77           | 8.7        | V    |

| Maximum supply voltage      | V <sub>CC</sub> 2 max | Pins 7, 61, 70, 75, and 76   | 12.0       | V    |

|                             | V <sub>DD</sub> max   | Pin 19                       | 6.0        | V    |

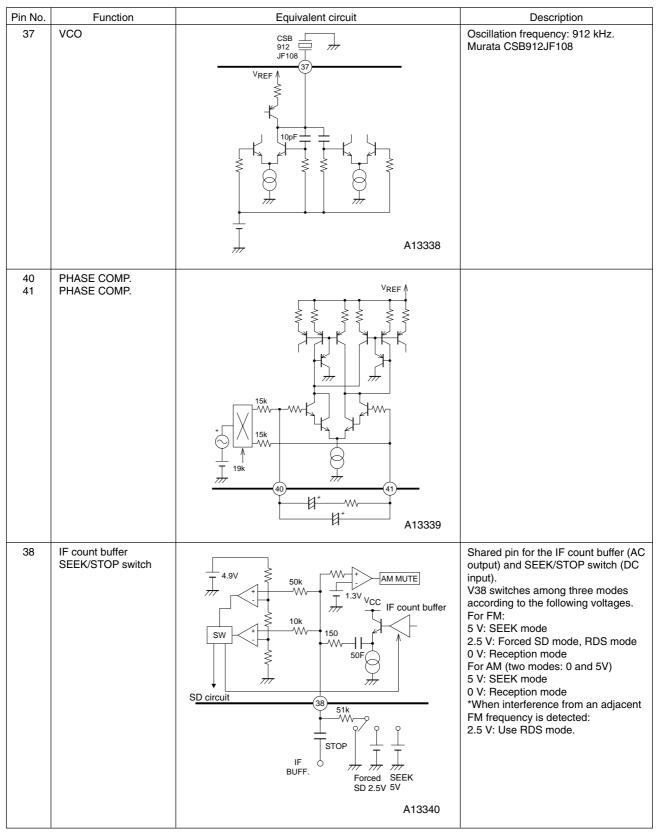

| Allowable power dissipation | Pd max                | Ta $\leq$ 85°C, * With board | 950        | mW   |

| Operating temperature       | Topr                  |                              | -40 to +85 | °C   |

| Storage temperature         | Tstg                  |                              | -40 to 150 | °C   |

\* Specified board:  $114.3 \times 76.1 \times 1.6 \text{ mm}^3$ , glass epoxy

## Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                      | Symbol             | Conditions                            | Ratings    | Unit |

|--------------------------------|--------------------|---------------------------------------|------------|------|

| Recommended supply voltage     | Maa                | Pins 6, 7, 56, 61, 70, 75, 76, and 77 | 8.0        | V    |

|                                | Vcc                | Pin 19                                | 5.0        | V    |

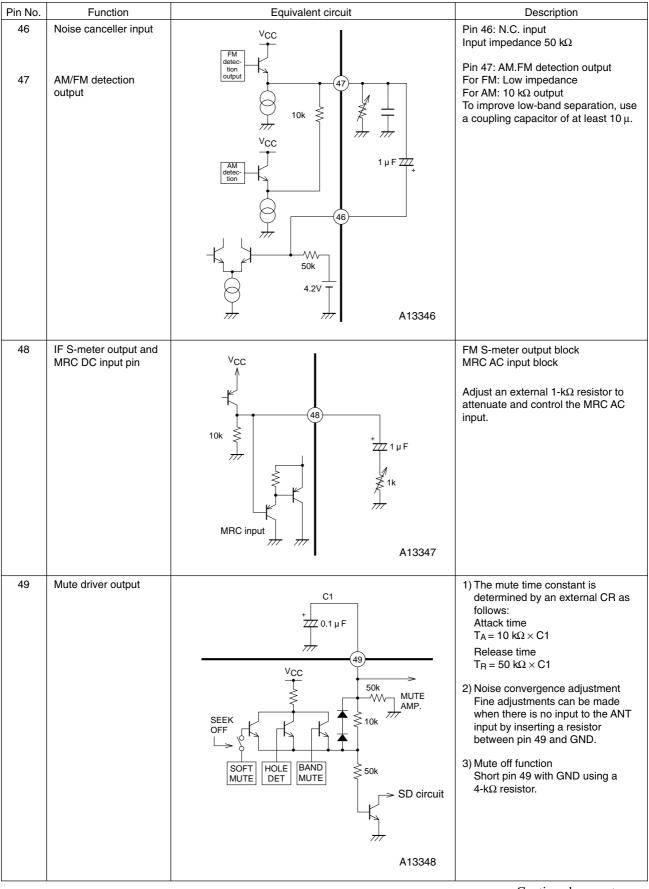

| Operating supply voltage range | V <sub>CC</sub> op |                                       | 7.5 to 8.5 | V    |

|                                | V <sub>DD</sub> op |                                       | 4.5 to 5.5 | V    |

## Tuner Block Operating Characteristics at Ta = $25^{\circ}$ C, V<sub>CC</sub> = 8.0 V, V<sub>DD</sub> = 5.0 V, in the specified Test Circuit

| De verse ete v                   | Cumhal               | Conditions                                                                                        |     | Ratings |     | 1.1   |

|----------------------------------|----------------------|---------------------------------------------------------------------------------------------------|-----|---------|-----|-------|

| Parameter                        | Symbol               | Symbol                                                                                            |     | typ     | max | Unit  |

| [FM characteristics] FM IF input | t                    |                                                                                                   |     |         |     |       |

| Current drain                    | I <sub>CCO</sub> -FM | No input, I56 + I61 + I70 + I75 + I76 + I79                                                       | 60  | 98      | 110 | mA    |

| Demodulated output               |                      | 10.7 MHz, 100 dBµV, 1 kHz, 100%mod,<br>pin 15 output                                              | 220 | 330     | 445 | mVrms |

| Channel balance                  | СВ                   | 10.7 MHz, 100 dBμV, 1 kHz,<br>ratio of pin15 and pin 16                                           | -1  | 0       | +1  | dB    |

| Total harmonic distortion        | THD-FMmono           | 10.7 MHz, 100 dBµV, 1 kHz, 100% mod, pin 15                                                       |     | 0.4     | 1   | %     |

| Signal-to-noise ratio IF         | S/N-FM IF            | 10.7 MHz, 100 dBµV, 1 kHz, 100% mod, pin 15                                                       | 75  | 82      |     | dB    |

| AM suppression ratio IF          | AMR IF               | 10.7 MHz, 100 dB $\mu$ , 1 kHz, fm = 1 kHz, pin 15 at 30% AM                                      | 55  | 68      |     | dB    |

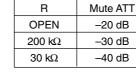

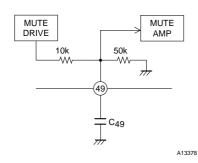

| Muting attenuation               | Att-1                | 10.7 MHz, 100 dBµV, 1 kHz, attenuation on pin 15 when V49 = 0 $\rightarrow$ 2 V                   | 3   | 8       | 13  | dB    |

|                                  | Att-2                | 10.7 MHz, 100 dBµV, 1 kHz, attenuation on pin 15 when V49 = 0 $\rightarrow$ 2 V *Note 1           | 13  | 18      | 23  | dB    |

|                                  | Att-3                | 10.7 MHz, 100 dB $\mu$ V, 1 kHz, attenuation on pin 15 when V49 = 0 $\rightarrow$ 2 V *Note 2     | 26  | 31      | 36  | dB    |

| Separation                       | Separation           | 10.7 MHz, 100 dBμ, L + R = 90%,<br>pilot = 10%, pin 15 output ratio                               | 25  | 35      |     | dB    |

| Stereo ON level                  | ST-ON                | Pilot modulation at which V17 < 0.5 V                                                             |     | 4.1     | 6.6 | %     |

| Stereo OFF level                 | ST-OFF               | Pilot modulation at which V17 > 3.5 V                                                             | 1.2 | 3.1     |     | %     |

| Main total harmonic distortion   | THD-Main L           | 10.7 MHz, 100 dBμV, L + R = 90%,<br>pilot = 10%, pin 15                                           |     | 0.4     | 1.2 | %     |

| Pilot cancellation               | PCAN                 | 10.7 MHz, 100 dBμV, pilot = 10%,<br>pin 15 signal/PILOT-LEVEL leak DIN AUDIO                      | 12  | 22      |     | dB    |

| SNC output attenuation           | AttSNC               | 10.7 MHz, 100 dB $\mu$ V, L – R = 90%, pilot = 10%, V44 = 3 V $\rightarrow$ 0.6 V, pin 15         | 1   | 5       | 9   | dB    |

| HCC output attenuation           | AttHCC-1             | 10.7 MHz, 100 dB $\mu$ V, 10 kHz, L + R = 90%, pilot = 10%, V45 = 3 V $\rightarrow$ 0.6 V, pin 15 | 1   | 5       | 9   | dB    |

|                                  | AttHCC-2             | 10.7 MHz, 100 dB $\mu$ V, 10 kHz, L + R = 90%, pilot = 10%, V45 = 3 V $\rightarrow$ 0.1 V, pin 15 | 6   | 10      | 14  | dB    |

Continued from preceding page.

| Parameter                    | Symbol                    | Conditions                                                                                     | Ratings   |      |     | Unit  |

|------------------------------|---------------------------|------------------------------------------------------------------------------------------------|-----------|------|-----|-------|

|                              |                           |                                                                                                | min typ m |      |     | Unit  |

| Input limiting voltage       | V <sub>IN</sub> -LIM      | 10.7 MHz, 100 dB $\mu$ V, 30% mod, IF input that decreases the input reference output by –3 dB | 29        | 36   |     | dBµV  |

| Muting sensitivity           | VIN-MUTE                  | IF input level non-mod when V49 = 2 V                                                          | 19        | 27   | 35  | dBµV  |

| SD sensitivity               | SD-sen1 FM                | IF input non-mod (at least 100 mVrms) at which the IF count buffer output turns on             | 48        | 56   | 64  | dBμV  |

|                              | SD-sen2 FM                |                                                                                                | 48        | 56   | 64  | dBµV  |

| IF counter buffer output     | VIFBUFF-FM1               | 10.7 MHz, 100 dB $\mu$ V, non-mod, pin 38 output, during SEEK                                  | 145       | 245  | 330 | mVrms |

|                              | VIFBUFF-FM2               | 10.7 MHz, 100 dB μV, non-mod,<br>pin 38 output, during RDS mode                                | 145       | 245  | 330 | mVrms |

| Signal meter output          | V <sub>SM</sub> FM-1      | No input, pin 42 DC output non-mod                                                             | 0.0       | 0.1  | 0.3 | V     |

|                              | V <sub>SM</sub> FM-2      | 50 dBµ, pin 42 DC output non-mod                                                               | 0.65      | 1.6  | 2.4 | V     |

|                              | V <sub>SM</sub> FM-3      | 70 dBµ, pin 42 DC output non-mod                                                               | 2.4       | 3.2  | 4.2 | V     |

|                              | V <sub>SM</sub> FM-4      | 100 dBµ, pin 42 DC output non-mod                                                              | 4.9       | 5.8  | 6.5 | V     |

| Muting bandwidth             | BW-MUTE                   | 100 dB $\mu$ V, when V49 = 2 V<br>Bandwidth non-mod                                            | 140       | 210  | 280 | kHz   |

| Muting drive output          | V <sub>MUTE</sub> -100    | 100 dBµV, 0 dBµ, pin 49 DC output non-mod                                                      | 0.00      | 0.1  | 0.3 | V     |

| [FM FE Block]                | •                         |                                                                                                |           |      |     |       |

| N-AGC on input               | V <sub>NAGC</sub>         | 83 MHz, non-mod, input at which pin 2 is 2.0 V or less                                         | 72        | 79   | 86  | dBµV  |

| W-AGC on input               | Vwagc                     | 83 MHz, non-mod, input at which pin 2 is<br>2.0 V or less (when KEYED-AGC is 4.0 V)            | 90        | 97   | 104 | dBµV  |

| Conversion gain              | A. V1                     | 83 MHz, 80 dBμ, non-mod, FECF output                                                           | 9         | 13   | 17  | dB    |

|                              | A. V2                     | 83 MHz, 80 dB $\mu$ , non-mod, 5 V applied to CF (pin 10), FECF output                         | 13        | 17   | 21  | dB    |

| Oscillator buffer output     | VOSCBUFFFM                | No input, pin 5 output                                                                         | 51        | 67   | 102 | mVrms |

| [NC Block] NC input (pin 30) |                           |                                                                                                |           |      |     |       |

| Gate time                    | <sup>™</sup> GATE         | f = 1 kHz, 1 μs, 100 mVp-o pulse input                                                         |           | 15   |     | μs    |

| Noise sensitivity            | SN                        | 1 kHz, 1 μs pulse input that starts noise canceller operation. Measured at Pin 30.             |           | 18   |     | mVp-o |

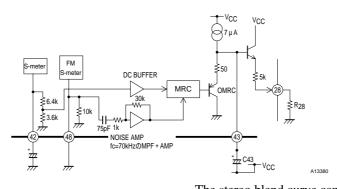

| [MRC Block]                  |                           |                                                                                                |           |      |     |       |

| MRC output                   | VMRC                      | V42 = 5 V                                                                                      | 2.1       | 2.25 | 2.4 | V     |

| MRC operating level          | MRC-ON                    | Input level on pin 48 that is below<br>pin 42 = 5 V and pin 43 = 2 V, f = 70 kHz               | 22        | 33   | 44  | mVrms |

| MRC sensor output            | VMRC-sensor1              | V42 = 5 V, pin 34 output                                                                       |           | 1.5  | 1.9 | V     |

|                              | V <sub>MRC</sub> -sensor2 | V42 = 5 V, pin 48 output, f = 70 kHz, 100 mVrms                                                | 2.1       | 2.9  |     | V     |

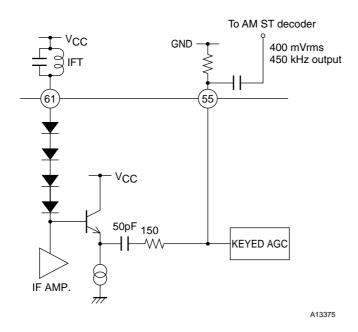

| [AM Characteristics] AM ANT  | input                     |                                                                                                |           |      |     |       |

| Practical sensitivity        | S/N-30                    | 1 MHz, 30 dBµV, fm = 1 kHz, 30% mod, pin 15                                                    | 15        |      |     | dB    |

| Detection output             | V <sub>O</sub> -AM        | 1 MHz, 74 dBµV, fm = 1 kHz, 30% mod, pin 15                                                    | 105       | 160  | 220 | mVrms |

| AGC-F.O.M                    | VAGC-FOM                  | 1 MHz, 74 dB $\mu$ V, output reference, input width at which output drops by 10 dB, pin 15     | 50        | 55   | 60  | mVrms |

| Signal-to-noise ratio        | S/N-AM                    | 1 MHz, 74 dBµV, fm = 1 kHz, 30% mod                                                            | 47        | 52   |     | dB    |

| Total harmonic distortion    | THD-AM                    | 1 MHz, 74 dBµV, fm = 1 kHz, 80% mod                                                            |           | 0.5  | 1.2 | %     |

| Signal meter output          | V <sub>SM</sub> AM-1      | 1 MHz, 30 dBµV, non - mod                                                                      | 0.6       | 1    | 1.4 | V     |

|                              | V <sub>SM</sub> AM-2      | 1 MHz, 120 dBµV, non - mod                                                                     | 3.4       | 4.5  | 5.9 | V     |

| Oscillator buffer output     | VOSCBUFFAM-1              | No input, pin 5 output                                                                         | 170       | 210  |     | mVrms |

| Wideband AGC sensitivity     | W-AGCsen1                 | 1.4 MHz, input when V62 = 0.7 V                                                                | 87        | 93   | 99  | dBµV  |

| ,                            | W-AGCsen2                 | 1.4 MHz, input when V62 = 0.7 V (during SEEK)                                                  | 78        | 84   | 90  | dBµV  |

#### Continued from preceding page.

| Devenueter       | Symbol Conditions     |                                                          |     |     |     |       |

|------------------|-----------------------|----------------------------------------------------------|-----|-----|-----|-------|

| Parameter        | Parameter Symbol Conc |                                                          | min | typ | max | Unit  |

| SD sensitivity   | SD-sen1AM             | 1 MHz, ANT input level at which IF count output turns on |     | 33  | 39  | dBμV  |

|                  | SD-sen2AM             | 1 MHz, ANT input level at which SD pin turns on          | 27  | 33  | 39  | dBµV  |

| IF buffer output | VIFBUFF-AM            | 1 MHz, 74 dB $\mu$ V, non-mod, pin 38 output             | 150 | 220 |     | mVrms |

# PLL Block Allowable Operating Ranges at Ta = -40 to $+85^{\circ}$ C, $V_{DD}$ = 5 V, $V_{SS}$ = 0 V

|                                      |                     |                                                                                     | Ratings |     |                       |       |

|--------------------------------------|---------------------|-------------------------------------------------------------------------------------|---------|-----|-----------------------|-------|

| Parameter                            | Symbol              | Conditions                                                                          | min     | typ | max                   | Unit  |

| High-level input voltage             | VIH1                | CE, CL, DI, I/O-1, I/O-2                                                            | 2.2     |     | V <sub>DD</sub> + 0.3 | V     |

| Low-level Input voltage              | VIL1                | CE, CL, DI, I/O-1, I/O-2, SDSTSW                                                    | 0       |     | 0.8                   | V     |

| Output voltage                       | Vo1                 | DO                                                                                  | 0       |     | 6.5                   | V     |

|                                      | V <sub>O</sub> 2    | I/O-1, I/O-2                                                                        | 0       |     | 13                    | V     |

| Input amplitude                      | fin1                | X <sub>IN</sub> ; Sine wave, capacitor coupled                                      | 1       |     | 8                     | MHz   |

|                                      | f <sub>IN</sub> 2   | PLL <sub>IN</sub> ; Sine wave, capacitor coupled                                    | 10      |     | 160                   | MHz   |

|                                      | f <sub>IN</sub> 3   | HCTR; Sine wave, capacitor coupled                                                  | 0.4     |     | 25                    | MHz   |

| Guaranteed crystal oscillator ranges | X'tal               | X <sub>IN</sub> , X <sub>OUT</sub> ; CI ≤ 70 Ω<br>(X'tal: 10.25, 10.35 MHz); Note 1 | 10.1    |     | 10.5                  | MHz   |

| Input amplitude                      | VIN1                | X <sub>IN</sub>                                                                     | 200     |     | 1500                  | mVrms |

|                                      | V <sub>IN</sub> 2-1 | PLL <sub>IN</sub> ; 10 ≤ f < 130 MHz; Note 2                                        | 40      |     | 1500                  | mVrms |

|                                      | V <sub>IN</sub> 2-2 | PLL <sub>IN</sub> ; 130 ≤ f <160 MHz; Note 2                                        | 70      |     | 1500                  | mVrms |

|                                      | V <sub>IN</sub> 3-1 | HCTR; $0.4 \le f < 25$ MHz: Serial data;<br>CTC = 0: Note 3                         | 40      |     | 1500                  | mVrms |

|                                      | V <sub>IN</sub> 3-2 | HCTR; $8 \le f < 12$ MHz: Serial data;<br>CTC = 1: Note 4                           | 70      |     | 1500                  | mVrms |

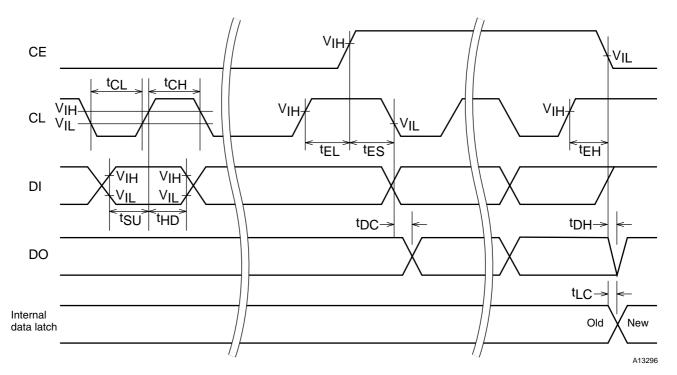

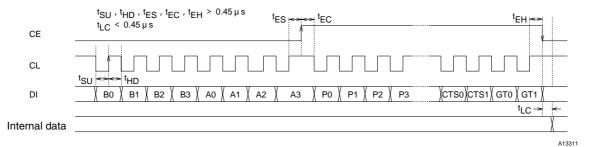

| Data setup time                      | tsu                 | DI, CL: Note 5                                                                      | 0.45    |     |                       | μs    |

| Data hold time                       | t <sub>HD</sub>     | DI, CL: Note 5                                                                      | 0.45    |     |                       | μs    |

| Clock low-level time                 | tCL                 | CL: Note 5                                                                          | 0.45    |     |                       | μs    |

| Clock high-level time                | tсн                 | CL: Note 5                                                                          | 0.45    |     |                       | μs    |

| CE wait time                         | tEL                 | CE, CL: Note 5                                                                      | 0.45    |     |                       | μs    |

| CE setup time                        | tES                 | CE, CL: Note 5                                                                      | 0.45    |     |                       | μs    |

| CE hold time                         | tен                 | CE, CL: Note 5                                                                      | 0.45    |     |                       | μs    |

| Data latch change time               | tLC                 | Note 5                                                                              |         |     | 0.45                  | μs    |

| Data output time                     | t <sub>DC</sub>     | DO, CL; Dependent on pull-up resistance,<br>board capacity: Note 5                  |         |     | 0.2                   | μs    |

|                                      | t <sub>DH</sub>     | DO, CL; Dependent on pull-up resistance, board capacity: Note 5                     |         |     | 0.2                   | μs    |

Note 1: Recommended CI value for crystal oscillator CI  $\leq$  70  $\Omega$  (X'tal: 10.25, 10.35 MHz)

However, because the characteristics of the X'tal oscillation circuit depend on the board and circuit constants, we recommend requesting that the X'tal manufacturer perform the evaluation.

Note 2: Refer to the program divider configuration.

Note 3: Serial data: CTC = 0

- Note 4: Serial data: CTC = 1

- Note 5: Refer to the serial data timing.

# PLL Characteristics Electrical Characteristics at Ta = 25°C, V<sub>DD</sub> = 5 V, V<sub>SS</sub> = 0 V

| Deremeter                              | Cumbal            | Conditions                                                                                                                                                                                               |                      | Ratings            |      | 11   |

|----------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------|------|

| Parameter                              | Symbol Conditions |                                                                                                                                                                                                          | min                  | typ                | max  | Unit |

| Built-in feedback resistors            | Rf1               | X <sub>IN</sub>                                                                                                                                                                                          |                      | 1                  |      | MΩ   |

|                                        | Rf2               | PLL <sub>IN</sub>                                                                                                                                                                                        |                      | 500                |      | kΩ   |

|                                        | Rf3               | HCTR                                                                                                                                                                                                     |                      | 250                |      | kΩ   |

| Hysterisis width                       | VHIS              | CE, CL, DI                                                                                                                                                                                               |                      | 0.1V <sub>DD</sub> |      | V    |

| High-level output voltage              | V <sub>OH</sub> 1 | PD1, PDS, SEEKSW; $I_0 = -1 \text{ mA}$                                                                                                                                                                  | V <sub>DD</sub> -1.0 |                    |      | V    |

|                                        | V <sub>OH</sub> 2 | XBUF; $I_0 = -0.5 \text{ mA}$                                                                                                                                                                            | V <sub>DD</sub> -1.5 |                    |      | V    |

| Low-level output voltage               | V <sub>OL</sub> 1 | PD1, PDS, SEEKSW; $I_0 = -1 \text{ mA}$                                                                                                                                                                  |                      |                    | 1    | V    |

|                                        | Vol2              | XBUFF; $I_0 = -0.5 \text{ mA}$                                                                                                                                                                           |                      |                    | 1.5  | V    |

|                                        | V <sub>OL</sub> 3 | I/O-1 to I/O-2; I <sub>O</sub> = 1.0 mA                                                                                                                                                                  |                      |                    | 0.2  | V    |

|                                        |                   | I/O-1 to I/O-2; I <sub>O</sub> = 2.5 mA                                                                                                                                                                  |                      |                    | 0.5  | V    |

|                                        |                   | I/O-1 to I/O-2; I <sub>O</sub> = 5.0 mA                                                                                                                                                                  |                      |                    | 1    | V    |

|                                        |                   | I/O-1 to I/O-2; I <sub>O</sub> = 9.0 mA                                                                                                                                                                  |                      |                    | 1.8  | V    |

| ·                                      | V <sub>OL</sub> 4 | DO; I <sub>O</sub> = 5.0 mA                                                                                                                                                                              |                      |                    | 1    | V    |

| High-level input current               | l <sub>IH</sub> 1 | CE, CL, DI; V <sub>IN</sub> = 6.5 V                                                                                                                                                                      |                      |                    | 5    | μA   |

|                                        | I <sub>IH</sub> 2 | I/O-1 to I/O-2; V <sub>IN</sub> = 13 V                                                                                                                                                                   |                      |                    | 5    | μA   |

|                                        | liH3              | XIN; VIN = VDD                                                                                                                                                                                           | 2                    |                    | 11   | μA   |

| ·                                      | lıH4              | PLLIN; VIN = VDD                                                                                                                                                                                         | 4                    |                    | 22   | μA   |

| Low-level input current                | lı∟1              | CE, CL, DI; V <sub>IN</sub> = 0 V                                                                                                                                                                        |                      |                    | 5    | μA   |

| -                                      | l <sub>IL</sub> 2 | I/O-1 to I/O-2; V <sub>IN</sub> = 0 V                                                                                                                                                                    |                      |                    | 5    | μA   |

|                                        | lı∟3              | $X_{IN}$ ; $V_{IN} = 0 V$                                                                                                                                                                                | 2                    |                    | 11   | μA   |

|                                        | IIL4              | PLL <sub>IN</sub> ; V <sub>IN</sub> = 0 V                                                                                                                                                                | 4                    |                    | 22   | μA   |

| Output off leakage current             | IOFF1             | I/O-1 to I/O-2; V <sub>O</sub> = 13 V                                                                                                                                                                    |                      |                    | 5    | μA   |

|                                        | IOFF2             | DO; V <sub>O</sub> = 6.5 V                                                                                                                                                                               |                      |                    | 5    | μA   |

| High-level 3-state off leakage current | IOFFH             | PD1, PDS; V <sub>IN</sub> = V <sub>DD</sub>                                                                                                                                                              |                      | 0.01               | 200  | nA   |

| Low-level 3-state off leakage current  | IOFFL             | PD1, PDS; V <sub>IN</sub> = 0 V                                                                                                                                                                          |                      | 0.01               | 200  | nA   |

| Input capacitance                      | CIN               |                                                                                                                                                                                                          |                      | 6                  |      | pF   |

| A/D converter linearity error          | Err               | MRC SENSOR AUTO ADJ (MOS)                                                                                                                                                                                | -0.5                 |                    | +0.5 | LSB  |

| Pull-down transistor on resistance     | Rpd1              | PLLIN                                                                                                                                                                                                    | 80                   | 200                | 600  | kΩ   |

| Supply current                         | I <sub>DD</sub> 1 | $\label{eq:VDD} \begin{array}{l} V_{DD}; X'tal = 10.25 \mbox{ MHz}, \\ f_{IN}2 = 160 \mbox{ MHz}, \\ V_{IN}2 = 70 \mbox{ mVrms}, \\ f_{IN}3 = 25 \mbox{ MHz}, \\ V_{IN}3 = 40 \mbox{ mVrms} \end{array}$ |                      | 10                 | 15   | mA   |

|                                        | I <sub>DD</sub> 2 | V <sub>DD</sub> ; PLL block halt (PLL INHIBIT),<br>X'tal OSC operation (10.25 MHz)                                                                                                                       |                      | 5                  | 10   | mA   |

|                                        | IDD3              | V <sub>DD</sub> ; PLL block halt, X'tal OSC halt                                                                                                                                                         |                      |                    | 3    | mA   |

No. 6522-6/54

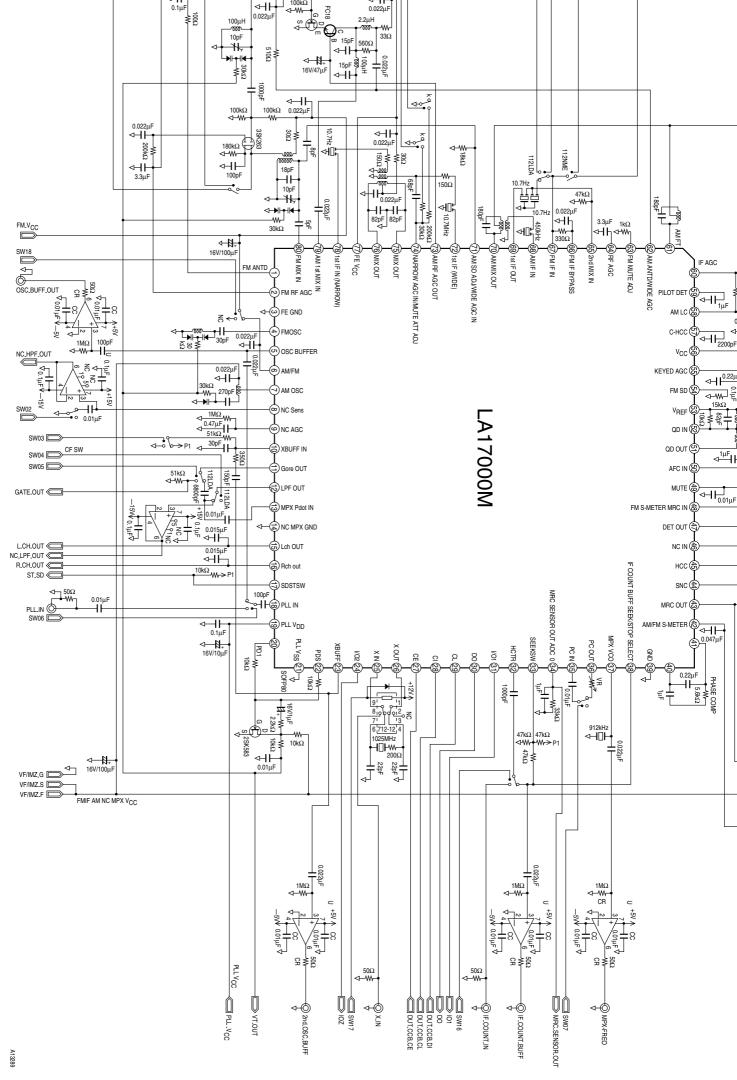

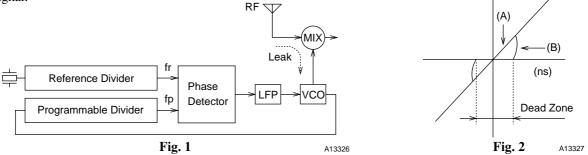

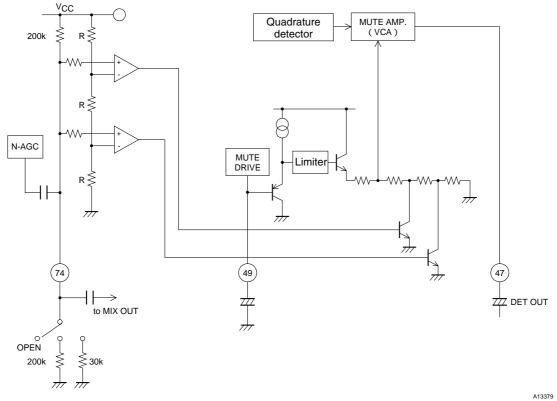

## [FM IF Selectivity Switching Circuit]

## Features

- 1) Comprises an FM/AM one-chip system.

- 2) Up conversion method is adopted for AM.

- 3) Uses an IF filter with a center frequency that is the same as the middle frequency of FM.

- 4) Uses a narrowband filter in AM mode.

- 5) Uses a narrowband filter in FM mode only during SEEK or when there is interference from adjacent frequencies.

- 6) Uses a wideband filter for normal reception in FM mode.

- 7) For an RDS AF search, switches to a narrowband filter and detects SD.

- 8) High sensitivity for detecting interference from adjacent frequencies.

## Advantages

- 1) This FM/AM one-chip tuner system (an IC that includes a microcontroller interface) allows for improved adjacent frequency interference characteristics without increased cost.

- 2) Prevents SD and IF count misdetection (station detection) during seek search, RDS AF search, and auto memory operations.

- 3) Permits adoption of an IC for certain functions without increasing the number of IC pins.

- 4) CF selectivity can be switched by the software in the microcontroller that controls the tuner, making it easy to achieve performance differentiation through the software.(The software can freely set the CF switching timing and conditions.)

- 5) Detects the radio wave status in the field through detection of SD, desired station field intensity, IF count output, and adjacent station field intensity. This IC offers improved adjacent frequency interference characteristics by switching the CF automatically when interference is being generated from an adjacent frequency.

## [IF Band Switching Circuit]

## Purpose

This AM/FM one-chip tuner IC automatically switches the FM selectivity, prevents misdetection during SEEK operations, and offers improved adjacent frequency interference characteristics without any increase in cost.

## **New Technological Features**

- 1. Comprises an AM/FM one-chip IC.

- 2. Because the narrowband CF that is used by the AM UP conversion system is also used for FM, additional external components required by earlier systems can be eliminated.

- 3. Uses a wideband CF during normal FM reception for high sound quality.

- 4. Uses a narrowband CF for AM reception, and if interference is being generated from adjacent frequencies during FM reception.

- 5. Uses a narrowband CF during SEEK and RDSAF search operations, preventing misdetection of SD and IF count due to adjacent stations.

- 6. CF switching is performed at the first IF amp input, and the amp gain is adjusted automatically to a suitable level according to the CF band form AM/FM or FM.

- 7. Switching of the CF input and the first IF amp gain is controlled by a microcontroller through the interface. The pins that are controlled are connected to the I/O ports of the microcontroller, and are controlled by the microcontroller's internal software.

- 8. Detection of adjacent frequency interference during FM reception is based on S-meter output, SD, and IF count output. The IF count buffer frequency fluctuates when interference is being generated from adjacent frequencies. This fluctuation is used to make the detection of interference from adjacent frequencies possible. (Related patents have been applied for.)

## **Conventional Technologies**

- 1. Comprised of a dedicated IC for IF band switching, or of multiple ICs.

- 2. None of the AM/FM all-in-one chip systems include the functions provided by the LA17000M.

- 3. Requires a narrowband CF especially for FM, resulting in increased costs. (Does not share the AM narrowband CF.)

- 4. Because CF switching control is handled by analog circuits or logic circuits, the switching timing can only be controlled through uniform conditions. Control by software is not possible.

LA17000M

## Conceptual Diagram of the FM-IF Band Switching System

A13294

#### I/O Port Assignment Table

| I/O-0            | OUTPUT<br>PLL output port                                                    | L: Reception mode<br>H: Seek mode                                                           |

|------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| DI data          | INPUT<br>PLL input port                                                      | OPEN: RDS                                                                                   |

| I/O-1            |                                                                              | Unused                                                                                      |

| I/O-2<br>DI data | OUTPUT<br>PLL output port                                                    | H: Dx mode<br>L: Lo mode                                                                    |

| I/O-3<br>DO data | INPUT<br>I/O-3 = 0 (input port)<br>OUT3 = 1 (OPEN or high)<br>PLL input port | When reception mode is set<br>H: Monaural<br>L: Stereo<br>When seek mode is set<br>H: SD ON |

|                  | Cannot be set as output port                                                 | L: SD OFF                                                                                   |

The MRC sensor reads DO data from the PLL microcontroller's 6-bit A/D converter.

Currently, aside from the CCB data lines, only three lines are connected to the controller microcontroller: CF/SW, AUDIO mute, and AM/FM band switching port.

## Selectivity Switching Evaluation Software

## State-based Data Switching Table

| I/O port state    | Tuner processing | Seek | Manual preset | Receiving | Remarks                                          |

|-------------------|------------------|------|---------------|-----------|--------------------------------------------------|

| CF switching      | WIDE             |      | 0             | 0         |                                                  |

| Or switching      | NARROW           | 0    | 0             | 0         |                                                  |

| AUDIO mute output | ON               | 0    | 0             |           | Switchable but fixed by software                 |

|                   | OFF              |      |               | 0         | Switchable but fixed by software                 |

| Lo/Dx             | Lo               | 0    | 0             | 0         | Processing is performed according to the setting |

| 20,07             | Dx               | 0    | 0             | 0         | Processing is performed according to the setting |

|                   | Seek mode        | 0    |               | 0         | I/O-3 is SD output                               |

| Mode switching    | Reception mode   |      | 0             | 0         | I/O-3 is monaural/stereo output                  |

|                   | RDS mode         |      |               | 0         | I/O-3 is SD output                               |

| IF count          | Output ON        | 0    |               | 0         | Seek mode<br>RDS mode                            |

|                   | Output OFF       |      | 0             |           | Reception mode                                   |

## Additional Settings (Added to the LC72144M)

#### Output (DI)

|                   | Mode           | Settings                                                 | When set                        |

|-------------------|----------------|----------------------------------------------------------|---------------------------------|

|                   | Seek mode      | DI data IN2<br>I/O-0 = 1 (output port)<br>OUT0 = 1 (Hi)  | For seek                        |

| Tuner mode switch | Reception mode | DI data IN2<br>I/O-0 = 1 (output port)<br>OUT0 = 0 (Lo)  | For seek-stop and for receiving |

|                   | RDS mode       | DI data IN2<br>I/O-0 = 0 (input port)<br>OUT0 = 1 (OPEN) | For AF search                   |

|                   | Lo mode        | DI data IN2<br>I/O-2 = 0 (output port)<br>OUT2 = 0 (Lo)  | When setting Lo mode            |

| Lo/Dx switch      | Dx mode        | DI data IN2<br>I/O-2 = 1 (output port)<br>OUT2 = 1 (Hi)  | When setting Dx mode            |

| Hard mute *1      | Mute ON        | DI data IN2<br>I/O-0 = 1 (output port)<br>OUT1 = 1 (Hi)  | For tuning processing           |

|                   | Mute OFF       | DI data IN2<br>I/O-0 = 1 (output port)<br>OUT1 = 1 (Lo)  | When switching reception mode   |

Note: \*1. Depends on the I/O ports usage.

## Input (DO)

|            |                 | DO data                                                                        | Conditions                                                                                       |

|------------|-----------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Sensor     | Monaural/stereo | OUT data I3 = 1 (Hi)<br>Monaural state<br>OUT data I3 = 0 (Lo)<br>Stereo state | When the tuner mode is set to reception mode                                                     |

|            | SD              | OUT data I3 = 1 (Hi)<br>SD ON<br>OUT data I3 = 0 (Lo)<br>SD OFF                | When the tuner mode is set to seek or<br>RDS mode<br>*2                                          |

| MRC output |                 | OUT data ADC0<br>AD00 to AD05<br>6 bit                                         | Start AD conversion and then read<br>after conversion is completed.<br>3.3 V at 6-bit resolution |

Note: \*2. I/O-3 = 0 (input port) and OUT3 = 1 (Hi) must already be set in the DI data (IN2) settings.

Other settings

|                        | In the LA17000 | Setting                                                           | When set                                                                        |

|------------------------|----------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|

| CF switch              | Pin 10         | Hi: Wide (wideband setting)<br>Lo: Narrow (narrowband<br>setting) | For normal operation<br>When there is interference from<br>adjacent frequencies |

| Soft mute (AUDIO mute) | Pin 49         | Hi: Forced mute<br>Lo: Mute off                                   | When setting mute<br>When cancelling mute                                       |

| AM/FM switch           | Pin 6          | Lo: AM<br>Hi: FM                                                  | For AM reception<br>For FM reception                                            |

| LA1781<br>Pin No. | Pin Function                                                                 | LA17000M<br>Pin No. | Pin Function                    | LC72144N<br>Pin No. |

|-------------------|------------------------------------------------------------------------------|---------------------|---------------------------------|---------------------|

| 1                 | FN ANTD                                                                      | 1                   |                                 |                     |

| 2                 | FM RF AGC                                                                    | 2                   |                                 |                     |

| 3                 | FE GND                                                                       | 3                   |                                 |                     |

| 4                 | FM OSC                                                                       | 4                   |                                 |                     |

| 5                 | AM/FM OSC buff.                                                              | 5                   |                                 |                     |

| 6                 | FE V <sub>CC</sub>                                                           | 6                   |                                 |                     |

| 7                 | AM V <sub>CC</sub>                                                           | 7                   |                                 |                     |

| 8                 | Noise AGC-Sense                                                              | 8                   |                                 |                     |

| 9                 | Noise AGC-ADJ                                                                | 9                   |                                 |                     |

| 10                | AM 2nd OSC                                                                   | 10                  |                                 |                     |

| 11                | Gate Out                                                                     | 11                  |                                 |                     |

| 12                | Memory circuit pin                                                           | 12                  |                                 |                     |

| 13                | Pilot In                                                                     | 13                  |                                 |                     |

| 14                | NC, MPX GND                                                                  | 14                  |                                 |                     |

| 15                | MPX L-Out                                                                    | 15                  |                                 |                     |

| 16                | MPX R-Out                                                                    | 16                  |                                 |                     |

| 26                | $\begin{array}{l} Seek \to AM/FM \ SD \\ Stop \to FM \ ST \ IND \end{array}$ | 17                  | Both I/O-3 and SD/ST-IND        | 23                  |

|                   |                                                                              | 18                  | FMIN                            | 16                  |

|                   |                                                                              | 19                  | VDD                             | 17                  |

|                   |                                                                              | 20                  | PD1                             | 18                  |

|                   |                                                                              | 21                  | V <sub>SS</sub>                 | 19                  |

|                   |                                                                              | 22                  | PDS                             | 20                  |

|                   |                                                                              | 23                  | XBUF                            | 22                  |

|                   |                                                                              | 24                  | I/O-2                           | 8                   |

|                   |                                                                              | 25                  | XIN                             | 24                  |

|                   |                                                                              | 26                  | XOUT                            | 1                   |

|                   |                                                                              | 27                  | CE                              | 2                   |

|                   |                                                                              | 28                  | DI                              | 3                   |

|                   |                                                                              | 29                  | CL                              | 4                   |

|                   |                                                                              | 30                  | DO                              | 5                   |

|                   |                                                                              | 31                  | I/O-1                           | 9                   |

|                   |                                                                              | 32                  | HCTR/I-6                        | 11                  |

|                   |                                                                              | 33                  | I/O-0                           | 12                  |

| 19                | MRC sensor output                                                            | 34                  | Both ADC0 and MRC sensor output | 7                   |

| 17                | Pilot Can. ADJ                                                               | 35                  |                                 |                     |

| 18                | Pilot Can. ADJ                                                               | 36                  |                                 |                     |

| 20                | MPX VCO                                                                      | 37                  |                                 |                     |

| 23                | IF count buffer and seek/stop switch                                         | 38                  |                                 |                     |

| 25                | GND                                                                          | 39                  |                                 |                     |

| 21                | PHASE COMP.                                                                  | 40                  |                                 |                     |

| 22                | PHASE COMP.                                                                  | 41                  |                                 |                     |

| 24                | AM/FM S-meter                                                                | 42                  |                                 |                     |

| 27                | MRC OUT                                                                      | 43                  |                                 |                     |

## Correspondence of Pins Between the LA17000M, the LA1781M, and the LC72144M

Continued from preceding page.

| LA1781<br>Pin No. | Pin Function            | LA17000M<br>Pin No. | Pin Function     | LC72144M<br>Pin No. |

|-------------------|-------------------------|---------------------|------------------|---------------------|

| 28                | SNC control input       | 44                  |                  |                     |

| 29                | HCC control input       | 45                  |                  |                     |

| 30                | Noise canceller IN      | 46                  |                  |                     |

| 31                | AM/FM detector output   | 47                  |                  |                     |

| 32                | FM S-meter output       | 48                  |                  |                     |

| 33                | MUTE drive              | 49                  |                  |                     |

| 34                | AFC IN                  | 50                  |                  |                     |

| 35                | QD OUT                  | 51                  |                  |                     |

| 36                | CD IN                   | 52                  |                  |                     |

| 37                | VREF                    | 53                  |                  |                     |

| 38                | FMSD                    | 54                  |                  |                     |

| 39                | GND Keyed AGC           | 55                  |                  |                     |

| 40                | Vcc                     | 56                  |                  |                     |

| 41                | HCC capacitor           | 57                  |                  |                     |

| 42                | AM L.C.                 | 58                  |                  |                     |

| 43                | Pilot detector          | 59                  |                  |                     |

| 44                | IF AGC                  | 60                  |                  |                     |

| 45                | AM IFT (IF output)      | 61                  |                  |                     |

| 46                | AM ANTD<br>W-AGC IN     | 62                  |                  |                     |

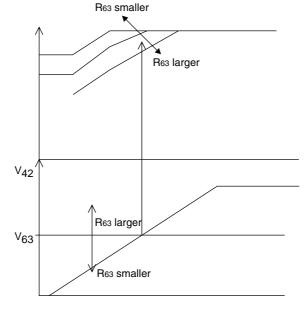

| 47                | FM Mute ON ADJ          | 63                  |                  |                     |

| 48                | RF AGC                  | 64                  |                  |                     |

| 49                | AM 2nd MIX IN           | 65                  |                  |                     |

| 50                | FM IF BYPASS            | 66                  |                  |                     |

| 51                | FM IF IN                | 67                  |                  |                     |

| 52                | AM IF IN                | 68                  |                  |                     |

| 53                | 1st IF amplifier output | 69                  |                  |                     |

| 54                | AM MIX OUT              | 70                  |                  |                     |

| 55                | W-AGC IN<br>AM SD ADJ   | 71                  |                  |                     |

| 56                | 1st IF IN               | 72                  |                  |                     |

| 57                | AM RF AGC OUT           | 73                  |                  |                     |

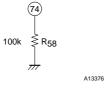

| 58                | N-AGC IN                | 74                  |                  |                     |

| 59                | 1st MIX OUT             | 75                  |                  |                     |

| 60                | 1st MIX OUT             | 76                  |                  |                     |

| 61                | F.E.V <sub>CC</sub>     | 77                  |                  |                     |

| 64                | FM MIX IN               | 78                  | 1st IF narrow IN |                     |

| 62                | AM MIX IN               | 79                  |                  |                     |

| 63                | FM MIX IN               | 80                  |                  |                     |

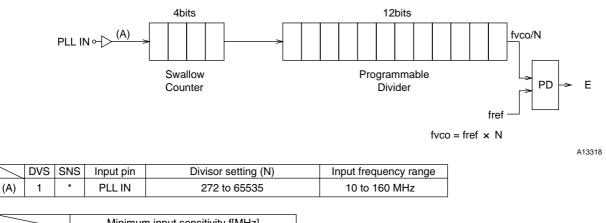

#### **PLL Block Functions**

- High-speed programmable divider

- FMIN : 10 to 160 MHz ..... Pulse swallower method

General-purpose counter

- HCTR : 0.4 to 25.0 MHz ..... Frequency measurement

- Crystal oscillator : Two frequencies selectable: 10.35/10.25 MHz

- Reference frequencies : 12 frequencies selectable:

- 50, <u>30</u>, 25, 12.5, 6.25, 3.125, 10, <u>9</u>, <u>3</u>, 5, and 1kHz \*1 \*1

- \*1: Not available when using the 10.25 MHz crystal oscillator

- · Phase comparator

- Dead zone can be controlled

- Unlock detection circuit

- Sub-charge pump for high-speed locking

- Deadlock clear circuit on chip

- Serial data I/O

- Communications with controller possible in CCB format

- Power-on reset circuit

- · On-chip crystal oscillator output buffer

- 2nd IF injection signal for AM up conversion (10.35/10.25 MHz)

- I/O port ...... General-purpose I/O: four ports

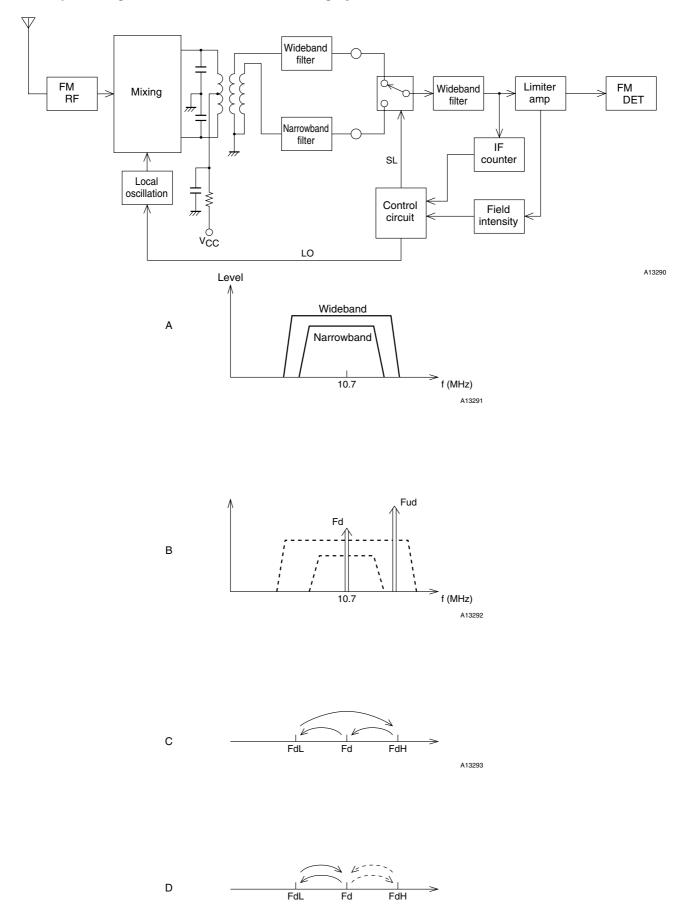

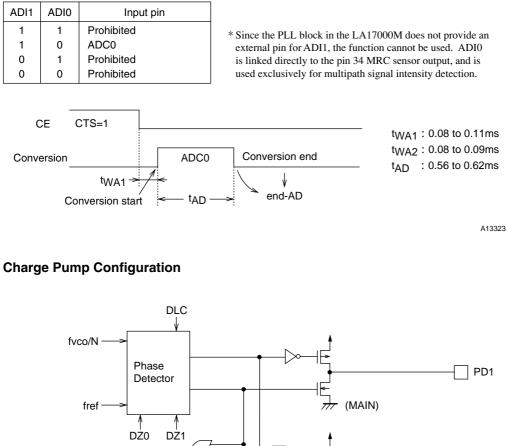

## **Serial Data Timing**

When CL is Stopped at the low level

When CL is Stopped at the high level

LA17000M

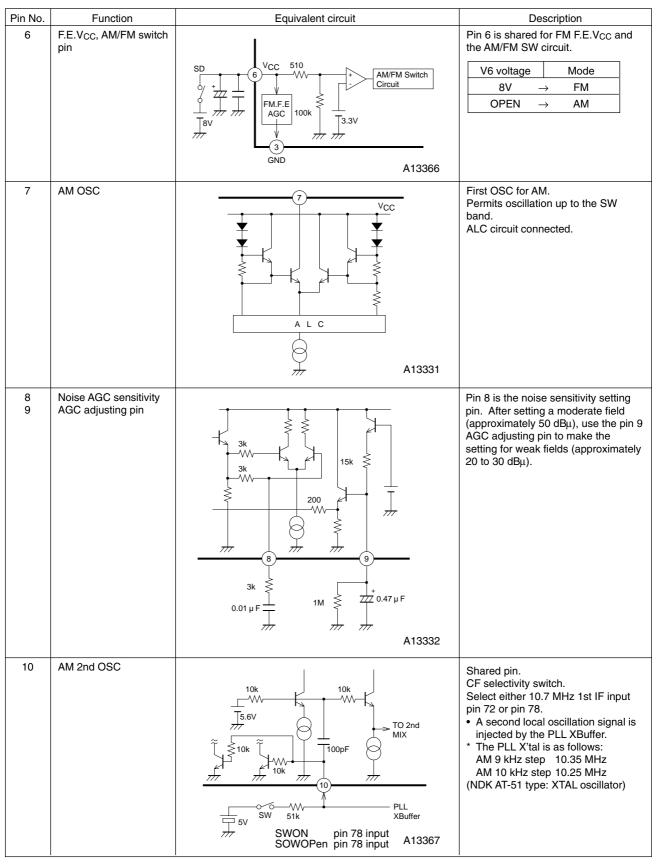

## **PLL Block Pin Description**

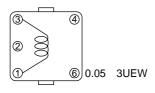

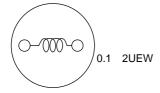

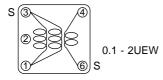

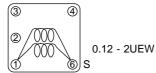

| Symbol                    | Pin No.        | Description                         | Function                                                                                                                                                                                                                                                                                                                                                                              | Pin Circuit |

|---------------------------|----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| XIN<br>XOUT               | 25<br>26       | X'tal OSC                           | <ul> <li>For connecting the crystal oscillator.<br/>(10.35, 10.25, 7.2 or 4.5 MHz)</li> </ul>                                                                                                                                                                                                                                                                                         | A13297      |

| PLL IN                    | 18             | Local<br>oscillator<br>signal input | <ul> <li>FMIN is selected when DVS in the serial data input is set to 1.</li> <li>The input frequency range is from 10 to 160 MHz.</li> <li>The signal is transmitted to the swallow counter.</li> <li>The divisor can be set to a value in the range 272 to 65535.</li> </ul>                                                                                                        | A13298      |

| CE                        | 27             | Chip enable                         | • This pin is set high during serial data input to the PLL (DI) or during serial data output (DO).                                                                                                                                                                                                                                                                                    | A13299      |

| CL                        | 29             | Clock                               | <ul> <li>This pin is the clock for data synchronization<br/>during serial data input to the PLL (DI) or<br/>during serial data output (DO).</li> </ul>                                                                                                                                                                                                                                | A13300      |

| DI                        | 28             | Input data                          | • This is the input pin for serial data that is transferred from the controller to the PLL.                                                                                                                                                                                                                                                                                           | A13301      |

| DO                        | 30             | Output data                         | • This is the output pin for serial data that is transferred from the controller to the PLL.                                                                                                                                                                                                                                                                                          | A13302      |

| VDD                       | 19             | Power supply                        | <ul> <li>This is the PLL power supply pin. Supply 4.5 V to 5.5 V to this pin when the PLL is operating.</li> <li>When power is first applied to this pin, the power-on reset circuit operates.</li> </ul>                                                                                                                                                                             |             |

| Vss                       | 21             | Ground                              | This is the PLL ground pin.                                                                                                                                                                                                                                                                                                                                                           |             |

| I/O-1<br>I/O-2<br>STSD SW | 31<br>24<br>17 | General-<br>purpose<br>I/O ports    | <ul> <li>These are general-purpose I/O ports.</li> <li>The output circuits open-drain.</li> <li>During a power-on reset, I/O-1 and I/O-2 become input ports. STSD SW becomes an output port, and is fixed low.</li> <li>These ports can be switched between input and output according to the serial data that is transferred from the controller (I/O-1, I/O-2, STSD SW).</li> </ul> | A13303      |

| SEEK SW                   | 33             | General-<br>purpose<br>I/O port     | <ul> <li>This is a general-purpose I/O port.</li> <li>The output circuits are complementary circuits.</li> <li>During a power-on reset, this port becomes an input port.</li> <li>This port can be specified as an input or output port by the serial data that is transferred from the controller.</li> </ul>                                                                        | A13304      |

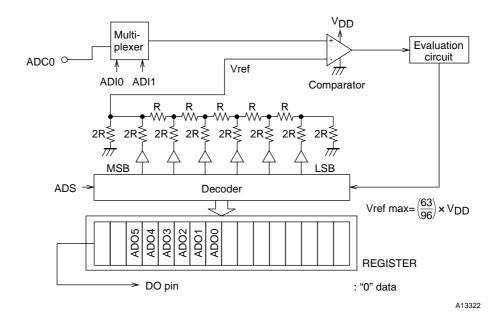

| ADC0                      | 34             | ADC input                           | <ul> <li>This is the A/D converter input pin.<br/>The converter is a 6-bit successive-approximation A/D converter.<br/>For details, refer to the page that describes the A/D converter configuration.</li> </ul>                                                                                                                                                                      |             |

#### Continued from preceding page.

| Symbol | Pin No.                                   | Description                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin Circuit |

|--------|-------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

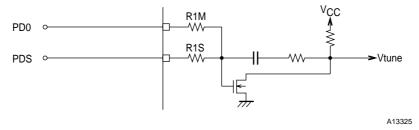

| PD1    | PD1 20 Main<br>0 charge<br>pump<br>output |                                | • This is the PLL charge pump output pin.<br>When the frequency of the local oscillation<br>signal frequency is divided by N is higher than<br>the reference frequency, a high level signal is<br>output from the PD1 pin. When the frequency<br>is lower, a low level signal is output. If the<br>frequencies match, the pin goes to high<br>impedance.                                                                                                                                                                             | A13306      |

| PDS    | 22                                        | Sub-charge<br>pump<br>output   | <ul> <li>A high-speed lockup circuit can be formed by<br/>using this pin in combination with the main<br/>charge pump.</li> <li>For details, refer to page that describes the<br/>charge pump configuration.</li> </ul>                                                                                                                                                                                                                                                                                                              |             |

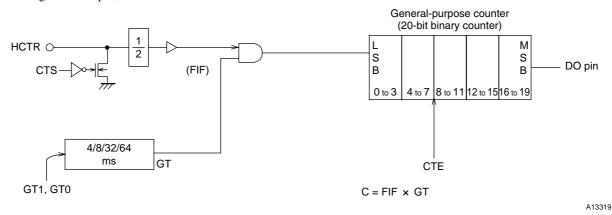

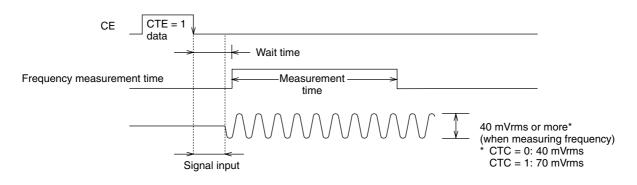

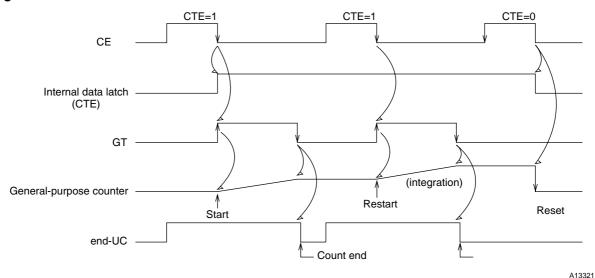

| HCTR   | 32                                        | General-<br>purpose<br>counter | <ul> <li>Serial data: HCTR is selected if CTS1 = 1 is set.</li> <li>The input frequency is 0.4 to 25 MHz.</li> <li>The signal is passed through to the general-purpose counter internally, via the 1/2 frequency divider. An integrating count can also be kept.</li> <li>The count result is output from the MSB of the general-purpose counter through the output pin DO.</li> <li>For details, refer to page that describes the general-purpose counter configuration.</li> <li>Serial data: Prohibited when HCTR = 0.</li> </ul> | A13308      |

| XBUF   | 23                                        | X'tal<br>oscillator<br>buffer  | <ul> <li>This is the output buffer for the crystal oscillator circuit.</li> <li>Serial data: When XB = 1 is set, the output buffer operates and the crystal oscillator signal (pulse) is output.<br/>When XB = 0, this pin outputs a low level.<br/>(When a power-on reset is executed, XB = 0 and the output buffer is fixed at the low level.)</li> </ul>                                                                                                                                                                          | XOUT        |

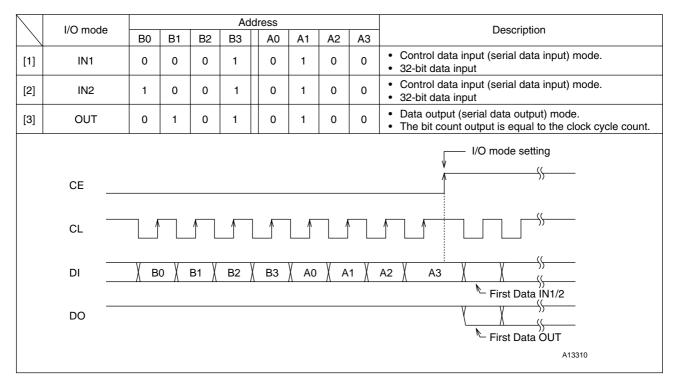

#### Procedures for Input and Output of Serial Data

Data I/O is handled through the Computer Control Bus (CCB), SANYO's audio IC serial bus format. This IC uses CCB with 8-bit addressing.

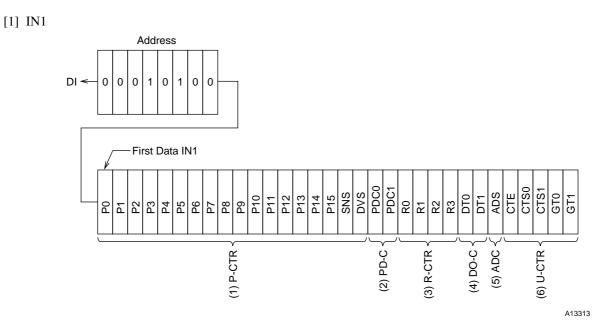

#### i) Serial Data Input (IN1/IN2)

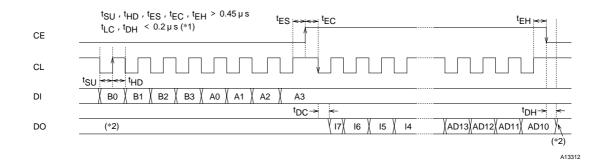

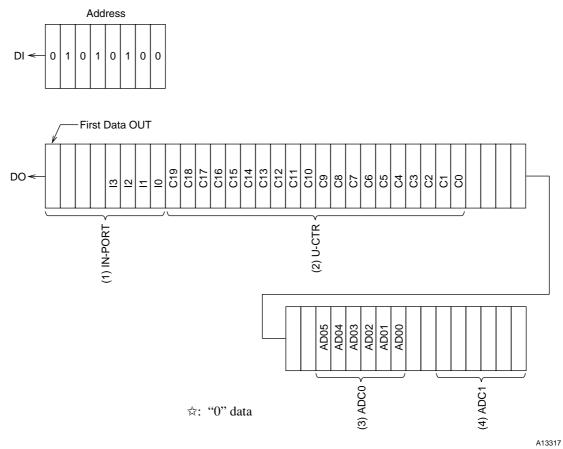

## ii) Serial data output (OUT)

\*1: Because the DO pin is an N-channel open drain pin, the data transition time varies according to the pull-up resistance and the board capacitance.

\*2: The DO pin is normally open.

## DI Control Data (Serial Data Input) Configuration

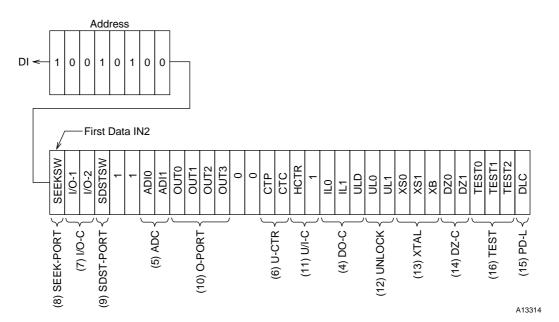

## [2] IN2 Mode

## **Description of DI Control Data**

| No. | Control block/Data              | Description |                                |                          |                                                                                       |                                    |                                                                                                                                            | Related data     |

|-----|---------------------------------|-------------|--------------------------------|--------------------------|---------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|     | Programmable divider data       |             |                                |                          |                                                                                       |                                    | the programmable divider. P15 is a binary value that is The LSB changes depending on DVS and SNS.                                          |                  |

|     | P0 to P15                       |             | DVS                            |                          |                                                                                       |                                    |                                                                                                                                            |                  |

|     |                                 |             | 1                              | 1                        |                                                                                       | P0                                 | 272 to 65535                                                                                                                               |                  |

| (1) |                                 | •           |                                |                          |                                                                                       |                                    |                                                                                                                                            |                  |

|     | DVS, SNS                        |             | DVS                            | SN                       | IS                                                                                    | Input pir                          | n Input pin frequency range                                                                                                                |                  |

|     |                                 |             | 1                              | 1                        |                                                                                       | PLLIN                              | 10 to 160 MHz                                                                                                                              |                  |

|     |                                 |             | * For de                       | etails                   | , ref                                                                                 | er to "Pro                         | ogrammable Divider Configuration."                                                                                                         |                  |

|     | Sub-charge pump<br>control data | •           | This da                        | ta co                    | ntro                                                                                  | ls the su                          | b-charge pump.                                                                                                                             |                  |

|     | control data                    |             | PDC                            | 1                        | Ρ                                                                                     | PDC0                               | Subcharge pump status                                                                                                                      | UL0, UL1,<br>DLC |

| (2) | PDC, PDC1                       |             |                                |                          | High impedance<br>Charge pump on (when unlocked)<br>Charge pump on (normal operation) |                                    |                                                                                                                                            |                  |

|     | Reference divider data          | •           | combi<br>For deta              | natio<br>ails, r         | n w<br>refe                                                                           | r to the p                         | can be used to form a high-speed lockup circuit in<br>and PD1 (main charge pump).<br>bage on charge pump.<br>quency (fref) selection data. |                  |

|     |                                 | [           | R3 F                           | 32                       | R1                                                                                    | R0                                 | Reference frequency                                                                                                                        |                  |

|     |                                 |             | 0                              | 0                        | 0                                                                                     | 0                                  | Prohibited                                                                                                                                 |                  |

|     |                                 |             | 0                              | 0                        | 0                                                                                     | 1                                  | 50                                                                                                                                         |                  |

|     |                                 |             | 0                              | 0                        | 1                                                                                     | 0                                  | 25                                                                                                                                         |                  |

|     |                                 |             | -                              | 0                        | 1                                                                                     | 1                                  | 25                                                                                                                                         |                  |

|     |                                 |             | -                              | 1                        | 0                                                                                     | 0                                  | 12.5                                                                                                                                       |                  |

|     |                                 |             |                                | 1                        | 0<br>1                                                                                | 1                                  | 6.25                                                                                                                                       |                  |

|     |                                 |             | -                              | 1                        | 1                                                                                     | 0                                  | <u>3.125</u><br><u>3.125</u>                                                                                                               |                  |

|     | R0 to R3                        |             | -                              | 0                        | 0                                                                                     | 0                                  | 10                                                                                                                                         |                  |