Monolithic Linear IC

No.505G

PLL FM MULTIPLEX STEREO DEMODULATOR

Use

The LA3361, PLL FM multiplex stereo demodulator, is designed for low supply voltage-use appliance such as portable radio or car stereo.

## Features

- Wide supply voltage range down to low supply voltage: 3V min. 1.

- Operation of forced monaural (IF muting) or VCO stopping by only one pin. Depending on supply voltage:

0.7V < V9 < 2.1V: forced monaural (IF muting) V9 > 2.1V: VCO stopping

- 3. Good ripple rejection.

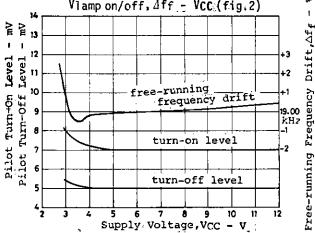

- 4. High level of lamp turning-on sensitivity: 7mV.

- With separation control pin.

- High gain. 6.

- 7. Less current consumption: 8.5mA typical.

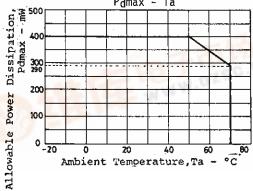

| Maximum Ratings at Ta=25°C      |                |         |             | unit |

|---------------------------------|----------------|---------|-------------|------|

| Maximum Supply Voltage          | VCCmax         | pin 6-7 | 16          | V    |

| AND WWW.DZ                      |                | pin 1-7 | 16          | V    |

| Lamp Driving Current            | IL             |         | 40          | mΑ   |

| Allowable Power Dissipation     | Pdmax          | Ta≦50°C | 400         | mW   |

| Operation Temperature           | Topr           |         | -20 to +70  | °C   |

| Storage Temperature             | Tstg           |         | -40 to +125 | °C   |

| Recommended Operating Condition | s at Ta=25     | °C      |             | unit |

| Recommended Supply Voltage      | $v_{CC}$       |         | 6           | V    |

| Input Signal Voltage            | v <sub>i</sub> |         | 100 to 200  | mV   |

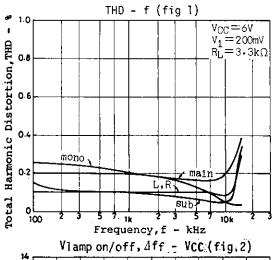

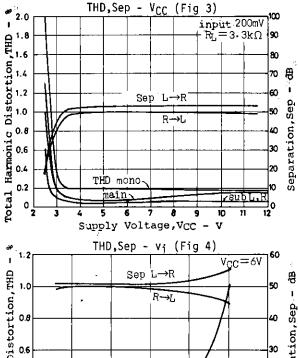

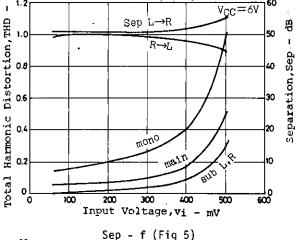

Operating Characteristics at Ta=25°C, VCC=6V, RL=3.3kohms, input=100mV, L+R=90%, pilot= 10%, f=1kHz: min tvp max unit

|                          | 70017 7 |             | ***** | ~J L | 1110421 | C4111 C | - |

|--------------------------|---------|-------------|-------|------|---------|---------|---|

| Quiescent Current        | Icco    |             |       | 8.5  | 12.0    | mA      |   |

| Input Resistance         | ri      |             | 15k   | 20k  |         | ohm     |   |

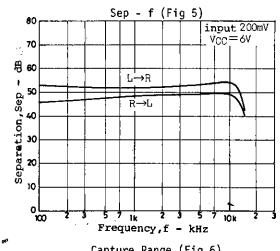

| Channel Separation       |         |             | 35    | 45   |         | dΒ      |   |

| Total Harmonic Distortio | n THD   | stereo, sub |       | 0.2  | 0.7     | ક       |   |

| Output Voltage           | $v_{O}$ | vi=100mV    | 66    | 85   | 115     | mV      |   |

| Channel Balance          |         |             |       | 0.5  | 1.5     | dB      |   |

|                          |         |             |       |      |         |         |   |

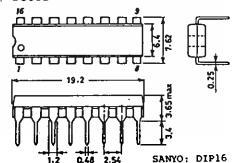

Continued on next page. Pdmax - Ta **Package Dimensions** (unit: mm) 3006B

| Continued from preceding | page.            |                   | min typ | max | unit |

|--------------------------|------------------|-------------------|---------|-----|------|

| Lamp Turn-on Level       | $v_{\mathbf{L}}$ | L+R=90%,pilot=10% | 65      |     | mV   |

| Hysteresis               | hy               |                   | 3.5     | 6.0 | đ₿   |

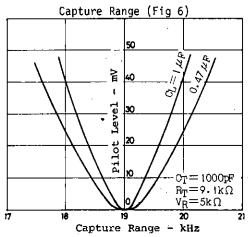

| Capture Range            | CR               |                   | ±2.5    |     | 8    |

| Allowable Input Level    | Vi               | THD=2%            | 450     |     | mV   |

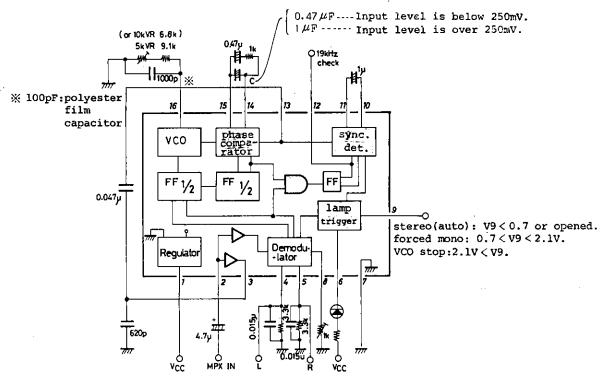

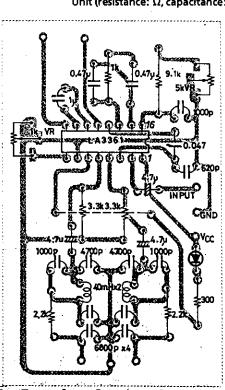

## Equivalent Circuit Block Diagram and Peripheral Circuit

Unit (resistance:  $\Omega$ , capacitance: F)

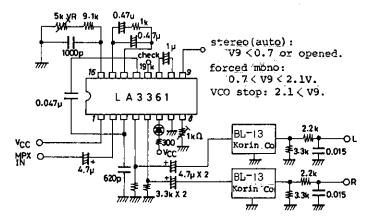

## Sample Application Circuit

```

V<sub>CC</sub>=6V

T<sub>a</sub>=25°C

f=1kHz

input

signal level=200mV

[pilot=10%]

L+R=45%

L-R=45%]

```

An Example of Printed Pattern Using LC Filter (Cu-foiled area, 50x82mm<sup>2</sup>)

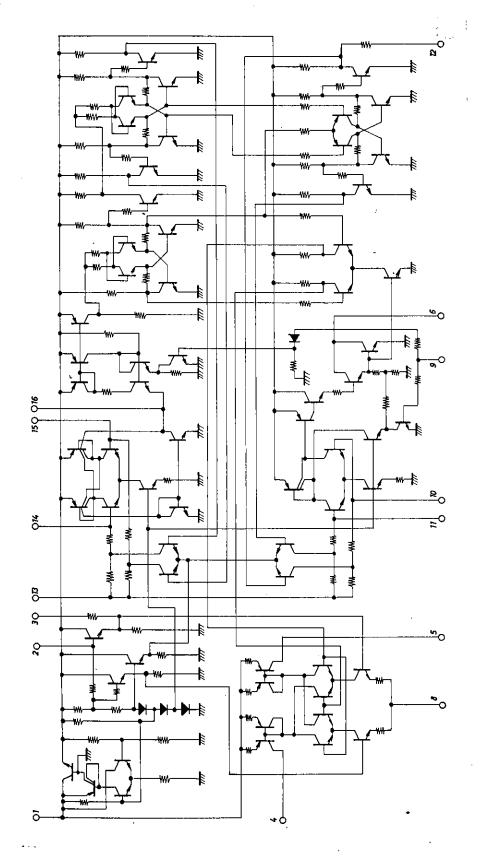

Equivalent Circuit

Unit (resistance:  $\Omega$ , capacitance: F)

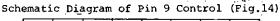

Proper cares in using the IC (1) Pin 9-used control

Pin 9 is for stereo/monaural selection and VCO stop. When a voltage of less than 0.7V is applied to pin 9 or pin 9 is grounded or brought into the open state, the stereo (automatic) mode is entered. When a voltage of more than 2.1V is applied to pin 9, the VCO stops operating and the stereo indicator is prevented from malfunctioning. Therefore, no external measure against malfunction is required. When applying a voltage to pin 9, the following should be noted. applied voltage of approximately 0.7V or 2.1V causes the internal transistors to enter the active region and hum or noise is liable to enter pin 9. Therefore, for example, the applied voltage must be set to an intermediate voltage such as 0V, 1.4V, 2.8V.

When the VCO stop mode caused by application of a voltage to pin 9 is released, the stereo indicator may be turned ON momentarily. This phenomenon is liable to occur if the value of the capacitor across pins 10 and 11 is large  $(C_{10-11}>2 \text{ to } 3uF)$ . The reason for this is that if the VCO stop mode and forced monaural mode are released simultaneously when the Cl0-11 is charged with the pin 10 side being at "H" level at the VCO stop mode, the trigger circuit is turned ON until the C10-11 is discharged. This can be prevented by making the release of the forced monuaral mode a little

later than that of the VCO stop mode. For this purpose, the C9 is connected across pin 9 and GND as shown below so that the voltage on pin 9 drops slowly at the time of release.

C9>2C10-11 is a rule-of-thumb guide for the relation between C9 and C10-11 which prevents the stereo indicator from being turned ON mistakenly.

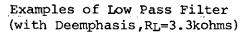

- (2) Loop filter capacitor C14-15 When your set is designed with an input signal level of 250mV or greater, the C14-15 is luf. The capture range tends to extend with the input level. When your set is designed with a high input signal level of 250mV or greater, your set is liable to be affected by highfrequency signals or noises. Therefore, the loop filter capacitor (across pins 14 and 15) should be made large to narrow the filter bandwidth. If C14-15=luF is used in your set with an input signal level of 250mV or greater, the capture range is made a little narrower and your set is hard to be affected by high-frequency signals.

- (3) Phase compensation capacitor (See Fig.8.) A capacitor of 620pF is connected across pin 3 and GND to compensate the phase lead caused by the decoupling capacitor across pins 3 and 13 and the phase shift caused by the PLL. If no phase compensation capacitor is connected, the center of the separation characteristic plotted against the free-running frequency is off 19.00kHz and the margin for the free-running frequency drift and adjustment error becomes narrow. Therefore, phase compensation should be done.

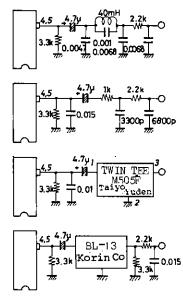

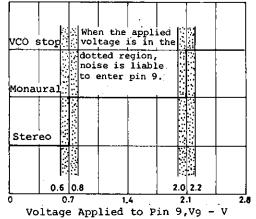

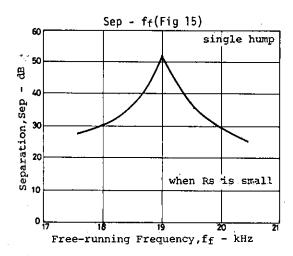

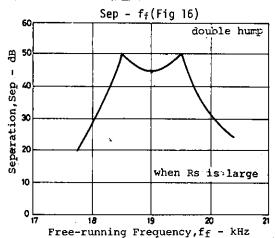

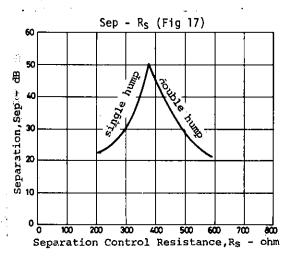

- (4) Separation control The separation control is done to provide a single or double hump response in the separation vs. free-running frequency characteristic as shown on next page.

As is obvious from the figure shown above, the double hump response has more margin for the free-funning frequency drift. The double hump response is obtained by setting separation control resistance RS to a rather large value. The separation varies with RS as shown above and has peak point at RS.380kohms give the single hump response. Separation control should be done at a point a little off this peak on the double

hump response side. For further details on separation, see the catalog of the LA3350.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.