Ordering number: EN5719

Monolithic Linear IC

# **LA5623M**

# **Combination System Reset IC**

### Overview

The LA5623M is a combination reset IC that provides two reset functions. The first, reset 1, detects the input voltage and applies a reset to the CPU system and other logic systems. The second, reset 2, detects the power supply voltage when the power is turned on or off, and applies a reset to the CPU system and other logic systems. This latter function allows the reset time to be adjusted from two external pins.

WWW.DZSC.CO

#### **Features**

- Reset circuit (output 1) that detects the input voltage and provides a delay time of 200 µs.

- System reset circuit (output 2) that provides a switchable delay time of 25, 50, 100, or 200 ms.

- Low operating limit voltage

- Both reset 1 and reset 2 have hysteresis characteristics.

# **Specifications**

Maximum Ratings at Ta = 25°C

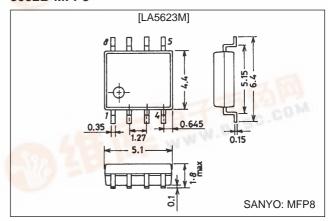

# Package Dimensions

unit: mm

#### 3032B-MFP8

| Parameter                   | Symbol              | Conditions    | . 0 | Unit |

|-----------------------------|---------------------|---------------|-----|------|

| Supply voltage              | V <sub>CC</sub>     | -0.3 to +     | 12  | V    |

| Output 1 sink current       | I <sub>SINK</sub> 1 | A PART OF WAY | 8   | mA   |

| Output 2 sink current       | I <sub>SINK</sub> 2 | AVA 6 Da      | 8   | mA   |

| Output voltage              | Vo                  | -0.3 to +     | 10  | V    |

| Manual input voltage        | V <sub>RES</sub>    | -0.3 to +     | 10  | V    |

| Input voltage range         | V <sub>IN</sub> 1   | -0.3 to +     | 10  | V    |

| Ct0, Ct1 voltage            | Vct                 | 0 to +        | 10  | V    |

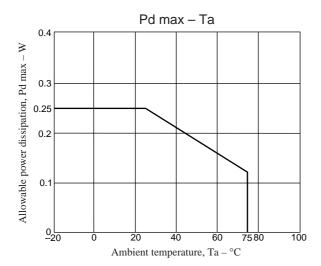

| Allowable power dissipation | Pd max              | 2             | 50  | mW   |

| Operating temperature       | Topr                | -20 to +      | 75  | °C   |

| Storage temperature         | Tstg                | -40 to +1     | 25  | °C   |

#### Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                  | Symbol            | Conditions                      | Ratings                   | Unit |

|----------------------------|-------------------|---------------------------------|---------------------------|------|

| Recommended supply voltage | V <sub>CC</sub>   | 180                             | 2 to 10                   | V    |

| Input voltage range        | V <sub>IN</sub>   | For pulse widths of up to 20 ns | –2 to V <sub>CC</sub> + 1 | V    |

| Input high-level voltage   | V <sub>RESH</sub> | For pulse widths of up to 20 ns | V <sub>CC</sub> + 1       | V    |

| Input low-level voltage    | V <sub>RESL</sub> | For pulse widths of up to 20 ns | -2                        | V    |

## LA5623M

# Operating Characteristics at $Ta=25^{\circ}C,\,V_{CC}$ = 5~V

| Parameter                                 | O. mahad            | Conditions                                                    |                     | Ratings |      |      |

|-------------------------------------------|---------------------|---------------------------------------------------------------|---------------------|---------|------|------|

| Parameter                                 | Symbol              | Conditions                                                    | min                 | typ     | max  | Unit |

| [Reset Circuit 1, 2 Common]               |                     |                                                               |                     |         |      |      |

| Current drain when off                    | I <sub>CC</sub> 1   |                                                               | _                   | 1.4     | 2.0  | mA   |

| Current drain when on                     | I <sub>CC</sub> 2   | When reset 1 and 2 are both on                                | _                   | 2       | 3    | mA   |

| Detection voltage temperature coefficient | VS/ΔT               |                                                               | _                   | 0.01    |      | %/°C |

| Output high-level voltage                 | V <sub>OH</sub>     | I <sub>OH</sub> = -40 μA                                      | 0.9 V <sub>CC</sub> | -       | -    | V    |

| Low-level signal propagation delay        | tPHL                | C <sub>L</sub> = 100 pF                                       | _                   | 10      | -    | μs   |

|                                           |                     | $R_L = 2.2 \text{ k}\Omega, \text{ V(sat)} \le 0.4 \text{ V}$ | _                   | 0.67    | 0.80 | V    |

| Operating limit voltage *1                | V <sub>OPL</sub>    | R <sub>L</sub> = 100 kΩ, V(sat) ≤ 0.4 V                       | -                   | 0.55    | 0.70 | ٧    |

| Internal pull-up resistance               | R                   |                                                               | 5                   | 10      | 15   | kΩ   |

| [Reset Circuit 1]                         |                     |                                                               |                     |         |      |      |

| Sense voltage 1                           | VS1                 |                                                               | 1.20                | 1.25    | 1.30 | V    |

| Hysteresis voltage 1                      | ΔVS1                |                                                               | 9                   | 15      | 23   | mV   |

| High-level signal propagation delay 1     | tPLH1               | C <sub>L</sub> = 100 pF                                       | 80                  | 200     | 500  | μs   |

| Output low voltage 1                      | V <sub>OL</sub> 1   | V <sub>IN</sub> < 1.2 V, I <sub>OL</sub> = 5 mA               | _                   | 0.2     | 0.4  | V    |

| Input voltage range                       | V <sub>IN</sub> 1   |                                                               | -0.3                | -       | +10  | V    |

| Input current                             | I <sub>IN</sub> 1   | V <sub>IN</sub> = 1.25 V                                      | _                   | 100     | 500  | nA   |

| [Reset Circuit 2]                         |                     |                                                               |                     |         |      |      |

| Sense voltage 2                           | VS2                 |                                                               | 4.0                 | 4.2     | 4.4  | V    |

| Hysteresis voltage 2                      | ΔVS2                |                                                               | 30                  | 50      | 100  | mV   |

| High-level signal propagation delay 2     |                     | Ct0 = "L", Ct1 = "H" : CL = 100pF                             | 15                  | 25      | 35   | ms   |

|                                           | (5) 110             | Ct0 = "H", Ct1 = "L" : CL = 100pF                             | 30                  | 50      | 70   | ms   |

|                                           | tPLH2               | Ct0 = "H", Ct1 = "H" : CL = 100pF                             | 60                  | 100     | 140  | ms   |

|                                           |                     | Ct0 = "L", Ct1 = "L" : CL = 100pF                             | 120                 | 200     | 280  | ms   |

| Output low-level voltage 2                | V <sub>OL</sub> 2   | V <sub>CC</sub> < 4.0 V, I <sub>OL</sub> = 5 mA               | _                   | 0.2     | 0.4  | V    |

| Input high-level voltage *2               | V <sub>RESH</sub> 2 |                                                               | 2                   | -       | 10   | V    |

| Input high-level current *2               | I <sub>RESH</sub> 2 | V <sub>RES</sub> = 2 V                                        | _                   | -       | 80   | μA   |

| Input low-level voltage *2                | V <sub>RESL</sub> 2 |                                                               | -0.3                | _       | +0.8 | V    |

Notes: 1. The minimum supply voltage such that a low-level output can be maintained.

2. Manual reset.

A high level applied to the manual reset pin sets the output 2 pin low, and a low level sets the output 2 pin high.

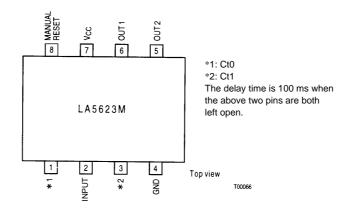

## **Pin Assignment**

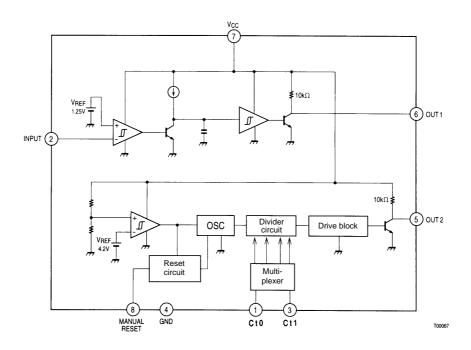

## **Block Diagram**

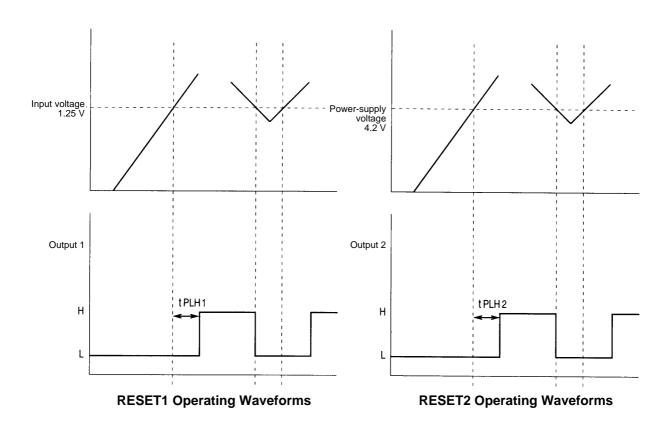

## **Operating Waveforms**

#### **RESET2 Truth Table**

| Ct0       | Ct1       | RESET2 delay time |

|-----------|-----------|-------------------|

| L         | Н         | 25 ms             |

| Н         | L         | 50 ms             |

| H or OPEN | H or OPEN | 100 ms            |

| L         | L         | 200 ms            |

#### **MANUAL RESET Truth Table**

| MANUAL RESET | OUT2 |

|--------------|------|

| Н            | L    |

| L            | Н    |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1997. Specifications and information herein are subject to change without notice.