#### 捷多邦,专业PCB打样工厂,24小时加急出货

Monolithic Linear IC

## LA6541D

# 4-channel Bridge Driver for Compact Discs

# **Functions and Features**

- 4-channel bridge (BTL) power amplifier.

- I<sub>O</sub> max. 700 mA.

- With mute circuit (Affects all amplifier outputs, Amp 1 to Amp 8).

(When the mute voltage is low, the outputs turn off; when the mute voltage is high, the outputs turn on).

WW.DZSC.CO

- 5.0 V regulator built in (Uses external PNP transistor).

- Reset circuit built in (The reset output delay time can be adjusted through an external capacitor).

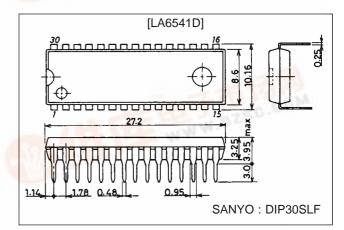

# Package Dimensions

#### 3196-DIP30SLF

# **Specifications**

#### Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                                        | Ratings     | Unit |

|-----------------------------|---------------------|---------------------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |                                                   | 14          | V    |

| Maximum input voltage       | VIN                 |                                                   | 13          | V    |

| Mute pin voltage            | V <sub>Mute</sub>   |                                                   | 13          | V    |

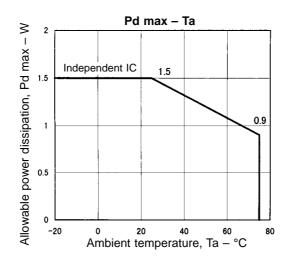

| Allowable power dissipation | Pd max              | When using standard board (material: glass epoxy) | 2.5         | W    |

| Operating temperature       | Topr                |                                                   | -20 to +75  | °C   |

| Storage temperature         | Tstg                |                                                   | -55 to +150 | °C   |

#### Recommended Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                   | Symbol          | Conditions     | Ratings   | Unit |

|-----------------------------|-----------------|----------------|-----------|------|

| Operating voltage           | V <sub>CC</sub> | ASA 7. 62. 1-1 | 5.6 to 13 | V    |

| Reset output source current | IORH            |                | 0 to 200  | μA   |

| Reset output sink current   | IORL            |                | 0 to 2    | mA   |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 8.0 V, $V_{REF}$ = 4 V

| Parameter                            | Symbol             | Conditions                                                                                                       | min  | typ  | max                  | Unit |

|--------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|------|------|----------------------|------|

| No-load current drain                | I <sub>CC</sub> 1  | When all amplifier outputs are on (Mute high)                                                                    |      | 20   | 40                   | mA   |

| No-load current drain                | I <sub>CC</sub> 2  | When all amplifier outputs are off (Mute low)                                                                    |      | 15   | 35                   | mA   |

| Output offect voltage                | V <sub>OF</sub> 1  | $\begin{array}{l} \mbox{Amplifier 1 to 2 (V_O1 to V_O2),} \\ \mbox{Amplifier 3 to 4 (V_O3 to V_O4)} \end{array}$ |      |      | 50                   | mV   |

| Output offset voltage                | V <sub>OF</sub> 2  | Amplifier 5 to 6 (V <sub>O</sub> 5 to V <sub>O</sub> 6), Amplifier 7 to 8 (V <sub>O</sub> 7 to V <sub>O</sub> 8) | -50  |      | 50                   | mV   |

| Buffer amplifier input voltage range | V <sub>BIN</sub>   |                                                                                                                  | 1.5  |      | V <sub>CC</sub> -1.5 | V    |

| Input voltage range                  | V <sub>IN</sub>    |                                                                                                                  | 1.0  |      | V <sub>CC</sub> -1.5 | V    |

| Output source voltage                | V <sub>O</sub> 1   | Note 1, when $R_L = 8.0 \Omega$                                                                                  | 5.0  | 5.6  |                      | V    |

| Output sink voltage                  | V <sub>O</sub> 2   | Note 2, when $R_L = 8.0 \Omega$                                                                                  |      | 1.8  | 2.4                  | V    |

| Closed-circuit voltage gain          | VG                 | Between bridge amplifiers                                                                                        |      | 9    |                      | dB   |

| Slew rate                            | SR                 |                                                                                                                  |      | 0.15 |                      | V/µs |

| Mute on voltage                      | V <sub>Mute</sub>  | Note 3                                                                                                           |      | 1.2  |                      | V    |

| [Power Supply] (with 2SK632K c       | connected exte     | rnally)                                                                                                          |      |      |                      |      |

| Output voltage                       | V <sub>OUT</sub> 1 | I <sub>O</sub> = 200 mA                                                                                          | 4.75 | 5.0  | 5.25                 | V    |

| Line regulation                      | $\Delta V_{OLN}$ 1 | $5.6 \leq V_{IN} 1 \leq 12 V$                                                                                    |      | 20   | 100                  | mV   |

| Load regulation                      | $\Delta V_{OLD}$ 1 | $5 \text{ mA} \leq I_{O} \leq 200 \text{ mA}$                                                                    |      | 50   | 150                  | mV   |

| [Reset]                              |                    |                                                                                                                  |      |      |                      |      |

| High reset output voltage            | V <sub>ORH</sub>   | I <sub>ORH</sub> = 200 μA, Cd pin open                                                                           | 4.73 | 4.98 | 5.23                 | V    |

| Low reset output voltage             | V <sub>ORL</sub>   | I <sub>SRL</sub> = 2 mA, Cd is shorted to GND                                                                    |      | 100  | 200                  | mV   |

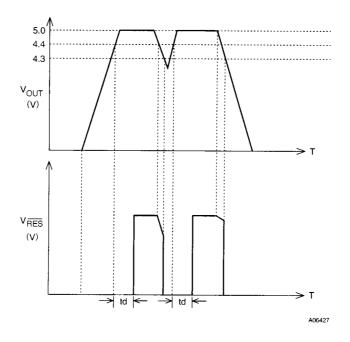

| Reset threshold voltage              | V <sub>RT</sub>    | Note 4                                                                                                           |      | 4.3  |                      | V    |

| Reset hysteresis voltage             | Vhys               | Note 5                                                                                                           | 40   | 100  | 200                  | mV   |

| Reset output delay time              | td                 | Cd = 0.1 µF                                                                                                      |      | 10   |                      | ms   |

Notes:

- 1. Source voltage to ground when an  $8 \Omega$  load is connected between bridge amplifier outputs.

- 2. Sink voltage to ground when an 8  $\Omega$  load is connected between bridge amplifier outputs.

- 3. When the mute signal is high, all amplifier outputs turn on, and when low, all amplifier outputs turn off. When the mute signal is low, amplifier output is undefined.

- 4. 5 V supply voltage when the reset output goes low.

- 5. Potential difference from the 5 V supply voltage when the reset output goes low and when it goes high.

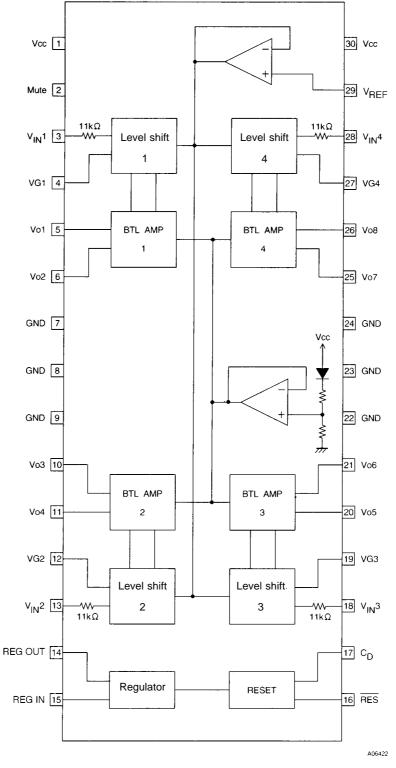

### **Pin Functions**

| Pin No. | Pin Name          | Description (Function)                                                   |

|---------|-------------------|--------------------------------------------------------------------------|

| 1       | V <sub>CC</sub>   | Power supply (shorted with pin 30)                                       |

| 2       | Mute              | ON/OFF control for all BTL AMP outputs                                   |

| 3       | V <sub>IN</sub> 1 | BTL AMP 1 input                                                          |

| 4       | VG1               | BTL AMP 1 input (for gain control)                                       |

| 5       | V <sub>O</sub> 1  | BTL AMP 1 output (non-inverting side)                                    |

| 6       | V <sub>O</sub> 2  | BTL AMP 1 output (inverting side)                                        |

| 7       | GND               | GND (minimum electric potential)                                         |

| 8       | GND               | GND (minimum electric potential)                                         |

| 9       | GND               | GND (minimum electric potential)                                         |

| 10      | V <sub>O</sub> 3  | BTL AMP 2 output (inverting side)                                        |

| 11      | V <sub>O</sub> 4  | BTL AMP 2 output (non-inverting side)                                    |

| 12      | VG2               | BTL AMP 2 input (for gain control)                                       |

| 13      | V <sub>IN</sub> 2 | BTL AMP 2 input                                                          |

| 14      | REG OUT           | Connection for collector of external transistor (PNP); 5 V supply output |

| 15      | REG IN            | Connection for base of external transistor (PNP)                         |

| 16      | RES               | Reset output                                                             |

| 17      | CD                | Reset output delay time setting (with capacitor)                         |

| 18      | V <sub>IN</sub> 3 | BTL AMP 3 input                                                          |

| 19      | VG3               | BTL AMP 3 input (for gain control)                                       |

| 20      | V <sub>O</sub> 5  | BTL AMP 3 output (non-inverting side)                                    |

| 21      | V <sub>O</sub> 6  | BTL AMP 3 output (inverting side)                                        |

| 22      | GND               | GND (minimum electric potential)                                         |

| 23      | GND               | GND (minimum electric potential)                                         |

| 24      | GND               | GND (minimum electric potential)                                         |

| 25      | V <sub>O</sub> 7  | BTL AMP 4 output (inverting side)                                        |

| 26      | V <sub>O</sub> 8  | BTL AMP 4 output (non-inverting side)                                    |

| 27      | VG4               | BTL AMP 4 input (for gain control)                                       |

| 28      | V <sub>IN</sub> 4 | BTL AMP 4 input                                                          |

| 29      | V <sub>REF</sub>  | Reference voltage input for level shift circuit                          |

| 30      | V <sub>CC</sub>   | Power supply (shorted with pin 1)                                        |

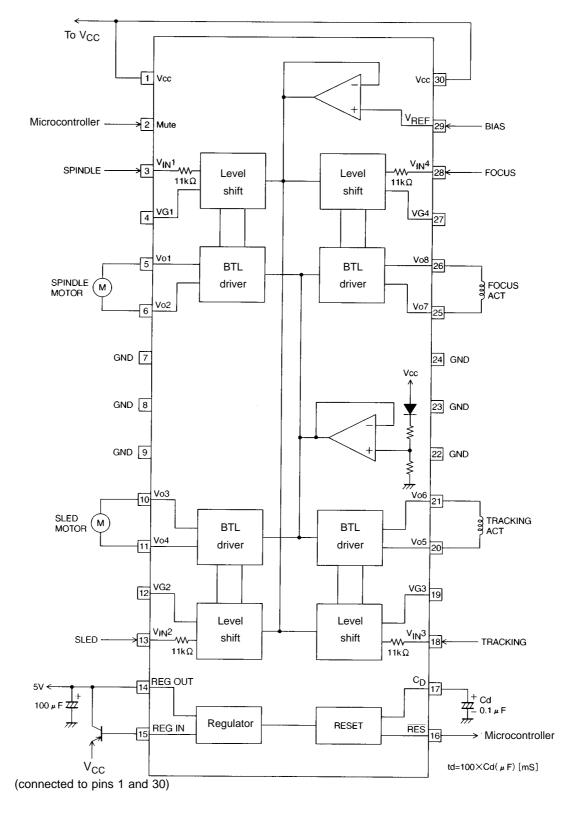

## Pin Assignment (Block Diagram)

Top view

## **Sample Application Circuit**

A06423

Note: Use a delay capacitor (Cd) whose capacitance does not change much according to the temperature.

## **Pin Functions**

| Pin    | Name                                                                                                                                                 | Pin No.                                    | Equivalent Circuit                                                                                                                                                                                                         | Description   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Input  | V <sub>IN</sub> 1<br>V <sub>IN</sub> 2<br>V <sub>IN</sub> 3<br>V <sub>IN</sub> 4<br>VG1<br>VG2<br>VG3<br>VG4                                         | 3<br>13<br>18<br>28<br>4<br>12<br>19<br>27 | $\begin{array}{c} \hline \\ 3,13,18,28 \\ \hline \\ V_{IN} \\ 11k\Omega \\ \hline \\ VG \\ 4,12,19,27 \\ \hline \\ 29 \\ \hline \\ V_{REF} \\ \hline \\ \\ NG \\ 7.8,9,22,23,24 \\ \hline \\ A06424 \\ \hline \end{array}$ | Input pins    |

| Output | V <sub>0</sub> 1, V <sub>0</sub> 2<br>V <sub>0</sub> 3, V <sub>0</sub> 4<br>V <sub>0</sub> 5, V <sub>0</sub> 6<br>V <sub>0</sub> 7, V <sub>0</sub> 8 | 5, 6<br>10, 11<br>20, 21<br>25, 26         | 5, 6<br>10, 11<br>20, 21<br>25, 26<br>OUT<br>GND<br>7, 8, 9, 22, 23, 24<br>A06425                                                                                                                                          | Output pins   |

| Mute   | Mute                                                                                                                                                 | 2                                          | Vcc<br>1,30<br>1,30<br>7,8,9,22,23,24<br>GND<br>2 MUTE<br>A06426                                                                                                                                                           | Output ON/OFF |

# Truth Table

|       | Input MUTE | CH1                        |                            | CH2                        |                            | CH3                        |                            | CH4                        |                            |

|-------|------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Input |            | V <sub>O</sub> 1<br>(Amp1) | V <sub>O</sub> 2<br>(Amp2) | V <sub>O</sub> 3<br>(Amp3) | V <sub>O</sub> 4<br>(Amp4) | V <sub>O</sub> 5<br>(Amp5) | V <sub>O</sub> 6<br>(Amp6) | V <sub>O</sub> 7<br>(Amp7) | V <sub>O</sub> 8<br>(Amp8) |

| н     | Н          | Н                          | L                          | L                          | Н                          | Н                          | L                          | L                          | Н                          |

|       | L          | —                          | —                          | —                          | —                          | —                          | —                          | —                          | —                          |

| L     | Н          | L                          | Н                          | Н                          | L                          | L                          | Н                          | Н                          | L                          |

|       | L          | —                          | —                          | —                          | —                          | —                          | —                          | _                          | —                          |

\* The "-" symbol means "undefined."

#### **Reset Operation**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1996. Specifications and information herein are subject to change without notice.