Monolithic Linear IC

No.4616

LA7945N

Closed Caption Signal (US specifications) **Extraction IC**

### Overview

The LA7945N extracts the closed caption signal overlapped in the video signal vertical retrace period and transfers the data and clock signal to a decoder IC. This IC requires the use of either an add-on type decoder, such as the LC7458B or 7457A (for I<sup>2</sup>C), or a microcontroller type decoder, such as the LC8640XX.

### **Functions**

- · Synchronization separation

- VCO

- Vertical countdown

- · Horizontal countdown

- · Data slicing

- Dual loop AFC

- · Field discrimination

- Lock detection

- Vertical/horizontal pulse output

### **Features**

- Adoption of a dual loop AFC allows the LA7945N to stably extract the caption signal.

- · Provides the pulse outputs required by caption decoder ICs.

# **Specifications**

# Maximum Ratings at Ta = 25°C

| Parameter                    | Symbol              | Condition | Rating      | Unit |

|------------------------------|---------------------|-----------|-------------|------|

| Maximum power supply voltage | V <sub>CC</sub> max |           | 7           | V    |

| Allowable power dissipation  | Pd max              | Ta≤70°C   | 250         | mW   |

| Operating temperature        | Topr                |           | -10 to +70  | °C   |

| Storage temperature          | Tstg                |           | -55 to +150 | °C   |

# Operating Conditions at Ta = 25°C

| Parameter                            | Symbol             | Rating     | Unit |

|--------------------------------------|--------------------|------------|------|

| Recommended power supply voltage     | V <sub>CC</sub>    | 5          | ٧    |

| Operating power supply voltage range | V <sub>CC</sub> op | 4.5 to 5.5 | V    |

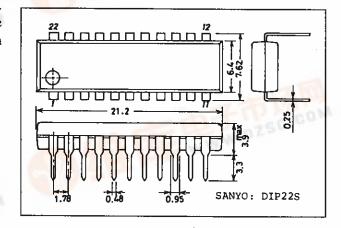

# Package Dimensions

3059-DIP22S

### **LA7945N**

# Electrical and Operating Characteristics at Ta = 25 $^{\circ}$ C, $V_{CC}$ = 5.0 V, Input signal: sync-white 1.0 V

|                                   |             |                     | Rating |      |      |      |

|-----------------------------------|-------------|---------------------|--------|------|------|------|

| Parameter                         |             | Symbol              | min    | typ  | max  | Unit |

| Horizontal pull-in range          |             | <sup>f</sup> HPULL  | ±1.5   |      |      | kHz  |

| Horizontal free-running frequency |             | fHFREE              | 15.3   | 15.7 | 16.3 | kHz  |

| Input clamping voltage            |             | V <sub>CLMP</sub>   | 2.3    | 2.5  | 2.7  | V    |

| H LOCK filter threshold level     |             | V <sub>LOCKTH</sub> | 2.3    | 2.5  | 2.7  | V ·  |

| Constitution and adding a second  | High level  | V <sub>SYNCH</sub>  | 4.0    | 4.2  | 5.0  | V    |

| Synchronization separation output | Low level   | V <sub>SYNCL</sub>  | 0      | 0.8  | 1.0  | V    |

| LLE COCK filter                   | High level  | V <sub>LOCKH</sub>  | 4.0    | 4.2  | 5.0  | V    |

| H LOCK filter                     | Low level   | VLOCKL              | 0      | 0.8  | 1.0  | v    |

| Data sutraut                      | High level  | V <sub>DATAH</sub>  | 4.0    | 4.2  | 5.0  | ٧    |

| Data output                       | Low level   | VDATAL              | 0      | 0.8  | 1.0  | ٧    |

| Olaska subsub                     | High level  | V <sub>CLKH</sub>   | 4.0    | 4.2  | 5.0  | V    |

| Clock output                      | Low level   | V <sub>CLKL</sub>   | 0      | 0.8  | 1.0  | ٧    |

|                                   | High level  | V <sub>21HH</sub>   | 4.0    | 4.2  | 5.0  | V    |

| 21H output                        | Low level   | V <sub>21HL</sub>   | 0      | 0.8  | 1.0  | ٧    |

|                                   | Pulse width | V <sub>21HW</sub>   | 60     | 65   | 70   | μs   |

|                                   | High level  | V <sub>OEH</sub>    | 4.0    | 4.2  | 5.0  | V    |

| O/E output                        | Low level   | V <sub>OEL</sub>    | 0      | 0.8  | 1.0  | V    |

|                                   | Pulse width | V <sub>OEW</sub>    | 16.4   | 16.7 | 17.0 | ms   |

|                                   | High level  | V <sub>HSH</sub>    | 4.0    | 4.2  | 5.0  | ٧    |

| Horizontal pulse output           | Low level   | V <sub>HSL</sub>    | 0      | 0.8  | 1.0  | ٧    |

|                                   | Pulse width | V <sub>HSW</sub>    | 7.4    | 7.7  | 8.0  | μs   |

| Vertical pulse output             | High level  | V <sub>RSTH</sub>   | 4.0    | 4.2  | 5.0  | V    |

|                                   | Low level   | V <sub>RSTL</sub>   | 0      | 0.8  | 1.0  | ٧    |

|                                   | Pulse width | V <sub>RSTW</sub>   | 30.8   | 31.8 | 32.8 | μs   |

| Input signal level                |             | VIN                 | -6     | 0    | +3   | dB   |

| CLK-RUN-IN start time             |             | TST                 | 6.6    | 7.6  | 8.6  | μs   |

| Current dissipation               |             | 1CC                 | 14.0   | 18.0 | 22.0 | mA   |

Note: Must not be pulled in to any frequency other than  $f_H$ . The pin 11 capacitor should be 100 pF ±5%. The pin 12 resistor should be 15 k $\Omega$  ±1%.

### LA7945N

### **Test Conditions**

| Parameter                         |             | Symbol              | Test point                          | Test method                                                                                                                               |

|-----------------------------------|-------------|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Horizontal pull-in range          |             | fHPULL              | Pins 2 and 10                       | Vary the frequency f <sub>H</sub> of the input signal and measure the point where the phase of pins 2 and 10 locks using an oscilloscope. |

| Horizontal free-running frequency |             | <sup>†</sup> HFREE  | Pin 10                              | Use a frequency counter to measure the frequency when there is no signal.                                                                 |

| Input clamping voltage            |             | V <sub>CLMP</sub>   | Pin 17                              | Measure the pedestal level with an oscilloscope.                                                                                          |

| H LOCK filter threshold level     |             | V <sub>LOCKTH</sub> | Pin 7                               | Measure the voltage at which pin 7 goes high by applying a DC voltage to pin 8 and varying that voltage.                                  |

| Synchronization separation output | High level  | V <sub>SYNCH</sub>  | Pin 2*1                             | Measure the pin 2 high and low levels with an oscilloscope.                                                                               |

|                                   | Low level   | VSYNCL              |                                     | model of the part rings and low totals with all occasiosope.                                                                              |

| H LOCK filter                     | High level  | VLOCKH              | Pin 7*1                             | Measure the pin 7 high and low levels with an oscilloscope.                                                                               |

|                                   | Low level   | VLOCKL              | 1 111 7                             | modulate and pin i might and loss levels with an oscilloscope.                                                                            |

| Data output                       | High level  | V <sub>DATAH</sub>  | Pin 3*1, 2                          | Measure the pin 3 high and low levels with an oscilloscope.                                                                               |

|                                   | Low level   | VDATAL              | 1 1113 11-                          | Weasone the pin 3 high and low levels with an oscilloscope.                                                                               |

| Clock output                      | High level  | V <sub>CLKH</sub>   | Pin 5*1, 2                          | Measure the pin 5 high and low levels with an oscilloscope.                                                                               |

|                                   | Low level   | V <sub>CLKL</sub>   | 1 110                               | indudate the pin o riight and low lovely that all oscilloscope.                                                                           |

| 21H output                        | High level  | V <sub>21HH</sub>   | Pin 1*1                             |                                                                                                                                           |

|                                   | Low level   | V <sub>21HL</sub>   |                                     | Measure the pin 1 high and low levels and the length of the high level period with an oscilloscope.                                       |

|                                   | Pulse width | V <sub>21HW</sub>   |                                     | Tover period Harris arr oscilloscope.                                                                                                     |

| O/E output                        | High level  | VOEH                | Pin 6*1                             |                                                                                                                                           |

|                                   | Low level   | V <sub>OEL</sub>    |                                     | Measure the pin 6 high and low levels and the length of the high level period with an oscilloscope.                                       |

|                                   | Pulse width | V <sub>OEW</sub>    |                                     | lover period with all escilloscope.                                                                                                       |

| Horizontal pulse output           | High leve!  | V <sub>HEH</sub>    | Pin 10*1                            |                                                                                                                                           |

|                                   | Low level   | V <sub>HSL</sub>    |                                     | Measure the pin 10 high and low levels and the length of the high level period with an oscilloscope.                                      |

|                                   | Pulse width | V <sub>HSW</sub>    |                                     | 10701 portou Will all oscilloscope.                                                                                                       |

| Vertical pulse output             | High level  | V <sub>RSTH</sub>   | Pin 9*1                             |                                                                                                                                           |

|                                   | Low level   | V <sub>RSTL</sub>   |                                     | Measure the pin 9 high and low levels and the length of the high level period with an oscilloscope.                                       |

|                                   | Pulse width | V <sub>RSTW</sub>   |                                     | Total pariod Will all additionable.                                                                                                       |

| Input signal level                |             | VIN                 | Each of pins 1,<br>3, 5, and 6*2    | Vary the signal level input to pin 17, and confirm that the pin 1, 3, 5, and 6 outputs are operating correctly.                           |

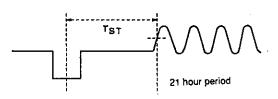

| CLK-RUN-IN start time             |             | тѕт                 | Each of pins 1,<br>3, 5, and 6*2, 3 | Vary the time between SYNC and CLK-RUN-IN, and confirm that the pin 1, 3, 5, and 6 outputs are operating correctly.                       |

| Current dissipation               |             | ICC                 | Pin 16*2                            | Connect a current meter to pin 16, and measure the current during decoding.                                                               |

Notes: 1. Connect a 20 kΩ resistor between the pin being measured and V<sub>CC</sub>, and also connect a 20 kΩ from that measurement pin to GND.

2. During measurement, this pin carries the closed caption encoded signal.

3. Time TST is shown in the figure below.

A01660

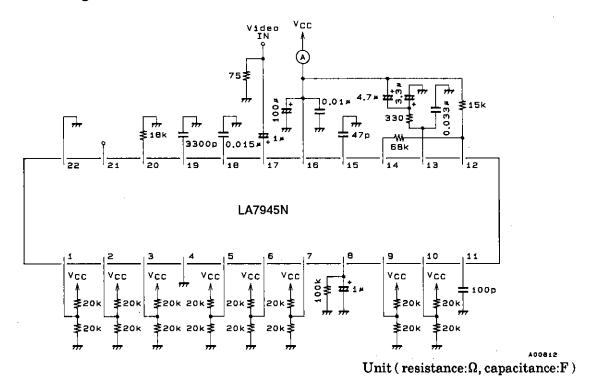

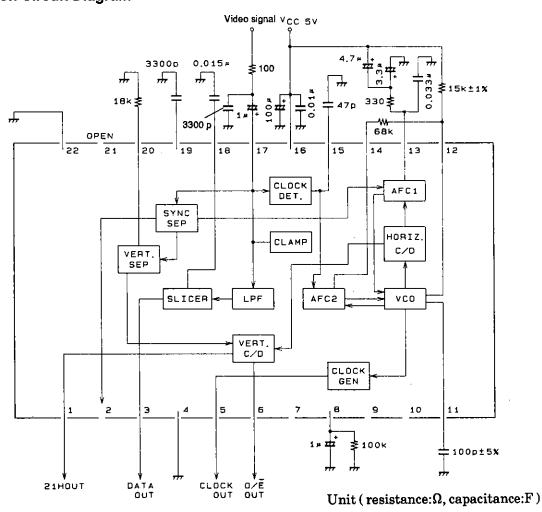

### **Test Circuit Diagram**

### **Application Circuit Diagram**

A0081

### **Pin Descriptions**

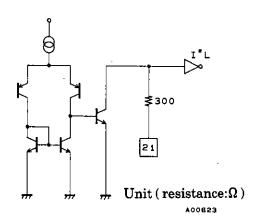

Figure 1

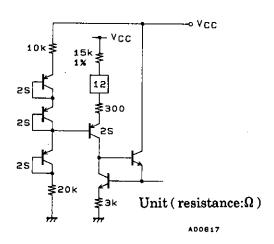

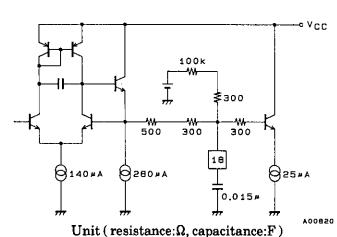

- The peripheral circuit for the pins described below is shown in figure 1. Either a resistor or a fixed current supply is connected to the lower side (the side away from the pin) of the differential amplifier.

- (21H OUT):  $R = 18 \text{ k}\Omega$ . This signal goes high during the 21H and 284H periods. The fall of this signal is taken as the completion of data transfer.

- Pin 2 (sync SEP):  $R = 9 k\Omega$ . Synchronization separation output, see pin 19.

- Pin 3 (DATA OUT):  $I = 280 \mu A$ . Outputs the data overlapped with the vertical retrace period.

- (CLOCK OUT):  $R = 9 \text{ k}\Omega$ . A clock output whose phase matches Pin 5 that of DATA OUT.

- Pin 6 (O/E OUT):  $R = 18 \text{ k}\Omega$ . Field discrimination signal. High on odd fields.

- Pin 7 (H LOCK OUT):  $I \approx 50 \mu A$ . A resistor and capacitor are connected to pin 8, and this pin goes high when the internal VCO and the input signal are synchronized.

- (V PULSE OUT):  $R = 18 \text{ k}\Omega$ . Set low during the 0.5H period synchronized with the vertical synchronization signal.

- Pin 10 (H PULSE OUT):  $R = 18 \text{ k}\Omega$ . Outputs a low signal synchronized with the horizontal synchronization signal.

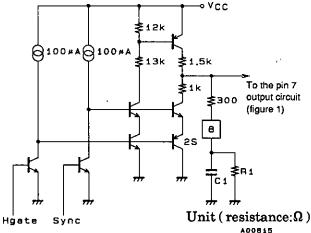

Pin 8 is charged when the H gate and Sync phases match, and this voltage is compared and output to pin 7. The resistor R1 is used for discharge. The time from internal VCO locking until pin 7 goes high, and the time from lock release to the pin going low can be adjusted by changing the values of C1 and R1. If the pin 7 H LOCK OUT output is not used, C1 and R1 will

• Pin 8 (H LOCK FILTER): The H LOCK detection filter is connected to this pin.

be unnecessary.

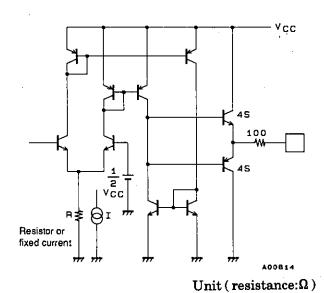

Figure 2: Pin 8 (H LOCK FILTER) Peripheral Circuit

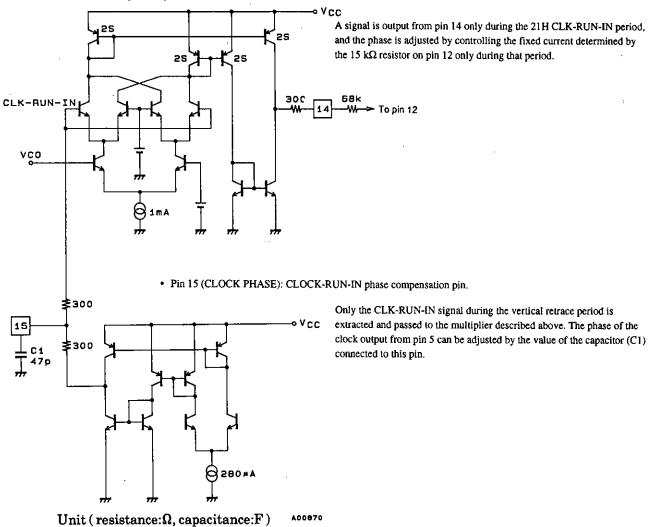

• Pin 11 (VCO C): The capacitor for the 32f<sub>H</sub> VCO is connected to this pin. (Error: 5%)

The LA7945N generates the 32fH oscillation not by using a ceramic resonator, but by charging this capacitor with the fixed current defined by the resistance connected at pin 12. The horizontal pulses and the clock output from pin 5 are generated using this oscillator as a reference.

Unit (resistance:  $\Omega$ , capacitance: F)

Figure 3: Pin 11 (VCO C) Peripheral Circuit

• Pin 12 (VCO R): The resistor for the  $32f_{\rm H}$  VCO is connected to this pin. (Error: 1%)

This resistor defines the current that charges the pin 11 capacitor. A DC voltage of 2/3 that of  $V_{CC}$  is output from pin 12.

Figure 4: Pin 12 (VCO R) Peripheral Circuit

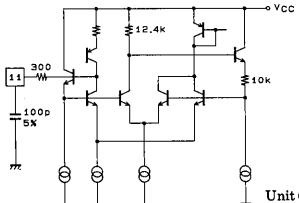

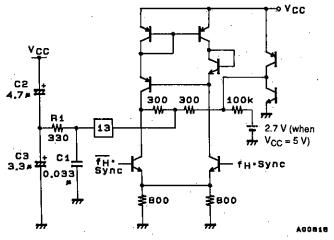

• Pin 13 (AFC1): The horizontal AFC filter is connected to this pin.

Unit (resistance:  $\Omega$ , capacitance: F)

Figure 5: Pin 13 (AFC1) Peripheral Circuit

Although the ability to follow horizontal fluctuations improves as R1 increases, the holding power is reduced. Select this value according to the application circuit. Since the closed caption signal is overlapped with 21 H, the VCO in this IC is influenced by signals such as the vertical synchronization signal and the copy guard signal. The values of C2 and C3 should be determined so that the VCO is stable with respect to these signals. To stabilize pin 13 at a voltage of about 2.7 V (when  $V_{CC} = 5$  V) with no input, the ratio of C2 and C3 should be set so that this voltage takes on a value close to that of pin 13 when power is first applied.

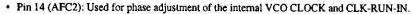

### Figure 6: Pin 14 (AFC2) and Pin 15 (CLOCK PHASE) Peripheral Circuits

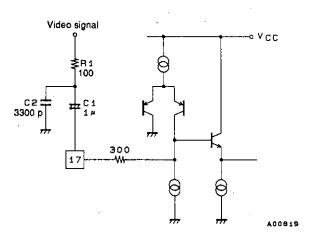

• Pin 17 (VIDEO IN): The video input pin. (sync-white 1 Vp-p)

Unit (resistance:  $\Omega$ , capacitance: F)

Figure 7: Pin 17 (VIDEO IN) Peripheral Circuit

Pin 17 is designed to clamp the pedestal level at  $1/2\ V_{CC}$ . Since C1 also functions as the clamping capacitor, it should be driven with a low impedance (less than 500  $\Omega$ ). The low field performance can be improved by adding an LPF such as R1 and C2. If this LPF is used, R1 must be a low resistance that can meet the conditions described above.

• Pin 18 (DATA LPF): The data slice LPF is connected to this pin.

A signal is output from pin 18 during the vertical retrace period CLK-RUN-IN period, and an LPF, which is used to detect the average value of CLK-RUN-IN (to be used as the slice level), is connected to this pin.

Figure 8: Pin 18 (DATA LPF) Peripheral Circuit

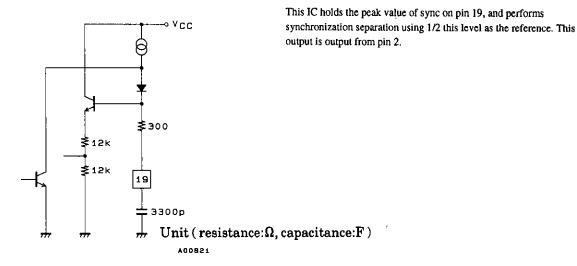

• Pin 19 (PEAK HOLD): The synchronization separator peak hold capacitor is connected to this pin.

Figure 9: Pln 19 (PEAK HOLD) Peripheral Circuit

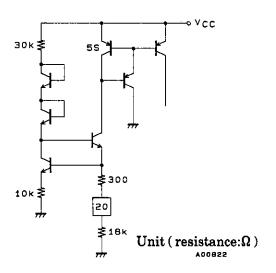

• Pin 20 (V SEP R): The resistor that determines the vertical synchronization separation is connected to this pin.

an internal capacitor using the fixed current determined by the resistor connected to this pin as the reference. The pin 20 DC voltage is 1/4  $V_{CC}$ .

The LA7945N performs vertical synchronization separation by charging

Figure 10: Pin 20 (V SEP R) Peripheral Circuit

• Pin 21: The vertical synchronization separation output pin.

The signal passed to the vertical C/D from vertical synchronization separation is output from pin 21. Since vertical C/D is  $I^2L$ , a signal of between 0 and 0.7 V is output. This pin is normally left open. The vertical C/D start position can be changed by an external override input.

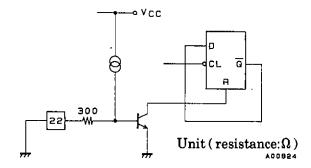

Figure 11: Pin 21 Peripheral Circuit

• Pin 22: This pin determines whether or not the horizontal count for vertical C/D is changed every frame when the start bit is not detected.

When this pin is grounded, 21H is fixed, and it functions when open. Ground this pin when captions are used.

Figure 12: Pin 22 Peripheral Circuit

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.