查询LB11827供应商

## Ordering number : ENN7110

# **Three-Phase Brushless Motor Driver for OA Products**

# **Overview**

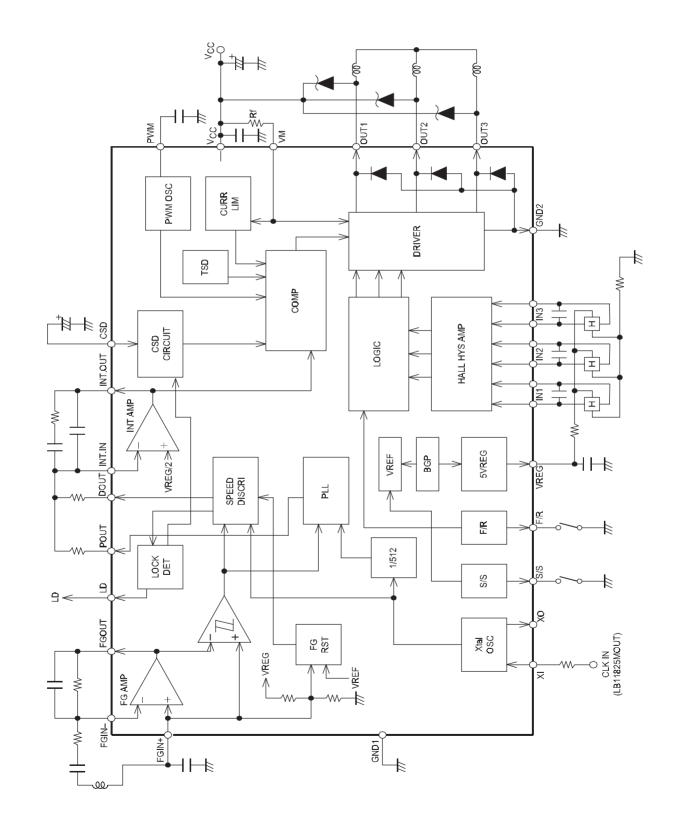

The LB11827 is a three-phase brushless motor driver that is optimal for driving drum and paper feed motors in laser printers and plain paper copiers. This IC adopts a direct PWM drive technique for minimal power loss. Flexible control of motor speed in response to an externally provided clock frequency (corresponding to the FG frequency) can be implemented by using the LB11827 in conjunction with the Sanyo LB11825M.

# **Functions and Features**

- Three-phase bipolar drive (30 V, 3.5 A)

- Direct PWM drive

- Built-in low side inductive kickback absorbing diode C.COM

- Speed discriminator + P<sub>LL</sub> speed control

- Speed locked state detection output

- Built-in forward/reverse switching circuit

- Full complement of built-in protection circuits, including current limiter circuit, thermal protection circuit, and motor constraint protection circuit.

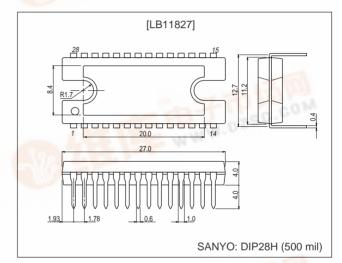

# Package Dimensions

unit: mm

## 3147B-DIP28H

# **Specifications**

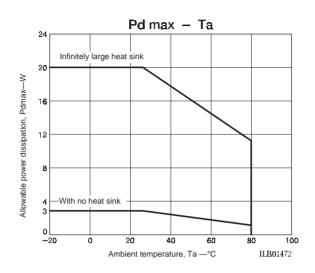

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                     | Symbol              | Conditions                      | Ratings     | Unit |

|-------------------------------|---------------------|---------------------------------|-------------|------|

| Supply voltage                | V <sub>CC</sub> max |                                 | 30          | V    |

| Output current                | I <sub>O</sub> m ax | T ≤ 500 ms                      | 3.5         | А    |

| Allowable power dissipation 1 | Pd max1             | Independent IC                  | 3           | W    |

| Allowable power dissipation 2 | Pd max2             | When infinitely large heat sink | 20          | W    |

| Operating temperature         | Topr                |                                 | -20 to +80  | °C   |

| Storage temperature           | Tstg                |                                 | -55 to +150 | °C   |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## LB11827

# Absolute Maximum Ratings at $Ta=25^{\circ}C$

| Parameter                        | Symbol           | Conditions | Ratings   | Unit |

|----------------------------------|------------------|------------|-----------|------|

| Supply voltage range 1           | V <sub>CC</sub>  |            | 9.5 to 28 | V    |

| Regulator voltage output current | I <sub>REG</sub> |            | 0 to - 30 | mA   |

| LD output current                | ILD              |            | 0 to 15   | mA   |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = VM = 24 V

| Parameter                              | Symbol                | Conditions                                                             |          | Ratings  |          | Unit              |  |

|----------------------------------------|-----------------------|------------------------------------------------------------------------|----------|----------|----------|-------------------|--|

|                                        |                       |                                                                        | min      | typ      | max      |                   |  |

| Supply current 1                       | I <sub>CC</sub> 1     |                                                                        |          | 23       | 30       | mA                |  |

| Supply current 2                       | I <sub>CC</sub> 2     | When stopped                                                           |          | 3.5      | 5        | mA                |  |

| [Output Block]                         |                       |                                                                        |          |          |          |                   |  |

| Output saturation voltage 1            | V <sub>O</sub> sat1   | $I_{O} = 1.0 \text{ A}, V_{O} \text{ (SINK)} + V_{O} \text{ (SOURCE)}$ |          | 2.0      | 2.5      | V                 |  |

| Output saturation voltage 2            | V <sub>O</sub> sat2   | $I_{O}$ = 2.0 A, $V_{O}$ (SINK)+ $V_{O}$ (SOURCE)                      |          | 2.6      | 3.2      | V                 |  |

| Output leakage current                 | V <sub>O</sub> leak   |                                                                        |          |          | 100      | μA                |  |

| Lower side diode forward voltage 1     | VD1                   | ID = -1.0 A                                                            |          | 1.2      | 1.5      | V                 |  |

| Lower side diode forward voltage 2     | VD2                   | ID = -2.0 A                                                            |          | 1.5      | 2.0      | V                 |  |

| [5 V Regulator Voltage Output]         |                       |                                                                        |          |          |          |                   |  |

| Output voltage                         | VREG                  | $I_{O} = -5 \text{ mA}$                                                | 4.65     | 5.00     | 5.35     | V                 |  |

| Voltage regulation                     | ∆VREG1                | V <sub>CC</sub> = 9.5 to 28 V                                          |          | 30       | 100      | mV                |  |

| Load regulation                        | ∆VREG2                | I <sub>O</sub> = -5 to -20 mA                                          |          | 20       | 100      | mV                |  |

| [Hall Amplifier]                       |                       |                                                                        |          |          |          |                   |  |

| Input bias current                     | IHB                   |                                                                        | -2       | -0.5     |          | μA                |  |

| Common-mode input voltage range        | VICM                  |                                                                        | 1.5      |          | VREG-1.5 | V                 |  |

| Hall input sensitivity                 |                       |                                                                        | 80       |          |          | mV <sub>P-P</sub> |  |

| Hysteresis                             | ΔV <sub>IN</sub>      |                                                                        | 15       | 24       | 42       | mV                |  |

| Input voltage low $\rightarrow$ high   | VSLH                  |                                                                        |          | 12       |          | mV                |  |

| Input voltage high $\rightarrow$ low   | VSHL                  |                                                                        |          | -12      |          | mV                |  |

| [PWM Oscillator Circuit]               |                       |                                                                        |          |          |          |                   |  |

| Output H level voltage                 | V <sub>OH</sub> (PWM) |                                                                        | 2.5      | 2.8      | 3.1      | V                 |  |

| Output L level voltage                 | V <sub>OL</sub> (PWM) |                                                                        | 1.2      | 1.5      | 1.8      | V                 |  |

| Oscillator frequency                   | f(PWM)                | C = 3900 pF                                                            |          | 18       |          | kHz               |  |

| Amplitude                              | V(PWM)                |                                                                        | 1.05     | 1.30     | 1.55     | V <sub>P-P</sub>  |  |

| [CSD Circuit]                          | . ,                   |                                                                        | -        |          |          |                   |  |

| Operating voltage                      | V <sub>OH</sub> (CSD) |                                                                        | 3.6      | 3.9      | 4.2      | V                 |  |

| External C charging current            | ICHG                  |                                                                        | -17      | -12      | -9       | μA                |  |

| Operating time                         | T(CSD)                | C = 10 µF Design target value*                                         |          | 3.3      |          | s                 |  |

| [Current Limiter Operation]            |                       |                                                                        |          | 1        |          |                   |  |

| Limiter                                | VRF                   | V <sub>CC</sub> –VM                                                    | 0.45     | 0.5      | 0.55     | V                 |  |

| [Thermal Shutdown Operation]           |                       |                                                                        |          |          |          |                   |  |

| Thermal shutdown operating temperature | TSD                   | Design target value* (junction temperature)                            | 150      | 180      |          | °C                |  |

| Hysteresis                             | ΔTSD                  | Design target value* (junction temperature)                            |          | 50       |          | °C                |  |

| [FG Amplifier]                         |                       |                                                                        |          |          |          |                   |  |

| Input offset voltage                   | VIO(FG)               |                                                                        | -10      |          | 10       | mV                |  |

| Input bias current                     | IB(FG)                |                                                                        | -1       |          | 1        | μA                |  |

| Output H level voltage                 | V <sub>OH</sub> (FG)  | IFGO = -0.2 mA                                                         | VREG-1.2 | VREG-0.8 |          | V                 |  |

| Output L level voltage                 | V <sub>OH</sub> (FG)  | IFGO = 0.2 mA                                                          |          | 0.8      | 1.2      | V                 |  |

| FG input sensitivity                   | .01(10)               | Gain: 100                                                              | 3        | 0.0      |          | mV                |  |

| Schmitt amplitude for the next stage   |                       | Design target value*                                                   | 100      | 180      | 250      | mV                |  |

| Operating frequency range              |                       |                                                                        |          | 100      | 200      | kHz               |  |

| Open-loop gain                         |                       | f(FG) = 2 kHz                                                          | 45       | 51       | <b>2</b> | dB                |  |

|                                        |                       |                                                                        | 45       |          |          |                   |  |

Note: \* These are design target values and are not tested.

## LB11827

## Continued from preceding page.

| Parameter                   | Symbol Conditions     |                                             | Ratings  |          |          | Unit |

|-----------------------------|-----------------------|---------------------------------------------|----------|----------|----------|------|

| i alametei                  | Gymbol                | Conditions                                  | min      | typ      | max      | Onit |

| [Speed Discriminator]       |                       |                                             |          |          |          |      |

| Output H level voltage      | V <sub>OH</sub> (D)   | IDO = -0.1 mA                               | VREG-1.0 | VREG-0.7 |          | V    |

| Output L level voltage      | V <sub>OL</sub> (D)   | IDO = 0.1 mA                                |          | 0.8      | 1.1      | V    |

| Number of counts            |                       |                                             |          | 512      |          |      |

| [PLL Output]                |                       |                                             |          |          |          |      |

| Output H level voltage      | V <sub>OH</sub> (P)   | IPO = -0.1 mA                               | VREG-1.8 | VREG-1.5 | VREG-1.2 | V    |

| Output L level voltage      | V <sub>OL</sub> (P)   | IPO = 0.1 mA                                | 1.2      | 1.5      | 1.8      | V    |

| [Lock Detection]            |                       |                                             | ·        |          |          |      |

| Output L level voltage      | V <sub>OL</sub> (LD)  | ILD = 10 mA                                 |          | 0.15     | 0.5      | V    |

| Lock range                  |                       |                                             |          | 6.25     |          | %    |

| [Integrator]                | ·                     | •                                           | ·        |          | ·1       |      |

| Input bias current          | IB(INT)               |                                             | -0.4     |          | 0.4      | μA   |

| Output H level voltage      | V <sub>OH</sub> (INT) | IINTO = -0.2 mA                             | VREG-1.2 | VREG-0.8 |          | V    |

| Output L level voltage      | V <sub>OL</sub> (INT) | IINTO = 0.2 mA                              |          | 0.8      | 1.2      | V    |

| Open-loop gain              |                       | f(INT) = 1 kHz                              | 45       | 51       |          | dB   |

| Gain width product          |                       | Design target value*                        |          | 450      |          | kHz  |

| Reference voltage           |                       | Design target value*                        | -5%      | VREG/2   | 5%       | V    |

| [Clock Input Pin]           |                       |                                             |          |          | ·        |      |

| Operating frequency range   | fosc                  |                                             |          |          | 1        | MHz  |

| L level pin voltage         | V <sub>OSCL</sub>     | I <sub>OSC</sub> = -0.5 mA                  |          | 1.55     |          | V    |

| H level pin current         | IOSCH                 | V <sub>OSC</sub> = V <sub>OSCL</sub> +0.5 V |          | 0.4      |          | mA   |

| [Start/Stop Pin]            |                       |                                             |          |          |          |      |

| H level input voltage range | V <sub>IH</sub> (S/S) |                                             | 3.5      |          | VREG     | V    |

| L level input voltage range | V <sub>IL</sub> (S/S) |                                             | 0        |          | 1.5      | V    |

| Input open voltage          | V <sub>IO</sub> (S/S) |                                             | VREG-0.5 |          | VREG     | V    |

| Hysteresis                  | ΔV <sub>IN</sub>      |                                             | 0.35     | 0.50     | 0.65     | V    |

| H level input current       | I <sub>IH</sub> (S/S) | V(S/S) = VREG                               | -10      | 0        | 10       | μA   |

| L level input current       | I <sub>IL</sub> (S/S) | V(S/S) = 0 V                                | -280     | -210     |          | μA   |

| [Forward/Reverse Pin]       |                       |                                             | 1        | 1        | ı        |      |

| H level input voltage range | V <sub>IH</sub> (F/R) |                                             | 3.5      |          | VREG     | V    |

| L level input voltage range | V <sub>IL</sub> (F/R) |                                             | 0        |          | 1.5      | V    |

| Input open voltage          | V <sub>IO</sub> (F/R) |                                             | VREG-0.5 |          | VREG     | V    |

| Hysteresis                  | ΔV <sub>IN</sub>      |                                             | 0.35     | 0.50     | 0.65     | V    |

| H level input current       | I <sub>IH</sub> (F/R) | V(F/R) = VREG                               | -10      | 0        | 10       | μA   |

| L level input current       | I <sub>IL</sub> (F/R) | V(F/R) = 0 V                                | -280     | -210     |          | μΑ   |

Note: \* These are design target values and are not tested.

#### **Truth Table**

|   | Source                  | F/R = "L" |     |     |     | F/R = "H" |     |

|---|-------------------------|-----------|-----|-----|-----|-----------|-----|

|   | Sink                    | IN1       | IN2 | IN3 | IN1 | IN2       | IN3 |

| 1 | $OUT2 \rightarrow OUT1$ | Н         | L   | Н   | L   | н         | L   |

| 2 | $OUT3 \rightarrow OUT1$ | Н         | L   | L   | L   | Н         | Н   |

| 3 | $OUT3 \rightarrow OUT2$ | н         | н   | L   | L   | L         | Н   |

| 4 | $OUT1 \rightarrow OUT2$ | L         | н   | L   | н   | L         | Н   |

| 5 | $OUT1 \rightarrow OUT3$ | L         | н   | н   | н   | L         | L   |

| 6 | $OUT2 \rightarrow OUT3$ | L         | L   | н   | н   | н         | L   |

The relation between the clock frequency, fCLK, and the FG frequency, fFG, is given by the following equation.

fFG(servo) = fCLK/<number of counts> = fCLK/512

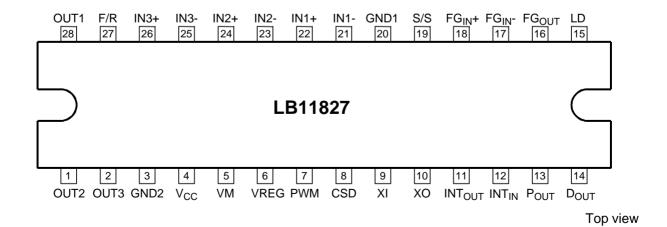

## **Pin Assignment**

LB11827

# **Pin Description**

| Pin No.      | Pin                  | Function                                                                                                                                                                                                 | Equivalent circuit     |

|--------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 28<br>1<br>2 | OUT1<br>OUT2<br>OUT3 | Motor drive output pin $\label{eq:connect} Connect the Schottky diode between the output - V_{CC}.$                                                                                                      | Vcc<br>300 Ω<br>W<br>5 |

| 3            | GND2                 | Output GND pin                                                                                                                                                                                           |                        |

| 5            | VM                   | Power and output current detection pins of the output. Connect a low resistance (Rf) between this pin and $V_{CC}$ .<br>The output current is limited to the current value set with $I_{OUT} = VRF/Rf$ . |                        |

| 4            | V <sub>CC</sub>      | Power pin (Other than the output)                                                                                                                                                                        |                        |

| 6            | VREG                 | Stabilized power supply output pin (5 V output)<br>Connect a capacitor (about 0.1 µF) between this pin and GND for<br>stabilization                                                                      |                        |

| 7            | PWM                  | Pin to set the PWM oscillation frequency.<br>Connect a capacitor between this pin and GND.<br>This can be set to about 18 kHz with C =3900 pF.                                                           |                        |

| 8            | CSD                  | Pin to set the operation time of motor lock protection circuit.<br>Connection of a capacitor (about 10 $\mu$ F) between CSD and GND can set the protection operation time of about 3.3seconds.           |                        |

Continued on next page.

LB11827

## Continued from preceding page.

| Pin No. | Pin        | Function                                                                                                                                    | Equivalent circuit                |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 9<br>10 | XI<br>XO   | Clock input pin, which enters the clock signal (1 MHz or less) to the XI pin via resistor (about 5.1 k $\Omega$ ).<br>Keep the XO pin open. | VREG                              |

| 11      | INT<br>OUT | Integrating amplifier output (speed control pin).                                                                                           | VREG                              |

| 12      | INT<br>IN  | Integrating amplifier input pin                                                                                                             |                                   |

| 13      | Роит       | PLL output pin                                                                                                                              | VREG<br>300 Ω<br>13<br>777<br>777 |

Continued on next page.

## Continued from preceding page.

| Pin No. | Pin                | Function                                                                                                                               | Equivalent circuit                                                                                          |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 14      | DOUT               | Speed discriminator output.<br>Accelerate: high, decelerate: low                                                                       | VREG<br>300 Ω<br>14<br><i>m</i>                                                                             |

| 15      | LD                 | Speed lock detection output.<br>L when the motor speed is within the speed lock range (±6.25%).<br>Voltage resistance 30 Vmax          | VREG<br>(15)<br>(15)<br>(15)<br>(15)<br>(15)<br>(15)                                                        |

| 16      | FG<br>OUT          | FG amplifier output pin                                                                                                                | VREG<br>VREG<br>G<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C |

| 17      | FG <sub>IN</sub>   | FG amplifier input pin.<br>Connection of a capacitor (about 0.1 μF) between FGIN and<br>GND causes initial reset to the logic circuit. |                                                                                                             |

| 18      | FG <sub>IN</sub> + |                                                                                                                                        |                                                                                                             |

| 19      | S/S                | Start/stop control pin.<br>Low: 0 V to 1.5 V<br>High: 3.5 V to VREG<br>H level when open.<br>Hysteresis width about 0.5 V              | VREG                                                                                                        |

#### Continued from preceding page.

| Pin No.                          | Pin                                          | Function                                                                                                                                                                                                                                                                                                         | Equivalent circuit |

|----------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 20                               | GND1                                         | GND pin (Other than the output)                                                                                                                                                                                                                                                                                  |                    |

| 22<br>21<br>24<br>23<br>26<br>25 | IN1+<br>IN1-<br>IN2+<br>IN2-<br>IN3+<br>IN3- | Hall amplifier input.<br>IN+ > IN- is the input high state, and the reverse is the input low<br>state.<br>It is recommended that the Hall signal has an amplitude of 100m<br>Vp-p (differential) or more.<br>Connect a capacitor between the IN+ and IN- inputs if there is<br>noise in the Hall sensor signals. | 21 23 25           |

| 27                               | F/R                                          | Forward/reverse control pin<br>Low: 0 V to 1.5 V<br>High: 3.5 V to VREG<br>H level when open<br>Hysteresis width about 0.5 V                                                                                                                                                                                     | VREG               |

#### **Function Description**

1. Speed control circuit

This IC performs speed control by using both the speed discriminator circuit and PLL circuit. The speed control circuit outputs the error signal once for every two cycles of FG (one FG cycle counted). The PLL circuit outputs the phase error signal once for each cycle of FG.

As the FG servo frequency is calculated as follows, the motor speed is set with the number of FG pulses and clock frequency.

$f_{FG}(servo) = f_{CLK}/512$

f<sub>CLK</sub>: Clock frequency

This IC achieves variable speed control with ease when combined with LB11825M.

#### 2. Output drive circuit

This IC employs a direct PWM drive method to minimize the power loss at output. The output Tr is always saturated at ON, and the motor drive force is adjusted through change of the duty at which the output is turned ON. Since the output PWM switching is made with the lower-side output Tr, it is necessary to connect the schottky diode between OUT and  $V_{CC}$  (because the through current flows at an instant when the lower-side Tr is turned ON if the diode with a short reverse recovery time is not used). The diode between OUT and GND is incorporated. When the large output current presents problem (waveform disturbance at kickback on the lower side), connect a commutating diode or schottky diode externally.

#### 3. Current limiting circuit

The current limiting circuit performs limiting with the current determined from  $I = V_{RF}/Rf$  ( $V_{RF} = 0.5$  Vtyp, Rf: current detector resistance) (that is, this circuit limits the peak current).

Limiting operation includes decrease in the output on-duty to suppress the current.

4. Power save circuit

This IC enters the power save condition to decrease the current dissipation in the stop mode. In this condition, the bias current of most of circuits is cut off. Even in the power save condition, the 5 V regulator output is given.

#### 5. Reference clock

This is entered from the external signal source (1 MHz max) via a resistor (reference: about 5.1 k $\Omega$ ) in series with the XI pin. The XO pin is left open.

Input signal source levels: Low-level voltage: 0 to 0.8 V High-level voltage: 2.5 to 5.0 V

#### 6. Speed lock range

The speed lock range is  $\pm 6.25\%$  of the constant speed. If the motor speed falls inside the lock range, the LD pin goes to "L" (open collector output). When the motor speed falls outside the lock range, the on-duty ratio of motor drive output changes according to the speed error, causing control to keep the motor speed within the lock range.

#### 7. PWM frequency

PWM frequency is determined from the capacity C (F) of capacitor connected to the PWM pin.

$f_{PWM} \approx 1/(14,400 \times C)$

It is recommended to keep the PWM frequency at 15 - 25 kHz. GND of a capacitor to be connected must be connected to the GND1 pin with the shortest possible wiring.

#### 8. Hall input signal

The Hall input requires the signal input with an amplitude exceeding the hysteresis width (42 mV max). Considering the effect of noise, the input with the amplitude of 100 mV or more is recommended.

When the output waveform is disturbed due to noise effects at a time of changeover of the output phase, connect a capacitor between Hall input pins (+ and -) at a point as near as possible to the pin.

#### 9. F/R changeover

Motor rotation direction can be changed over with the F/R pin. When changing F/R while the motor is running, pay attention to following points.

- For the through current at a time of changeover, the countermeasure is taken using a circuit. However, it is necessary to prevent exceeding of the rated voltage (30 V) due to rise of V<sub>CC</sub> voltage at a time of changeover (because the motor current returns instantaneously to the power supply). When this problem exists, increase the capacity of a capacitor between V<sub>CC</sub> and GND.

- When the motor current exceeds the current limit value after changeover, the lower-side Tr is turned OFF. But, the upper-side Tr enters the short-brake condition and the current determined from the motor counter electromotive voltage and coil resistance flows. It is necessary to prevent this current from exceeding the rated current (3.5 A). (F/R changeover speed is dangerous.)

#### 10. Motor lock protection circuit

A motor lock protection circuit is incorporated for protection of IC and motor when the motor is locked.

When the LD output is "H" (unlocked) for a certain period in the start condition, the lower-side Tr is turned OFF. This time is set with the capacity of the capacitor connected to the CSD pin. The time can be set to about 3.3 seconds with the capacity of 10  $\mu$ F (variance about ±30%).

Set time (s)  $\approx 0.33 \times C (\mu F)$

When the capacitor used has a leak current, due consideration is necessary because it may cause error in the set time, etc.

Cancelling requires either the stop condition or re-application of power supply (in the stop condition). When the lock protection circuit is not to be used, connect the CSD pin to GND.

When the stop period during which lock protection is to be cancelled is short, the charge of capacitor cannot be discharged completely and the lock protection activation time at restart becomes shorter than the set value. It is

necessary to provide the stop time with an allowance while referring to the following equation. (The same applies to restart in the motor start transient condition.)

Stop time (ms)  $\geq 15 \times C \ (\mu F)$

#### 11. Power supply stabilization

This IC has a large output current and is driven by switching, resulting in ready oscillation of the power line. It is therefore necessary to connect a capacitor with a sufficient capacity (several ten  $\mu$ F or more) between the VCC pin and GND for stabilization. GND of a capacitor to be connected must be connected to the GND2 pin (GND of the power block) at a point as near as possible to the pin. If a capacitor (electrolytic) cannot be provided near the pin because of existence of a heat sink, etc., provide a ceramic capacitor of about 0.1  $\mu$ F near the pin.

When a diode is inserted in the power line to prevent breakdown due to reverse connection of power supply, the power line is particularly readily oscillated. The larger capacity need be selected.

#### 12. VREG stabilization

The  $V_{REG}$  pin (5 V regulator output) that is a power supply for control circuit must be provided with a stabilizing capacitor (about 0.1  $\mu$ F). GND of a capacitor to be connected must be connected to the GND1 pin with the shortest possible wiring.

#### 13. Constant of integrating amplifier parts

Arrange the integrating amplifier external parts as near as possible to IC to protect them from noise effects. Arrange them by keeping the largest possible distance from the motor.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 2003. Specifications and information herein are subject to change without notice.