Ordering number : EN4264A

Monolithic Digital IC

# Power Brushless Motor Driver for OA Equipment

# Overview

The LB1824 produces the direct PWM drive output appropriate for the brushless motors used in office data processing (OA) equipment, and integrates on a single chip the speed control circuits, FG amplifier, and other circuits required to form the drive circuit.

NWW.DZSC.CO

#### **Features**

- Breakdown voltage: 30 V, output current: 2.5 A

- Direct PWM drive output

- · Crystal oscillator circuit

- Speed discriminator plus PLL speed control system

- Forward/reverse switching circuit

- Start/stop switching circuit

- Current control circuit

- Overheating protection circuit

- Built-in FG amplifier

- Lock detection output

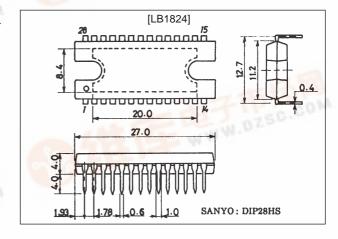

# **Package Dimensions**

unit: mm

# 3147A-DIP28HS

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                        | Ratings     | Unit |

|-----------------------------|---------------------|-----------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max | S (5)//6                          | 30          | V    |

| Maximum supply voltage      | V <sub>M</sub> max  |                                   | 30          | V    |

| Output current              | I <sub>O</sub> max  | T ≤ 100 ms                        | 2.5         | A    |

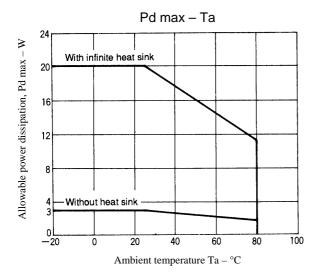

| Allowable power dissipation | Pd max1             | The IC independently              | 3           | W    |

| Allowable power dissipation | Pd max2             | With an arbitrary large heat sink | 20          | W    |

| Operating temperature       | Topr                |                                   | -20 to +80  | °C   |

| Storage temperature         | Tstg                |                                   | -55 to +150 | °C   |

# Allowable Operating Ranges at Ta = 25°C

| Parameter                          | Symbol           | Conditions | Ratings   | Unit |

|------------------------------------|------------------|------------|-----------|------|

| Supply voltage range               | V <sub>CC</sub>  | igo V A -  | 9.5 to 28 | V    |

| Supply voltage range               | V <sub>M</sub>   |            | 9 to 28   | V    |

| FG Schmitt output, applied voltage | V <sub>FGS</sub> |            | 0 to 8    | V    |

|                                    | I <sub>01</sub>  | 7 V output | 0 to -20  | mA   |

| Fixed voltage output current       | I <sub>O2</sub>  | 5 V output | 0 to -20  | mA   |

|                                    | I <sub>O3</sub>  | 4 V output | 0 to −15  | mA   |

| FG Schmitt output, output current  | I <sub>FGS</sub> |            | 0 to 5    | mA   |

| Lock detection output current      | I <sub>LD</sub>  |            | 0 to 20   | mA   |

# LB1824

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{CC}$ = $V_{M}$ = 24 V

| Parameter                  |                                        | Symbol                          | Conditions                              |      | Ratings           |      | 1154    |

|----------------------------|----------------------------------------|---------------------------------|-----------------------------------------|------|-------------------|------|---------|

|                            | Parameter                              | Symbol                          | Conditions                              | min  | typ               | max  | Unit    |

| Current drain              |                                        | I <sub>CC1</sub>                |                                         |      | 34                | 50   | mA      |

| Current drain              |                                        | I <sub>CC2</sub>                | When stopped                            |      | 8                 | 11   | mA      |

| Output saturation voltage  |                                        | V <sub>Osat1</sub>              | I <sub>O</sub> = 1A                     |      | 2.0               | 3.0  | V       |

| Output Saturation voitage  |                                        | V <sub>Osat2</sub>              | I <sub>O</sub> = 2A                     |      | 2.7               | 4.2  | V       |

| Output leakage current     |                                        | I <sub>Oleak</sub>              |                                         |      |                   | 100  | μA      |

|                            | Output voltage                         | V <sub>H</sub>                  | I <sub>O</sub> = -10 mA                 | 6.65 | 7.0               | 7.35 | V       |

| 7 V fixed voltage output   | Voltage variation                      | $\Delta V_{H1}$                 | V <sub>CC</sub> = 9.5 to 28 V           |      | 50                | 200  | mV      |

|                            | Load variation                         | ΔV <sub>H2</sub>                | $I_{O} = -5 \text{ to } -20 \text{ mA}$ |      | 40                | 200  | mV      |

|                            | Output voltage                         | V <sub>X</sub>                  | I <sub>O</sub> = -5 mA                  | 4.45 | 4.80              | 5.15 | V       |

| 5 V fixed voltage output   | Voltage variation                      | $\Delta V_{X1}$                 | V <sub>CC</sub> = 9.5 to 28 V           |      | 50                | 200  | mV      |

|                            | Load variation                         | $\Delta V_{X2}$                 | $I_{O} = -5 \text{ to } -20 \text{ mA}$ |      | 5                 | 200  | mV      |

|                            | Output voltage                         | V <sub>FG</sub>                 | I <sub>O</sub> = -5 mA                  | 3.65 | 4.0               | 4.35 | V       |

| 4 V fixed voltage output   | Voltage variation                      | $\Delta V_{FG1}$                | V <sub>CC</sub> = 9.5 to 28 V           |      | 40                | 200  | mV      |

| 0 1                        | Load variation                         | $\Delta V_{FG2}$                | $I_{O} = -5 \text{ to } -15 \text{ mA}$ |      | 110               | 200  | mV      |

|                            | Input bias current                     | I <sub>HB</sub>                 | 0 111                                   | -4   | -1                |      | μA      |

|                            | Common mode input voltage range        | V <sub>ICM</sub>                |                                         | 1.5  |                   | 5.1  | V       |

|                            | Hall input sensitivity                 | * ICIVI                         |                                         | 60   |                   | 0.1  | mVp-p   |

| Hall amplifier             | Hysteresis                             | ΔV <sub>IN</sub>                |                                         | 8    | 14                | 24   | mV      |

|                            | Input voltage low → high               | V <sub>SLH</sub>                |                                         | 0    | 7                 | 24   | mV      |

|                            |                                        |                                 |                                         |      |                   |      |         |

|                            | Input voltage high → low               | V <sub>SHL</sub>                |                                         | 2.0  | -7<br>2.1         | 2.4  | mV<br>V |

|                            | Output high level voltage              | V <sub>OH(CR)</sub>             |                                         | 2.8  | 3.1               | 3.4  | V       |

| Oscillator                 | Output low level voltage               | V <sub>OL(CR)</sub>             | B 5010 0 1000 5                         | 0.8  | 1.1               | 1.4  |         |

|                            | Oscillator frequency                   | f <sub>(CR)</sub>               | R = 56 kΩ, C = 1000 pF                  |      | 15                |      | kHz     |

|                            | Amplitude                              | V <sub>(CR)</sub>               |                                         |      | 2.0               |      | Vp-p    |

| Current control operation  | Limiter                                | V <sub>CC</sub> –V <sub>M</sub> |                                         | 0.4  | 0.5               | 0.6  | V       |

| Thermal shutdown operation | Thermal shutdown operating temperature | TSD                             | Design target                           | 150  | 180               |      | °C      |

| Thermal shaldown operation | Hysteresis                             | ΔTSD                            |                                         |      | 50                |      | °C      |

|                            | Input offset voltage                   | V <sub>IO(FG)</sub>             |                                         | -10  |                   | +10  | mV      |

|                            | Input bias current                     | I <sub>B(FG)</sub>              |                                         | -1   |                   | +1   | μA      |

|                            | Output high level voltage              | V <sub>OH(FG)</sub>             | I <sub>FG</sub> = −2 mA                 | 5.5  | 6                 |      | V       |

| CC amplifier               | Output low level voltage               | V <sub>OL(FG)</sub>             | I <sub>FG</sub> = 2 mA                  |      | 1                 | 1.5  | V       |

| FG amplifier               | FG input sensitivity                   |                                 | 100x gain                               | 3    |                   |      | mV      |

|                            | Next stage Schmitt width               |                                 |                                         | 100  | 180               | 250  | mV      |

|                            | Operating frequency range              |                                 |                                         |      |                   | 2    | kHz     |

|                            | Open loop gain                         |                                 | f <sub>(FG)</sub> = 2 kHz               | 45   | 51                |      | dB      |

|                            | Output saturation voltage              | V <sub>O(FGS)</sub>             | I <sub>O(FGS)</sub> = 2 mA              |      | 0.1               | 0.5  | V       |

| FGS output                 | Output leakage current                 | I <sub>L(FGS)</sub>             | V <sub>O</sub> = 5 V                    |      |                   | 10   | μA      |

|                            | Output high level voltage              | V <sub>OH(D)</sub>              |                                         | 4.0  | 4.3               |      | V       |

| Speed discriminator        | Output low level voltage               | I <sub>OL(D)</sub>              |                                         |      | 0.8               | 1.1  | V       |

| .,                         | Number of counts                       | OL(D)                           |                                         |      | 512               |      |         |

|                            | Output high level voltage              | V <sub>OH(P)</sub>              |                                         | 3.2  | 3.5               | 3.8  | V       |

| PLL output                 | Output low level voltage               | V <sub>OL(P)</sub>              |                                         | 1.2  | 1.5               | 1.8  | V       |

|                            | Output low level voltage               | V <sub>OL(LD)</sub>             | I <sub>LD</sub> = 10 mA                 | 1.2  | 0.15              | 0.5  | V       |

| Lock detection             | Locking range                          | * OL(LD)                        | ·LD = 10 m/v                            |      | ±6.25             | 0.0  | %       |

|                            | Input bias current                     | la ar :                         |                                         | -0.4 | 10.20             | +0.4 | μA      |

|                            | Output high level voltage              | I <sub>B(INT)</sub>             |                                         | 3.7  | 4.3               | +0.4 | μA<br>V |

| Integrator                 | · · · · · · · · · · · · · · · · · · ·  | V <sub>OH(INT)</sub>            |                                         | 3.7  |                   | 1.2  | V       |

|                            | Output low level voltage               | V <sub>OL(INT)</sub>            |                                         |      | 0.8               | 1.2  |         |

|                            | Open loop gain                         |                                 |                                         | 60   | 4.0               |      | dB      |

|                            | Gain-bandwidth product                 |                                 |                                         |      | 1.6               | =0:  | MHz     |

|                            | Reference voltage                      |                                 |                                         | -5%  | V <sub>X</sub> /2 | 5%   | V       |

| Crystal oscillator         | Operating frequency range              | fosc                            |                                         | 1    |                   | 10   | MHz     |

|                            | Input high level voltage               | V <sub>IH(S/S)</sub>            |                                         | 4.0  |                   |      | V       |

| Start/stop pin             | Input low level voltage                | V <sub>IL(S/S)</sub>            |                                         |      |                   | 1.5  | V       |

|                            | Pull-down resistance                   | R <sub>D(S/S)</sub>             |                                         | 30   | 50                | 70   | kΩ      |

|                            | Input high level voltage               | V <sub>IH(F/R)</sub>            |                                         | 4.0  |                   |      | V       |

| F                          | Input low level voltage                | V <sub>IL(F/R)</sub>            |                                         |      |                   | 1.5  | V       |

| Forward/reverse pin        | Hysteresis                             | ΔV <sub>IN</sub>                |                                         |      | 0.5               |      | V       |

|                            | Pull-down resistance                   | R <sub>D(F/R)</sub>             |                                         | 30   | 50                | 70   | kΩ      |

|                            |                                        | 1 (1117)                        | 1                                       |      |                   |      |         |

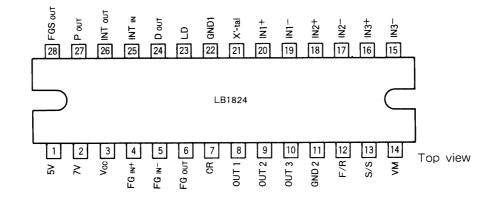

# **Pin Assignment**

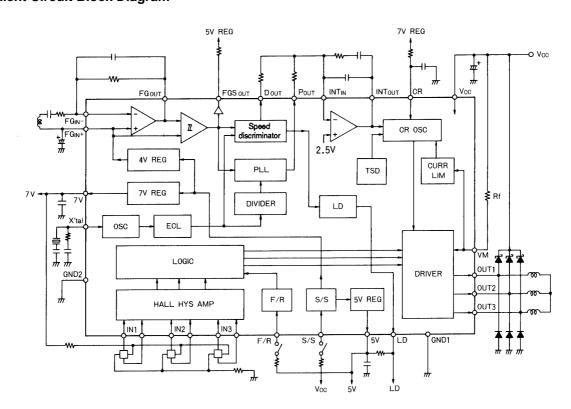

# **Equivalent Circuit Block Diagram**

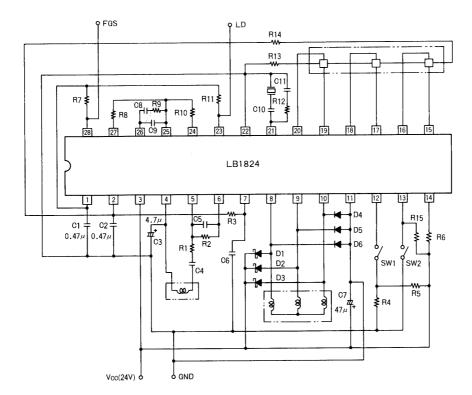

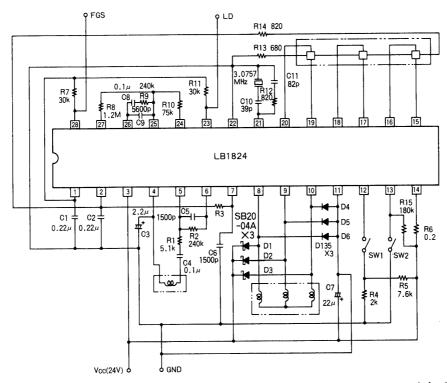

# **Sample Application Circuit**

Unit ( capacitance: F )

# **AC Test Circuit Diagram**

Unit (resistance:  $\Omega$ , capacitance: F)

# **Logic Table**

|           |                         | F/R = Low |     |     | F/R = High |     |     |

|-----------|-------------------------|-----------|-----|-----|------------|-----|-----|

| Parameter | Parameter Source → Sink |           | IN2 | IN3 | IN1        | IN2 | IN3 |

| 1         | OUT3 → OUT2             | Н         | Н   | L   | L          | L   | Н   |

| 2         | OUT3 → OUT1             | Н         | L   | L   | L          | Н   | Н   |

| 3         | OUT2 → OUT3             | L         | L   | Н   | Н          | Н   | L   |

| 4         | OUT1 → OUT2             | L         | Н   | L   | Н          | L   | Н   |

| 5         | OUT2 → OUT1             | Н         | L   | Н   | L          | Н   | L   |

| 6         | OUT1 → OUT3             | L         | Н   | Н   | Н          | L   | L   |

Note: 'H' for an input indicates the state where IN+ > IN-.

H: High L: Low

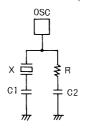

The formula below gives the relationship between the crystal oscillator frequency ( $f_{OSC}$ ) and the FG frequency ( $f_{FG}$ ).

$$f_{FG} \, (servo) = f_{OSC} / (the \, ECL \, divider \, factor \, (16) \times the \, number \, of \, counts) \\ = f_{OSC} / 8192$$

(External crystal oscillator circuit)

# **External Constants (reference values)**

| X'tal (MHz) | C1 (pF) | C2 (pF) | R (kΩ) |

|-------------|---------|---------|--------|

| 3 to 4      | 39      | 82      | 0.82   |

| 4 to 5      | 39      | 82      | 1.0    |

| 5 to 7      | 39      | 47      | 1.5    |

| 7 to 10     | 39      | 27      | 2.0    |

Note that the crystal used should have a ratio between the fundamental wave  $f_O$  impedance and  $3f_O$  impedance of 1:5 or greater.

# **Pin Functions**

| Pin name        | Pin No. | Function                                                                                                      |

|-----------------|---------|---------------------------------------------------------------------------------------------------------------|

| IN1+, IN1-      | 20, 19  | OUT1 Hall input pin                                                                                           |

| IN2+, IN2-      | 18, 17  | OUT2 Hall input pin                                                                                           |

| IN3+, IN3-      | 16, 15  | OUT3 Hall input pin                                                                                           |

| OUT1            | 8       | Output pin 1                                                                                                  |

| OUT2            | 9       | Output pin 2                                                                                                  |

| OUT3            | 10      | Output pin 3                                                                                                  |

| V <sub>CC</sub> | 3       | Pin for the power supply applied to all blocks other than the output block                                    |

| $V_{M}$         | 14      | Output block power supply pin. Also used for output current detection: connecting a resistor                  |

|                 |         | (R <sub>f</sub> ) between this pin and V <sub>CC</sub> allows the output current to be detected as a voltage. |

| GND1            | 22      | Ground for all blocks other than the output block                                                             |

| GND2            | 11      | Output block ground                                                                                           |

| CR              | 7       | Pin for setting the PWM oscillator frequency                                                                  |

| INT IN          | 25      | Integrator input pin                                                                                          |

| INT OUT         | 26      | Integrator output pin (speed control pin)                                                                     |

| D OUT           | 24      | Speed discriminator output pin: overspeed → high                                                              |

| P OUT           | 27      | PLL output pin                                                                                                |

| LD              | 23      | Lock detection pin. Open collector output. Goes low when the motor speed is within the lock range (±6.25%).   |

| FG IN+          | 4       | FG pulse input pin (4 V power supply pin)                                                                     |

| FG IN-          | 5       |                                                                                                               |

| FG OUT          | 6       | FG amplifier output pin                                                                                       |

| FGS OUT         | 28      | FG amplifier output pin (post-schmitt). Open collector output.                                                |

| X'tal           | 21      | Crystal oscillator pin. Connect the crystal oscillator to this pin.                                           |

| 5 V             | 1       | 5 V power supply pin                                                                                          |

| 7 V             | 2       | 7 V power supply pin                                                                                          |

| S/S             | 13      | Start/stop control pin                                                                                        |

|                 |         | $Start \to low, stop \to high$                                                                                |

| F/R             | 12      | Forward/reverse control pin                                                                                   |

|                 |         | Forward → low, reverse → high                                                                                 |

#### LB1824 Functional Description (including external components)

#### 1. Speed control circuit

The LB1824 uses a combination of a speed discriminator circuit and a PLL circuit for speed control. The speed discriminator circuit outputs an error signal once every two FG periods using a charge pump method. The PLL circuit outputs a phase error signal once every FG period also using a charge pump method. As compared with earlier speed control methods that used only a speed discriminator circuit, the combination of both a PLL circuit as well as a speed discriminator circuit employed in the LB1824 results in improved suppression of speed variations in cases where motors with large load variations are used. Since the FG servo frequency determined as shown in the formula below, the motor speed is set by the FG pulse count and the crystal oscillator frequency.

$f_{FG}(servo) = f_{OSC}/8192$  $f_{OSC} = crystal oscillator frequency$

#### 2. Direct PWM drive

The LB1824 adopts a direct PWM drive method in order to reduce the power loss at the output. The output transistor is always saturated when on, and it adjusts the motor drive power by varying the duty that the output is on. Since the output switching is performed by the lower side transistor, Schottky diodes (D1, D2 and D3) must be attached between OUT and  $V_{CC}$ . (This is because if diodes with a short reverse recovery time are not used, through current will flow at the instant that the lower side transistor turns on.) Normal forward current diodes can be used for the diodes between OUT and GND.

#### 3. Current control circuit

The current control circuit performs its control operation with a current determined by  $I=0.5/R_{\rm f}$ . (This limits the peak current.) The control operation functions to reduce the on duty and thus suppress the current. No phase compensation capacitor is required.

#### 4. Speed locking range

The speed locking range is within  $\pm 6.25\%$  of the set speed, and when the motor speed enters the locking range the LD pin goes low (open collector output). When the motor speed is outside the locking range, the motor drive output on duty is changed according to the speed error, thus implementing the control required to return the motor speed to within the locking range.

#### 5. PWM frequency

The PWM frequency is determined by the resistor R3 and the capacitor C6 that are attached to the CR pin.

- When R3 is connected to the 4 V fixed voltage power supply:  $f_{PWM} \approx 1/(1.2 \times C \times R)$

- When R3 is connected to the 7 V fixed voltage power supply:  $f_{PWM} \approx 1/(0.5 \times C \times R)$

Do not use a resistor of less than 30 k $\Omega$  for R3. A PWM frequency of about 15 kHz is desirable. If the PWM frequency is too low, the motor could oscillate at the PWM frequency during motor constraint and become noisy since the oscillation will be in the audible frequency range. On the other hand, if the PWM frequency is too high, the output transistor switching time loss will increase.

# 6. Ground leading

GND1 (pin 22): ground for blocks other than the output block

GND2 (pin 11): output block ground

Connect D4, D5 and D6 to GND2. All other external components should be connected to GND1. The GND1 and GND2 leads should be grounded at a single point at the connector. Since GND2 carries a large current, its lead should be as short as possible.

#### 7. Output parasitic effect

Parasitism occurs when the voltage on an output pin falls more than -0.7 V below GND1 and GND2. (The -0.7 V figure is reduced by the temperature characteristics.) Also, do not let the voltage on the output pins exceed  $V_{CC}$  by more than 1 V. When parasitism occurs, first speed control will be lost intermittently, and then, if it becomes larger, the output transistors can be damaged. D1, D2 and D3 are used to prevent through currents, and Schottky diodes with a low  $V_f$  should be used. Therefore the potential difference between the output pin and  $V_{CC}$  will not be a serious issue. Although normal forward current diodes can be used for D4, D5 and D6, care must be taken to keep the ground leads short, as mentioned in item 6 above, to avoid parasitism.

#### 8. External interface pins

• LD pin

Output type: open collector

Breakdown voltage: a maximum current voltage of 30 V Saturation voltage variance reference value (at  $I_{LD} = 10 \text{ mA}$ )

0.10 V to 0.15 V

• FGS pin

Output type: open collector

Breakdown voltage: a maximum current voltage of 30 V Saturation voltage variance reference value (at  $I_{FGS} = 2 \text{ mA}$ )

0.12 V to 0.18 V

FGS is the FG amplifier output converted to pulses by a hysteresis comparator (for high speed monitoring).

• Start/stop pin

Input type: PNP transistor base with a 50 k $\Omega$  pull-down resistor to ground

Threshold level (typical): about 2.6 V

Turns off the 4, 5 and 7 V fixed voltage power supplies in steps.

• F/R pin

Input type: PNP transistor base with a 50 k $\Omega$  pull-down resistor to ground Threshold level (typical): about 2.2 V (high  $\rightarrow$  low), about 2.7 V (low  $\rightarrow$  high)

With a hysteresis of about 0.5 V.

F/R switching must be performed when stopped. Continued from preceding page.

- 9. Fixed voltage power supply temperature characteristics

- 4 V power supply: about -0.5 mV/°C (typical)

- 5 V power supply: about -0.6 mV/°C (typical)

- 7 V power supply: about -2.5 mV/°C (typical)

### 10. FG amplifier

The FG amplifier gain is set by R1 and R2 to be a gain of G = R2/R1. C4 and C5 determine the FG amplifier's frequency characteristics. (R1 and C4 form a high pass filter, and R2 and C5 form a low pass filter.) Since a Schmitt comparator is connected following the FG amplifier, the FG amplifier's output must be set to be over 250 mVp-p by R1, R2, C4 and C5. (It is desirable that the FG output be between 1 to 3 Vp-p during normal motor rotation.)

#### 11. External capacitors

C3

C3 is required for FGIN+ pin fixed voltage power supply stabilization and for IC internal logic initial reset pulse generation. Although a low capacitance is acceptable for the power supply stabilization function, a relatively large capacitance (about 4.7  $\mu$ F) is required for reset pulse generation. The reset pulse is generated when the FGIN+ pin goes from 0 V to about 1.3 V. If the reset does not occur, it is possible that LD could go on briefly at start time. If this phenomenon is not a problem, a value of 0.1  $\mu$ F can be used for C3. After C3 has been charged to 4 V, when V<sub>CC</sub> is turned off (or in stop mode) the charge on C3 is dissipated through an IC internal load resistance of about 10 k $\Omega$  that is connected to ground.

#### • C1 and C2

C1 and C2 are required for fixed voltage power supply stabilization. Since this IC adopts a direct PWM method and a large current is switched at the output, noise is generated extremely easily. Accordingly, adequate stabilization is required on the power supplies so that noise does not cause incorrect circuit operation.

The connections between C1, C2 and C3 and ground should be kept as short as possible. Special care should be exercised with respect to C1, since its characteristics are easily influenced by grounding problems.

#### 12. External resistors

• R4 and R5

R4 and R5 are used to apply a high level to the F/R pin. Since there is a pull-down resistance of about 50 k $\Omega$  on the F/R input pin it goes low when open. A high level input to the F/R pin should be at least 4.0 V and not more than 6.3 V.

• R15

R15 is used to apply a high level to the S/S pin. Since there is a pull-down resistance of about 50 k $\Omega$  on the S/S input it goes low when open. (In the start state a high level input to the S/S pin should be at least 4.0 V and not more than 6.3 V.) As is the case with the F/R pin, the resistance is divided into 2 resistors, and while this scheme is resistant to noise (since the input impedance can be lowered), if noise is not a problem the high level can be set by connecting a single resistor such as R15. (A value of 180 k $\Omega$  is recommended.)

If the initial rise in  $V_{CC}$  is slow (under about 10 V/ms) the motor may turn to some extent (in stop mode) when  $V_{CC}$  is first applied. This is because the S/S input voltage is resistor divided, and when  $V_{CC}$  is under 12 V, the input voltage will be under 2.6 V (the start input level). If the rise slope cannot be increased and this phenomenon is a problem, it can be handled by connecting a capacitor between  $V_{CC}$  and S/S.

#### 13. Through currents due to the direct PWM method

In the direct PWM method through currents flow in the outputs due to the switching, e.g., when used in a discrete structure or in LB1822 applications. This is due to the output transistor's delay and parasitic capacitance. Previously, an external capacitor was used to handle this kind of situation. However, the LB1824 provides internal circuit measures to handle this problem, and no measures based on external components are required. Although an overshoot with a duration of under 10 ns will appear on the RF voltage waveform during switching, this will not be a problem.

# 14. Oscillator

A crystal oscillator is normally used with the LB1824. If the speed control conditions are not critical, a ceramic oscillator could be used. To avoid problems always consult the oscillator's manufacturer concerning the oscillator itself and the external resistances and capacitances used.

15. IC internal power dissipation calculation example (calculation for a V<sub>CC</sub> of 24 V and typical ratings)

• Power dissipation due to the power supply current (I<sub>CC</sub>)

At start time:

$$P1 = V_{CC} \times I_{CC1} = 24 \times 34 \text{ m} = 0.82 \text{ W}$$

At stop time:

$$P2 = V_{CC} \times I_{CC2} = 24 \times 8 \text{ m} = 0.19 \text{ W}$$

• Power dissipation when a -10 mA load current is taken from the 7 V fixed voltage output P3 =  $(V_{CC} - 7) \times 10$  m =  $17 \times 10$  m = 0.17 W

• Power dissipation due to the output drive current (for an output on duty of 100%)

$$P4 = \{(V_{CC} - 1)^2/8 \text{ k}\} + \{(V_{CC} - 2)^2/10 \text{ k}\}$$

$$= (23^2/8 \text{ k}) + (22^2/10 \text{ k}) = 0.12 \text{ W}$$

• Power dissipation in the output transistor (For  $I_0 = 2$  A and an output on duty of 100%)

$$P5 = V_{Osat2} \times I_{O} = 2.7 \times 2 = 5.4 \text{ W}$$

Therefore the IC overall power dissipation is:

At stop time:

P = P2 = 0.19 WAt start time: P = P1 + P3 + P4 + P5 = 6.51 W(for an output on duty of 100%)

#### 16. Techniques for measuring the IC temperature increase

• Measurement with a thermocouple

When using a thermocouple to measure the IC temperature, the thermocouple should be attached to a fin. While this measurement technique is simple, it is subject to large measurement errors if the IC is not in a stable heat generation state.

- Measurement using the characteristics of an IC internal diode We recommend using the parasitic diode between INT.IN and GND internal to the IC. (According to our data,  $I_D$  = 1 mA with about

- 1.8 mV/°C) Remove the external resistor when making the measurements.

#### 17. Servo constants

When calculating the servo constants, they will be heavily dependent on the motor actually used. Since experience is generally required, these constants should be determined by the motor manufacturer. We can provide the IC characteristics data required for the servo constants calculations as well as frequency characteristics simulation data for the filter constants set by the motor manufacturer.

If the resistor connected between DOUT and INT.IN (R10) is too small, C8 and C9 are too large, and R10 is too large, speed errors will be likely to occur due to the speed discriminator cutoff current and the integrator input current. Therefore, a 10 to 100 k $\Omega$  resistor should be used. If the resistor connected between POUT and INT.IN (R8) is too small, the PLL system influence will become too large and the in-phase pull-in to locking will get worse. Therefore, do not make this value too small. (We recommend 1 M $\Omega$  when R10 is 75 k $\Omega$ .) First set the constants just for the speed discriminator system (R9, R10, C8 and C9) and then set the R8 value for the PLL system.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 1997. Specifications and information herein are subject to change without notice.