Ordering number : EN\*5041A

**CMOS LSI**

# LC11011-141

# **Computer Image Signal Processing Full-Color Gray-Scale Processor**

# **Preliminaly**

#### Overview

The LC11011-141 is a pseudo gray scale processor for TFT LCD. It allows LCD panels with inputs of three to six bits per RGB to display the equivalent of 16.7 million colors.

#### **Features**

- Handles 8-bits of input data (256-scale data) for each of the RGB colors.

- Operating mode selection of three, four, or six bit driver outputs

- Realizes reduced resolution loss (as compared to dithering techniques) by using intra- and inter-frame error diffusion processing.

- Supports both 5 V and low voltage (3.3 V) operation.

- Operates with arbitrary clock frequencies up to 50 MHz (at 5 V) or up to 30 MHz (at 3.3 V).

- Can operate independently of the number of displayed pixels since internal operation is controlled by the horizontal and vertical synchronization signals.

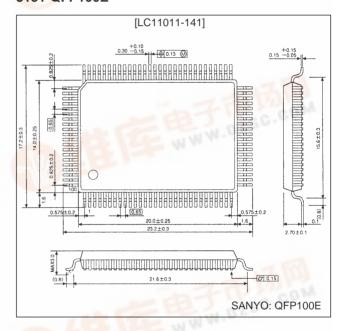

# Package Dimensions

unit: mm

#### 3151-QFP100E

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C, V<sub>SS</sub> = 0 V

| Parameter                 | Symbol                          | Conditions | Ratings                       | Unit |

|---------------------------|---------------------------------|------------|-------------------------------|------|

| Maximum supply voltage    | V <sub>DD</sub> max             |            | -0.3 to +7.0                  | V    |

| Input and output voltages | V <sub>I</sub> , V <sub>O</sub> |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature     | Topr                            | 100        | 0 to +70                      | °C   |

| Storage temperature       | Tstg                            |            | -40 to +125                   | °C   |

# Electrical Characteristics: At an operating voltage of 5.0 V Operating Ranges at Ta = 0 to $+70^{\circ}C$

| D               |                  | 750-0      |     | Ratings |                 |      |

|-----------------|------------------|------------|-----|---------|-----------------|------|

| Parameter       | Symbol           | Conditions | min | typ     | max             | Unit |

| Supply voltage  | $V_{DD}$         |            | 4.5 | 5.0     | 5.5             | V    |

| Input voltage   | V <sub>IN</sub>  |            | 0   |         | V <sub>DD</sub> | V    |

| Clock frequency | f <sub>clk</sub> |            |     |         | 50              | MHz  |

#### LC11011-141

# DC Characteristics at Ta=0 to +70°C, $V_{SS}=0$ V, $V_{DD}=4.5$ to 5.5 V

|                           |                 | 0 111                   |                     | Ratings |                     | 11.7 |

|---------------------------|-----------------|-------------------------|---------------------|---------|---------------------|------|

| Parameter                 | Symbol          | Conditions              | min typ             |         | max                 | Unit |

| High level input voltage  | V <sub>IH</sub> | CMOS level              | 0.7 V <sub>DD</sub> |         |                     | V    |

| Low level input voltage   | V <sub>IL</sub> | CMOS level              |                     |         | 0.3 V <sub>DD</sub> | V    |

| High level output voltage | V <sub>OH</sub> | I <sub>OH</sub> (–4 mA) | 2.4                 |         |                     | V    |

| Low level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> (4 mA)  |                     |         | 0.4                 | V    |

| Supply current            | Icc             | *                       |                     | 40      | 70                  | mA   |

Note: \* The test conditions are:  $f_{CP} = 25.175 \text{ MHz}$ ,  $V_{DD} = 5.0 \text{ V}$ ,  $C_L = 15 \text{ pF}$  (measured with VGA timing)

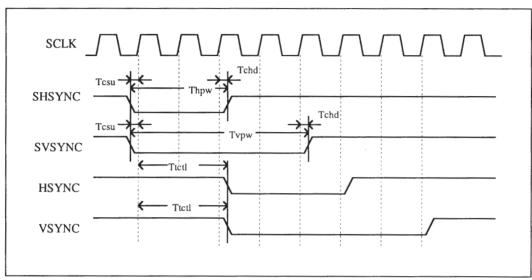

# Switching Characteristics at Ta = 0 to +70 $^{\circ}$ C, $V_{SS}$ = 0 V, $V_{DD}$ = 4.5 to 5.5 V, $C_L$ = 15 pF

|                                       |        | 9 1111     |             |             |              |      |

|---------------------------------------|--------|------------|-------------|-------------|--------------|------|

| Parameter                             | Symbol | Conditions | min         | typ         | max          | Unit |

| Dot clock cycle time                  | Tdclk  |            | 20          |             |              | ns   |

| Hsync low level pulse width           | Thpw   |            | 2 Tdclk     |             |              | ns   |

| Vsync low level pulse width           | Tvpw   |            | 2 Tdclk     |             |              | ns   |

| Data setup time                       | Tdsu   |            | 5           |             |              | ns   |

| Data hold time                        | Tdhd   |            | 5           |             |              | ns   |

| Control signal setup time             | Tcsu   |            | 5           |             |              | ns   |

| Control signal hold time              | Tchd   |            | 5           |             |              | ns   |

| CLK propagation delay time            | Ttdhh  |            | 2           | 3           | 6            | ns   |

| CLK propagation delay time            | Ttdll  |            | 2           | 4           | 7            | ns   |

| CLKB propagation delay time           | Ttdhl  |            | 2           | 4           | 7            | ns   |

| CLKB propagation delay time           | Ttdlh  |            | 2           | 4           | 7            | ns   |

| Control signal propagation delay time | Ttctl  |            | 2 Tdclk + 3 | 2 Tdclk + 6 | 2 Tdclk + 10 | ns   |

| Data output propagation delay time    | Ttdata |            | 2 Tdclk + 3 | 2 Tdclk + 6 | 2 Tdclk + 11 | ns   |

# Electrical Characteristics: At an operating voltage of 3.3 V Operating Ranges at Ta = 0 to $+70^{\circ}C$

| Demonstra       | 0                 | Condition - |     | Ratings |          | Unit |  |  |

|-----------------|-------------------|-------------|-----|---------|----------|------|--|--|

| Parameter       | Symbol Conditions |             | min | typ     | typ max  |      |  |  |

| Supply voltage  | V <sub>DD</sub>   |             | 3.0 | 3.3     | 3.6      | V    |  |  |

| Input voltage   | V <sub>IN</sub>   |             | 0   |         | $V_{DD}$ | V    |  |  |

| Clock frequency | f <sub>clk</sub>  |             |     |         | 30       | MHz  |  |  |

# DC Characteristics at Ta = 0 to +70 $^{\circ}C,\,V_{SS}$ = 0 V, $V_{DD}$ = 3.0 to 3.6 V

| B                         |                 | 0 111                   |                     | Ratings |                     |      |  |

|---------------------------|-----------------|-------------------------|---------------------|---------|---------------------|------|--|

| Parameter                 | Symbol          | Conditions              | min                 | typ     | max                 | Unit |  |

| High level input voltage  | V <sub>IH</sub> | CMOS level              | 0.7 V <sub>DD</sub> |         |                     | V    |  |

| Low level input voltage   | V <sub>IL</sub> | CMOS level              |                     |         | 0.3 V <sub>DD</sub> | V    |  |

| High level output voltage | V <sub>OH</sub> | I <sub>OH</sub> (–2 mA) | 2.2                 |         |                     | V    |  |

| Low level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> (2 mA)  |                     |         | 0.4                 | V    |  |

| Supply current            | I <sub>CC</sub> | *                       |                     | 30      | 45                  | mA   |  |

Note: \* The test conditions are:  $f_{clk} = 25.175 \text{ MHz}$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $C_L = 15 \text{ pF}$  (measured with VGA timing)

LC11011-141

# Switching Characteristics at Ta = 0 to $+70^{\circ}$ C, $V_{SS} = 0$ V, $V_{DD} = 3.0$ to 3.6 V, $C_L = 15$ pF

|                                       |                   | 9 1111 |             | Ratings      |              |      |  |

|---------------------------------------|-------------------|--------|-------------|--------------|--------------|------|--|

| Parameter                             | Symbol Conditions |        | min         | typ          | max          | Unit |  |

| Dot clock cycle time                  | Tdclk             |        | 33          |              |              | ns   |  |

| Hsync low level pulse width           | Thpw              |        | 2 Tdclk     |              |              | ns   |  |

| Vsync low level pulse width           | Tvpw              |        | 2 Tdclk     |              |              | ns   |  |

| Data setup time                       | Tdsu              |        | 10          |              |              | ns   |  |

| Data hold time                        | Tdhd              |        | 10          |              |              | ns   |  |

| Control signal setup time             | Tcsu              |        | 10          |              |              | ns   |  |

| Control signal hold time              | Tchd              |        | 10          |              |              | ns   |  |

| CLK propagation delay time            | Ttdhh             |        | 2           | 5            | 12           | ns   |  |

| CLK propagation delay time            | Ttdll             |        | 2           | 6            | 14           | ns   |  |

| CLKB propagation delay time           | Ttdhl             |        | 2           | 6            | 14           | ns   |  |

| CLKB propagation delay time           | Ttdlh             |        | 2           | 6            | 14           | ns   |  |

| Control signal propagation delay time | Ttctl             |        | 2 Tdclk + 5 | 2 Tdclk + 10 | 2 Tdclk + 22 | ns   |  |

| Data output propagation delay time    | Ttdata            |        | 2 Tdclk + 5 | 2 Tdclk + 10 | 2 Tdclk + 24 | ns   |  |

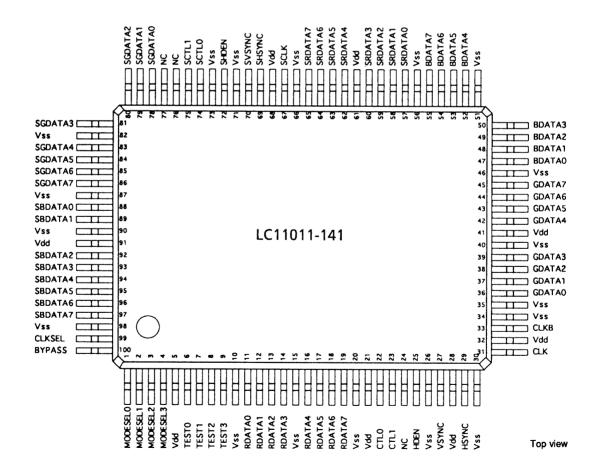

## **Pin Assignment**

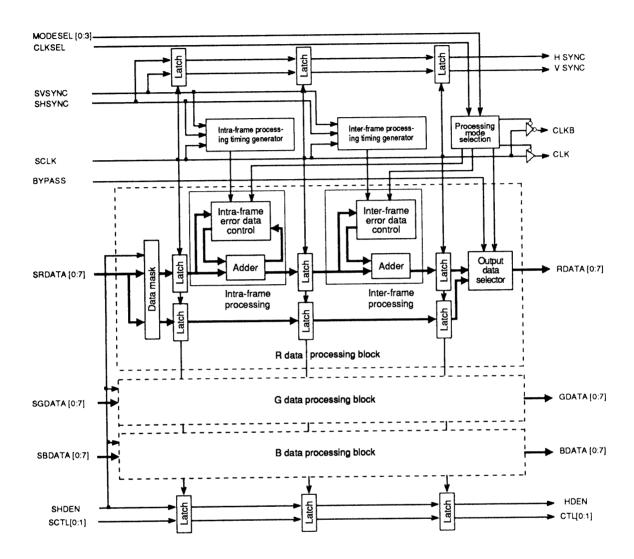

## **Block Diagram**

## LC11011-141

## **Pin Functions**

| Symbol          | Pin No.                                                               | I/O    | Function                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|-----------------|-----------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|-------------|--------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------------------|-------------|-------------|-------------|-------|

| V <sub>DD</sub> | 5, 21, 28, 32, 41,<br>61, 68, 91                                      | Input  | Power supply                                                                                                                                                                                   | (+5 V)                                                                                                                                                                                                                                                                                                                |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| V <sub>SS</sub> | 10, 15, 20, 26, 30, 34, 35, 40, 46,51, 56, 66, 71, 73, 82, 87, 90, 98 | Input  | GND (0 V)                                                                                                                                                                                      | GND (0 V)                                                                                                                                                                                                                                                                                                             |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| NC              | 24, 76, 77                                                            | _      | Must be left op                                                                                                                                                                                | en.                                                                                                                                                                                                                                                                                                                   |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| MODESELO        | 1                                                                     | Input  | The setting promoted MODESEL0 is Note that mode of input for each                                                                                                                              | Mode selection signals [0:3] for the gray scale mode.  The setting process for the mode selection lines is described below.  MODESEL0 is the LSB, and MODESEL3 is the MSB.  Note that modes 8, 9, C, D and E are compatible with the LC1001-131 (a product that handles 6-bits of input for each of the RGB signals). |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | l                                                                                                                                                                                              | ale mode                                                                                                                                                                                                                                                                                                              | 0                                       | 1      | 2           | 3                                                                        | 4           | 5           | 6           | 7           | 8           | 9           | Α           | В                | С           | D           | E           | F     |

| MODESEL1        | 2                                                                     | Input  | MODESEL0<br>MODESEL1<br>MODESEL2<br>MODESEL3                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                       | L<br>L<br>L                             | HLLL   | H<br>L<br>L | H<br>H<br>L                                                              | L<br>H<br>L | H<br>H<br>L | H<br>H<br>L | H<br>H<br>L | L<br>L<br>H | H<br>L<br>H | H<br>L<br>H | H<br>H<br>L<br>H | L<br>H<br>H | H<br>H<br>H | H<br>H<br>H | H H H |

|                 | _                                                                     |        | Processing                                                                                                                                                                                     | Intra-frame processing Inter-frame                                                                                                                                                                                                                                                                                    | Υ                                       | Υ      | R           | Y                                                                        | R           | Y           | Y           | Y           | Υ           | Y           | R           | R                | Y           | Υ           | Υ           | R     |

|                 |                                                                       |        |                                                                                                                                                                                                | processing                                                                                                                                                                                                                                                                                                            | Y                                       | Υ      |             | Υ                                                                        |             | N           | N           | N           | Υ           | Υ           |             |                  | N           | N           | N           |       |

|                 |                                                                       |        | Number of va                                                                                                                                                                                   | alid input bits                                                                                                                                                                                                                                                                                                       | 8                                       | 8      |             | 8                                                                        |             | 8           | 8           | 8           | 6           | 6           |             |                  | 6           | 6           | 6           |       |

|                 | 3                                                                     |        | Number of ou                                                                                                                                                                                   | utput bits                                                                                                                                                                                                                                                                                                            | 3                                       | 4      |             | 6                                                                        |             | 4           | 5           | 6           | 3           | 4           |             |                  | 3           | 4           | 5           |       |

| MODESEL2        |                                                                       | 3      | Input                                                                                                                                                                                          | Note: Y = yes,                                                                                                                                                                                                                                                                                                        | N = no, R = ro                          | eserv  | ed          |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | Gray scale modes 0, 8 and C Operating mode for TFT-LCD modules using 3-bit source drivers.                                                                                                     |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | Gray scale modes 1 and 9 Operating mode for TFT-LCD modules using 4-bit source drivers.                                                                                                        |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | Gray scale mode 3 Operating mode for TFT-LCD modules using 6-bit source drivers.                                                                                                               |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | Gray scale modes 5 and D  Operating mode for TFT-LCD modules that perform FRC or other inter-frame processing.                                                                                 |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| MODESEL3        | 4                                                                     | Input  | Gray scale m                                                                                                                                                                                   | odes 6, 7 and                                                                                                                                                                                                                                                                                                         | Е                                       |        |             | ting mode for TFT-LCD modules that perform FRC or other rame processing. |             |             |             |             |             |             |             |                  |             |             |             |       |

|                 |                                                                       |        | Note: Do not u<br>frame pr                                                                                                                                                                     | ise gray scale<br>ocessing.                                                                                                                                                                                                                                                                                           | mod                                     | es 0,  | 1, 3        | , 8 ar                                                                   | nd 9        | with        | LCD         | mod         | ules        | that        | perfo       | rm F             | RC o        | or oth      | ner in      | ter-  |

| BYPASS          | 100                                                                   | Input  | Input bypass p<br>simply passes<br>rising edge of                                                                                                                                              | the input sign                                                                                                                                                                                                                                                                                                        | als th                                  | roug   | h un        | chan                                                                     | ged.        | Whe         | n a l       | ow le       | evel i      | nput        | on th       | is pi            | n is s      | amp         |             |       |

| TEST0           | 6                                                                     | Input  |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| TEST1           | 7                                                                     | Input  | Toot nine (0.01                                                                                                                                                                                | loft open in -                                                                                                                                                                                                                                                                                                        | orma                                    | l one  | roti-       | 'n                                                                       |             |             |             |             |             |             |             |                  |             |             |             |       |

| TEST2           | 8                                                                     | Input  | Test pins [0:3]                                                                                                                                                                                | , ieit open in n                                                                                                                                                                                                                                                                                                      | orma                                    | п оре  | ıaliC       | 11.                                                                      |             |             |             |             |             |             |             |                  |             |             |             |       |

| TEST3           | 9                                                                     | Input  |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                         |        | _           |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| SCLK            | 67                                                                    | Input  | Display dot clo                                                                                                                                                                                | ck input. Data                                                                                                                                                                                                                                                                                                        | is pr                                   | oces   | sed         | acco                                                                     | rding       | to th       | nis clo     | ock s       | igna        | I.          |             |                  |             |             |             |       |

| SRDATA [0:7]    | 57 to 60, 62 to 65                                                    | Input  |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             | <b>-</b>    | 00-         |             | _           |             |             |                  |             |             | <b>.</b>    |       |

| SGDATA [0:7]    | 78 to 81, 83 to 86                                                    | Input  | Input pins for r<br>SRDATA0, SG                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             | SGD         | ATA         | .7, ar      | nd SI       | 3DA7        | 1A7 a            | are th      | e MS        | SBs.        |       |

| SBDATA [0:7]    | 88, 89, 92 to 97                                                      | Input  | 51.57.17.0, 00                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,.0    | ur C        |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| Shsync          | 69                                                                    | Input  | Horizontal and                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                     |                                         |        | _           |                                                                          | •           |             |             |             |             |             |             |                  | •           |             | Vsyr        | nc    |

| Svsync          | 70                                                                    | Input  | signals. These                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| SHDEN           | 72                                                                    | Input  | Horizontal data valid. If this sig period.                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

| SCTL0           | 74                                                                    | Input  | LCD control in                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                       |                                         | -      |             |                                                                          |             |             |             |             |             |             | -           |                  | -           |             | are         | the   |

| SCTL1           | 75                                                                    | Input  | sources for the<br>SCTL [0:1] sig                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                     | ii the                                  | UIL    | . [U:1      | ı sıgı                                                                   | nais        | are r       | iot us      | sea, i      | nere        | ıs n        | o nee       | a to             | ınpu        | tne         |             |       |

| CLKSEL          | 99                                                                    | Input  | CLKSEL is the                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                       | out se                                  | electi | on. I       | t is u                                                                   | sed t       | o se        | lect tl     | he o        | utput       | mod         | le of       | the c            | lot clo     | ock s       | igna        | I     |

| CLK             | 31                                                                    | Output | output pin.                                                                                                                                                                                    | ·                                                                                                                                                                                                                                                                                                                     |                                         |        |             |                                                                          |             |             |             |             | ·           |             |             |                  |             |             | _           |       |

| CLKB            | 33                                                                    | Output | If CLKSEL is low: A signal with the same phase as the SCLK pin is output from the CLK pin.  If CLKSEL is high: A signal with the opposite phase from the SCLK pin is output from the CLKB pin. |                                                                                                                                                                                                                                                                                                                       |                                         |        |             |                                                                          |             |             |             |             |             |             |             |                  |             |             |             |       |

#### Continued from preceding page.

| Symbol      | Pin No.            | I/O    | Function                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RDATA [0:7] | 11 to 14, 16 to 19 | Output | Red, green and blue gray scale data output pins. These are delayed by 2 clock cycles with respect to the input data.  RDATA7, GDATA7 and BDATA7 are the MSBs.  In modes 0, 8, C and F, RDATA5, GDATA5 and BDATA5 are the LSBs. In these modes, RDATA [0:4].        |  |  |  |  |

| GDATA [0:7] | 36 to 39, 42 to 45 | Output | GDATA [0:4] and BDATA [0:4] are not used. In modes 1, 5, 9 and D, RDATA4, GDATA4 and BDATA4 are the LSBs. In these modes, RDATA [0:3], GDATA [0:3] and BDATA [0:3] are not used.                                                                                   |  |  |  |  |

| BDATA [0:7] | 47 to 50, 52 to 55 | Output | In modes 6 and E, RDATA3, GDATA3 and BDATA3 are the LSBs. In these modes, RDATA [0:2], GDATA [0:2] and BDATA [0:2] are not used.  In modes 3 and 7, RDATA2, GDATA2 and BDATA2 are the LSBs. In these modes, RDATA [0:1], GDATA [0:1] and BDATA [0:1] are not used. |  |  |  |  |

| Vsync       | 27                 | Output | Horizontal and vertical synchronization signal outputs. To match the data signal timing these are delayed                                                                                                                                                          |  |  |  |  |

| Hsync       | 29                 | Output | by two clock cycles with respect to their input signals.                                                                                                                                                                                                           |  |  |  |  |

| HDEN        | 25                 | Output | Horizontal data valid period signal output                                                                                                                                                                                                                         |  |  |  |  |

| CLT0        | 22                 | Output | LCD control signal outputs. To match the data signal timing these are delayed by two clock cycles with                                                                                                                                                             |  |  |  |  |

| CLT1        | T1 23 Output       |        | respect to the SCTL [0:1] input signals.                                                                                                                                                                                                                           |  |  |  |  |

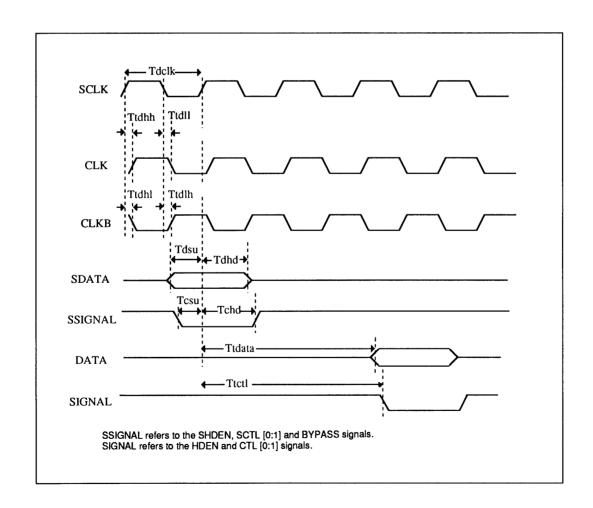

# **Timing Chart**

Continued from preceding page.

This LSI is an improved version of the ALC1009-141.

#### **Usage Note**

Since this LSI performs spatial modulation using an error diffusion algorithm, patterns that differ from the original images may be displayed for certain display pattern and gray-scale mode combinations.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.