Ordering number: EN \$1966 A404A供应商

CMOS LSI

No × 3966A

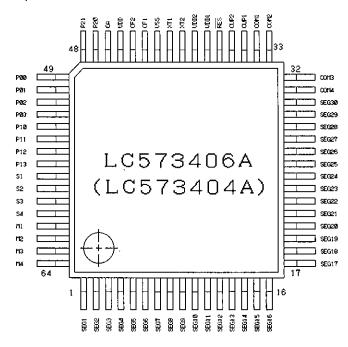

## LC573404A, 573406A

4-bit Single Chip Microcomputer with LCD Driver

#### Preliminary

#### OVERVIEW

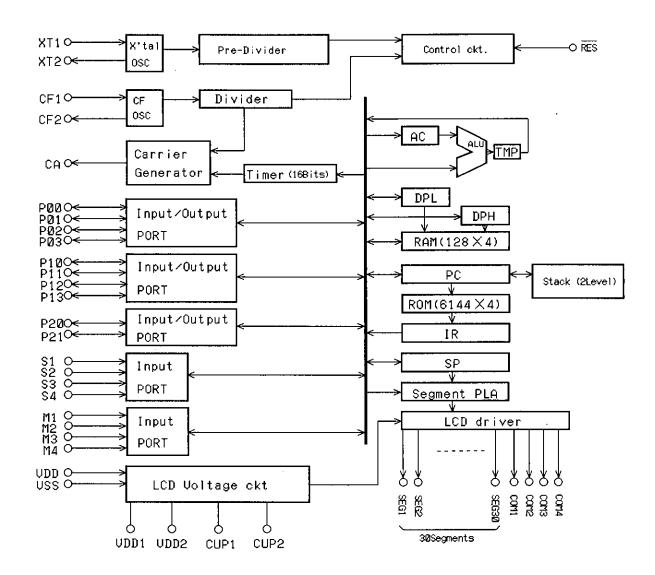

The LC573404A and LC573406A are low-power 4-bit microcontrollers with built-in 4- and 6-Kbyte ROMs, respectively.

They incorporate a 120-segment LCD driver, RAM, a 4-bit parallel-processing ALU, a 16-bit timer and a carrier output for infrared remote control applications.

The LC573404A and LC573406A are ideal for use in battery-operated measuring instruments, products that require timing functions, and LCD and remote controller applications. The LC573404A and LC573406A operate from a 2.3 to 6.0 V supply and are available in 64-pin QFPs and as dice.

#### **FEATURES**

1) ROM

6 Kbytes (LC573406A)

4 Kbytes (LC573404A)

2) RAM

512-bit (128  $\times$  4)

- 4) 120-segment LCD controller/driver

- ·30 segment outputs

- ·Four common outputs

120-segment capability when using 1/4 duty

90-segment capability when using 1/3 duty

60-segment capability when using 1/2 duty

30-segment capability when using static drive

SEG16 to SEG30 can be used as normal, p-channel open-drain output ports.

- 5) 16-bit software-controllable timer

- 6)455 kHz ceramic resonator timebase

- ·Configurable as a 15-bit free-running timer

- ·108 ms HALT-mode cancel signal output

- 7) HALT mode

- ·Reduces current consumption.

- ·Suspends program execution.

- •Exited by a system reset or the HALT-mode cancel signal.

- 8) STOP mode

- ·Stops the ceramic resonator oscillator.

- ·Exited by a system reset or under program control.

#### 9) HOLD mode

- ·Stops the ceramic resonator oscillator.

- ·Exited by a system reset or a HIGH level on ports S or M.

- 10) Two-level subroutine stack

- 11)Cycle Time

- •17.6  $\mu$ s and 122  $\mu$ s cycle times at f = 455 kHz and 32.768 kHz, respectively

- 12)Software-controllable remote control carrier signal generator

- ·Software-controllable frequency and duty cycle

- ·1 to 200 kHz

- ·Three fixed waveforms

- 38 kHz with 1/3 duty

- 38 kHz with 1/2 duty

- 57 kHz with 1/2 duty

- 13) Built-in ceramic and crystal oscillators

- 14)Ports

- •Two 4-bit keyscan input ports

- ·Two 4-bit keyscan output ports

- ·One 2-bit keyscan expansion or LED driver port

- 15) Voltage

- •2.3 to 6.0 V supply voltage

- 16) Factory shipment

- ·64-pin QFP and 66-pad die

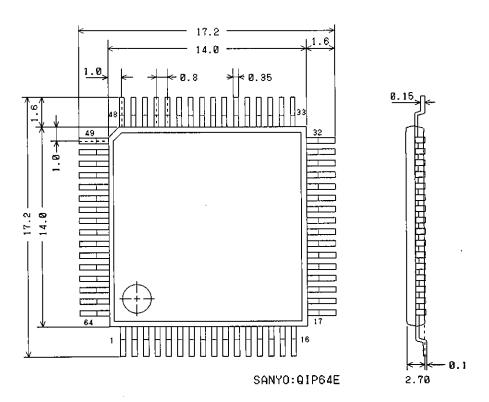

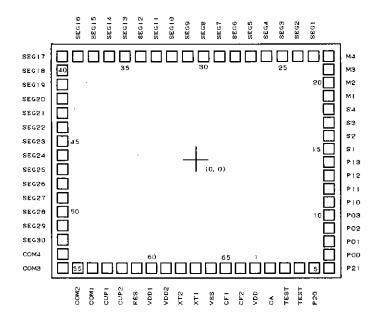

#### PINOUT

Do not use a soldering iron when mounting the package.

#### DIE SPECIFICATIONS

Chip size

: 3.89 mm imes 3.59 mm

Pad size

: 120  $\mu$  m imes 120  $\mu$  m

Chip thickness

:480 μm

#### Pad Layout

Pin Assignment of Package Chip thickness : 330 μm

SANYO: QIP64E

#### Pad Coordinates

|        |     | <u></u>  |       |       |        | ı   |          |                  |      |

|--------|-----|----------|-------|-------|--------|-----|----------|------------------|------|

| QFP64  | pad | Pad Name | X     | Y     | QFP64  | pad | Pad Name | X                | Y    |

| Pin No | No. |          | (μm)  | (μm)  | Pin No | No. |          | $(\mu  {\tt m})$ | (μ1  |

|        |     |          |       |       |        |     |          |                  |      |

| 45     | 1   | VDD      | 720   | -1530 | 14     | 36  | SEG14    | -1210            | 160  |

| 46     | 2   | CA       | 975   | -1530 | 15     | 37  | SEG15    | -1390            | . 16 |

| -      | 3   | TEST     | 1155  | -1530 | 16     | 38  | SEG16    | -1570            | 16   |

| -      | 4   | TEST     | 1335  | -1530 | 17     | 39  | SEG17    | -1750            | 16   |

| 47     | 5   | P20      | 1515  | -1530 | 18     | 40  | SEG18    | -1750            | 13   |

| 48     | 6   | P21      | 1700  | -1530 | 19     | 41  | SEG19    | -1750            | 120  |

| 49     | 7   | P00      | 1690  | -1170 | 20     | 42  | SEG20    | -1750            | 10:  |

| 50     | 8   | P01      | 1690  | - 990 | 21     | 43  | SEG21    | -1750            | 8    |

| 51     | 9   | P02      | 1690  | - 810 | 22     | 44  | SEG22    | -1750            | 6    |

| 52     | 10  | P03      | 1690  | - 630 | 23     | 45  | SEG23    | -1750            | 4    |

| 53     | 11  | P10      | 1690  | - 450 | 24     | 46  | SEG24    | -1750            | 3    |

| 54     | 12  | P11      | 1690  | - 270 | 25     | 47  | SEG25    | -1750            | 1:   |

| 55     | 13  | P12      | 1690  | - 90  | 26     | 48  | SEG26    | -1750            | -    |

| 56     | 14  | P13      | 1690  | 90    | 27     | 49  | SEG27    | -1750            | - 2  |

| 57     | 15  | S1       | 1690  | 310   | 28     | 50  | SEG28    | -1750            | - 4  |

| 58     | 16  | S2       | 1690  | 490   | 29     | 51  | SEG29    | -1750            | - 5  |

| 59     | 17  | S3       | 1690  | 670   | 30     | 52  | SEG30    | -1750            | - 7  |

| 60     | 18  | S4       | 1690  | 850   | 31     | 53  | COM4     | -1750            | - 9  |

| 61     | 19  | M1       | 1690  | 1030  | 32     | 54  | COM3     | -1750            | -15  |

| 62     | 20  | M2       | 1690  | 1210  | 33     | 55  | COM2     | -1570            | -15  |

| 63     | 21  | M3       | 1690  | 1390  | 34     | 56  | COM1     | -1390            | -15  |

| 64     | 22  | M4       | 1690  | 1570  | 35     | 57  | CUP1     | -1160            | -15  |

| 1      | 23  | SEG1     | 1130  | 1600  | 36     | 58  | CUP2     | - 980            | -15  |

| 2      | 24  | SEG2     | 950   | 1600  | 37     | 59  | RES      | - 800            | -15  |

| 3      | 25  | SEG3     | 770   | 1600  | 38     | 60  | VDD1     | - 620            | -15  |

| 4      | 26  | SEG4     | 590   | 1600  | 39     | 61  | VDD2     | - 440            | -15  |

| 5      | 27  | SEG5     | 410   | 1600  | 40     | 62  | XT2      | - 260            | -15  |

| 6      | 28  | SEG6     | 230   | 1600  | 41     | 63  | XT1      | - 80             | -15  |

| 7      | 29  | SEG7     | 50    | 1600  | 42     | 64  | VSS      | 100              | -15  |

| 8      | 30  | SEG8     | - 130 | 1600  | 43     | 65  | CF1      | 360              | -15  |

| 9      | 31  | SEG9     | - 310 | 1600  | 44     | 66  | CF2      | 540              | -15  |

| 10     | 32  | SEG10    | - 490 | 1600  |        |     |          | ]                |      |

| 11     | 33  | SEG11    | - 670 | 1600  |        |     |          |                  |      |

| 12     | 34  | SEG12    | - 850 | 1600  |        |     |          |                  | ٠    |

| 13     | 35  | SEG13    | -1030 | 1600  |        |     |          |                  |      |

| -0     | ~~  |          | -~~   | -000  |        |     |          |                  |      |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

#### BLOCK DIAGRAM

### PIN DESCRIPTION

| Num      | ber      | NT            | D                                                                                                                                       |

|----------|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| QFP64    | Die      | Name          | Description                                                                                                                             |

| 45       | 1        | VDD           | Supply voltage. See figure 1.                                                                                                           |

| 42       | 64       | VSS           | Ground. See figure 1.                                                                                                                   |

| 38<br>39 | 60<br>61 | VDD1<br>VDD2  | LCD driver supply voltage inputs. See figure 1.                                                                                         |

|          |          |               | NON 1/1bias 1/2bias 1/3bias  VDD O O O O  VDD1 O O O O  VDD2 O O O O  VSS O O O O                                                       |

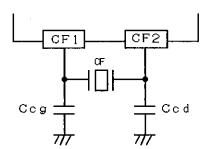

| 35<br>36 | 57<br>58 | CUP1<br>CUP2  | LCD driver external coupling capacitor. A non-polarized capacitor should be connected between CUP1 and CUP2 when using 1/2 or 1/3 bias. |

| 43       | 65       | CF1           | 455kHz ceramic resonator oscillator input                                                                                               |

| 44       | 66       | CF2           | 455kHz ceramic resonator oscillator output                                                                                              |

| 41       | 63       | XT1           | 32.768 kHz crystal oscillator input                                                                                                     |

| 40       | 62       | XT2           | 32.768 kHz crystal oscillator output                                                                                                    |

| 57 to 60 | 15 to 18 | S1 to S4      | Input port S.                                                                                                                           |

| 61 to 64 | 19 to 22 | M1 to M4      | Input port M                                                                                                                            |

| 49 to 52 | 7 to 10  | P00 to<br>P03 | Bidirectional port PO. P-channel open-drain outputs                                                                                     |

| 53 to 56 | 11 to 14 | P10 to<br>P13 | Bidirectional port P1. P-channel open-drain outputs                                                                                     |

| 47<br>48 | 5<br>6   | P20<br>P21    | Bidirectional port P2. P-channel open-drain outputs. P20 and P21 can be used to directly drive a LED in remote control applications.    |

| Num                  | ber                  | Name                         |                                                                                                  | D                |                  |                  |               |  |  |

|----------------------|----------------------|------------------------------|--------------------------------------------------------------------------------------------------|------------------|------------------|------------------|---------------|--|--|

| QFP64                | Die                  | Name                         |                                                                                                  | Desc             | ription          |                  |               |  |  |

| 46                   | 2                    | CA                           | Remote co                                                                                        | ntrol ca         | rrier ou         | tput             |               |  |  |

| 37                   | 59                   | RES                          | Reset inp                                                                                        | ut. Inte         | rnal pul         | l-up res         | istor         |  |  |

| 34<br>33<br>32<br>31 | 56<br>55<br>54<br>53 | COM1<br>COM2<br>COM3<br>COM4 | LCD commo<br>required<br>are indic                                                               | for the          | various          | operatin         | g modes       |  |  |

| 31                   | 00                   | COM4                         | ,                                                                                                | ty               |                  |                  |               |  |  |

|                      |                      |                              | Pin                                                                                              | Static<br>(64Hz) | 1/2<br>(32Hz)    | 1/3<br>(42Hz)    | 1/4<br>(32Hz) |  |  |

|                      |                      |                              | COM1<br>COM2<br>COM3<br>COM4                                                                     | O<br>×<br>×<br>× | 0<br>0<br>×<br>× | 0<br>0<br>0<br>× | 0000          |  |  |

| 1 to 15              | 23 to 37             | SEG1 to<br>SEG15             | LCD segme                                                                                        | nt drive         | r output         | s                |               |  |  |

| 16 to 30             | 38 to 52             | SEG16 to<br>SEG30            | P-channel open-drain outputs. Configurable as either LCD segment drivers or normal output ports. |                  |                  |                  |               |  |  |

|                      | 3                    | TECT                         | Test inputs. Leave open for normal                                                               |                  |                  |                  |               |  |  |

|                      | 4                    | TEST                         | operation                                                                                        | l <b>.</b>       |                  |                  |               |  |  |

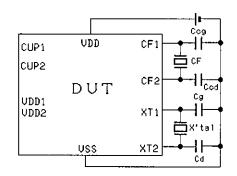

#### Supply connections

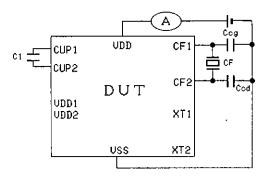

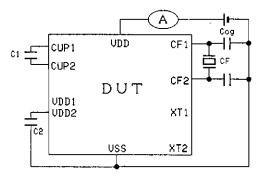

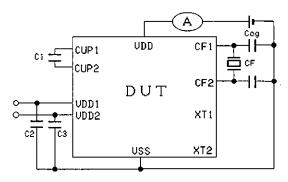

Figure 1. Supply Connections

#### SPECIFICATIONS

#### Absolute Maximum Ratings

| Parameter                                  | Symbol           | Rating                       | Unit |

|--------------------------------------------|------------------|------------------------------|------|

|                                            | V <sub>DD</sub>  | -0.3 to 7.0                  | v    |

| Supply voltage range                       | V <sub>DD1</sub> | -0.3 to V <sub>DD</sub>      | v    |

|                                            | V <sub>DD2</sub> | -0.3 to V <sub>DD</sub>      | v    |

| Input voltage range                        | V <sub>1</sub>   | -0.3 to V <sub>DD</sub> +0.3 | v    |

| Output voltage range                       | Vo               | -0.3 to V <sub>DD</sub> +0.3 | v    |

| CA output current                          | Ioi              | 25                           | m A  |

| Ports PO and P1 output current             | Ι 02             | 0. 5                         | m A  |

| Port P2 output current                     | I 03             | 10                           | m A  |

| Output current for all other ports         | I 04             | 0. 5                         | mA   |

| Total output current of all pins except CA | Ios              | 25                           | mA   |

| Operating temperature range                | Topr             | -30 to 70                    | လ    |

| Storage temperature range                  | Tstg             | -40 to 125                   | ဇ    |

# Recommended Operating Conditions Vss = 0 V, Ta= 25 $^{\circ}\mathrm{C}$

| Parameter            | Symbol          | Rating       | Unit |

|----------------------|-----------------|--------------|------|

| Supply voltage       | V <sub>DD</sub> | 3            | v    |

| Supply voltage range | V <sub>DD</sub> | 2. 3 to 6. 0 | v    |

## Electrical Characteristics Vss = 0 V, Ta= -30 to 70 °C

| D                 | C-1-1  |                                                                                                                                     |         |     | Unit |     |      |  |

|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|-----|------|--|

| Parameter         | Symbol | Condition                                                                                                                           | VDD (V) | min | typ  | max |      |  |

|                   |        | f = 32.768 kHz,<br>C1 = C2 = 0.1 $\mu$ F,<br>C <sub>G</sub> = C <sub>D</sub> = 20 pF,<br>Ta $\leq$ 50 °C, osci-                     |         | -   | 7    | 30  |      |  |

|                   | I DD ( | llator stopped. See note 3.                                                                                                         | 5. 0    | -   | 15   | 50  | - μΑ |  |

| Operating Current |        | f = 455 kHz,<br>$C1 = C2 = 0.1 \mu F$ ,<br>$C_{CD} = C_{CG} = 150 pF$<br>, Ta $\leq$ 50 °C, osc-<br>illator stopped.<br>See note 4. | 3. 0    | İ   | 150  | 500 |      |  |

|                   |        |                                                                                                                                     | 5. 0    | _   | 400  | 500 |      |  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                | Comb a l           | C 1:4:                                                                                                                                          |         | II. i.e. |      |     |      |

|--------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|------|-----|------|

| rarameter                | Symbol             | Condition                                                                                                                                       | VDD (V) | min      | typ  | max | Unit |

|                          |                    | f = 32.768 kHz,<br>C1 = C2 = 0.1 $\mu$ F,<br>C <sub>G</sub> = C <sub>D</sub> = 20 pF,<br>Ta $\leq$ 50 °C, osci-                                 | 3. 0    | _        | 3    | 15  |      |

|                          | I DDH1             | llator stopped. See note 3.                                                                                                                     | 5. 0    | -        | 8    | 50  |      |

| HALT-mode supply Current |                    | f = 455 kHz,<br>C1 = C2 = 0.1 $\mu$ F,<br>$C_{\text{CD}}$ = $C_{\text{CG}}$ = 150 pF<br>, Ta $\leq$ 50 °C,<br>oscillator stopped<br>See note 4. | 3. 0    | -        | 80   | 500 | μΑ   |

| Current                  |                    |                                                                                                                                                 | 5. 0    | _        | 300  | 400 |      |

|                          | I <sub>оон</sub> 2 | f = 455 kHz,<br>oscillator stopped                                                                                                              | 5. 0    |          | 0. 1 | -   | μΑ   |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                                                   | Symbol           | Condition                                                             |                      | Rating |                     | Unit   |  |

|-------------------------------------------------------------|------------------|-----------------------------------------------------------------------|----------------------|--------|---------------------|--------|--|

| r di dille ter                                              | Symbol           | Condition                                                             | min                  | typ    | max                 | UIII E |  |

| Instruction execution time                                  |                  | $V_{\rm DD}$ = 2.3 to 6.0,<br>Ceramic resonator,<br>f = 455 kHz       | ı                    | 17. 6  | I                   |        |  |

|                                                             | t <sub>cyc</sub> | V <sub>DD</sub> = 2.3 to 6.0,<br>crystal oscillator<br>f = 32.768 kHz | 1                    | 122    | _                   | μS     |  |

| Ports S, M, PO, P1<br>and P2<br>LOW-level input<br>voltage  | VILI             | Ports PO, P1 and<br>P2 configured as<br>inputs                        | 0                    | _      | 0. 3V <sub>dd</sub> | V      |  |

| Ports S, M, PO, P1<br>and P2<br>HIGH-level input<br>voltage | V <sub>1H1</sub> | Ports PO, P1 and P2 configured as inputs                              | 0. 7V <sub>dd</sub>  | _      | $V_{	extsf{DD}}$    | V      |  |

| RES LOW-level input voltage                                 | V <sub>IL2</sub> |                                                                       | 0                    | -      | 0.25V <sub>DD</sub> | v      |  |

| RES HIGH-level input voltage                                | V <sub>1H2</sub> |                                                                       | 0. 75V <sub>dd</sub> | _      | · V <sub>DD</sub>   | V      |  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                                    | Symbol             | Condition                                                         |             |                               | Rating |                              | Unit |

|----------------------------------------------|--------------------|-------------------------------------------------------------------|-------------|-------------------------------|--------|------------------------------|------|

| Parameter                                    | SAIIDOT            | Condition                                                         | $V_{DD}(V)$ | min                           | typ    | max                          | Unit |

|                                              | Rii                | V <sub>IL</sub> = 0.4 V,<br>LOW-level hold<br>transistor ON.      | 2. 9        | 150                           | 300    | 1000                         | kΩ   |

| Ports S and M input impedance                | 1(1)               | See figure 2.                                                     | 5. 0        | 70                            | 200    | 600                          | N ba |

| Tiput impedance                              | R <sub>12</sub>    | V <sub>IL</sub> = 0.4 V,<br>LOW-level pull-<br>down transistor ON | 2. 9        | 60                            | 100    | 150                          | kΩ   |

|                                              | K <sub>12</sub>    | See figure 2.                                                     |             | 60                            | 100    | 150                          | K 52 |

| RES input imped-<br>ance                     | Ris                |                                                                   | 2. 9        | 10                            | -      | 300                          | kΩ   |

|                                              |                    |                                                                   | 5. 0        | 10                            | ı      | 300                          |      |

| <del></del>                                  | V <sub>OM1</sub>   | $I_{OL} = 0.4 \mu A,$ $I_{OH} = -0.4 \mu A,$ $1/3 \text{ bias}$   | 2. 9        | 2V <sub>DD</sub> /3<br>- 0.2  | 1      | 2V <sub>DD</sub> /3<br>+ 0.2 | V    |

| CEG1 A. CEGGO                                |                    | 1/3 blas                                                          | 5. 0        | 2V <sub>DD</sub> /3<br>- 0. 2 | 1      | 2V <sub>DD</sub> /3<br>+ 0.2 |      |

| SEG1 to SEG30<br>MID-level output<br>voltage | V <sub>ОМ1-1</sub> | See note 1.                                                       | 2. 9        | V <sub>DD</sub> /3<br>- 0.2   | **     | V <sub>DD</sub> /3<br>+ 0.2  | V    |

|                                              |                    |                                                                   | 5. 0        | V <sub>DD</sub> /3<br>- 0.2   |        | V <sub>DD</sub> /3<br>+ 0. 2 |      |

|                                              | v                  | $I_{OL} = 0.4 \mu A,$                                             | 2. 9        | _                             | ~      | 0. 2                         | v    |

|                                              | V <sub>OM1-2</sub> | See note 1.                                                       | 5. 0        | _                             | -      | 0. 2                         | - v  |

|                                              | V                  | $I_{OH} = -0.4 \mu A$ , See note 1.                               | 2. 9        | V <sub>DD</sub> =0. 2         | _      | _                            | u    |

| SEG1 to SEG30                                | V <sub>OH1</sub>   | oee note 1.                                                       | 5. 0        | V <sub>DD</sub> =0. 2         | -      | -                            | - v  |

| HIGH-level output<br>voltage                 | V                  | $I_{OH}$ = -45 $\mu$ A, See note 2.                               |             | V <sub>DD</sub> =0. 45        | -      | -                            | v    |

|                                              | V <sub>OH2</sub>   | $I_{OH}$ = -75 $\mu$ A,<br>See note 2.                            | 5. 0        | V <sub>DD</sub> -0. 75        | _      | _                            | , v  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| D-wt                                            | Complex 1          | Constitution                         | -                   |                               | Rating |                               | ** * . |  |

|-------------------------------------------------|--------------------|--------------------------------------|---------------------|-------------------------------|--------|-------------------------------|--------|--|

| Parameter                                       | Symbol             | Condition                            | V <sub>DD</sub> (V) | min                           | typ    | max                           | Unit   |  |

| SEG1 to SEG30                                   | т                  | $V_1 = V_{ss}$                       | 2. 9                | _                             | -      | 1                             |        |  |

| LOW-level leakage<br>current                    | ILLI               | See note 2.                          | 5. 0                | -                             | -      | 1                             | μΑ     |  |

| SEG1 to SEG30<br>HIGH-level leakage             | I <sub>LH1</sub>   | $V_1 = V_{DD}$ ,<br>See note 2.      | 2. 9                | -1                            | _      | _                             | 4      |  |

| current                                         | ±LH1               | See note 2.                          | 5. 0                | -1                            | _      | -                             | μΑ     |  |

| COM1 to COM4<br>LOW-level output                | VOLI               | $I_{OL} = 4 \mu A$                   | 2. 9                | _                             | _      | 0.2                           | V      |  |

| voltage                                         |                    |                                      | 5. 0                | ***                           | ~      | 0. 2                          |        |  |

|                                                 | V <sub>ОМ2-1</sub> | 1/2 bias                             | 2. 9                | V <sub>DD</sub> /2<br>- 0.2   | -      | V <sub>DD</sub> /2<br>+ 0.2   | V      |  |

|                                                 |                    |                                      | 5. 0                | V <sub>DD</sub> /2<br>- 0. 2  | _      | V <sub>DD</sub> /2<br>+ 0.2   |        |  |

| COM1 to COM4 MID-level output                   | V <sub>ом2-2</sub> | 1/3 bias,<br>I <sub>OH</sub> = -4 μA | 2. 9                | 2V <sub>DD</sub> /3<br>- 0.2  | _      | 2V <sub>DD</sub> /3<br>+ 0.2  | V      |  |

| voltage                                         |                    |                                      | 5. 0                | 2V <sub>DD</sub> /3<br>- 0. 2 | -      | 2V <sub>DD</sub> /3<br>+ 0. 2 |        |  |

|                                                 | V <sub>OM2-3</sub> | 1/3 bias,<br>I <sub>OL</sub> = -4 μA | 2. 9                | V <sub>DD</sub> /3<br>- 0.2   | -      | V <sub>DD</sub> /3<br>+ 0. 2  | V      |  |

|                                                 |                    |                                      | 5. 0                | V <sub>DD</sub> /3<br>- 0. 2  |        | V <sub>DD</sub> /3<br>+ 0.2   |        |  |

| COM1 to COM4                                    | V                  | I <sub>OL</sub> = -4 μA              | 2. 9                | V <sub>DD</sub> =0. 2         | _      |                               | 31     |  |

| HIGH-level output<br>voltage                    | V <sub>OH3</sub>   |                                      | 5. 0                | V <sub>DD</sub> =0. 2         | _      | _                             | V      |  |

| Ports PO and P1<br>HIGH-level output<br>voltage | V <sub>OH4</sub>   | $I_{OH} = -450 \ \mu \text{ A},$     | 2. 9                | V <sub>DD</sub> - 0. 45       | -      | _                             | V      |  |

| vortage                                         |                    | $I_{OH} = -500 \ \mu  A$             | 5. 0                | V <sub>DD</sub> - 0. 50       | -      | -                             |        |  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                            | Comb a 1           | C 4:4:                                |                     |                       | Rating |      | 11-:4 |  |

|--------------------------------------|--------------------|---------------------------------------|---------------------|-----------------------|--------|------|-------|--|

| rarameter                            | Symbol             | Condition                             | V <sub>DD</sub> (V) | min                   | typ    | шах  | Unit  |  |

| Ports PO and P1                      | T                  | $V_1 = V_{SS}$                        | 2. 9                | _                     | _      | 1    |       |  |

| LOW-level leakage<br>current         | ILL2               |                                       | 5. 0                | -                     | -      | 1    | μΑ    |  |

| Ports PO and P1                      | т                  | $V_1 = V_{DD},$                       | 2. 9                | -1                    | -      | -    |       |  |

| HIGH-LEVEL leakage<br>current        | І <sub>сн2</sub>   |                                       | 5. 0                | -1                    | _      | -    | μΑ    |  |

| Port P2 HIGH-level                   | V <sub>OH5</sub>   | I <sub>он</sub> = -1.0 mA,            | 2. 9                | V <sub>DD</sub> -0. 5 | -      |      | V     |  |

| output voltage                       |                    |                                       | 5. 0                | V <sub>DD</sub> -0.5  | -      | -    |       |  |

| Port P2 LOW-level<br>leakage current | ILL3               | $V_1 = V_{SS}$                        | 2. 9                | _                     | _      | 1    | μΑ    |  |

|                                      |                    |                                       | 5. 0                | _                     | -      | 1    |       |  |

| Port P2 HIGH-level                   | І <sub>ьнз</sub>   | $V_1 = V_{DD}$                        | 2.9                 | -1                    | -      | -    | μΑ    |  |

| leakage current                      |                    |                                       | 5. 0                | -1                    | _      | _    |       |  |

| CA LOW-level                         | I <sub>OL 1</sub>  | V <sub>OL</sub> = 0.9 V,              | 3. 0                | 2                     | 5      |      | mA    |  |

| output current                       |                    |                                       | 5. 0                | 2                     | 5      | _    |       |  |

| CA HIGH-level                        | I <sub>он1</sub>   | $V_{OH} = V_{DD} - 1.5 V,$            | 3. 0                | 6                     | 12     | _    | mA    |  |

| output current                       |                    | $V_{OH} = V_{DD} - 2.5 V,$            | 5. 0                | 10                    | 20     | _    |       |  |

| V                                    | 17                 | C1 =C2 = 0.1 $\mu$ F,                 | 3. 0                | 1. 3                  | 1. 5   | 1. 7 | **    |  |

| $V_{ m DD1}$ output voltage          | V <sub>DD1-1</sub> | f =32.768 kHz, 1/2 bias. See figure 3 | 5. 0                | 2. 4                  | 2. 5   | 2. 6 | V     |  |

| V <sub>DD1</sub> - V <sub>DD2</sub>  | ,,                 | C1 =C2 = 0.1 $\mu$ F,                 | 3. 0                | 1.8                   | 2. 0   | 2. 2 | v     |  |

| voltage<br>differential              | V <sub>DD1-2</sub> | f =32.768 kHz, 1/3 bias. See figure 4 | 5. 0                | 3. 1                  | 3. 33  | 3. 5 |       |  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                          | Symbol                                                                                                                              | Condi                                                                                                  | ition             |                     |      | Rating |      | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|--------|------|------|

| - Grane ter                        | Symbol .                                                                                                                            | condition                                                                                              |                   | V <sub>DD</sub> (V) | min  | typ    | max  | Onit |

| V <sub>DD2</sub> output            | V <sub>DD2</sub>                                                                                                                    | C1 =C2 = 0.1 $\mu$ F,<br>f =32.768 kHz, 1/3                                                            |                   | 3. 0                | 0.8  | 1. 0   | 1. 2 | - v  |

| voltage                            | 7 DD2                                                                                                                               |                                                                                                        | figure 4          | 5. 0                | 1. 4 | 1. 67  | 1.8  | V    |

| Power supply                       |                                                                                                                                     | ceramic<br>resona-<br>tor                                                                              | Ta = 25 ℃         | 3. 0                | _    | 0. 2   | 1    |      |

| leakage current                    | ILK                                                                                                                                 |                                                                                                        | 25 C              | 5. 0                | _    | 0. 2   | 1    |      |

| Tourage Current                    | T L K                                                                                                                               |                                                                                                        | Ta = 50 °C        | 3. 0                | _    | 1      | 5    | μΑ   |

|                                    |                                                                                                                                     |                                                                                                        |                   | 5. 0                | _    | 1      | 5    |      |

| Oscillator                         | V                                                                                                                                   | Crystal oscillator<br>, f = 32.768 kHz,<br>C <sub>G</sub> = C <sub>D</sub> = 20 pF,<br>See note 5.     |                   |                     | _    | _      | 2. 3 |      |

| start up vortage                   | V <sub>ST</sub>                                                                                                                     | Ceramic resonator,<br>f = 455 kHz,<br>$C_{\text{CD}} = C_{\text{CG}} = 150 \text{ pF},$<br>See note 5. |                   |                     | _    | -      | 2. 3 | V    |

| Oscillator sus-<br>taining voltage | Crystal osci, $f = 32.768$ $C_{c} = C_{D} = 20$ p See note 5.  Vsus  Ceramic reso $f = 455$ kHz, $C_{cD} = C_{cg} = 15$ See note 5. |                                                                                                        | 768 kHz,<br>0 pF, |                     | 2    | -      | _    |      |

|                                    |                                                                                                                                     |                                                                                                        | Hz,<br>150 pF,    |                     | 2    | _      | _    | V    |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

| Parameter                                                         | Symbol                                                                                               | Condition                                                                                                         |     | Unit    |     |      |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|--|

| rarameter                                                         | 39111001                                                                                             | Condition                                                                                                         | min | typ     | max | Onit |  |

| Oscillator                                                        | $V_{DD}$ = 2.3 V,<br>crystal oscilla<br>f = 32.768 kHz,<br>$C_{G}$ = $C_{D}$ = 20 pF,<br>See note 5. |                                                                                                                   | I   | -       | 5   | s    |  |

| start-up time                                                     | t <sub>s⊤</sub>                                                                                      | $V_{\rm DD}$ = 2 V,<br>ceramic resonator,<br>f = 455 kHz,<br>$C_{\rm CG}$ = $C_{\rm CD}$ = 150 pF.<br>See note 5. | -   | -       | 30  | ms   |  |

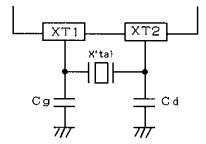

| Oscillator operat-                                                | fopg                                                                                                 | 32.768 kHz<br>crystal oscillator<br>See figure 12.                                                                | 32  | 32. 768 | 33  | kHz  |  |

| ing frequency<br>range                                            | Topg                                                                                                 | 455 kHz<br>ceramic resonator.<br>See figure 13.                                                                   | 380 | 455     | 500 | Kn2  |  |

| Crystal oscillator<br>external adjust-<br>ment capacitor<br>range | C <sub>D</sub>                                                                                       |                                                                                                                   | 16  | 20      | 24  | pF   |  |

- 1. Configured as LCD driver outputs.

- 2. Configured as p-channel open-drain outputs.

- 3. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 6, 7 and 8, respectively.

- 4. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 9, 10 and 11, respectively.

- 5. The measurement circuit for static drive, 1/2 or 1/3 bias is shown in figures 5, 3 and 4, respectively.

#### Measurement Circuits

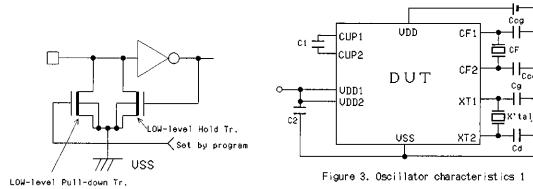

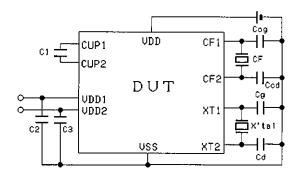

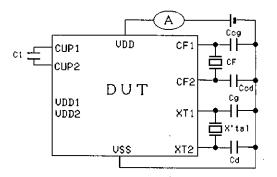

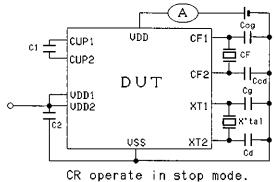

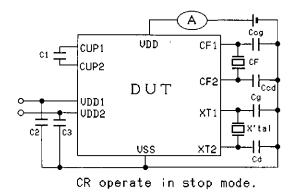

The following conditions apply to figures 3 to 5.

- Ports S and M have their hold transistors enabled.

- · Bidirectional ports are in output mode and are all HIGH.

- · LCD drivers are open-circuit.

- · RESis open-circuit and is connected to an internal resistor.

- · 32 kHz crystal oscillator frequency

- · 455 kHz ceramic oscillator frequency

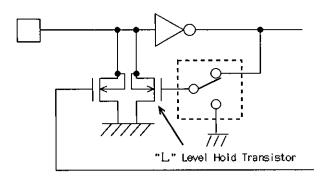

Figure 2. Input hold transistor

Figure 4. Oscillator characteristics 2

Figure 5. Oscillator characteristics 3

CR oscillator in stop mode.

Figure 6. Supply current measurement 1

Figure 7. Supply current measurement 2

Figure 8. Supply current measurement 3

Figure 9. Supply current measurement 4

Figure 10. Supply current measurement 5

Figure 11. Supply current measurement 6

Figure 12. Crystal oscillator connections

Figure 13. Ceramic oscillator connections

#### Recommended Oscillators

| Oscillator                       | Manufacturer | Part number | CG/CCG (pF) | CD/CCD(pF) |

|----------------------------------|--------------|-------------|-------------|------------|

| 32.768 kHz<br>crystal oscillator | V            | KF-38G      | 18          | 18         |

|                                  | Kyocera      | KF-38Y      | 16          | 16         |

|                                  | Daishinku    | DT-38       | 15          | 15         |

| 455 kHz ceramic                  | Kyocera      | KBR-455BK   | 150         | 150        |

| resonator                        | Murata       | CSB455E     | 150         | 150        |

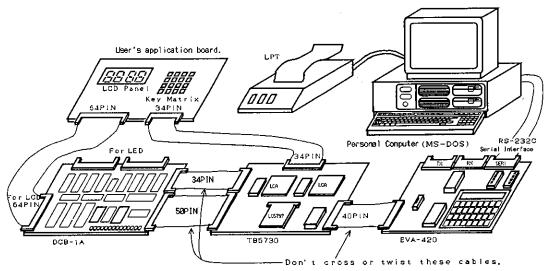

## DEVELOPMENT TOOLS Manuals

- · LC573400 Series User's Manual

- LC573400 Series Development Tools

#### Hardware/Software

Software development tools

- Personal computer (MS-DOS based)

- Cross assembler

LC573406 EXE (LC573406A)

LC573404 EXE (LC573404A)

- Mask option generator (SU573400. EXE)

#### Hardware development tools

- · LC5797 evaluation chip

- · LC5797 evaluation board (TB5730)

- EVA420 evaluation board containing the SCR-5730 monitor ROM

- DCB-1 display and mask option control board (Rev. 3.5)

- · User's application development board

- 1. The RAM capacity of the LC5797 is different to that of the LC573400 series. The LC5797 has a 256  $\times$  4-bit RAM whereas the LC573400 series has a 128  $\times$  4-bit RAM.

- 2. When developing software for the LC573400 series on the LC5797 evaluation chip, use only OH to 7H as values for DPH.

## LC573400 Series Development System

#### MASK OPTIONS

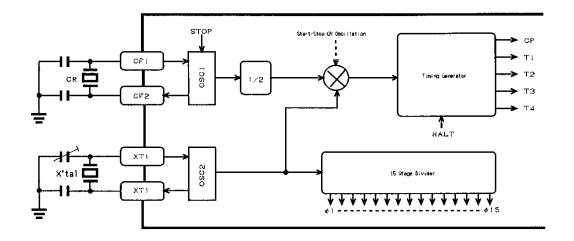

Combined ceramic resonator and crystal oscillator operation

The ceramic resonator and crystal oscillators can be combined in several ways as shown in figure 14.

Figure 14. Oscillator configuration 1

In this configuration, the microprocessor cycle time is eight times the ceramic resonator frequency. When the ceramic resonator oscillator is stopped with the CF command, the cycle time is four times the crystal oscillator frequency.

The divider outputs  $\phi$  1 to  $\phi$  15 are used to generate the LCD drive waveforms and timing pulses.

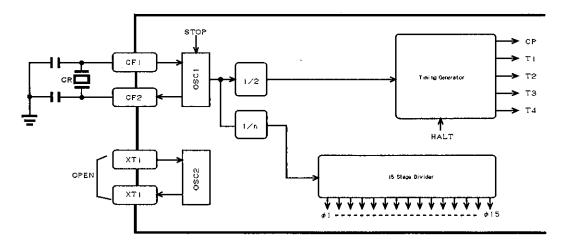

Ceramic resonator-only operation

In this configuration, the clock circuitry becomes as shown in figure 15.

Figure 15. Oscillator configuration 2

This configuration offers the same features as the combined oscillator option with the exception that stopping the ceramic resonator oscillator also stops program execution.

Input port LOW-level latching

Ports S and M have a LOW-level input latching transistor mask option as shown in figure 16.

Figure 16. Input latching transistors

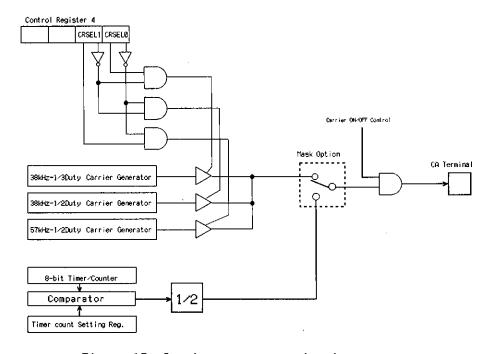

Remote control carrier generator

The remote control carrier generator circuitry is shown in figure 17.

Figure 17. Carrier generator circuit

The carrier waveform can be either software selectable from one of the three fixed waveforms 38 kHz with 1/3 duty, 38 kHz with 1/2 duty and 57 kHz with 1/2 duty-or programmable using the overflow from the 8-bit timer.

#### LCD drive method

Any drive method can be selected from the following list.

- 1. Static drive

- 2.1/2 bias, 1/2 duty

- 3.1/2 bias, 1/3 duty

- 4.1/2 bias, 1/4 duty

- 5.1/3 bias, 1/3 duty

- 6.1/3 bias, 1/4 duty

#### OPERATING INFORMATION

#### Reset

The LC573404A/LC573406A can be reset by taking  $\overline{\text{RES}}$  LOW or S1 to S4 HIGH. When the LC573404A/LC573406A is reset, the following take place.

- The pull-down resistors of ports S and M are enabled.

- · CA outputs a 38 kHz, ⅓ -duty signal.

- · All LCD segments and commons turn ON, and static drive is selected.

- · Segment outputs configured as normal p-channel open-drain outputs go HIGH

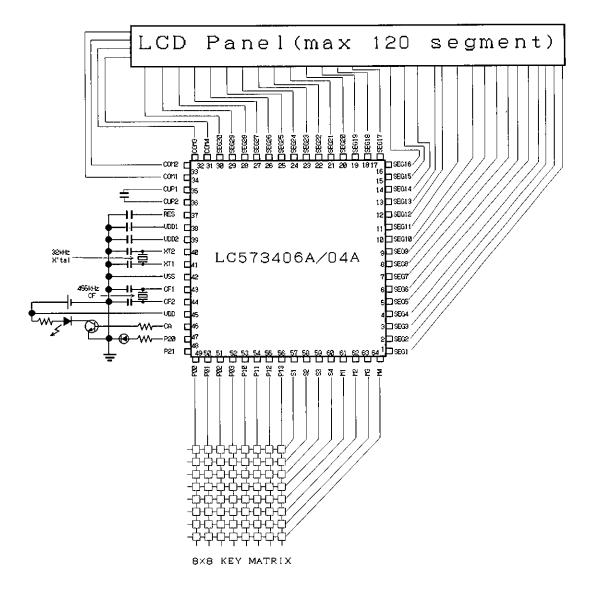

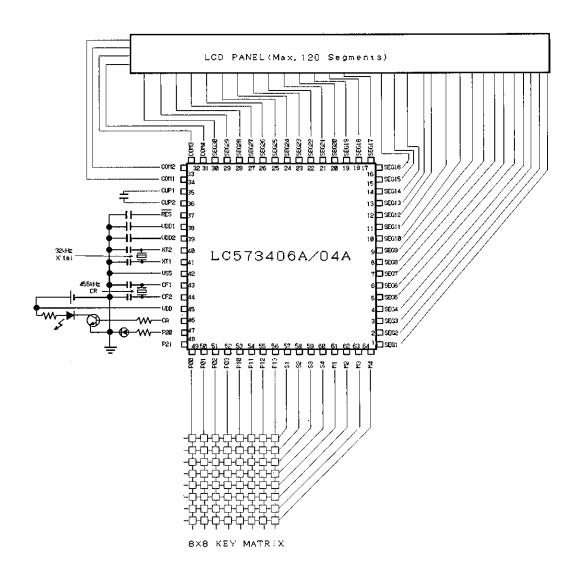

#### TYPICAL APPLICATION

#### INSTRUCTION SET

The instruction set uses the following abbreviations and symbols.

| AC:     | Accumulator                               | ACn:             | Accumulator bit n                           |

|---------|-------------------------------------------|------------------|---------------------------------------------|

| CF:     | Carry flag                                | DP :             | Data pointer                                |

| DPL:    | Data pointer low nibble                   | DPH:             | Data pointer high nibble                    |

| EDP:    | Data pointer save register                | EDPL:            | Data pointer save register low nibble       |

| EDPH:   | Data pointer save register high nibble    | SP:              | Strobe pointer                              |

| TREG:   | Temporary register                        | SCFn:            | Start condition flag n                      |

| CTLn:   | Control register n                        | L(SP):           | LCD latch specified by SP                   |

| HEFn:   | HALT cancel inhibit flag n                | ROM:             | ROM data                                    |

| CFCN:   | Ceramic resonator oscillator control flag | M:               | Memory                                      |

| M (DP): | Memory addressed by DP                    | [M(DP)]          | :Contents of memory addressed by DP         |

| PC:     | Program counter                           | PCn:             | Program counter bit n                       |

| PAGE:   | Page latch                                | STSn:            | Status register n                           |

| [P()]   | :Contents of port n                       | χ:               | Immediate data                              |

| Xn:     | Immediate data bit n                      | PDF:             | Input port pull-down flag                   |

| SFR:    | Special function register                 | (SFR):           | Contents of special function register       |

| CSTF:   | Chrono start flag.                        | SPC:             | Strobe pointer control bit                  |

| CCF:    | Carrier output control flag               | ():              | Contents                                    |

| [ ]:    | Contents                                  | <del>( )</del> : | Complement of contents                      |

| [ ]:    | Complement of contents                    | φn:              | Output from stage n of the 15-stage divider |

| +:      | Logical OR                                | +:               | Logical exclusive-OR                        |

| ٠:      | Logical AND                               | <del></del> ;    | Transfer direction or result                |

|         |                                           |                  |                                             |

The special function registers are abbreviated as follows.

TCON: THIGH:

P2:

Timer control register Timer counter register high byte TLOW:

Timer/counter register low byte

PO: Po:

Port P0 Port P2 CTL4: P1: Control register 4

l: Port Pl

| Mnemo-<br>nic | Instruction code                                                               | Operation                                                                                     | B<br>y<br>t<br>e<br>s | C<br>y<br>c<br>l<br>e<br>s | Description                                                                                                                            | Flags |

|---------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

|               | Accumulator                                                                    |                                                                                               |                       |                            |                                                                                                                                        |       |

| TAAT          | 0000 0001                                                                      | AC, TREG←ROM                                                                                  | 1                     | 2                          | Transfers the data from the memory location in the current page, pointed to by the lower 8 bits of PC, to the accumulator and to TREG. | :     |

| MTR           | 0001 0010                                                                      | 1 0 0 1 0 M(DP)←TREG 1 1 Stores the contents of TREG in the memory location pointed to by DP. |                       |                            |                                                                                                                                        |       |

| ASR0          | 0 0 0 1 1 0 0 0                                                                | AC <sub>a</sub> ←AC <sub>a+1</sub> , AC <sub>3</sub> ←0                                       | 1                     | l                          | Shifts the contents of the accumulator right and enters 0 into the msb.                                                                |       |

| ASR1          | 0001 1001                                                                      | $AC_0 \leftarrow AC_{n+1}, AC_0 \leftarrow 1$                                                 | 1                     | 1                          | Shifts the contents of the accumulator right and enters 1 into the msb.                                                                |       |

| ASL0          | 0001 1010                                                                      | $AC_n \leftarrow AC_{n-1}, AC_0 \leftarrow 0$                                                 | 1                     | 1                          | Shifts the contents of the accumulator left and enters 0 into the 1sb.                                                                 |       |

| ASL1          | 0 0 0 1 1 0 1 1                                                                | $AC_n \leftarrow AC_{n-1}, AC_0 \leftarrow 1$                                                 | 1                     | 1                          | Shifts the contents of the accumulator left and enters 1 into the lsb.                                                                 |       |

| INC           | 1001 1000                                                                      | AC, M (DP) ←M (DP) +1                                                                         | 1                     | 1                          | Increments the contents of M(DP) and stores it in the accumulator and in M(DP).                                                        |       |

| DEC           | 1001 1001                                                                      | AC, M (DP) ←M (DP) -1                                                                         | i                     | 1                          | Decrements the contents of M(DP) and stores it in the accumulator and in M(DP).                                                        |       |

|               | Arithmetic                                                                     |                                                                                               |                       |                            |                                                                                                                                        | ·     |

| ADC           | 1000 0000                                                                      | AC← (AC)+[M (DP)]+CF                                                                          | 1                     | 1                          | Adds the contents of the accumulator to M(DP) with carry and stores the result in the accumulator.                                     | CF    |

| ADC*          | 1000 1000                                                                      | AC, M (DP) (AC) +[M (DP) ]+CF                                                                 | 1                     | 1                          | Adds the contents of the accumulator to M(DP) with carry and stores the result in the accumulator and M(DP).                           | CF    |

| ADCI X        | 1 0 0 1 0 0 0 0<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) +X+CF                                                                                | 2                     | 2                          | Adds the contents of the accumulator to the immediate data with carry and stores the result in the accumulator.                        | CF    |

|               |                                                                                | ,                               |                       |                            |                                                                                                                                                    |       |

|---------------|--------------------------------------------------------------------------------|---------------------------------|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Mnemo-<br>nic | Instruction code                                                               | Operation                       | B<br>y<br>t<br>e<br>s | C<br>y<br>c<br>l<br>e<br>s | Description                                                                                                                                        | Flags |

| SBC           | 1000 0001                                                                      | AC (AC) + [M (DP)]+CF           | 1                     | 1                          | Subtracts the contents of M(DP) from the accumulator with carry and stores the result in the accumulator.                                          | CF    |

| SBC*          | 1000 1001                                                                      | AC, M (DP) ← (AC) + [M (DP)]+CF | 1                     | 1                          | Subtracts the contents of M(DP) from the accumulator with carry and stores the result in the accumulator and M(DP).                                | CF    |

| SBCI X        | 1 0 0 1 0 0 0 1<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC)+X+CF                   | 2                     | 2                          | Subtracts the immediate data from the accumulator with carry and stores the result in the accumulator.                                             | CF    |

| ADD           | 1000 0010                                                                      | AC← (AC)+[M (DP)]               | l                     | 1                          | Adds the contents of the accumulator to the contents of M(DP) and stores the result in the accumulator.                                            | CF    |

| ADD*          | 1000 1010                                                                      | AC, M (DP) ← (AC) + [M (DP)]    | ì                     | 1                          | Adds the contents of the accumulator to the contents of M(DP) and stores the result in the accumulator and M(DP).                                  | CF    |

| ADDI X        | 1 0 0 1 0 0 1 0<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) +X                     | 2                     | 2                          | Adds the contents of the accumulator to the immediate data and stores the result in the accumulator.                                               | CF    |

| SUB           | 1000 0011                                                                      | AC← (AC) + [M (DP)]+1           | 1                     | 1                          | Subtracts the contents of M(DP) from the accumulator and stores the result in the accumulator.                                                     | CF    |

| SBC*          | 1000 1011                                                                      | AC, M (DP) ← (AC) + [M (DP) ]+1 | 1                     | 1                          | Subtracts the contents of M(DP) from the accumulator and stores the result in the accumulator and M(DP).                                           | CF    |

| SBCI X        | 1 0 0 1 0 0 1 1<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) +X+1                   | 2                     | 2                          | Subtracts the immediate data from the accumulator and stores the result in the accumulator.                                                        | CF    |

| ADN           | 1000 0100                                                                      | AC← (AC)+[M (DP) ]              | 1                     | 1                          | Adds the contents of the accumulator to the contents of M(DP) and stores the result in the accumulator.                                            |       |

| ADN*          | 1000 1100                                                                      | AC, M (DP) ← (AC) + [M (DP)]    | 1                     | 1                          | Adds the contents of the accumulator to the contents of M(DP) and stores the result in the accumulator and M(DP).                                  |       |

| ADNI X        | 1 0 0 1 0 1 0 0<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) +X                     | 2                     | 2                          | Adds the contents of the accumulator to the immediate data and stores the result in the accumulator.                                               |       |

|               | Logical                                                                        | ·                               | <del></del>           | •                          |                                                                                                                                                    | ***** |

| AND           | 1000 0101                                                                      | AC←(AC) / [M (DP)]              | I                     | 1                          | Takes the logical AND of the contents of the accumulator and the contents of M(DP) and stores the result in the accumulator.                       |       |

| AND*          | 1000 1101                                                                      | AC, M (DP) ← (AC) / [M (DP) ]   | 1                     | 1                          | Takes the logical AND of the contents of the accumulator and the contents of M(DP) and stores the result in the accumulator and in M(DP).          |       |

| ANDI X        | 1 0 0 1 0 1 0 1<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) ∧X                     | 2                     | 2                          | Takes the logical AND of the contents of the accumulator and the immediate data and stores the result in the accumulator.                          |       |

| EOR           | 1000 0110                                                                      | AC← (AC) ~ [M (DP)]             | 1                     | 1                          | Takes the logical exclusive-OR of the contents of the accumulator and the contents of M(DP) and stores the result in the accumulator.              |       |

| EOR*          | 1000 1110                                                                      | AC, M (DP) ← (AC) → [M (DP)]    | 1                     | 1                          | Takes the logical exclusive-OR of the contents of the accumulator and the contents of M(DP) and stores the result in the accumulator and in M(DP). |       |

| EORI X        | 1 0 0 1 0 1 1 0<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) ⇔X                     | 2                     | 2                          | Takes the logical exclusive-OR of the contents of the accumulator and the immediate data and stores the result in the accumulator.                 |       |

| OR            | 1000 0111                                                                      | AC← (AC) √[M (DP) ]             | . 1                   | 1                          | Takes the logical OR of the contents of M(DP) and the accumulator and stores the result in the accumulator.                                        |       |

| OR*           | 1000 1111                                                                      | AC, M (DP) ← (AC) √[M (DP)]     | 1                     | 1                          | Takes the logical OR of the contents of M(DP) and the accumulator and stores the result in the accumulator and in M(DP).                           |       |

| ORI X         | 1 0 0 1 0 1 1 1<br>X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC← (AC) ∨X                     | 2                     | 2                          | Takes the logical OR of the contents of the accumulator and the immediate data and stores the result in the accumulator.                           |       |

| Mnemo-<br>nic | Instructuion code                                                   | Operation         | B<br>y<br>t<br>e<br>s | C<br>y<br>c<br>l<br>e<br>s | Description                                                               | Flags  |

|---------------|---------------------------------------------------------------------|-------------------|-----------------------|----------------------------|---------------------------------------------------------------------------|--------|

| . :           | Data pointer                                                        |                   |                       |                            |                                                                           |        |

| SDPL          | 0001 1100                                                           | DPL← (AC)         | 1                     | l                          | Stores the contents of the accumulator in DPL.                            |        |

| SDPH          | 0 0 0 1 1 1 0 1                                                     | DPH← (AC)         | 1                     | 1                          | Stores the contents of the accumulator in DPH.                            |        |

| LDPL          | 1111 1101                                                           | AC← (DPL)         | l                     | 1                          | Loads the contents of DPL into the accumulator.                           |        |

| LDPH          | 1111 1110                                                           | AC← (DPH)         | 1                     | 1                          | Loads the contents of DPH into the accumulator.                           |        |

| MOPL X        | 1 0 I 1 X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | DPL←X             | ì                     | 1                          | Stores the immediate data in DPL.                                         |        |

| MDPH X        | 1 1 0 0 X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | DPH←X             | l                     | l                          | Stores the immediate data in DPH.                                         |        |

| EDPL          | 0001 1110                                                           | (DPL) ←→ (EDPL)   | 1                     | 1                          | Swaps the contents of DPL and EDPL.                                       |        |

| EDPH          | 0001 1111                                                           | (DPH) ←→ (EDPH)   | 1                     | ì                          | Swaps the contents of DPH and EDPH.                                       |        |

| IDPL          | 1001 1010                                                           | DPL← (DPL)+1      | 1                     | 1                          | Increments the contents of DPL and stores the result in DPL.              |        |

| IDPH          | 1001 1100                                                           | DPH← (DPH) +1     | 1                     | 1                          | Increments the contents of DPH and stores the result in DPH.              |        |

| DDPL          | 1001 1011                                                           | DPL←(DPL)-1       | 1                     | 1                          | Decrements the contents of DPL and stores the result in DPL.              |        |

| DDPH          | 1001 1101                                                           | DPH← (DPH) -1     | 1                     | 1                          | Decrements the contents of DPH and stores the result in DPH.              |        |

| SSP           | 1010 1110                                                           | SP←(AC)           | l                     | 1                          | Stores the contents of the accumulator in SP.                             |        |

| LSP           | 1010 1010                                                           | AC←(SP)           | 1                     | ı                          | Loads the contents of SP into the accumulator.                            |        |

| MSP X         | 1 1 1 0 X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | SP←X              | 1                     | 1                          | Stores the immediate data in SP.                                          |        |

| ISP           | 1001 1110                                                           | SP← (SP)+1        | 1                     | 1                          | Increments the contents of SP and stores the result in SP.                |        |

| DSP           | 1001 1111                                                           | SP← (SP) -1       | 1                     | 1                          | Decrements the contents of SP and stores the result in SP.                |        |

|               | Flag                                                                | •                 |                       | -                          |                                                                           |        |

| LHILT         | 1010 1011                                                           | AC←(STS2), STS2←0 | 1                     | 1                          | Loads the contents of STS2 into the accumulator and clears STS2.          | SCF1∼4 |

| L500          | 1010 1100                                                           | AC←(STS1), SCF0←0 | 1                     | 1                          | Loads the contents of STS1 into the accumulator and clears SCF0.          | SCF0   |

| CSP           | 0000 0100                                                           | CSTF←0            | 1                     | 1                          | Clears CSTF.                                                              | CSTF   |

| CST           | 0000 0101                                                           | CSTF←1            | 1                     | 1                          | Sets CSTP.                                                                | CSTF   |

| RC5           | 0000 0110                                                           | HEF0←0            | 1                     | 1                          | Clears HEFO to prevent HALT-mode cancellation when the divider overflows. | HEFO   |

| SC5           | 0000 0111                                                           | HEF0←1            | 1                     | 1                          | Sets HEFO to enable HALT-mode cancellation when the divider overflows.    | HEF0   |

| RCF           | 1111 0000                                                           | CF←0              | 1                     | 1                          | Clears CF.                                                                | CF     |

| SCF           | 1111 0001                                                           | CF←1              | 1                     | 1                          | Sets CF.                                                                  | CF     |

|               | Data transfer                                                       | -                 | •                     | •                          |                                                                           |        |

| LDA           | 1010 1001                                                           | AC←[M (DP)]       | l                     | 1                          | Loads the contents of M(DP) into the accumulator.                         |        |

| STA           | 1010 1100                                                           | M (DP) ← (AC)     | 1                     | 1                          | Stores the contents of the accumulator in M(DP).                          | CF     |

| LDI X         | 0 0 1 1 X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | AC←X              | l                     | 1                          | Loads the immediate data into the accumulator.                            |        |

| MVI X         | 0 0 1 0 X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | M (DP) ← X        | 1                     | 1                          | Loads the immediate data into M(DP).                                      |        |

| of the SIC X and SC5 commands.  Stores the immediate data in CTL2. The function code control the HALT must make bits, X0 to X2 to This bit sets HEF1, cancell HALT mode with the divider of the HALT mode with a rising edge to the HALT mode with the 10 Hz time.  NOP 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The lower 4 bits of the code cancellation.  3, are described below.  ing overflow signal.  ing e on port S.  ing ming pulse.  the accumulator.  The accumulator.  DF controls the ts S and M. |