**CMOSIC**

LC58E76

On-Chip EPROM Microcomputer

4-Bit Single Chip Microprocessor with LCD Driver,

12 Kbytes of EPROM and 1 Kbit of RAM On-Chip

## **Preliminary**

### Overview

The LC58E76 is an on-chip EPROM microcontroller in the LC587X series of CMOS 4-bit single chip microcontrollers.

The LC58E76 provides the same functionality as the LC5876 mask ROM version, and has the same pin layout. The LC58E76 has a 16-kbyte EPROM capacity, and corresponds to the LC5872, LC5873, LC58E74 and LC5876.

The LC58E76 is provided in an 80-pin ceramic window package, and programs can be written and erased repeatedly. Thus it is optimal for use during program development.

## **Applications**

The LC58E76 can be used for program and function evaluation in the following applications.

- System control of consumer products that use LCD displays, such as cameras, CD players and tuners

- Remote controllers for products such as VCRs or tuners

- System control of instruments that use LCD displays, such as miniature test equipment and medical equipment.

- The LC58E76 is optimal for products that use LCD displays, in particular, battery operated products.

#### **Features**

• Optional functions can be switched by EPROM data

The LC58E76 includes both program and option selection EPROM on-chip. The option selection EPROM can be used to specify almost all of the LC587X options, including crystal/ceramic oscillator specifications, port hold transistor selection and segment PLA specifications. These option specifications allow functional and operational testing in the actual PC board used in the mass-produced end product.

- On-chip 16 kbyte program EPROM

The on-chip 16 kbyte program EPROM allows the LC58E76 to be used to evaluate all four members of the

- LC58E76 to be used to evaluate all four members of the LC587X series. (See the series structure table on the next page.)

- Program and option data read/write

The program and option data can be read and written with a standard commercial EPROM writer by using a dedicated EPROM writing board. (256K equivalent)

(Either a Sanyo or an Advanced EPROM writer should be used.)

- Pin correspondence

The LC58E76 is pin compatible with the mask ROM versions. (There is no chip correspondence.)

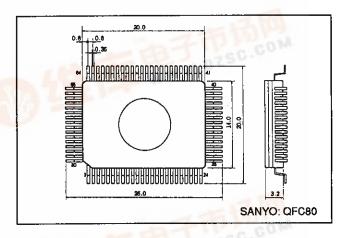

## **Package Dimensions**

unit: mm

3152A-QFC80

#### **Series Structure**

| Type No.     | LC5872                | LC5873                | LC5874                | LC5876                | LC58E76                                                     |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------------------------------------------------|

| ROM capacity | 2 k × 16 bits         | 3 k × 16 bits         | 4 k × 16 bits         | 6 k × 16 bits         | EPROM: 16 kbytes                                            |

| RAM capacity | 256 x 4 bits          | 256 × 4 bits          | 256× 4 bits           | 256 × 4 bits          | 256 x 4 bits                                                |

| Package      | QIP80                 | QIP80                 | QIP80                 | QIP80                 | QFC80 ceramic window package                                |

| Notes        | Available in quantity | Available in quantity | Available In quantity | Available in quantity | The on-chip EPROM window version will be available shortly. |

#### **Usage Notes**

The LC58E76 is designed for use in developing and evaluating programs for the microprocessors in the LC587X series. However, there are differences between the LC58E76 and the mask ROM versions. Keep the following points in mind when using the LC58E76.

#### 1. Notes on Reset

When the RES pin input changes from high to low, the reset state is cleared after the prescribed oscillator stabilization period has elapsed. The options and the segment PLA are set up during the first 256 cycles following the clearing of the reset state. Instructions are executed starting at location 0 after this setup phase has completed. (The options are undefined and the segment outputs are held at the V<sub>SS</sub> level when the RES pin is high and during the first 256 cycles following the clearing of the reset state.)

- 2. Cover the LC58E76's window with an opaque seal when writing data to EPROM.

- 3. The LC58E76 and the mask ROM versions differ in the following points.

| Item                                                   | LC58E76                                                                                                                                                                       | Mask ROM versions (LC587X)                                                                                                                                                        | Note                                                                      |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Operating temperature                                  | 10 to 40°C                                                                                                                                                                    | −30 to 70°C                                                                                                                                                                       |                                                                           |  |

| Operating supply voltage                               | 2.8 to 5.5 V                                                                                                                                                                  | 2.0 to 6.0 V                                                                                                                                                                      |                                                                           |  |

| Operating supply currents                              | 5 μA typ. (3 V, 32 kHz crystal) 20 μA typ. (5 V, 32 kHz crystal) 400 μA typ. (5 V, 400 kHz ceramic) 500 μA typ. (5 V, 2 MHz ceramic) 700 μA typ. (5 V, 4 MHz ceramic)         | 4 μA typ. (3 V, 32 kHz crystal)<br>15 μA typ. (5 V, 32 kHz crystal)<br>400 μA typ. (5 V, 400 kHz ceramic)<br>500 μA typ. (5 V, 2 MHz ceramic)<br>700 μA typ. (5 V, 4 MHz ceramic) | Hold mode                                                                 |  |

| Common segment output states at reset                  | Segment pins: VSS level (CMOS output) Common pins: N-channel open drain                                                                                                       | Static operation<br>(LCD drive output)                                                                                                                                            |                                                                           |  |

| Segment output states after the reset state is cleared | Off state                                                                                                                                                                     | Off state/lit state                                                                                                                                                               |                                                                           |  |

| Oscillator circuit specifications                      | CF/Xtal/CF + Xtal                                                                                                                                                             | CF/Xtal/CF + Xtal<br>RC/RC+Xtal/EXT/EXT+Xtal                                                                                                                                      | Option switching in the                                                   |  |

| Crystal oscillator circuit                             | 32K/38K/65K (Note that this is 65K in the reset state)                                                                                                                        | 32K/38K/65K                                                                                                                                                                       | EPROM version is<br>performed by writing                                  |  |

| RES pin specifications                                 | Open (reset on high)                                                                                                                                                          | Open (reset on high) Open (reset on low) Pull-up (reset on low) Pull-down (reset on high)                                                                                         | data to the option<br>EPROM.  Option switching in<br>mask ROM versions is |  |

| N ports                                                | Open drain output                                                                                                                                                             | Open drain output/CMOS output                                                                                                                                                     | performed by specifying mask                                              |  |

| LCD drive specifications                               | Static 1/2 bias, 1/2 duty 1/2 bias, 1/3 duty 1/2 bias, 1/3 duty 1/3 bias, 1/4 duty 1/3 bias, 1/3 duty 1/3 bias, 1/4 duty (Substitute static when the LCD driver is not used.) | Static 1/2 bias, 1/2 duty 1/2 bias, 1/3 duty 1/2 bias, 1/3 duty 1/3 bias, 1/4 duty 1/3 bias, 1/3 duty 1/3 bias, 1/4 duty (Substitute static when the LCD driver is not used.)     | options.                                                                  |  |

| Number of specifiable strobes                          | 00 - 1E<br>However, 0E and 0F cannot be used with<br>the 4 MHz specifications.                                                                                                | 00 – 1E However, 0E and 0F cannot be used with the 4 MHz specifications.                                                                                                          |                                                                           |  |

Note: Although the strobes number 00 to 1E can be used with CF 2 MHz and lower specifications, strobes number 0E, 0F and 1E cannot be used with the CF 4 MHz specifications.

NT 4404 0 0 7

## Pin Assignments

| Pln No. | Symbol              | Pin No.  | Symbol                                 | Pin No.  | Symbol                | Pin No.  | Symbol         |

|---------|---------------------|----------|----------------------------------------|----------|-----------------------|----------|----------------|

| 1 2     | COM2<br>COM1        | 21<br>22 | V <sub>DD</sub> 2<br>V <sub>DD</sub> 1 | 41<br>42 | N3<br>N4 Output ports | 61<br>62 | Seg18<br>Seg19 |

| 3       | CUP1                | 23       | V <sub>SS</sub>                        | 43       | TST                   | 63       | Seg20          |

| 4       | CUP2                | 24       | V <sub>DD</sub>                        | 44       | Seg1                  | 64       | Seg21          |

| 5       | RES                 | 25       | CFIN                                   | 45       | Seg2                  | 65       | Seg22          |

| 6       | INT                 | 26       | CFOUT                                  | 46       | Seg3                  | 66       | Seg23          |

| 7       | SO1                 | 27       | S1                                     | 47       | Seg4                  | 67       | Seg24          |

| 8       | SO2 1/O, serial I/O | 28       | S2                                     | 48       | Seg5                  | 68       | Seg25          |

| 9       | SO3 ports           | 29       | S3 Input ports                         | 49       | Seg6                  | 69       | Seg26          |

| 10      | SO4丿                | 30       | ا ل S4                                 | 50       | Seg7                  | 70       | Seg27          |

| 11      | A1                  | 31       | K1                                     | 51       | Seg8                  | 71       | Seg28          |

| 12      | A2 I/O ports        | 32       | K2 I/O ports                           | 52       | Seg9                  | 72       | Seg29          |

| 13      | A3   "O ports       | 33       | K3 POPORS                              | 53       | Seg10                 | 73       | Seg30          |

| 14      | A4 J                | 34       | K4                                     | 54       | Seg11                 | 74       | Seg31          |

| 15      | P1                  | 35       | M1 )                                   | 55       | Seg12                 | 75       | Seg32          |

| 16      | P2 I/O ports        | 36       | M2 I/O ports                           | 56       | Seg13                 | 76       | Seg33          |

| 17      | P3 P3               | 37       | M3   "                                 | 57       | Seg14                 | 77       | Seg34          |

| 18      | P4 J                | 38       | M4 2                                   | 58       | Seg15                 | 78       | Seg35          |

| 19      | XTOUT               | 39       | N1 Output ports                        | 59       | Seg16                 | 79       | COM4           |

| 20      | XTIN                | 40       | N2 J Coupul ports                      | 60       | Seg17                 | 80       | СОМЗ           |

Note: 1. The TST pin must be connected to  $V_{\mbox{\scriptsize SS}}$  in normal operation.

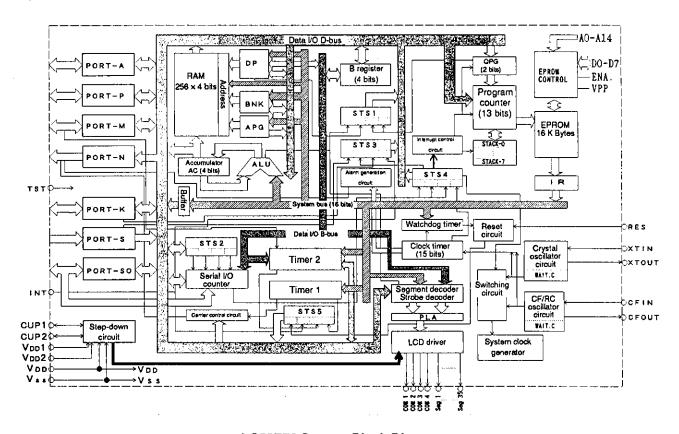

## System Block Diagram

### LC58E76 System Block Diagram

| RAM | : Data memory           | В    | : B register           | STS4   | : Status register 4      |

|-----|-------------------------|------|------------------------|--------|--------------------------|

| ROM | : Program memory        | OPG  | : ROM page flag        | STS5   | : Status register 5      |

| DP  | : Data pointer register | PC   | : Program counter      | PLA    | : Program logic for      |

| BNK | : Bank register         | IR   | : Instruction register |        | segment data and strobes |

| APG | : RAM page flag         | STS1 | : Status register 1    | WAIT.C | : Wait time counter      |

| AC  | · Accumulator           | STS2 | : Status register 2    |        |                          |

ALU : Arithmetic and logic unit STS3 : Status register 3

<sup>2.</sup> When mounting the LC58E76, do not use solder dip techniques.

## **Pin Functions**

| Pin                                    | VO               | QFC-80<br>Pin No.    | Function                                                                                                                                                                                                                                                                                               | Option                                                                                               | At reset                                                                                                                                              |

|----------------------------------------|------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub><br>V <sub>SS</sub>     | _                | 24<br>23             | Power supply                                                                                                                                                                                                                                                                                           |                                                                                                      |                                                                                                                                                       |

| 133                                    |                  |                      | LCD drive power supply                                                                                                                                                                                                                                                                                 |                                                                                                      |                                                                                                                                                       |

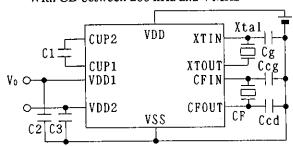

| V <sub>DD</sub> 1<br>V <sub>DD</sub> 2 | =                | 22<br>21             | NON 1/1 bias 1/2 bias 1/3 bias  VDD VDD1 VDD2 VSS                                                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                                                       |

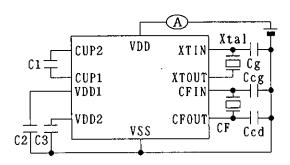

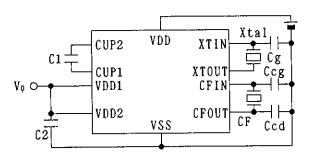

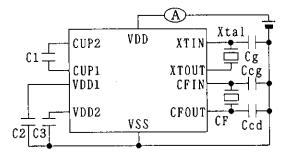

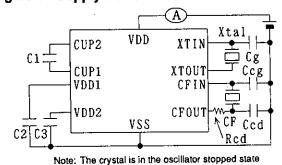

| CUP1<br>CUP2                           | _<br><del></del> | 3<br>4               | Switching pin used to supply the LCD drive voltage to the VDD1 and VDD2 pins  Connect a nonpolar capacitor between CUP1 and CUP2 when 1/2 or 1/3 bias is used.  Leave open when a bias other than 1/2 or 1/3 is used.                                                                                  |                                                                                                      |                                                                                                                                                       |

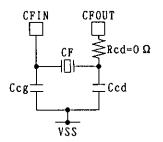

| CFIN                                   | Input            | 25                   | System clock oscillator connections  Ceramic resonator connection (CF specifications)  RC component connection (RC specifications)                                                                                                                                                                     | CF specifications                                                                                    |                                                                                                                                                       |

| CFOUT                                  | Output           | 26                   | <ul> <li>External signal input pin (CFOUT is left open)</li> <li>This oscillator is stopped by the execution of a STOP or SLOW instruction.</li> </ul>                                                                                                                                                 | Not used                                                                                             |                                                                                                                                                       |

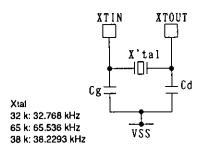

| XTIN                                   | Input            | 20                   | Reference calculation (clock specifications, LCD alternation frequency), system clock oscillator                                                                                                                                                                                                       | 32k specifications     65k specifications                                                            |                                                                                                                                                       |

| хтоит                                  | Output           | 19                   | <ul> <li>32 kHz crystal resonator connection</li> <li>65 kHz crystal resonator connection</li> <li>This oscillator is stopped by the execution of a STOP instruction.</li> </ul>                                                                                                                       | 38k specifications     Not used                                                                      |                                                                                                                                                       |

| S1<br>S2<br>S3<br>S4                   | Input            | 27<br>28<br>29<br>30 | Input-only ports Input pins used to read data into RAM Built-in 7.8 ms and 1.95 ms chatter exclusion circuits Built-in pull-up/pull-down resistors Note: The 7.8 ms and 1.95 ms times are the times when Ø0 is 32.768 kHz.                                                                             | Transistors to hold<br>a low or high level Selection of either<br>pull-up or pull-<br>down resistors | The pull-up or pull-down resistors are on. Note: These pins go to the floating state when reset is cleared.                                           |

| K1<br>K2<br>K3<br>K4                   | VO               | 31<br>32<br>33<br>34 | VO ports Input pins used to read data into RAM Output pins used to output data from RAM Built-in 7.8 ms and 1.95 ms input-mode chatter exclusion circuits. The selection of 7.8 or 1.95 ms is linked to that for the S ports.  Note: The 7.8 ms and 1.95 ms times are the times when ©0 is 32.768 kHz. | Transistors to hold a low or high level Selection of either pull-up or pull-down resistors           | The pull-up or pull-down resistors are on. Note: These pins go to the floating state when reset is cleared. Input mode Output latch data is set high. |

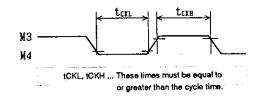

| M1<br>M2<br>M3<br>M4                   | vo               | 35<br>36<br>37<br>38 | I/O ports Input pins used to read data into RAM Output pins used to output data from RAM M4 is used as the external clock input pin in TM2 mode 3. The minimum period for the external clock is twice the cycle time. Built-in pull-up/pull-down resistors                                             | The same as K1 to K4                                                                                 | The same as K1 to<br>K4                                                                                                                               |

| A1<br>A2<br>A3<br>A4                   | I/O              | 11<br>12<br>13<br>14 | I/O ports Input pins used to read data into RAM Output pins used to output data from RAM Built-in pull-up/pull-down resistors                                                                                                                                                                          | The same as K1 to K4                                                                                 | The same as K1 to<br>K4                                                                                                                               |

| P1<br>P2<br>P3<br>P4                   | VO               | 15<br>16<br>17<br>18 | I/O ports Function: The same as pins A1 to A4                                                                                                                                                                                                                                                          | The same as K1 to<br>K4                                                                              | The same as K1 to<br>K4                                                                                                                               |

#### Continued from preceding page.

| Pin                       | 1/0    | OFC-80<br>Pin No.    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Option                                                                                                                                                                                                                                                                                                         | At reset                                                                                                                                                                                                                                                              |

|---------------------------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

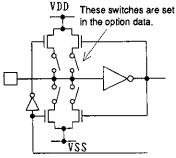

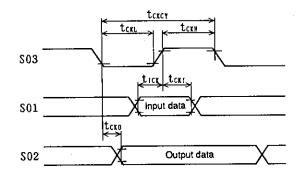

| SO1<br>SO2<br>SO3<br>SO4  | VO     | 7<br>8<br>9<br>10    | VO ports Function: The same as pins A1 to A4 Pins SO1 to SO3 area also used for the serial interface.  • Use of these pins in serial mode can be selected under program control.  • Pin functions: SO1: Serial input pin SO2: Serial output pin SO3: Serial clock pin The serial clock pin can be switched between internal and external, and between rising edge output and falling edge output.                                                                                                                                                                                                                                                                            | Transistors to hold a low or high level Selection of either pull-up or pull-down resistors Internal serial clock divisor selection 1 1/1 II 1/2 III 1/4                                                                                                                                                        | The same as K1 to K4                                                                                                                                                                                                                                                  |

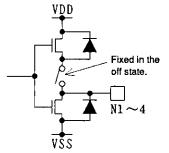

| N1<br>N2<br>N3<br>N4      | Output | 39<br>40<br>41<br>42 | Output-only ports  Output pins used to output data from RAM  An alarm signal can be output from pin N4. (Note that this is only when the N4 output latch is low.)  An alarm signal modulated at 1, 2 or 4 kHz can be output. (These frequencies are output when Ø0 is 32.768 kHz.)  A carrier signal can be output from N3. (Note that this is only when the N3 output latch is low.)                                                                                                                                                                                                                                                                                        | Pin N1 to N4 output circuit type: I N-channel open drain Pin N1 to N4 output level I High level II Low level                                                                                                                                                                                                   | The output levels on pins N1 to N4 can be specified as an option.                                                                                                                                                                                                     |

| INT                       | Input  | 6                    | Input ports  External interrupt request inputs  Input pins used to read data into RAM  Input detection can be performed on either rising or falling edges.  Built-in pull-up/pull-down resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transistors to hold a low or high level Selection of either pull-up or pull-down resistors Signal conversion (rising/falling) selection                                                                                                                                                                        |                                                                                                                                                                                                                                                                       |

| RES                       | Input  | 5                    | LSI reset input  The LC58E7008 resets on a high level input Note: • An external resistor is required.  The reset pulse must be at least 200 μs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Only when the input resistor open specification is selected.                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                       |

| TST                       | Input  | 43                   | Test input Connect to V <sub>SS</sub> in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                       |

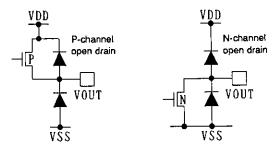

| Seg1,<br>Seg2 to<br>Seg35 | Output | 44,<br>45 to<br>78   | LCD panel drive/general-purpose output  LCD panel drive I STATIC II 1/2 bias = 1/2 duty III 1/2 bias = 1/3 duty IV 1/2 bias = 1/3 duty V 1/3 bias = 1/4 duty V 1/3 bias = 1/4 duty Types I to V can be specified as mask options.  General-purpose output mode I CMOS II P-channel open drain III N-channel open drain Types I to III can be specified as mask options.  LCD/general-purpose output control is handled by the segment PLA, and thus program control is not required.  These pins support output latch control on reset and in standby states when the oscillators are stopped.  Arbitrary combinations of LCD drive and general-purpose outputs can be used. | LCD driver/ general-purpose output switching LCD drive type switching STATIC 1/2 bias - 1/2 duty 1/2 bias - 1/4 duty 1/3 bias - 1/4 duty 1/3 bias - 1/4 duty 1/3 bias - 1/4 duty General-purpose output circuit switching CMOS P-chennel open drain N-channel open drain Output latch control in standby modes | LCD drive     All segments off     General-purpose outputs     Low level     Note: When a combination of LCD drive and general-purpose outputs, the output state is either all segments off or low level.     These pins go to the VSS level during the reset period. |

#### Continued from preceding page.

| Pin          | 1/0    | QFC-80<br>Pin No. |                       |                           | Function                        | Option          | At reset        |  |                                       |

|--------------|--------|-------------------|-----------------------|---------------------------|---------------------------------|-----------------|-----------------|--|---------------------------------------|

|              |        |                   | The table belo        | for alternation<br>or ø0) | these pins are<br>frequency ref | ect a typical s |                 |  |                                       |

| COM1         |        | 2                 |                       | Static duty               | 1/2 duty                        | 1/3 duty        | 1/4 duty        |  | These pins are n-                     |

| COM2<br>COM3 | Output | 1<br>80           | COM1<br>COM2          | O<br>X                    | 0                               | 0               | 0               |  | channel open-drain outputs during the |

| COM3         |        | 79                | COMB                  | Î                         | ×                               | ŏ               | l ŏ II          |  | reset period.                         |

| 1            |        | '`                | COM4                  | ×                         | ×                               | ×               | ō               |  |                                       |

|              |        |                   | Alternation frequency | 32 Hz                     | 32 Hz                           | 42.7 Hz         | 32 Hz           |  |                                       |

|              |        |                   | Note: A cross         | (×) Indicates             | that the pin is                 | not used with   | that duty type. |  |                                       |

#### **Usage Notes**

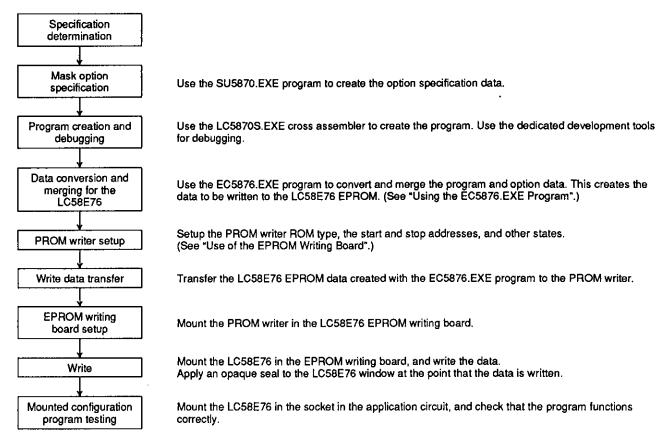

The following tools and software are required when the LC58E76 is used.

The LC5870 Series Software Development Tools: For creating programs and option data.

Note that only MS-DOS machines are supported as the development host machine. See the LC5870 Series Software Development Tools manuals for details on the use of these tools.

EC5876.EXE: This is a program that converts and merges program and option data for the LC5870 series so that it can be written to the LC58E76 EPROM.

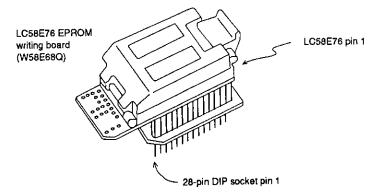

EPROM writing board (adapter socket: W58E68Q): This is a socket adapter that allows a general-purpose PROM writer to be used to write program data to the LC58E76.

General-purpose PROM writer: The EVA-520 programmer that comes with the LC5870 Series Software Development Tools cannot be used. A general-purpose PROM writer must be used.

This section describes the procedures used with the LC58E76 and the EC5876.EXE program, which is one of the tools mentioned above. More details on LC5870 Series program development are available in LC5870 Series Users Manual and the manuals for the LC5870 Series Development Tools and the general-purpose PROM writer.

Note: There are differences in function and characteristics between the LC58E76 and the LC5870 series mask ROM versions. Be sure to take these differences into account when testing the programmed LC58E76. See the "Usage Notes" section for details on the differences.

#### 2. Using the EC5876.EXE Program (Operation)

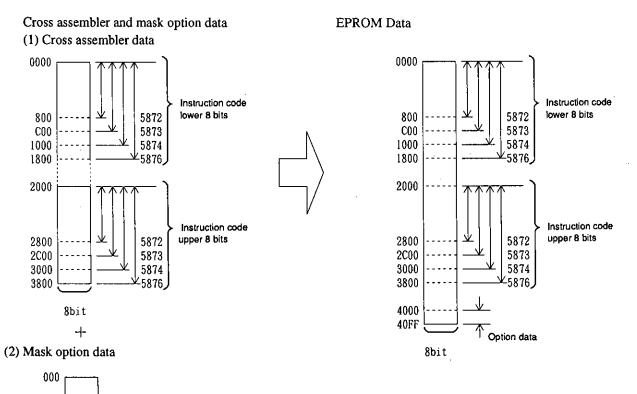

As shown in the figures below, the data to be written to the LC58E76 consists of a program data area (instruction code area) and an option data area. The EC5876.EXE program applies a special conversion process to the option specification data to create the option data area data.

The EC5876.EXE program converts and merges program data and option data to create the data to be written to the LC58E76.

#### · Start-up procedure

### • Error messages

|          |                                  | The file "filename.HEX" was not found. The filename "filename.HEX" was incorrect. The ROM data and the option data object microcontroller type did not agree. The ROM data must be created with a cross assembler and option specification software designed for the same microcontroller type. |

|----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error ON | I filename.HEX, EOF NOT DETECTED | A hexadecimal record end marker was not found in the file "filename.HEX".                                                                                                                                                                                                                       |

| Error ON | filename.HEX, ILLEGAL CHARACTER  | A character other than 0 to 9 or A to F was found in a hexadecimal context while reading the file "filename.HEX".                                                                                                                                                                               |

| Error ON | I filename.HEX, ADDRESS OVER     | .An address in the file "filename.HEX" exceeded the allowed range.                                                                                                                                                                                                                              |

| Error ON | I filename.HEX, ILLEGAL FILEHDR  | .The header in the file "filename.HEX" is not for<br>the LC5870 series.  There was an error in the hexadecimal file                                                                                                                                                                             |

|          |                                  | specification.                                                                                                                                                                                                                                                                                  |

| Error ON | command line input,              |                                                                                                                                                                                                                                                                                                 |

|          | INVALID NUMBER OF PARAMETERS     | .The number of parameters in the command line was inappropriate.                                                                                                                                                                                                                                |

| Error ON | I ILLEGAL, MASK OPTION DATA      | .There was an error in the mask option data.                                                                                                                                                                                                                                                    |

#### • EPROM data structure

3FF

- Use of the W58E68Q EPROM Writing Board (Board used with both the LC58E68 and the LC58E76)

The EPROM writing board is a socket adapter that fits the LC58E76 to the device socket in a general-purpose PROM writer.

- · EPROM Writing Board Appearance

- PROM writer settings

- ROM type:

256 K, VPP = 21 V mode

— Start and stop addresses:

Set these to 0000H and 40FFH.

4. Erasing LC58E76 EPROM Data

Use a general-purpose EPROM eraser to erase data written to an LC58E76.

- 5. Notes On Order Mask ROM

- The following methods cannot be used to order LC5870 Series mask ROM products.

- Use of ".HEX" files that were converted and merged for use in an LC58E76

- Use of an LC58E76 itself

- · Ordering mask ROM

- Use the program hexadecimal data generated by the cross assembler.

- Use the option hexadecimal data generated by the option specification software.

- Provide three EPROMs to which the program hexadecimal data has been written using a general-purpose EPROM writer.

- Provide three EPROMs to which the option hexadecimal data has been written using a general-purpose EPROM writer.

## **Specifications**

The electrical characteristics listed here are provisional values and are subject to change.

# Absolute Maximum Ratings at $V_{SS}$ = 0 V, TA = 25°C

|                             |                   |                                                |           |                              |                                        |               | Rating                             |                         |             |  |

|-----------------------------|-------------------|------------------------------------------------|-----------|------------------------------|----------------------------------------|---------------|------------------------------------|-------------------------|-------------|--|

| Parameter                   | Symbol            |                                                | Con       | dition/Pin                   |                                        | min           | typ                                | max                     | Unit        |  |

|                             | V <sub>DD</sub>   |                                                |           |                              |                                        | -0.3          |                                    | +6.0                    | V           |  |

| Maximum supply voltage      | V <sub>DD</sub> 1 |                                                |           |                              |                                        | -0.3          |                                    | $v_{DD}$                | V           |  |

|                             | V <sub>DD</sub> 2 |                                                |           |                              |                                        | -0.3          |                                    | V <sub>DD</sub>         | V           |  |

|                             | VI (1)            | As allowe<br>XTIN, CF                          | •         | ecified cir                  | cuit (figure 1)                        | Allowed up to | wed up to the voltage that appears |                         |             |  |

| Maximum input voltage       | VI (2)            | INT, TST                                       | •         | •                            | - 4, A1 - 4, RES,  put mode)           | -0.3          |                                    | V <sub>DD</sub><br>+0.3 | <b>&gt;</b> |  |

|                             | VO (1)            | As allowe<br>XTOUT,                            |           | ecified cir                  | cuit (figure 1)                        | Allowed up to | wed up to the voltage that appears |                         |             |  |

| Maximum output voltage      | VO (2)            | CUP1, C                                        | UP2, Seg1 | - 35, CO                     | - 4, N1 = 4,<br>M1 = 4,<br>utput mode) | -0.3          |                                    | V <sub>DD</sub><br>+0.3 | V           |  |

|                             | VO (3)            | Open drain specifications N1 to N4 (n-channel) |           |                              |                                        | -0.3          |                                    | +13                     | V           |  |

|                             | IO (1)            | Per pin                                        | N1 – 4    |                              |                                        | 0             |                                    | 15                      | mA          |  |

|                             | IO (2)            | Per pin                                        | 1 11 - 4  |                              |                                        | -10           |                                    | 0                       | mA          |  |

|                             | IO (3)            | Per pin                                        | K1 – 4, F | 1 – 4, M                     | 1 – 4, SO1 – 4,                        | 0             |                                    | 5                       | mΑ          |  |

| Outros de la compani        | IO (4)            | Per pin                                        | A1 – 4    |                              |                                        | -5            |                                    | 0                       | mA          |  |

| Output pin current          | Σ ΙΟ (1)          | Total (sur<br>pin curre                        | , ,       | ,                            | P1 – 4, M1 – 4,                        |               |                                    | 70                      | mA          |  |

|                             | Σ 10 (2)          | Total (sur<br>pin curre                        | ' 1       | SO1 4, A14, N1 4,<br>Seg1 35 |                                        | -70           |                                    |                         | mA          |  |

| Allowable power dissipation | Pdmax             | For the C                                      | FC80 wind | low ceran                    | nic flat package                       |               |                                    | 500                     | mW          |  |

| Operating temperature       | Topr              |                                                |           |                              |                                        | 10            |                                    | 40                      | °C          |  |

| Storage temperature         | Tstg              |                                                |           |                              |                                        | -55           |                                    | +125                    | ۰c          |  |

# Allowable Operating Ranges at $V_{SS} = 0$ V, $Ta = 25^{\circ}C$

|                               |                   |                                                                                                    |                                                                                                                     |                                        |                      | l   |                      |      |

|-------------------------------|-------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|-----|----------------------|------|

| Parameter                     | Symbol            | Condi                                                                                              | tion/Pin                                                                                                            |                                        | min                  | typ | max                  | Unit |

|                               |                   | No LCD specifications                                                                              | : V <sub>DD</sub> 1 :                                                                                               | = V <sub>DD</sub> 2 = V <sub>DD</sub>  | 2.8                  |     | 5.5                  | V    |

|                               |                   | Static drive specifications: V <sub>DD</sub> 1 = V <sub>DD</sub> 2 = V <sub>DD</sub>               |                                                                                                                     |                                        | 2.8                  |     | 5.5                  | V    |

| Supply voltage                | V <sub>DD</sub>   | 1/2 bias specifications                                                                            | : V <sub>DD</sub> 1 =                                                                                               | V <sub>DD</sub> 2 ≅ 1/2V <sub>DD</sub> | 2.8                  |     | 5.5                  | V    |

|                               |                   | 1/3 bias specifications<br>V <sub>DD</sub> 2 ≅ 1/3V <sub>DD</sub>                                  | : V <sub>DD</sub> 1 a                                                                                               | ≅ 2 × 1/3V <sub>DD</sub>               | 2.8                  |     | 5.5                  | v    |

| Data retention supply voltage | V <sub>HD</sub>   | RAM and register con                                                                               | tents ret                                                                                                           | ention voltage*                        | 2.8                  |     | $V_{DD}$             | V    |

| Input high-level voltage      | V <sub>IH</sub> 1 | S1 - 4, K1 - 4, P1 - 4, M1 - 4, SO1 - 4,<br>A1 - 4, INT<br>(K, P, M, SO and A ports in input mode) |                                                                                                                     |                                        | 0.7 V <sub>DD</sub>  |     | V <sub>DD</sub>      | V    |

| Input low-level voltage       | V <sub>IL</sub> 1 | (K,P,M,SO and Apo                                                                                  | (K, F, M, SO and A ports in input mode)                                                                             |                                        |                      |     | 0.3 V <sub>DD</sub>  | V    |

| Input high-level voltage      | V <sub>IH</sub> 2 | PC0 -:-                                                                                            |                                                                                                                     |                                        | 0.75 V <sub>DD</sub> |     | V <sub>DD</sub>      | V    |

| Input low-level voltage       | V <sub>IL</sub> 2 | HES DIN                                                                                            | RES pin                                                                                                             |                                        |                      |     | 0.25 V <sub>DD</sub> | ٧    |

| Input high-level voltage      | V <sub>IH</sub> 3 | OCINI -i-                                                                                          |                                                                                                                     |                                        | 0.75 V <sub>DD</sub> |     | V <sub>DD</sub>      | V    |

| Input low-level voltage       | V <sub>IL</sub> 3 | CFIN pin                                                                                           |                                                                                                                     |                                        | 0                    |     | 0.25 V <sub>DD</sub> | V    |

| Operating frequency 1         | fopg1             | V <sub>DD</sub> = 2.8 to 5.5 V, 32                                                                 | 2 kHz                                                                                                               | XTIN/XTOUT                             | 32                   |     | 33                   | kHz  |

| Operating frequency 2         | fopg2             | V <sub>DD</sub> = 2.8 to 5.5 V, 38                                                                 | 3 kHz                                                                                                               | crystal                                | 37                   |     | 39                   | kHz  |

| Operating frequency 3         | fopg3             | V <sub>DD</sub> = 2.8 to 5.5 V, 65                                                                 | kHz                                                                                                                 | oscillator                             | 60                   |     | 70                   | kHz  |

| Operating frequency 4         | fopg4             | V <sub>DD</sub> = 2.8 to 5.5 V                                                                     |                                                                                                                     |                                        | 190                  |     | 1200                 | kHz  |

| Operating frequency 5         | fopg5             | V <sub>DD</sub> = 3.0 to 5.5 V                                                                     |                                                                                                                     | CFOUT CF                               | 190                  |     | 2300                 | kHz  |

| Operating frequency 6         | fopg6             | V <sub>DD</sub> = 4.5 to 5.5 V                                                                     | specii                                                                                                              | fications                              | 190                  |     | 4200                 | kHz  |

| Operating frequency 7         | fopg7             | V <sub>DD</sub> ≈ 3.0 to 5.5 V                                                                     | Pins SO1 and SO3 (in serial mode) The rising and falling edges of input signal and clock waveforms must be ≤ 10 μs. |                                        | DC                   |     | 200                  | kHz  |

Note: \* In a state with the CF/RC oscillator and the crystal oscillator completely stopped, and all internal circuits stopped

## Electrical Characteristics at $V_{DD}$ = 2.8 to 3.2 V, $V_{SS}$ = 0 V, Ta = 25 $^{\circ}C$

|                                                            |         |                                                    |                                            |                       | Rating |      |      |

|------------------------------------------------------------|---------|----------------------------------------------------|--------------------------------------------|-----------------------|--------|------|------|

| Parameter                                                  | Symbol  | Co                                                 | ondition/Pin                               | min                   | typ    | max  | Unit |

|                                                            | RIN1 A  | VIN = 0.2 V <sub>DD</sub> ,<br>Low-level hold trai | nsistor *, Figure 2                        | 60                    | 300    | 1200 | kΩ   |

|                                                            | RIN1 B  | VIN = V <sub>DD</sub> , Pull-de                    | own resistor *, Figure 2                   | 30                    | 150    | 500  | kΩ   |

|                                                            | RIN1 C  | VIN = 0.8 V <sub>DD</sub> ,<br>High-level hold tra | nsistor *, Figure 2                        | 60                    | 300    | 1200 | kΩ   |

|                                                            | RIN1 D  | VIN = V <sub>SS</sub> , Pull-up                    | resistor *, Figure 2                       | 30                    | 150    | 500  | kΩ   |

| Input resistance                                           | RIN2 A  | VIN = 0.2 V <sub>DD</sub> , IN                     | T low-level hold transistor                | 60                    | 300    | 1200 | kΩ   |

|                                                            | RIN2 B  | VIN = V <sub>DD</sub> , INT pu                     | ıll-down resistor                          | 300                   | 1500   | 5000 | kΩ   |

|                                                            | RIN2 C  | VIN = 0.8 V <sub>DD</sub> , IN                     | T high-level hold transistor               | 60                    | 300    | 1200 | kΩ   |

|                                                            | RIN2 D  | VIN = VSS, INT pu                                  | ıll-up resistor                            | 300                   | 1500   | 5000 | kΩ   |

|                                                            | RIN3    | VIN = V <sub>DD</sub> .<br>With a pull-down r      | esistor on the TST pin                     | 20                    | 70     | 300  | kΩ   |

| Output low-level voltage                                   | VOL (1) | IOL = 1.0 mA                                       | N1 – 4                                     |                       |        | 0.5  | ٧    |

| Output high-level voltage                                  | VOH (2) | IOH = –400 μA                                      | K1 = 4, P1 = 4, M1 = 4,<br>SO1 = 4, A1 = 4 | V <sub>DD</sub> – 0.5 |        |      | v    |

| Output low-level voltage                                   | VOL (2) | IOL = 400 μA                                       | (K, P, M, SO and A ports in output mode)   |                       |        | 0.5  | ٧    |

| Output off leakage current                                 | [IOFF]  | VOH = 10.5 V                                       | N1 - 4, Figure 10                          |                       |        | 1.0  | μА   |

| Segment port output impedance • When CMOS output ports are |         |                                                    |                                            |                       |        |      |      |

| Output high-level voltage                                  | VOH (3) | IOH = -100 μA                                      | Con the OF                                 | V <sub>DD</sub> - 0.5 |        |      | V    |

| Output low-level voltage                                   | VOL (3) | IOL = 100 µA                                       | Seg 1 to 35                                |                       |        | 0,5  | V    |

Note: \* The 24 pins S1 to S4, K1 to K4, P1 to P4, M1 to M4, SO1 to SO4 and A1 to A4.

#### Continued from preceding page.

|                                    | ·                     |                                                                             |                             |                                                                                                                                                |                                                  |                                                  | Rating |                           |            |

|------------------------------------|-----------------------|-----------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------|---------------------------|------------|

| Parameter                          | Symbol                |                                                                             | Con                         | dition/Pin                                                                                                                                     |                                                  | min                                              | typ    | max                       | Unit       |

| - When p-channel open-drain output | ports are us          | ed (See figure 1                                                            | 1.)                         |                                                                                                                                                |                                                  |                                                  |        | , ,                       |            |

| Output high-level voltage          | VOH (3)               | /بر 100 = HOH                                                               | ١                           | Seg 1 to 35                                                                                                                                    | 5                                                | V <sub>DD</sub> – 0.5                            |        |                           | V          |

| Output off leakage current         | [10FF]                | VOL = VSS                                                                   |                             |                                                                                                                                                |                                                  | <u> </u>                                         |        | 1.0                       | μА         |

| When n-channel open-drain output   | ports are us          | ed (See figure 1                                                            | 1.)                         |                                                                                                                                                |                                                  | ,                                                |        | <del>,</del>              |            |

| Output low-level voltage           | VOL (3)               | IOL = 100 μA                                                                |                             | Seg 1 to 35                                                                                                                                    |                                                  | <u> </u>                                         |        | 0.5                       | <u> </u>   |

| Output off leakage current         | I OFF                 | VOH = V <sub>DD</sub>                                                       |                             | oog . w o                                                                                                                                      |                                                  | <u> </u>                                         |        | 1.0                       | μΑ         |

| Static drive                       |                       |                                                                             |                             |                                                                                                                                                |                                                  |                                                  |        | ·                         |            |

| Output high-level voltage          | VOH (4)               | IOH = −20 μA                                                                |                             | Seg 1 to 35                                                                                                                                    | 5                                                | V <sub>DD</sub> 0.2                              |        | 1                         | V          |

| Output low-level voltage           | VOL (4)               | IOL = 20 μA                                                                 |                             |                                                                                                                                                |                                                  | <u> </u>                                         |        | 0.2                       | ٧          |

| Output high-level voltage          | VOH (5)               | /لر 100 = - IOH                                                             | A                           | COM1                                                                                                                                           |                                                  | V <sub>DD</sub> - 0.2                            |        |                           | ٧          |

| Output low-level voltage           | VOL (5)               | IOL = 100 μA                                                                |                             |                                                                                                                                                |                                                  |                                                  |        | 0.2                       | ٧          |

| • 1/2 bias                         |                       |                                                                             |                             |                                                                                                                                                |                                                  |                                                  |        |                           |            |

| Output high-level voltage          | VOH (4)               | IOH = -20 μA                                                                |                             | San 1 to 21                                                                                                                                    |                                                  | V <sub>DD</sub> - 0.2                            |        |                           | ٧          |

| Output low-level voltage           | VOL (4)               | IOL = 20 μA                                                                 |                             | Seg 1 to 35                                                                                                                                    |                                                  |                                                  |        | 0.2                       | ٧          |

| Output high-level voltage          | VOH (6)               | IOH = −100 μ/                                                               | A                           |                                                                                                                                                |                                                  | V <sub>DD</sub> - 0.2                            |        |                           | ٧          |

| Output middle-level voltage        | VOM2-1                | IOH = -100 μ/<br>IOL = 100 μA                                               | A                           | COM1 - 4                                                                                                                                       |                                                  | V <sub>DD</sub> /2 - 0.2                         |        | V <sub>DD</sub> /2 + 0.2  | ٧          |

| Output low-level voltage           | VOL (6)               | IOL = 100 μA                                                                |                             |                                                                                                                                                |                                                  |                                                  |        | 0.2                       | ν          |

| • 1/3 bias                         |                       | ·                                                                           |                             |                                                                                                                                                |                                                  | <u> </u>                                         |        | •                         | ·····      |

| Output high-level voltage          | VOH (4)               | 1OH = -20 μA                                                                |                             |                                                                                                                                                |                                                  | V <sub>DD</sub> - 0.2                            |        |                           | V          |

|                                    | VOM1-1                | IOH = -20 μA                                                                |                             | Seg 1 to 35                                                                                                                                    |                                                  | 2V <sub>DD</sub> /3 - 0.2                        |        | 2V <sub>DD</sub> /3 + 0.2 | V          |

| Output middle-level voltage        | VOM1-2                | IOL = 20 μA                                                                 |                             |                                                                                                                                                |                                                  | V <sub>DD</sub> /3 - 0.2                         |        | V <sub>DD</sub> /3 + 0.2  | ٧          |

| Output low-level voltage           | VOL (4)               | IOL = 20 μA                                                                 |                             |                                                                                                                                                |                                                  |                                                  |        | 0.2                       | V          |

| Supply leakage current             | ILEK (1)              | V <sub>DD</sub> = 3.0 V                                                     |                             | Ta = 25°C, STOP mode,<br>Figure 3                                                                                                              |                                                  |                                                  | 1.0    |                           | μА         |

|                                    |                       | V <sub>DD</sub> = 3.0 V S1 - 4, K1 - 4, P1 - 4,<br>M1 - 4, SO1 - 4, A1 - 4, |                             |                                                                                                                                                |                                                  |                                                  |        |                           |            |

| Input leakage current              | IOFF                  | VIN = V <sub>DD</sub>                                                       |                             | INT, RES (K, P, M, SO<br>and A ports in input                                                                                                  |                                                  |                                                  |        | 1.0                       | μА         |

|                                    |                       | VIN = V <sub>SS</sub>                                                       |                             | mode, INT<br>open spec                                                                                                                         | and RES pin<br>ifications)                       | -1.0                                             |        |                           | μА         |

| Output voltage 1                   | V <sub>DD</sub> 1-(1) | V <sub>DD</sub> = 3.0 V, (<br>1/2 bias, fopg<br>Figure 4                    | C1 = 0<br>= 32.             | C2 = 0.1 µF<br>768 kHz                                                                                                                         | V <sub>DD</sub> 1 = V0                           |                                                  | 1.5    |                           | ٧          |

|                                    | V <sub>DD</sub> 2-(1) | $V_{DD} = 3.0 \text{ V}, 0$                                                 |                             |                                                                                                                                                |                                                  |                                                  | 2.0    |                           | V          |

| Output voltage 2                   | <del></del>           | 1/3 bias, fopg                                                              | <b>= 32</b> .               | 768 kHz,                                                                                                                                       | V <sub>DD</sub> 1 = V0<br>V <sub>DD</sub> 2 = V0 | <del> </del>                                     | 1.0    | 1                         | v          |

|                                    | V <sub>DD</sub> 2-(2) | Figure 4                                                                    | T ===                       | 25°C, Cryst                                                                                                                                    |                                                  | <del>                                     </del> | 1.0    | +                         | <b>_ `</b> |

| Supply current 1                   | IDD   1               | V <sub>DD</sub> = 3.0 V                                                     | spec<br>Cg =                | sfications, Cr<br>20 pF, Cl =<br>mode, LCD                                                                                                     | rystal: 32 kHz,<br>25 kΩ                         |                                                  | 5.0    |                           | μА         |

| Supply current 2                   | IDD   2               | V <sub>DD</sub> = 3.0 V                                                     | spec<br>or 69<br>C1 =       | Figure 6  Fa = 25°C, Crystal oscillator specifications, Crystal: 38 kHz or 65 kHz, Cg = 10 pF, Cl = 25 kΩ, Halt mode, CD at 1/3 bias, Figure 6 |                                                  |                                                  | 10.0   |                           | μΑ         |

| Supply current 3                   | IDD   3               | V <sub>DD</sub> = 3.0 V                                                     | spec<br>Ccg<br>Hait<br>Figu | a = 25°C, CF oscillator secifications, CF: 400 kHz, cg = Cod = 330 pF alt mode, LCD at 1/3 bias, gure 8                                        |                                                  |                                                  | 150    |                           | μΑ         |