#### 捷多邦,专业PCB打样工厂,24小时加急出货

查询LC651104N供应商

Ordering number : EN\*5221

#### CMOS LSI

LC65E1104

**On-Chip UVEPROM**

## **Preliminaly**

# **Overview**

The LC65E1104 is an on-chip UVEPROM version of Sanyo's LC651104N/F/L and LC651102N/F/L CMOS 4-bit single-chip microcontrollers. The LC65E1104 has the same functions and pin assignment as the LC651104N/F/L and LC651102N/F/L mask ROM products, although the A/D characteristics and certain other characteristics differ somewhat. It includes a 4-KB on-chip EPROM.

WWW.DZSC.CO

The LC65E1104 is provided in DIC30S and MFC30S window packages and is ideal for program development and evaluation since program data can be rewritten multiple times.

# **Features**

- EPROM data option switching

- The following four LC65E1104 functions can be specified by EPROM data:

- Port C and D output levels at reset

- Clock oscillator option

- Clock predivider option

- Watchdog reset option

However, note that the port output circuit type cannot be changed. These circuits are always open-drain outputs.

- Internal UVEPROM capacity: 4096 bytes

- The LC65E1104 on-chip UVEPROM can be programmed and verified using a general-purpose EPROM programmer.

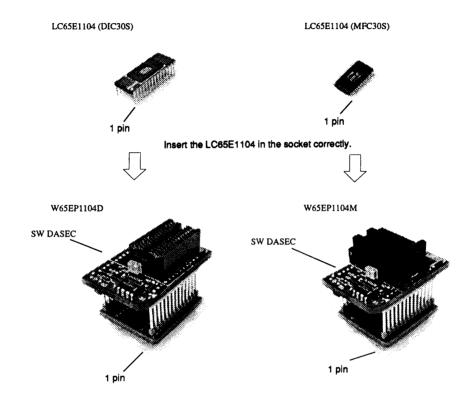

Sanyo provides special-purpose 30-to-28-pin adapters (the W65EP1104D for the DIC package and the W65EP1104M for the MFC package) to allow commercial EPROM programmers to be used with the LC65E1104.

- · Data security function

- Pin compatible with the LC651104/1102 mask ROM devices

- Instruction cycle time: 0.92 µs to 20 µs (A/D converter cycle time: 0.98 µs to 12 µs)

- Factory shipment: DIC-30S (with window), MFC-30S (with window)

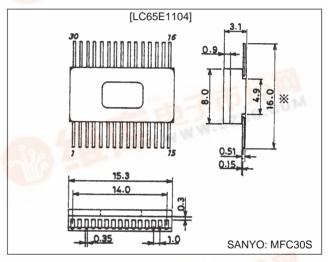

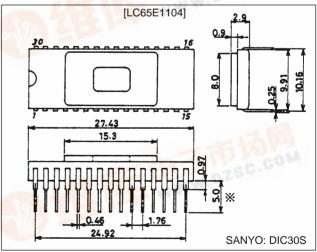

# Package Dimensions

unit: mm

#### 3212-MFC30S

4-Bit Single-Chip Microcontroller

unit: mm

3215-DIC30S

These figures are provided for reference purposes and do not include Note: tolerance specifications. Official drawings are available on request from your Sanvo representative.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

#### LC651104/1102 series organization

| Model name                   | Pins | ROM capacity | RAM capacity | Package                  |

|------------------------------|------|--------------|--------------|--------------------------|

| LC651104N/F/L, LC651102N/F/L | 30   | 4 k/2 k      | 256 W        | DIP30S, DIP30S-D, MFP30S |

| LC65E1104                    | 30   | 4 k          | 256 W        | DIC30S, MFC30S           |

| LC65P1104                    | 30   | 4 k          | 256 W        | DIP30S-D, MFP30S         |

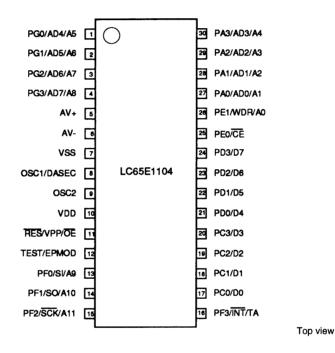

#### **Pin Assignment**

Common to DIC/MFC

#### **Usage Notes**

The LC65E1104 was designed for developing and evaluating programs for the LC651104/1102 series microcontrollers. Keep the following points in mind when using the LC65E1104.

- 1. Protecting EPROM data from UV exposure

- Keep the LC65E1104's package window covered with an opaque seal when using the device.

- 2. The LC65E1104 differs from the LC651104N/F/L and LC651102N/F/L as listed in the table below.

|                            | Item                 | LC65E1104                                              | LC651104F/1102F                | LC651104N/1102N                                       | LC651104L/1102L  |

|----------------------------|----------------------|--------------------------------------------------------|--------------------------------|-------------------------------------------------------|------------------|

| I/O circuit c              | onfiguration         | Open drain (N channel)                                 |                                | stor-provided output selectable b                     |                  |

| Port C and levels at res   |                      | High or low selected in 4-bit<br>units (by EPROM data) | ł                              | High or low selected in 4-bit unit (user mask option) | 5                |

| Oscillator                 | Resonator            | RC/ceramic<br>(by EPROM data)                          |                                | RC/ceramic (user mask option)                         |                  |

| Oscillator                 | Predivider option    | 1/1, 1/3, 1/4<br>(by EPROM data)                       | 1/1 only<br>(user mask option) | 1/1, 1/3, 1/4<br>(user mask option)                   |                  |

| Watchdog I                 | reset                | Available/not available<br>(by EPROM data)             |                                | Available/not available<br>(user mask option)         |                  |

| Operating s<br>voltage ran |                      | 3.0 to 6.0 V*                                          | 4.0 t 6.0 V                    | 3.0 to 6.0 V                                          | 2.5 to 6.0 V     |

| Normal mo                  | de current drain     | Mask version + about 3 mA (typical)                    | 2 mA (typical)                 | 1.5 mA (typical)                                      | 1.5 mA (typical) |

| Low-level in<br>(RES termi | nput current<br>nal) | –50 μA (typical)                                       |                                | –10 μA (typical)                                      |                  |

| Operating t                | emperature range     | +10 to +40°C                                           |                                | -40 to +85°C                                          |                  |

| Package                    |                      | DIC30S (with window)<br>MFC30S (with window)           |                                | DIP30S, DIP30S-D<br>MFP30S                            |                  |

Note: A/D converter operating supply voltage range: 4.7 to 5.3  ${\rm V}$

#### **Pin Names**

| OSC1, OSC2 | RC or ceramic oscillator           | TEST       | Test                                 |

|------------|------------------------------------|------------|--------------------------------------|

| RES        | Reset                              | INT        | Interrupt request pin                |

| PA0 to PA3 | Shared-function I/O ports A0 to A3 | SI         | Serial input pin                     |

| PC0 to PC3 | Shared-function I/O ports C0 to C3 | SO         | Serial output pin                    |

| PD0 to PD3 | Shared-function I/O ports D0 to D3 | SCK        | Serial clock input/output pin        |

| PE0 to PE1 | Shared-function I/O ports E0 to E1 | AD0 to AD7 | AD converter input pin               |

| PF0 to PF3 | Shared-function I/O ports F0 to F3 | AV+, AV–   | AD converter reference voltage input |

| PG0 to PG3 | Shared-function I/O ports G0 to G3 | WDR        | Watchdog reset pin                   |

Note: The SI, SO, SCK, and INT pins are shared function pins that are also used as the PF0 to PF3 pins, respectively.

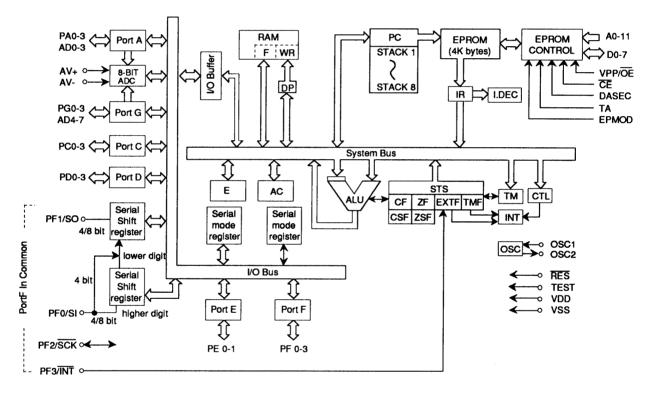

#### System Block Diagram

| RAM | Data memory               | ROM     | Program memory                  |

|-----|---------------------------|---------|---------------------------------|

| F   | Flag                      | PC      | Program counter                 |

| WR  | Working register          | INT     | Interrupt control               |

| AC  | Accumulator               | IR      | Instruction register            |

| ALU | Arithmetic and logic unit | I.DEC   | Instruction decoder             |

| DP  | Data pointer              | CF, ZSF | Carry flag, Carry save flag     |

| E   | E register                | ZF, ZSC | Zero flag, zero save flag       |

| CTL | Control register          | EXTF    | External interrupt request flag |

| OSC | Oscillator                | TMF     | Internal interrupt request flag |

| ТМ  | Timer                     | STS     | Status register                 |

### **Pin Description**

| Symbol                                                                 | Pins | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Option                                                                                                                                                                   | At reset                                                                                | PROM mode                                                                             |

|------------------------------------------------------------------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| V <sub>DD</sub>                                                        | 1    | —   | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                        | _                                                                                       | _                                                                                     |

| V <sub>SS</sub><br>OSC1/DASEC                                          | 1    |     | Connections for the external RC or ceramic oscillator circuit used as the system clock oscillator.     If external clock input is used, leave the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol> <li>Pin 2: RC oscillator<br/>external clock</li> <li>Pin 2: Ceramic<br/>oscillator</li> <li>Predivider option         <ul> <li>No predivider</li> </ul> </li> </ol> |                                                                                         | EPROM control signal<br>DASEC                                                         |

| OSC2                                                                   | 1    | 0   | OSC2 pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>1/3 predivider</li> <li>1/4 predivider</li> </ul>                                                                                                               |                                                                                         |                                                                                       |

| PA0/AD0/A1<br>PA1/AD1/A2<br>PA2/AD2/A3<br>PA3/AD3/A4                   | 4    | I/O | <ul> <li>I/O port: A0 to A3<br/>Input in 4-bit units (IP instruction)<br/>Output in 4-bit units (OP instruction)<br/>Testing in single-bit units (BP and BNP<br/>instructions)<br/>Setting or clearing in single-bit units (SPB<br/>and RPB instructions)</li> <li>Standby is controlled by PA3</li> <li>The PA3 pin must be free from chattering<br/>during the halt instruction execution cycle.<br/>Each of these four pins has two functions as<br/>listed below.<br/>PA0/AD0: AD converter input pin AD0<br/>PA1/AD1: AD converter input pin AD1<br/>PA2/AD2: AD converter input pin AD2<br/>PA3/AD3: AD converter input pin AD3</li> </ul> | Open drain type<br>output                                                                                                                                                | High-level output<br>(Output Nch<br>transistor: Off)                                    | Address inputs A1 to<br>A4                                                            |

| PC0/D0<br>PC1/D1<br>PC2/D2<br>PC3/D3                                   | 4    | I/O | <ul> <li>I/O port: C0 to C3<br/>Identical to PA0 to PA3*</li> <li>Option permits output at reset to be high or<br/>low.</li> <li>Note: * No standby control function is<br/>provided.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>Open drain type<br/>output</li> <li>Output at reset:<br/>high</li> <li>Output at reset:<br/>low</li> <li>3.: Specified in a<br/>group of 4 bits</li> </ol>      | <ul> <li>High-level output</li> <li>Low-level output<br/>(Option-selectable)</li> </ul> | Data lines D0 to D3                                                                   |

| PD0/D4<br>PD1/D5<br>PD2/D6<br>PD3/D7                                   | 4    | I/O | I/O port: D0 to D3<br>Identical to PC0 to PC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Identical to PC0 to<br>PC3                                                                                                                                               | Identical to PC0 to<br>PC3                                                              | Data lines D4 to D7                                                                   |

| PE0/CE<br>PE1/WDR/A0                                                   | 2    | I/O | <ul> <li>I/O port: E0 and E1<br/>Input in 4-bit units (IP instruction)<br/>Output in 4-bit units (OP instruction)<br/>Setting or clearing in single-bit units (SPB,<br/>RPB instructions)<br/>Testing in single-bit units (BP and BNP<br/>instructions)</li> <li>PE0 provides a continuous burst (64-Tcyc)<br/>function.</li> </ul>                                                                                                                                                                                                                                                                                                              | 1. Open drain type<br>output                                                                                                                                             | High-level output<br>(Output Nch<br>transistor: Off)                                    | <ul> <li>EPRO<u>M c</u>ontrol signal CE</li> <li>Address input A0</li> </ul>          |

| PF0/SI/A9<br>PF1/ <u>SO/A</u> 10<br>PF2/ <u>SCK</u> /A11<br>PF3/INT/TA | 4    | I/O | <ul> <li>I/O ports F0 tp F3<br/>Identical to PE0 to PE1*</li> <li>Shared with the serial interface and INT<br/>input.</li> <li>Program-selectable<br/>SI Serial input port</li> <li><u>SO</u> Serial output port</li> <li><u>SCK</u> Serial clock input/output</li> <li>INT Interrupt request input</li> <li>The serial I/O function can be switched<br/>between 4-bit and 8-bit operation under<br/>program control.</li> <li>Note: * No burst pulse output function is<br/>provided.</li> </ul>                                                                                                                                                | Identical to PE0 to<br>PE1                                                                                                                                               | Identical to PE0 to<br>PE1<br>Serial port: Disabled<br>Interrupt source: INT            | <ul> <li>Address inputs A9<br/>to A11</li> <li>EPROM control<br/>signal TA</li> </ul> |

Continued on next page.

Continued from preceding page.

| Symbol                                               | Pins | I/O | Function                                                                                                                                                                                                                                                                                                                                                                     | Option                     | At reset                   | PROM mode                              |

|------------------------------------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------------------|

| PG0/AD4/A5<br>PG1/AD5/A6<br>PG2/AD6/A7<br>PG3/AD7/A8 | 4    | I/O | <ul> <li>I/O ports G0 to G3<br/>Identical to PE0 to PE1*<br/>Note: * No burst pulse output function is<br/>provided.</li> <li>Each of these four pins has two functions as<br/>listed below.</li> <li>PG0/AD4: AD converter input pin AD4<br/>PG1/AD5: AD converter input pin AD5<br/>PG2/AD6: AD converter input pin AD6<br/>PG3/AD7: AD converter input pin AD7</li> </ul> | Identical to PE0 to<br>PE1 | Identical to PE0 to<br>PE1 | Address inputs A5 to<br>A8             |

| AV+                                                  | 1    | _   | Reference voltage input pin for A/D                                                                                                                                                                                                                                                                                                                                          |                            |                            |                                        |

| AV-                                                  | 1    | _   | conversion.                                                                                                                                                                                                                                                                                                                                                                  | —                          | _                          | —                                      |

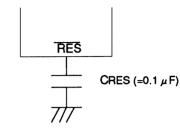

| RES/VPP/OE                                           | 1    |     | <ul> <li>System reset input</li> <li>Connect an external capacitor for power on reset.</li> <li>Apply a low level for at least 4 clock cycles for the power-on reset.</li> </ul>                                                                                                                                                                                             | _                          | _                          | EPR <u>QM</u> control signal<br>VPP/OE |

| TEST/EPMOD                                           | 1    |     | LSI test pin<br>Normally connected to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                        | _                          | _                          | EPROM control signal<br>EPMOD          |

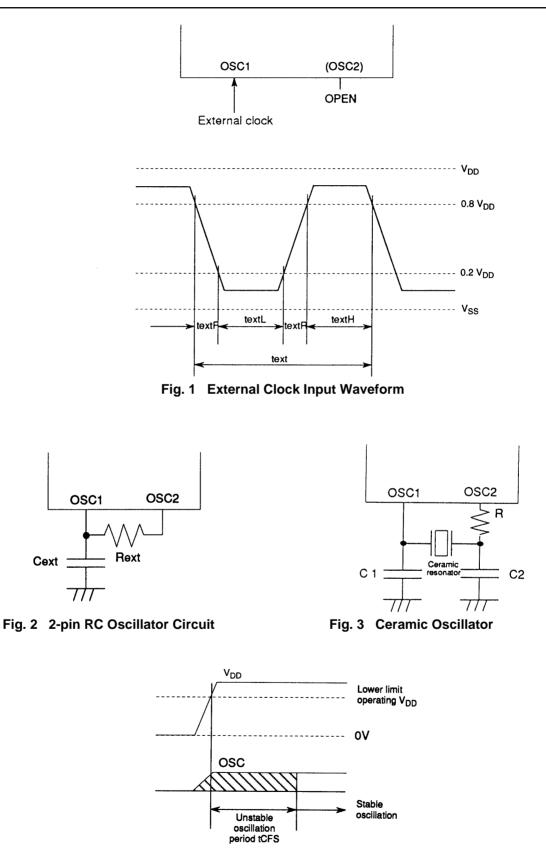

# Oscillator circuit option

| Option                | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Conditions and notes     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1. External clock     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Leave the OSC2 pin open. |

| 2. 2-pin RC OSC       | Cext OSC 1<br>Cext OSC 1<br>Cext OSC 2<br>Cext O |                          |

| 3. Ceramic oscillator | Ceramic OSC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

# Predivider option

| Option                 | Circuit                                                                                                                                                                                                                                                                                                                                       | Conditions and notes                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. No predivider (1/1) | OSC circuit<br>Timing<br>generator                                                                                                                                                                                                                                                                                                            | <ul> <li>Applicable to all 3 oscillator options.</li> <li>The oscillator or external clock frequency must<br/>not exceed 1444 kHz. (LC651104N,<br/>LC651102N)</li> <li>The oscillator or external clock frequency must<br/>not exceed 4330 kHz. (LC651104F,<br/>LC651102F)</li> <li>The oscillator or external clock frequency must<br/>not exceed 1040 kHz. (LC651104L,<br/>LC651102L)</li> </ul> |

| 2. 1/3 predivider      | ticsc 1/3 fosc Surger Solution                                                                                                                                                                                                                                                                                                                | <ul> <li>Applicable to the external clock and ceramic oscillator options.</li> <li>The oscillator or external clock frequency must not exceed 4330 kHz.</li> </ul>                                                                                                                                                                                                                                 |

| 3. 1/4 predivider      | losc → 1/4<br>predivider → 0000<br>0000 → 0000 → 0000 → 0000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 00000 → 000000 | <ul> <li>Applicable to the external clock and ceramic oscillator options.</li> <li>The oscillator or external clock frequency must not exceed 4330 kHz.</li> </ul>                                                                                                                                                                                                                                 |

Note: The oscillator and predivider options are summarized in the LC651104/1102 semiconductor news.

#### Port C and D reset output level options

Either of the following two options may be selected for the C and D I/O ports. Note that these options are specified in 4bit units.

| Option name              | Conditions                                          |

|--------------------------|-----------------------------------------------------|

| 1. Output at reset: high | All 4 bits of the selected port(s) (C or D or both) |

| 1. Output at reset: low  | All 4 bits of the selected port(s) (C or D or both) |

#### Port output configuration option

All shared-function I/O ports have an open-drain output circuit in the LC65E1104.

| Option               | Circuit | Conditions and notes   |

|----------------------|---------|------------------------|

| 1. Open drain output |         | Ports A, C, D, E and F |

#### Watchdog reset option

This option specifies the use of the PE1/WDR pin. This pin can be specified to function either as the normal port PE1 or as the WDR watchdog reset pin.

#### **Usage Notes**

1. Option specification

The SU60K.EXE program is used for option specification. The option code for the option specification area (addresses 1000 to 100A (hexadecimal)) is created by assembling the output of the SU60K.EXE program using the Sanyo M60K.EXE macro assembler and then linking the macro assembler output with the Sanyo L60K.EXE linker. It is also possible to load data directly into the option specification area. Specify options according to the option code creation table on page 8.

2. PROM programming

LC65E1104 can be programmed with a general-purpose EPROM programmer using either the W65EP1104D or W65EP1104M adapter.

• Recommended EPROM programmers

| Manufacturer       | EPROM programmer                             |

|--------------------|----------------------------------------------|

| Advantest          | R4945, R4944, R4943 or equivalent programmer |

| Ando               | AF-9704                                      |

| AVAL               | _                                            |

| Minato electronics | _                                            |

- The Intel 27512 (VPP: 12.5 V) high-speed programming method must be used to program this device. The address range must be set to 0 to 100A (hexadecimal) and the DASEC jumper must be set to the off position.

- 3. Using the data security function

The data security function prevents data already written to the microcontroller's PROM from being overwritten. LC651104 data security function procedure

- Move the DASEC jumper on the EPROM programming pin adapter to the on position. This enables the data security function.

- Attempt to reprogram the EPROM.

Since the data security function is enabled, the EPROM programmer will display an error. Note that this error is not due to an error in either the programmer or the LSI.

- Note: 1. At step 2, the data security function will not operate if all the data at the addresses to be programmed have the value FF (hexadecimal).

- 2. At step 2, the data security function will not apply to (i.e., will not prevent) programming using the sequence BLANK Æ PROGRAM Æ VERIFY.

- 3. Return the jumper to the off position after executing the data security function.

#### **DASEC** jumper setting

Normal data programming enabled

DASEC ON OFF

|--|

· Data security function enabled

| DASEC | ON | OFF |  |

|-------|----|-----|--|

|       |    |     |  |

#### LC65E1104

#### **Option specification area**

| ROM area               | Bit        |                      | Option specified             | Option/data relationship                            |  |  |  |

|------------------------|------------|----------------------|------------------------------|-----------------------------------------------------|--|--|--|

|                        | 7          | Unused               |                              | 0 (fixed)                                           |  |  |  |

|                        | 6 Watchdog |                      | g reset                      | 0: Disabled, 1: Enabled                             |  |  |  |

| 1000H 5<br>4<br>3<br>2 |            | PD                   |                              |                                                     |  |  |  |

|                        |            | PC                   | Output level at reset        | 0: Low level, 1: High level                         |  |  |  |

|                        |            | 000                  |                              |                                                     |  |  |  |

|                        |            | - OSC pre            | divider (XX = bits 3, bit 2) | 00: 1/1, 01: 1/3, 10: 1/4,. 11: unused              |  |  |  |

|                        | 1          |                      |                              |                                                     |  |  |  |

| 0                      |            | OSC reso             | onator (XX = bits 1, bit 0)  | 00: unused, 01: unused, 10: (2RC, EXT), 11: Ceramic |  |  |  |

|                        | 7          | PC3                  |                              |                                                     |  |  |  |

|                        | 6          | PC2                  | 1                            |                                                     |  |  |  |

|                        | 5          | PC1                  | Output configuration         | 0: OD, 1: PU*                                       |  |  |  |

|                        | 4          | PC0                  |                              |                                                     |  |  |  |

| 1001H                  | 3          | PA3                  |                              |                                                     |  |  |  |

|                        | 2          | PA2                  | -                            |                                                     |  |  |  |

|                        | 1          | PA1                  | Output configuration         | 0: OD, 1: PU*                                       |  |  |  |

|                        | 0          |                      | -                            |                                                     |  |  |  |

|                        | 7          | PA0                  |                              |                                                     |  |  |  |

|                        | 6 Unused   |                      |                              | 0 (fixed)                                           |  |  |  |

| 5                      | PE1        |                      |                              |                                                     |  |  |  |

|                        | PE0        | Output configuration | 0: OD, 1: PU*                |                                                     |  |  |  |

| 1002H                  | 1002H 4    | PD3                  |                              |                                                     |  |  |  |

|                        | 2          | PD2                  | -                            |                                                     |  |  |  |

|                        | 1          | PD1                  | Output configuration         | 0: OD, 1: PU*                                       |  |  |  |

|                        | 0          | PD0                  | -                            |                                                     |  |  |  |

|                        | 7          | PG3                  |                              |                                                     |  |  |  |

|                        | 6          | PG2                  | -                            |                                                     |  |  |  |

|                        | 5          | PG1                  | Output configuration         | 0: OD, 1: PU*                                       |  |  |  |

|                        | 4          | PG0                  | -                            |                                                     |  |  |  |

| 1003H                  | 3          | PG0<br>PF3           |                              |                                                     |  |  |  |

|                        | 2          | PF3<br>PF2           | -                            |                                                     |  |  |  |

|                        | 1          | PF2<br>PF1           | - Output configuration       | 0: OD, 1: PU*                                       |  |  |  |

|                        | 0          | PF1<br>PF0           | -                            |                                                     |  |  |  |

|                        | 7          |                      |                              |                                                     |  |  |  |

|                        |            |                      |                              |                                                     |  |  |  |

| 6                      |            |                      |                              |                                                     |  |  |  |

| 1004H                  | 5          |                      |                              |                                                     |  |  |  |

| to                     | 4          | Unused               |                              | 0 (fixed)                                           |  |  |  |

| 100AH                  | 3          |                      |                              |                                                     |  |  |  |

|                        | 2          |                      |                              |                                                     |  |  |  |

|                        | 1          |                      |                              |                                                     |  |  |  |

|                        | 0          |                      |                              |                                                     |  |  |  |

Note: Since all LC65E1104 ports are open-drain output circuits, the pull-up resistor options are ignored. However, the port options must be selected when using the LC651104/1102 mask ROM products. PU: Built-in pull-up resistor output circuit, OD: Open-drain output circuit

#### Specifications For LC651104N, 651102N Absolute Maximum Ratings at Ta = $25^{\circ}$ C, V<sub>SS</sub> = 0 V

#### Ratings Parameter Symbol Conditions Unit -0.3 to +7.0 Maximum supply voltage $V_{DD}$ max $V_{\text{DD}}$ V Allowable up to the OSC2 V Output voltage Vo generated voltage -0.3 to V<sub>DD</sub> + 0.3 V<sub>I</sub>1 OSC1\*1 V Input voltage V<sub>l</sub>2 TEST, RES, AV+, AV-–0.3 to $V_{DD}$ + 0.3 V PC0 to PC3, PD0 to PD3, PE0, PE1, PF0 to PF3 V<sub>IO</sub>1 -0.3 to +15 V Input/output voltage V<sub>IO</sub>2 PA0 to PA3, PG0 to PG3 -0.3 to V<sub>DD</sub> + 0.3 V Peak output current I/O port -2 to +20 mΑ lop I/O port: Per pin over a 100 ms period -2 to +20 mΑ IOA PC0 to PC3, PD0 to PD3, PE0, PE1:Total current for -15 to +100 $\Sigma I_{OA} 1$ mΑ Average output current PC0 to PC3, PD0 to PD3, and PE0, PE1\*2 PF0 to PF3, PG0 to PG3, PA0 to PA3; Total current for $\Sigma I_{OA}2$ -15 to +100 mΑ PF0 to PF3, PG0 to PG3, and PA0 to PA3\*2 Pd max1 Ta = +10 to +40°C (DIC package) 250 mW Allowable power dissipation Pd max2 Ta = +10 to +40°C (MFC package) mW 150 +10 to +40 °C Operating temperature Topr -55 to +125 °C Storage temperature Tstg

#### Allowable Operating Conditions at Ta = +10 to +40°C, $V_{SS} = 0 V$ , $V_{DD} = 3.0$ to 6.0 V

| Deveryor                            | Querchal           |                                                                                                               |                     | Ratings  |                      |             |

|-------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------|---------------------|----------|----------------------|-------------|

| Parameter                           | Symbol             | Conditions                                                                                                    | min                 | typ      | max                  | Unit        |

| Operating supply voltage            | V <sub>DD</sub>    | V <sub>DD</sub>                                                                                               | 3.0                 |          | 6.0                  | V           |

| Standby supply voltage              | V <sub>ST</sub>    | V <sub>DD</sub> : RAM, register hold*3                                                                        | 1.8                 |          | 6.0                  | V           |

|                                     | V <sub>IH</sub> 1  | Port C, D, E, F: Output Nch Tr. off                                                                           | 0.7 V <sub>DD</sub> |          | +13.5                | V           |

|                                     | V <sub>IH</sub> 2  | Port A, G: Output Nch Tr. off                                                                                 | 0.7 V <sub>DD</sub> |          | V <sub>DD</sub>      | V           |

| High level input voltage            | V <sub>IH</sub> 3  | INT, SCK, SI: Output Nch Tr. off                                                                              | 0.8 V <sub>DD</sub> |          | +13.5                | V           |

|                                     | V <sub>IH</sub> 4  | $\overline{\text{RES}}$ : V <sub>DD</sub> = 1.8 to 6 V                                                        | 0.8 V <sub>DD</sub> |          | V <sub>DD</sub>      | V           |

|                                     | V <sub>IH</sub> 5  | OSC1: External clock mode                                                                                     | 0.8 V <sub>DD</sub> |          | V <sub>DD</sub>      | V           |

|                                     | V <sub>IL</sub> 1  | Port: Output Nch Tr. off, V <sub>DD</sub> = 4 to 6 V                                                          | V <sub>SS</sub>     |          | 0.3 V <sub>DD</sub>  | V           |

|                                     | V <sub>IL</sub> 2  | Port: Output Nch Tr. off, V <sub>DD</sub> = 3 to 6 V                                                          | V <sub>SS</sub>     |          | 0.25 V <sub>DD</sub> | V           |

|                                     | V <sub>IL</sub> 3  | $\overline{\text{INT}}$ , $\overline{\text{SCK}}$ , SI: Output Nch Tr. off, $V_{\text{DD}}$ = 4 to 6 V        | V <sub>SS</sub>     |          | 0.25 V <sub>DD</sub> | V           |

|                                     | V <sub>IL</sub> 4  | $\overline{\text{INT}}$ , $\overline{\text{SCK}}$ , SI: Output Nch Tr. off, $V_{\text{DD}}$ = 3 to 6 V        | V <sub>SS</sub>     |          | 0.2 V <sub>DD</sub>  | V           |

| I and land in a track and           | V <sub>IL</sub> 5  | OSC1: External clock mode, V <sub>DD</sub> = 4 to 6 V                                                         | V <sub>SS</sub>     |          | 0.25 V <sub>DD</sub> | V           |

| Low level input voltage             | V <sub>IL</sub> 6  | OSC1: External clock mode, V <sub>DD</sub> = 3 to 6 V                                                         | V <sub>SS</sub>     |          | 0.2 V <sub>DD</sub>  | V           |

|                                     | V <sub>IL</sub> 7  | TEST: $V_{DD} = 4 \text{ to } 6 \text{ V}$                                                                    | V <sub>SS</sub>     |          | 0.3 V <sub>DD</sub>  | V           |

|                                     | V <sub>IL</sub> 8  | TEST: V <sub>DD</sub> = 3 to 6 V                                                                              | V <sub>SS</sub>     |          | 0.25 V <sub>DD</sub> | V           |

|                                     | V <sub>IL</sub> 9  | $\overline{\text{RES}}$ : V <sub>DD</sub> = 4 to 6 V                                                          | V <sub>SS</sub>     |          | 0.25 V <sub>DD</sub> | V           |

|                                     | V <sub>IL</sub> 10 | $\overline{\text{RES}}$ : V <sub>DD</sub> = 3 to 6 V                                                          | V <sub>SS</sub>     |          | 0.2 V <sub>DD</sub>  | V           |

| Operating frequency<br>(cycle time) | fop<br>(Tcyc)      | When the 1/3 or 1/4 predivider option is selected, clock must not exceed 4.33 MHz. V <sub>DD</sub> = 3 to 6 V | 200<br>(20)         |          | 1444<br>(2.77)       | kHz<br>(µs) |

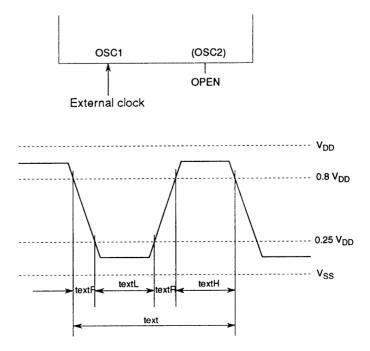

| [External clock conditions]         |                    |                                                                                                               |                     |          |                      |             |

| Frequency                           | text               | OSC1: Fig 1, when clock exceeds 1.444 MHz,                                                                    | 200                 |          | 4330                 | kHz         |

| Pulse width                         | textH, textL       | the 1/3 or 1/4 predivider option must be selected.                                                            | 69                  |          |                      | ns          |

| Rise/fall time                      | textR, textF       | $V_{DD} = 3 \text{ to } 6 \text{ V}$                                                                          |                     |          | 50                   | ns          |

| [Oscillator guaranteed constants]   | 1                  |                                                                                                               |                     | 1        | 1                    |             |

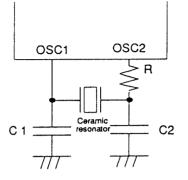

|                                     | Cext               | OSC1, OSC2: Fig 2, V <sub>DD</sub> = 3 to 6 V                                                                 |                     | 270 ± 5% |                      | pF          |

|                                     | Cext               | OSC1, OSC2: Fig 2, V <sub>DD</sub> = 4 to 6 V                                                                 |                     | 270 ± 5% |                      | pF          |

| 2-pin RC oscillator                 | Rext               | OSC1, OSC2: Fig 2, V <sub>DD</sub> = 3 to 6 V                                                                 |                     | 12 ± 1%  |                      | kΩ          |

|                                     | Rext               | OSC1, OSC2: Fig 2, V <sub>DD</sub> = 4 to 6 V                                                                 |                     | 4.7 ± 1% |                      | kΩ          |

| Ceramic                             |                    | Fig 3                                                                                                         |                     | Table 1  |                      |             |

# Electrical Characteristics at Ta = +10 to +40 $^{\circ}C,$ $V_{SS}$ = 0 V, $V_{DD}$ = 3.0 to 6.0 V

| Parameter                           | Symbol Conditions |                                                                                                                                       | Ratings             |                      |                     |      |

|-------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------------------|------|

| Farameter                           | Symbol            | Conditions                                                                                                                            | min                 | typ                  | max                 | Unit |

|                                     | I <sub>IH</sub> 1 | Port C, D, E, F: Output Nch Tr. off (including off leak current of Nch Tr.), $V_{IN}$ = +13.5                                         |                     |                      | +5.0                | μA   |

| High-level input current            | I <sub>IH</sub> 2 | Port A, G: Output Nch Tr. off (including off leak current of Nch Tr.), V <sub>IN</sub> = V <sub>DD</sub>                              |                     |                      | +5.0                | μA   |

|                                     | I <sub>IH</sub> 3 | OSC1: External clock mode, V <sub>IN</sub> = V <sub>DD</sub>                                                                          |                     |                      | +1.0                | μA   |

|                                     | I <sub>IL</sub> 1 | Port: Output Nch Tr. off, V <sub>IN</sub> = V <sub>SS</sub>                                                                           | -1.0                |                      |                     | μA   |

| Low-level input current             | I <sub>IL</sub> 2 | RES: V <sub>IN</sub> = V <sub>SS</sub>                                                                                                | -150                | -50                  |                     | μA   |

|                                     | I <sub>IL</sub> 3 | OSC1: External clock mode, V <sub>IN</sub> = V <sub>SS</sub>                                                                          | -1.0                |                      |                     | μA   |

|                                     | V <sub>OL</sub> 1 | Port: $I_{OL}$ = 10 mA, $V_{DD}$ = 4.0 to 6.0 V                                                                                       |                     |                      | 1.5                 | V    |

| Low-level output current            | V <sub>OL</sub> 2 | Port: $I_{OL}$ = 1 mA, $I_{OL}$ of each port; 1 mA or less $V_{DD}$ = 3.0 to 6.0 V                                                    |                     |                      | 0.5                 | v    |

| [Schmitt characteristics]           |                   |                                                                                                                                       |                     |                      |                     |      |

| Hysteresis voltage                  | VHIS              |                                                                                                                                       |                     | 0.1 V <sub>DD</sub>  |                     | V    |

| High-level threshold voltage        | VtH               | RES, INT, SCK, SI, OSC1 of Schmitt type*4                                                                                             | 0.4 V <sub>DD</sub> |                      | 0.8 V <sub>DD</sub> | V    |

| Low-level threshold voltage         | VtL               |                                                                                                                                       | 0.2 V <sub>DD</sub> |                      | 0.6 V <sub>DD</sub> | V    |

| [Current dissipation]               | ·                 |                                                                                                                                       |                     | ·                    |                     |      |

| 2-pin RC oscillator                 | IDDOP1            | $V_{DD}$ : Output Nch Tr. off at operating, port = $V_{DD}$ ,<br>Fig. 2, fosc = 900 kHz (typ)                                         |                     | 4.5                  | 6                   | mA   |

|                                     | IDDOP2            | V <sub>DD</sub> : Fig 3, 4 MHz, 1/3 predivider                                                                                        |                     | 4.5                  | 7                   | mA   |

|                                     | IDDOP3            | V <sub>DD</sub> : Fig 3, 4 MHz, 1/4 predivider                                                                                        |                     | 4.5                  | 6                   | mA   |

| Ceramic oscillator                  | IDDOP4            | V <sub>DD</sub> : Fig 3, 400 kHz                                                                                                      |                     | 4.0                  | 4.5                 | mA   |

|                                     | IDDOP5            | V <sub>DD</sub> : Fig 3, 800 kHz                                                                                                      |                     | 4.5                  | 6                   | mA   |

| External clock                      | IDDOP6            | V <sub>DD</sub> : 200 kHz to 1444 kHz, 1/1 predivider;<br>600 kHz to 4330 kHz, 1/3 predivider;<br>800 kHz to 4330 kHz, 1/4 predivider |                     | 4.5                  | 7                   | mA   |

|                                     |                   | $V_{DD}$ : Output Nch Tr. off, $V_{DD} = 6 V$                                                                                         |                     | 0.05                 | 10                  | μA   |

| Standby mode                        | IDDst             | $V_{DD}$ : Port = $V_{DD}$ , $V_{DD}$ = 3 V                                                                                           |                     | 0.025                | 5                   | μA   |

| [Oscillator characteristics]        |                   |                                                                                                                                       |                     |                      |                     |      |

|                                     |                   | OSC1, OSC2: Fig 3, fo = 400 kHz                                                                                                       | 384                 | 400                  | 416                 | kHz  |

|                                     | fCFOSC*5          | OSC1, OSC2: Fig 3, fo = 800 kHz                                                                                                       | 768                 | 800                  | 832                 | kHz  |

| Ceramic OSC frequency               |                   | OSC1, OSC2: Fig 3, fo = 1 MHz                                                                                                         | 960                 | 1000                 | 1040                | kHz  |

|                                     |                   | OSC1, OSC2: Fig 3, fo = 4 MHz, 1/3 predivider, 1/4 predivider                                                                         | 3840                | 4000                 | 4160                | kHz  |

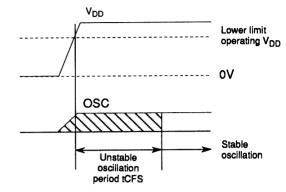

|                                     |                   | Fig 4, fo = 400 kHz                                                                                                                   |                     |                      | 10                  | ms   |

| Stabilization                       | tCFS              | Fig 4, fo = 800 kHz, 1 MHz, 4 MHz, 1/3 predivider, 1/4 predivider                                                                     |                     |                      | 10                  | ms   |

| 2-pin RC oscillator                 | #1000             | OSC1, OSC2: Fig. 2, Cext = 270 pF ± 5%,<br>Fig. 2, Rext = 4.7 kΩ ± 1%, $V_{DD}$ = 4 to 6 V                                            | 666                 | 900                  | 1334                | kHz  |

| frequency                           | fMOSC             | OSC1, OSC2: Fig. 2, Cext = 270 pF ± 5%,<br>Fig. 2, Rext = 12 kΩ ± 1%, V <sub>DD</sub> = 3 to 6 V                                      | 283                 | 400                  | 717                 | kHz  |

| [Pull-up resistance]                |                   |                                                                                                                                       |                     |                      |                     |      |

| I/O port RES:                       | RU                | $\overline{\text{RES}}$ : V <sub>IN</sub> = V <sub>SS</sub> , V <sub>DD</sub> = 5 V                                                   | 50                  | 100                  | 250                 | kΩ   |

| [External reset characteristics]    |                   |                                                                                                                                       |                     |                      |                     |      |

| Reset time                          | tRST              |                                                                                                                                       |                     | See Fig. 5           |                     |      |

| Pin capacitance                     | CP                | f = 1 MHz. $V_{IN}$ = $V_{SS}$ for all pins other than those being tested.                                                            |                     | 10                   |                     | pF   |

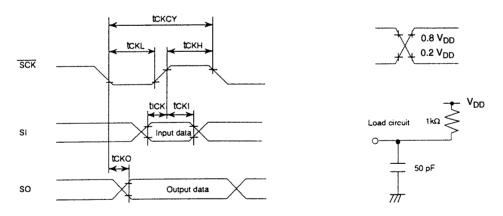

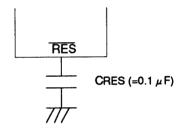

| [Serial clock]                      |                   |                                                                                                                                       |                     |                      |                     | _    |

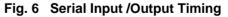

| Input clock cycle time              | tCKCY1            | SCK: Fig. 6                                                                                                                           | 3.0                 |                      |                     | μs   |

| Output clock cycle time             | tCKCY2            | SCK: Fig. 6                                                                                                                           |                     | $64 	imes tCYC^{*6}$ |                     | μs   |

| Input clock low-level pulse width   | tCKL1             | SCK: Fig. 6                                                                                                                           | 1.0                 |                      |                     | μs   |

| Output clock low-level pulse width  | tCKL2             | SCK: Fig. 6                                                                                                                           |                     | $32 \times tCYC$     |                     | μs   |

| Input clock high-level pulse width  | tCKH1             | SCK: Fig. 6                                                                                                                           | 1.0                 |                      |                     | μs   |

| Output clock high-level pulse width | tCKH2             | SCK: Fig. 6                                                                                                                           |                     | $32 \times tCYC$     |                     | μs   |

| [Serial input]                      |                   |                                                                                                                                       |                     |                      |                     |      |

| Data setup time                     | tICK              | SI: Specified from the rising edge of SCK. Fig. 6                                                                                     | 0.4                 |                      |                     | μs   |

|                                     | tCKI              |                                                                                                                                       | 0.4                 |                      | 1                   | 1    |

#### Continued from preceding page.

| Parameter                       | Symbol | Conditions                                                                                                              | Ratings                 |                    |                       | Unit |  |

|---------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|-----------------------|------|--|

| i arameter                      | Gymbol |                                                                                                                         |                         | typ                | max                   | Onic |  |

| [Serial output]                 |        | 1                                                                                                                       |                         |                    |                       |      |  |

| Output delay time               | tCKO   | SO: Specified from the falling edge of $\overline{SCK}$ .<br>Nch OD only, external 1k $\Omega$ , external 50 pF, Fig. 6 |                         |                    | 0.6                   | μs   |  |

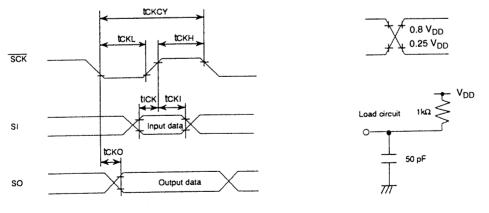

| [Pulse output]                  |        |                                                                                                                         |                         |                    |                       |      |  |

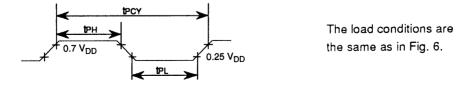

| Period                          | tPCY   |                                                                                                                         |                         | 64 ×tCYC           |                       | μs   |  |

| High-level pulse width          | tPH    | PE0: Fig. 7, tCYC = 4 × system clock period,<br>Nch OD only, external 1 kΩ, external 50 pF                              |                         | 32 × tCYC<br>± 10% |                       | μs   |  |

| Low-level pulse width           | tPL    |                                                                                                                         |                         | 32 × tCYC<br>± 10% |                       | μs   |  |

| [AD conversion characteristics] | •      |                                                                                                                         | ·                       |                    |                       |      |  |

| Resolution                      |        | V <sub>DD</sub> = 4.7 to 5.3 V                                                                                          |                         | 8                  |                       | bits |  |

| Absolute accuracy               |        | $AV+ = V_{DD}, AV- = V_{SS}, V_{DD} = 4.7 \text{ to } 5.3 \text{ V}$                                                    |                         | ±1                 | ±2                    | LSB  |  |

| Conversion time TCA             | TOAD   | AD speed 1/1, at 26 $\times$ tCYC, V <sub>DD</sub> = 4.7 to 5.3 V                                                       | 72 (tCYC<br>= 2.77 μs)  |                    | 312 (tCYC<br>= 12 μs) |      |  |

|                                 |        | AD speed 1/2, at 51 $\times$ tCYC, V <sub>DD</sub> = 4.7 to 5.3 V                                                       | 141 (tCYC<br>= 2.77 μs) |                    | 612 (tCYC<br>= 12 μs) | μs   |  |

|                                 | AV+    | AV+: V <sub>DD</sub> = 4.7 to 5.3 V                                                                                     | AV-                     |                    | V <sub>DD</sub>       | v    |  |

| Reference input voltage AV      |        | AV-: V <sub>DD</sub> = 4.7 to 5.3 V                                                                                     | V <sub>SS</sub>         |                    | AV+                   | V    |  |

| Reference input current range   | IRIF   | AV+, AV–: AV+ = $V_{DD}$ , $V_{DD}$ = 4.7 to 5.3 V, AV– = $V_{SS}$                                                      | 75                      | 150                | 300                   | μA   |  |

| Analog input voltage range      | VAIN   | AD0 to AD7: V <sub>DD</sub> = 4.7 to 5.3 V                                                                              | AV-                     |                    | AV+                   | V    |  |

| Analog port input current       | IAIN   | Port pins AD0 to AD7 Including output OFF leakage current. VAIN = $V_{DD}$ , $V_{DD}$ = 4.7 to 5.3 V                    |                         |                    | 1                     | μA   |  |

|                                 |        | Port pins AD0 to AD7<br>VAIN = $V_{SS}$ , $V_{DD}$ = 4.7 to 5.3 V                                                       | -1                      |                    |                       |      |  |

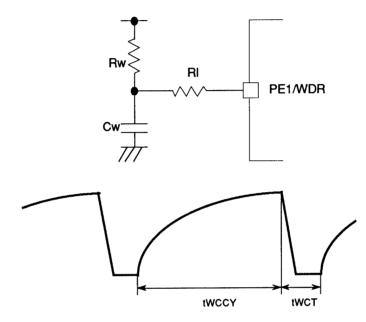

| [Watchdog timer]                | •      |                                                                                                                         |                         |                    |                       |      |  |

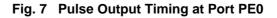

|                                 | Cw     | WDR: V <sub>DD</sub> = 3 to 6 V                                                                                         |                         | 0.1 ± 5%           |                       | μF   |  |

| Guaranteed constant*7           | Rw     | WDR: V <sub>DD</sub> = 3 to 6 V                                                                                         |                         | 680 ± 1%           |                       | kΩ   |  |

|                                 | RI     | WDR: $V_{DD} = 3 \text{ to } 6 \text{ V}$                                                                               |                         | 100 ± 1%           |                       | Ω    |  |

| Clear time (discharge)          | tWCT   | WDR: Fig. 8, V <sub>DD</sub> = 3 to 6 V                                                                                 | 100                     |                    |                       | μs   |  |

| Clear time (charge)             | tWCCY  | WDR: Fig. 8, V <sub>DD</sub> = 3 to 6 V                                                                                 | 36                      |                    |                       | ms   |  |

|                                 | Cw     | WDR: $V_{DD} = 4 \text{ to } 6 \text{ V}$                                                                               |                         | 0.047 ± 5%         |                       | μF   |  |

| Guaranteed constant*7           | Rw     | WDR: $V_{DD} = 4 \text{ to } 6 \text{ V}$                                                                               |                         | 680 ± 1%           |                       | kΩ   |  |

|                                 | RI     | WDR: $V_{DD} = 4 \text{ to } 6 \text{ V}$                                                                               |                         | 100 ± 1%           |                       | Ω    |  |

| Clear time (discharge)          | tWCT   | WDR: Fig. 8, V <sub>DD</sub> = 4 to 6 V                                                                                 | 40                      |                    |                       | μs   |  |

| Clear time (charge)             | tWCCY  | WDR: Fig. 8, V <sub>DD</sub> = 4 to 6 V                                                                                 | 18                      |                    |                       | ms   |  |

Note: 1. The LC65E1104 will accept input voltages up to the generated oscillator amplitude if the oscillator circuit in figure 4 with circuit constants in the guaranteed constants ranges is driven from within the IC.

2. Average over a 100 ms period

The operating supply voltage V<sub>DD</sub> must be held until standby mode is enterd after the execution of a HALT instruction. The PA3 pin must be free from chattering during the HALT instruction cycle.

4. The OSC1 pin input circuit has Schmitt trigger characteristics when the 2-terminal RC oscillator option or the external clock oscillator option is selected.

5. fCFOSC: oscillator frequency. The center frequency of a ceramic oscillator has a tolerance range of about 1% around the nominal value specified by the manufacturer of the oscillator element. For details, refer to the specifications of the ceramic resonator.

6. TCYC =  $4 \times$  system clock period

7. If the LC65E1104 is used in an environment subject to condensation, leakage between PE1 and adjacent pins and leakage associated with external RCA circuits require special attention.

Fig. 4 Oscillator Stabilization Period

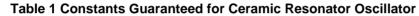

#### Table 1 Constants Guaranteed for Ceramic Resonator Oscillator

| 4 MHz (Murata)                | C1 | 33 pF ± 10%  |

|-------------------------------|----|--------------|

| CSA4.00MG                     | C2 | 33 pF ± 10%  |

| CST4.00MGW (built-in C)       | R  | 0 Ω          |

| 4 MHz (Kyocera)               | C1 | 33 pF ± 10%  |

| KBR4.0 MSA                    | C2 | 33 pF ± 10%  |

| KBR4.0MKS (built-in C)        | R  | 0 Ω          |

|                               | C1 | 100 pF ± 10% |

| 1 MHz (Murata)<br>CSB1000J    | C2 | 100 pF ± 10% |

|                               | R  | 2.2 kΩ       |

|                               | C1 | 100 pF ± 10% |

| 1 MHz (Kyocera)<br>KBR1000F   | C2 | 100 pF ± 10% |

|                               | R  | 0 kΩ         |

|                               | C1 | 100 pF ± 10% |

| 800 kHz (Murata)<br>CSB800J   | C2 | 100 pF ± 10% |