**CMOS LSI**

SANYO

No.2577B

LC6538D

SINGLE-CHIP 4-BIT MICROCOMPUTER FOR LARGE-SCALE CONTROL-ORIENTED APPLICATIONS

(with FLT Controller/Drivers, Comparator, PWM Output, 8K Byte-ROM)

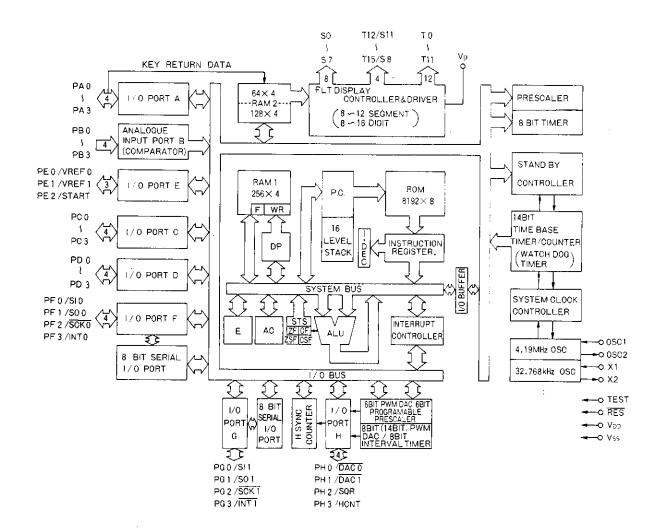

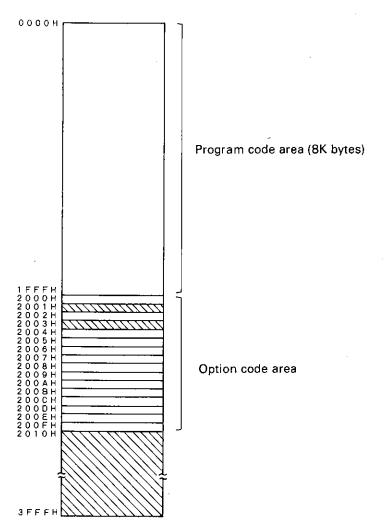

The LC6538D is a single-chip 4-bit microcomputer placed in a 64-pin package. It contains a high-speed CPU (minimum cycle time: 0.92 $\mu$ s) which is the heart of the LC6538D, an 8K-byte ROM, a 448-word RAM, an automatic FLT display controller/drivers, a dual 8-bit serial I/O port, an 8-bit timer, an interval timer capable of delivering 14-bit PWM output signal or 8-bit + 6-bit PWM output signal, a 14-bit time-keeping time base timer which can be also used as an event counter or watchdog timer, a 4-channel comparator input port, a horizontal sync detection counter, and provides 8 interrupt sources with 4 vector addresses. The LC6358D has 2 crystal oscillators (4.19MHz and 32.768kHz) which make it possible to select either clock signal for system clock or time-keeping as required and also make it possible to use either clock signal to continue time-keeping in the standby mode. The LC6538D is especially suited for use in VCR, CD, ECR applications. In particular, the LC6538D is so designed as to facilitate processing of the time-keeping/timer function, voltage/frequency synthesizer tuner control, remote control signal reception, tape counter, etc. on a single chip. Since the FLT display controller has the static output mode and structure capable of being also used as a general-purpose output port, the LC6538D is also especially suited for use in VCR, CD system/servo controller applications.

#### **Features**

- 78 instructions

- On-chip 8192-byte ROM, 448x4-bit RAM (64x4 bits of the 448x4-bit RAM are used both for data memory and display, KEY Return Data memory.)

- Minimum instruction cycle time:  $0.92\mu s$  (4.33MHz,  $V_{DD} \ge 4.5V$ )  $61\mu s$  (32.768kHz,  $V_{DD} \ge 2.7V$ )

- Power-down function available when a system clock signal is selected (program-selectable)

- When 4.19MHz clock signal is selected: 0.95μs, 1.9μs, 30.6μs

- When 32.768kHz clock signal is selected: 61 us

- Working register/flag function

- (16 flags + 8 working registers) x 4 banks

- · Stack level: 16 levels

- I/O port: 55 pins in all

- Input-only port

4 pins (common with comparator input)

- Input/output common port 27 pins (high-current port for LED drive: 8 pins)

- Output-only port

24 pins (FLT direct drive capability, high-current output for digits: 16 pins)

- On-chip FLT display controller

- Number of segments: 8 to 12 Program-selectable

- Number of digits: 16 to 8 Program-selectable

- On-chip automatic KEY Return Data input function

- 4x15-bit

- Timer: 3 channels

Digit interrupt

- 6-bit prescaler + 8-bit programmable timer

- Interval timer: Common with PWM DAC, capable of frequency division for melody generation

- Time-keeping time base timer: On-chip 14-stage frequency divider

- PWM DAC output: Common with Timer 1 (Interval Timer)

- 6-bit PWM DAC + 8-bit PWM DAC or 14-bit PWM DAC

- Serial input/output interface (LSB first)

- 8-bit input/output x 2 channels or 16-bit input/output x 1 channel

- Interrupt function: 8 sources, 4 vector addresses

- External interrupt

Timer interrupt

Serial I/O interrupt

2 lines

2 lines

2 lines

- On-chip comparator for AFC signal detection (4 channels)

1 line

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

- · On-chip watchdog timer: Common with time-keeping time base timer (Option)

- · On-chip 9-bit counter for horizontal sync detection

- On-chip OSC stabilizing time wait function in the reset mode

- · OSC curcuit: 2 channels

- Main clock: 4.19MHz crystal OSC or 4.0MHz ceramic resonator OSC

- Subclock: 32.768kHz crystal OSC

- Standby function: 2 modes of HALT and HOLD

- Supply voltage: 2.7 to 6.0V

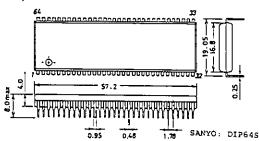

- Package: DIP-64S

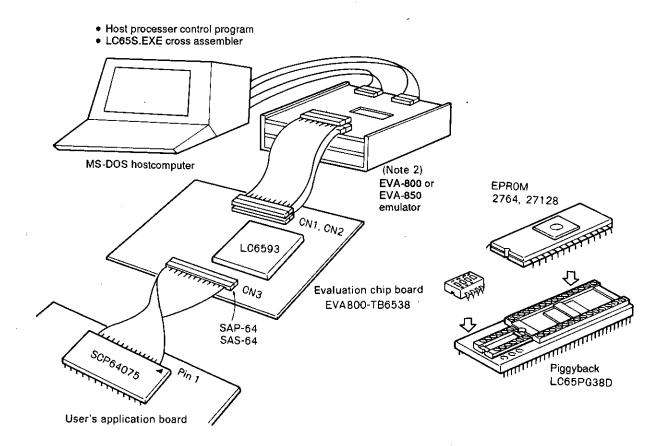

- Evaluation LSI: LC6593 (evaluation chip) + EVA800-TB6593 (evaluation chip board)

LC65PG38D (piggyback)

#### System Block Diagram

### **Development Support Tools**

The follwoing tools are provided to support the program development for the LC6538D microcomputer.

(1) User's Manual

"LC6538D User's Manual" (Issued in February, 1988)

(2) Developement Tool Manual

This contains the basic information on the EVA-800. For more detailed information on the LC6538D, refer to the description of Developement Support Tools in "LC6538D User's Manual".

(3) Development Tools

① For program development (Note 1)

i. MS-DOS-based host system and cross-assembler:

ii. Cross assembler ..... MS-DOS base cross assembler: (LC65S.EXE)

② For program evaluation

i. Evaluation chip : LC6593ii. Piggyback microcomputer: LC65PG38D

iii. Emulator The EVA-800 controller board and evaluation chip board, or the EVA-850

emulator and evaluation chip board

### Appearance of Development Support System

(Note 1) MS-DOS: Trademark of MicroSoft Corporation

(Note 2) The EVA-800, EVA-850 is a general term for emulator. A suffix (A, B, ---) is added at the end of EVA-800e EVA-850 as the EVA-800, EVA-850 is improved to be a newer version. Do not use the EVA-800, EVA-850 with no suffix added.

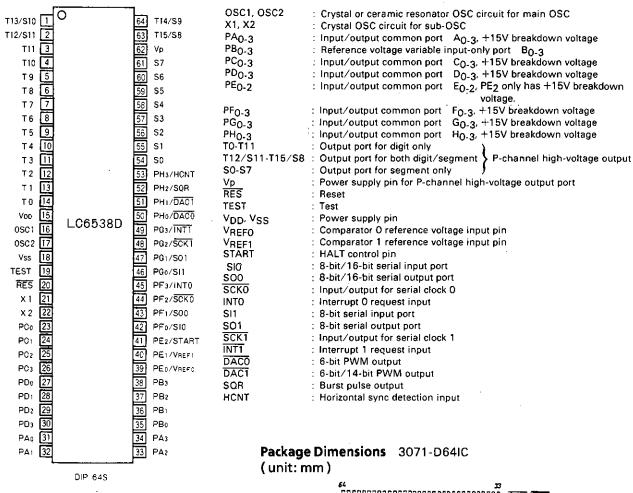

#### Pin Assignment

### Pin Description

PU: Output with pull-up MOS OD: Open drain output

| Pin Name                           | Pins | 1/0 | Functions                                                                                                                                                                               | Output<br>Driver                                            | Option                                                                  | During<br>Reset           |

|------------------------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------|

| V <sub>DD</sub>                    | 1    |     | Power supply pin                                                                                                                                                                        | <b>–</b> .                                                  | -                                                                       |                           |

| V <sub>SS</sub>                    | 1    |     |                                                                                                                                                                                         |                                                             |                                                                         |                           |

| TEST                               | 1    | 1   | LSI test pin. Must be connected to VSS.                                                                                                                                                 | _                                                           | _                                                                       | _                         |

| RES                                | 1    | 1   | System reset input<br>Initial reset at RES=L                                                                                                                                            | _                                                           | _                                                                       | _                         |

| OSC1                               | 1    | l l | Pin used for main system clock OSC                                                                                                                                                      |                                                             | <del></del>                                                             |                           |

| OSC2                               | 1    | 0   | For the external clock mode, the OSC2 is made open and the external clock is applied to the OSC1.  With feedback resistance                                                             |                                                             |                                                                         |                           |

| X1                                 | 1    | ı   | Pin used for sub-clock OSC                                                                                                                                                              |                                                             | <u> </u>                                                                | _                         |

| X2                                 | 1    | 0   | For the external clock mode, the X2 is made open and the external clock is applied to the X1.  With feedback resistance, damping resistance                                             |                                                             |                                                                         |                           |

| TO to T11                          | 12   | 0   | Output for FLT digit only Outputs a fixed address in the display RAM at the static mode.                                                                                                | Pch high<br>breakdown<br>voltage<br>High-current<br>type    | Presence or<br>absence of pull-<br>down resistance<br>(in bit units)    | <b>L</b> .                |

| T12/S11<br>to T15/S8               | 4    | 0   | Output for FLT digit/segment Outputs a fixed address in the display RAM at the static mode.                                                                                             | Pch high<br>breakdown<br>voltage<br>High-current<br>type    | Presence or<br>absence of pull-<br>down resistance<br>(in bit units)    | L                         |

| S0 to S7                           | 8    | 0   | Output for FLT segment only Outputs a fixed address in the display RAM at the static mode.                                                                                              | Pch high<br>breakdown<br>voltage<br>Medium-<br>current type | Presence or<br>absence of pull-<br>down resistance<br>(in bit units)    | L                         |

| Vρ                                 | 1    |     | Power supply pin for FLT output pull-down resistance                                                                                                                                    | _                                                           | _                                                                       |                           |

| PA <sub>O</sub> to PA <sub>3</sub> | 4    | 1/0 | 4-bit and single-bit input/output The input is of low threshold type for key scan and has the function to automatically fetch the key scan data into the RAM.                           | +15V<br>breakdown<br>voltage<br>Medium-<br>current type     | PU or OD to be<br>specified in bit<br>units                             | н                         |

| PB <sub>O</sub> to PB <sub>3</sub> | 4    | 1   | With 4-channel independint comparator Internal/external reference voltage selectable 4-bit/single-bit input The input function stops at the low-speed mode (1/32 mode, sub-clock mode). | _                                                           | <u> </u>                                                                | Input<br>function<br>stop |

| PCO to PC3                         | 4    | 1/0 | 4-bit and single-bit input/output                                                                                                                                                       | +15V<br>breakdown<br>voltage<br>High-current<br>type        | PU or OD to<br>be specified<br>in bit units Output at the<br>reset mode | H/L (option)              |

| PD <sub>O</sub> to PD <sub>3</sub> | 4    | 1/0 | 4-bit and single-bit input/output                                                                                                                                                       | +15V<br>breakdown<br>voltage<br>High-current<br>type        | PU or OD to<br>be specified<br>in bit units Output at the<br>reset mode | H/L (option)              |

### LC6538D

## Continued from proceding page.

| Pin Name                           | Pins | 1/0 | Functions                                                                                                                                                                                                            | Output<br>Driver                                        | Option                                      | During<br>Reset |

|------------------------------------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|-----------------|

| PE <sub>O</sub> to PE <sub>2</sub> | 3    | 1/0 | 3-bit and single-bit input/output PEO/VREFO Common with external reference voltage input of PB1.3 PE1/VREF1 Common with external reference voltage input of PB0 PE2/START Common with HALT mode control START        | breakdown                                               | PU or OD to be<br>specified in bit<br>units | Н               |

| PF <sub>0</sub> to PF <sub>3</sub> | 4    | 1/0 | 4-bit and single-bit input/output PF0/SI0 Common with serial input SI0 PF1/SO0 Common with serial output SO0 PF2/SCKO Common with serial clock input/output SCKO PF3/INTO Common with INTO interrupt input           | +15V<br>breakdown<br>voltage<br>Medium-<br>current type | PU or OD to be<br>specified in bit<br>units | Н               |

| PG <sub>O</sub> to PG <sub>3</sub> | 4    | 1/0 | 4-bit and single-bit input/output PG0/SI1 Common with serial input SI1 PG1/SO1 Common with serial output SO1 PG2/SCK1 Common with serial clock input/output SCK1 PG3/INT1 Common with INT1 interrupt input           | +15V<br>breakdown<br>voltage<br>Medium-<br>current type | PU or OD to be<br>specified in bit<br>units | Н               |

| PH <sub>O</sub> to PH <sub>3</sub> | 4    | 1/0 | 4-bit and single-bit input/output PH0/DACO Common with 6-bit PWM D/A output PH1/DAC1 Common with 8/14-bit PWM D/A output PH2/SQR Common with burst pulse output PH3/HCNT Common with horizontal sync detection input | +15V<br>breakdown<br>voltage<br>Medium-<br>current type | PU or OD to be<br>specified in bit<br>units | н               |

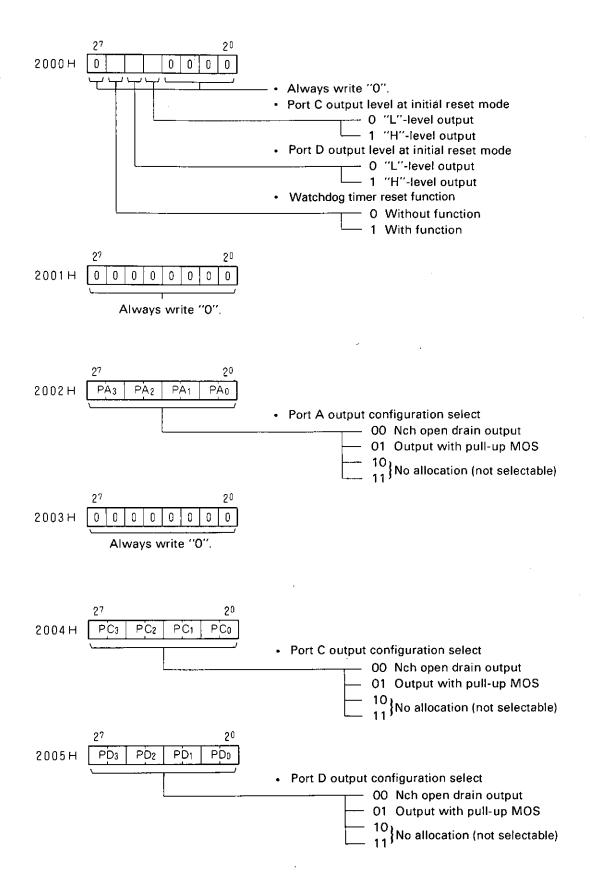

#### **User Options**

Option of ports C, D Output Level at the Reset Mode.

For input/output common ports C, D, either of the following two output levels may be selected in a group of 4 bits during reset by option.

| Option Name                             | Conditions, etc.            |

|-----------------------------------------|-----------------------------|

| Output at the reset mode:     "H" level | All of 4 bits of ports C, D |

| Output at the reset mode:     "L" level | All of 4 bits of ports C, D |

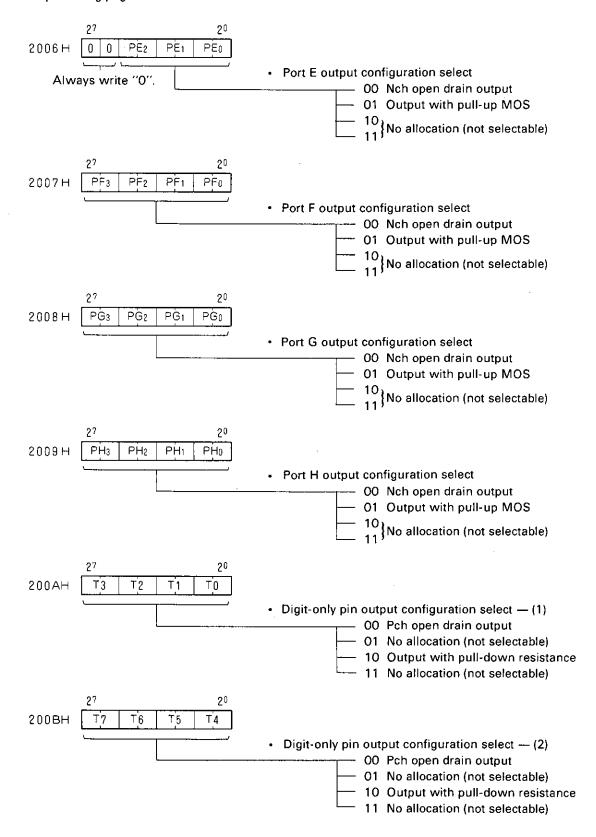

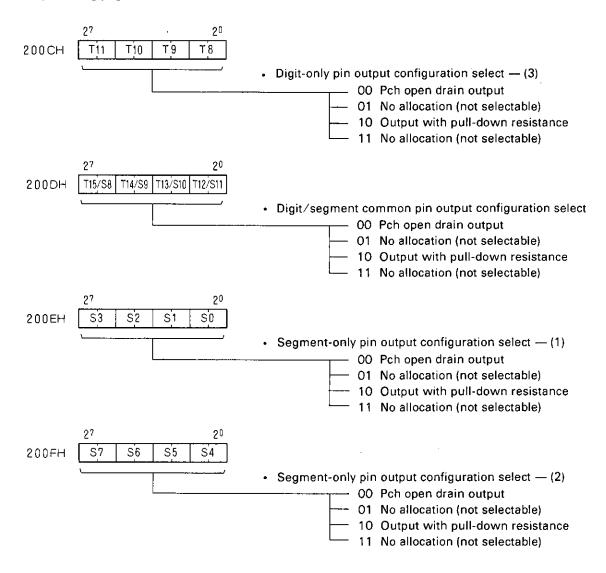

2) Option of Port Output Configuration

For each input/output common port, either of the following two output configurations may be selected by option (in bit units).

| Option Name                         | Circuit | Conditions, etc.              |

|-------------------------------------|---------|-------------------------------|

| 1. Open drain output                |         | Ports A, C, D, E, F, G, H     |

|                                     | <u></u> | T0~T11, T12/S11~T15/S8, S0~S7 |

| 2. Output with pull-up resistance   |         | Ports A, C, D, E, F, G, H     |

| 3. Output with pull-down resistance | RD Vp   | T0~T11, T12/S11~T15/S8, S0~S7 |

### 3) Watchdog Reset Option

The presence or absence of the time base timer-used watchdog reset function may be selected by option.

| Option Name                     | Conditions, etc.                                                                                                                                                                             |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| With watchdog reset function    | Programming must be made so that the time base interrupt request flag is reset within a certain period of time not to cause the watchdog reset to be performed as long as no runaway occurs. |

| Without watchdog reset function |                                                                                                                                                                                              |

### LC6538D Electrical Characteristics

1. Absolute Maximum Ratings at Ta=25°C, VSS=0V

| Parameter              | Symbol               | Applicable Pins, Remarks | Conditions                           | Limits                                                       | Unit    |

|------------------------|----------------------|--------------------------|--------------------------------------|--------------------------------------------------------------|---------|

| Maximum Supply         | V <sub>DD</sub> max  | V <sub>DD</sub>          |                                      | −0.3 to +7.0                                                 | V       |

| Voltage                |                      | V0.0000                  |                                      | A)1                                                          |         |

| Output Voltage         | V <sub>O</sub> (1)   | X2,OSC2                  |                                      | Allowable up to<br>voltage generated                         | V       |

|                        | V <sub>O</sub> (2)   | To to T11,               |                                      | Voltage generated<br>VDD-45 to                               | V       |

|                        | V ((2)               | T12/S11 to               |                                      | V <sub>DD</sub> +0.3                                         |         |

|                        | 1                    | T15/S8, S0 to S7         |                                      | 100 10.0                                                     |         |

| Input Voltage          | V <sub>I</sub> (1)   | X1, OSC1                 |                                      | Allowable up to                                              | V       |

| ,                      | 1                    |                          |                                      | voltage generated                                            |         |

|                        | V <sub>I</sub> (2)   | TEST, RES, PBO           |                                      | -0.3 to V <sub>DD</sub> +0.3                                 | V       |

|                        | _                    | to 3, OSC1, X1 at        |                                      |                                                              |         |

|                        |                      | external clock           |                                      |                                                              |         |

|                        |                      | mode                     |                                      |                                                              |         |

|                        | V <sub>I</sub> (3)   | Vp                       |                                      | V <sub>DD</sub> -45 to                                       | V       |

|                        |                      |                          |                                      | V <sub>DD</sub> +0.3                                         | L.,     |

| Input/Output Voltage   | V <sub>IO</sub> (1)  | Ports                    | At open drain                        | −0.3 to +15                                                  | V       |

|                        | \( \( \) \( \)       | A,C,D,E2,F,G,H           | output option                        | 0.2 += \/- = 1.0.2                                           |         |

|                        | V <sub>IO</sub> (2)  | Ports E0,E1              | At pull-up MOS-                      | -0.3 to V <sub>DD</sub> +0.3<br>-0.3 to V <sub>DD</sub> +0.3 | V       |

|                        |                      | A,C,D,E2,F,G,H           | provided output                      | 0.5 to vDD±0.3                                               | , v     |

|                        |                      | 7,0,0,1,24,1,0,11        | option                               |                                                              |         |

| Peak Output Current    | I <sub>OP</sub> (1)  | Ports A,E,F,G,H          | орион                                | -2 to 10                                                     | mA      |

| a mapper warrant       | I <sub>OP</sub> (2)  | Ports C,D                | ,                                    | -2 to 30                                                     | mA      |

|                        | IOP(3)               | T0 to T11,               |                                      | -30 to 0                                                     | mA      |

|                        |                      | T12/S11 to               |                                      |                                                              |         |

|                        |                      | T15/S8                   |                                      |                                                              |         |

|                        | IOP(4)               | S0 to S7                 |                                      | -10 to 0                                                     | mΑ      |

| Average Output Current | IOA(1)               | Ports A,E,F,G,H          | Per pin                              | −2 to 10                                                     | mA      |

|                        |                      |                          | Average over the                     |                                                              |         |

|                        |                      |                          | period of 100 msec.                  |                                                              | · · · · |

|                        | I <sub>OA</sub> (2)  | Ports C,D                | Per pin                              | −2 to 30                                                     | mA      |

|                        |                      |                          | Average over the period of 100 msec. |                                                              |         |

|                        | 10.4(2)              | T0 to T11,               | Per pin                              | -30 to 0                                                     | mA      |

|                        | IOA(3)               | T12/\$11 to              | Average over the                     | -30 10 0                                                     | m#      |

|                        |                      | T15/S8                   | period of 100 msec.                  |                                                              |         |

|                        | I <sub>OA</sub> (4)  | S0 to S7                 | Per pin                              | -10 to 0                                                     | m.A     |

|                        | 1000                 |                          | Average over the                     |                                                              |         |

|                        |                      |                          | period of 100 msec.                  |                                                              |         |

|                        | ΣI <sub>OA</sub> (1) | Ports A,E                | Total current of all                 | -14 to 20                                                    | mΑ      |

|                        |                      |                          | applicable pins                      |                                                              |         |

|                        |                      |                          | Average over the                     |                                                              |         |

|                        |                      |                          | period of                            |                                                              |         |

|                        | 51 10)               | - B . F C !!             | 100msec.                             | 24.00                                                        |         |

|                        | ΣΙΟΑ(2)              | Ports F,G,H              | Total current of all                 | -24 to 60                                                    | m/      |

|                        |                      |                          | applicable pins Average over the     |                                                              |         |

|                        |                      | · [                      | period of                            |                                                              |         |

|                        |                      |                          | 100msec.                             |                                                              |         |

|                        | ΣΙ <sub>ΟΑ</sub> (3) | Ports C,D                | Total current of all                 | -16 to 80                                                    | m/      |

|                        |                      | 10100 072                | applicable pins                      |                                                              |         |

|                        |                      |                          | Average over the                     |                                                              |         |

|                        |                      |                          | period of                            |                                                              |         |

| •                      |                      |                          | 100msec.                             |                                                              |         |

|                        | ΣΙΟΑ(4)              | T0 to T11,               | Total current of all                 | -100 to 0                                                    | mΑ      |

|                        |                      | T12/S11 to               | applicable pins                      |                                                              |         |

|                        |                      | T15/S8, S0 to S7         | Average over the                     |                                                              |         |

|                        |                      |                          | period of                            |                                                              |         |

| Allowable Barries      | Del ev:              | DIDEAC                   | 100msec.                             |                                                              |         |

| Allowable Power        | Pd max               | DIP64S                   | T <sub>a</sub> =-30 to<br>+70° C     | 600                                                          | mV      |

| Dissipation            | Tarra                |                          | +70 C                                | 20/ 170                                                      | 0.0     |

| Operating Temperature  | Topr                 |                          |                                      | -30 to +70<br>-55 to +125                                    | °C      |

| Storage Temperature    | Tstg                 |                          |                                      | -95 10 1125                                                  | ٠.ر     |

2. Allowable Operating Conditions at Ta=-30 to +70°C, VSS=0V

| Parameter                                        | Symbol               | Applicable Pins,<br>Remarks | Conditions                                             | V <sub>DD</sub> [V]      | min                                | Limits<br>typ   | max                                        | Unit |

|--------------------------------------------------|----------------------|-----------------------------|--------------------------------------------------------|--------------------------|------------------------------------|-----------------|--------------------------------------------|------|

| Operating Supply<br>Voltage                      | V <sub>DD</sub> (1)  | V <sub>DD</sub>             | 0.92 <i>μ</i> s≦Tcyc<br><1.9 <i>μ</i> s                | _                        | 4.5                                |                 | 6.0                                        | V    |

| (Including supply<br>voltage at standby<br>mode) | V <sub>DD</sub> (2)  | V <sub>DD</sub>             | 1.9 <i>μ</i> s≦Tcyc ≦6 <i>μ</i> s                      | _                        | 4.0                                |                 | 6.0                                        | ٧    |

|                                                  | V <sub>DD</sub> (3)  | $V_{DD}$                    | 6 <i>μ</i> s <tcyc ≦67<i="">μs</tcyc>                  | _                        | 3.0                                |                 | 6.0                                        | V    |

|                                                  | V <sub>DD</sub> (4)  | V <sub>DD</sub>             | 4.19MHz OSC stop,<br>32kHz OSC<br>operating            | _                        | 2.7                                |                 | 6.0                                        | V    |

| Memory Retention<br>Supply Voltage               | V <sub>ST</sub>      | V <sub>DD</sub>             | At operation<br>completely stopped<br>mode (HOLD mode) | _                        | 1.8                                |                 | 6.0                                        | V    |

| "H"-Level Input                                  | V <sub>IH</sub> (1)  | Port A of OD type           | Output Nch Tr OFF                                      |                          | 1.90                               |                 | 13.5                                       | V    |

| Voltage                                          | V <sub>IH</sub> (2)  | Port A of PU type           | Output Nch Tr OFF                                      | 3.0 to 6.0               | 1.90                               |                 | VDD                                        | v    |

|                                                  | V <sub>IH</sub> (3)  | Ports C, D of OD            | Output Nch Tr OFF                                      | 4.5 to 6.0               | 0.70V <sub>DD</sub>                |                 | 13.5                                       |      |

|                                                  | 7111(-7              | type                        |                                                        | 3.0 to 6.0               | 0.75V <sub>DD</sub>                |                 | 13.5                                       |      |

|                                                  | V <sub>IH</sub> (4)  | Ports C, D of PU            | Output Nch Tr OFF                                      | 4.5 to 6.0               | 0.70V <sub>DD</sub>                |                 | V <sub>DD</sub>                            | V    |

|                                                  | VIH(-+)              | type                        | Output Non II OI I                                     | 3.0 to 6.0               | 0.75V <sub>DD</sub>                |                 | VDD<br>QQV                                 | Ÿ    |

|                                                  | V <sub>IH</sub> (5)  | Ports E2, F to H of         | Output Nch Tr OFF                                      | 4.5 to 6.0               | 0.75V <sub>DD</sub>                |                 | 13.5                                       | V    |

|                                                  | *1U(0)               | OD type                     | Output Non II O                                        | 3.0 to 6.0               | 0.80V <sub>DD</sub>                | · · · · · · · · | 13.5                                       |      |

|                                                  | V <sub>IH</sub> (6)  | Ports E2, F to H of         | Output Nch Tr OFF                                      | 4.5 to 6.0               | 0.75V <sub>DD</sub>                |                 | V <sub>DD</sub>                            | V    |

|                                                  | AIH(O)               | PU type                     | Output Non II OII                                      | 3.0 to 6.0               |                                    |                 | V <sub>DD</sub>                            | ľů   |

|                                                  | V <sub>IH</sub> (7)  | Ports EO, E1                | Output Nch Tr OFF                                      | 4.5 to 6.0               | 0.75V <sub>DD</sub>                |                 | V <sub>DD</sub>                            | ľ    |

|                                                  | *10(*)               | . 0.10 20, 21               | output Hom H of F                                      | 3.0 to 6.0               | 0.80V <sub>DD</sub>                |                 | V <sub>DD</sub>                            | Ÿ    |

| į                                                | V <sub>IH</sub> (8)  | Port B                      | At internal reference voltage mode                     | 4.0 to 6.0               | 0.65V <sub>DD</sub>                |                 | VDD                                        | V    |

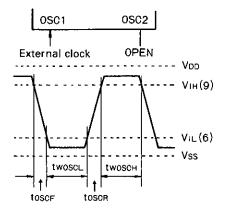

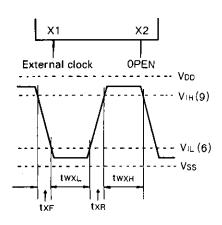

|                                                  | V <sub>IH</sub> (9)  | OSC1, X1                    | Fig. 5, Fig. 6                                         | 4.5 to 6.0               |                                    |                 | $V_{DD}$                                   | V    |

|                                                  | V <sub>IH</sub> (10) | RES                         | Fig. 7                                                 | 3.0 to 6.0<br>4.5 to 6.0 | 0.80V <sub>DD</sub>                |                 | V <sub>DD</sub><br>V <sub>DD</sub>         | V    |

|                                                  | ·                    |                             | _                                                      | 1.8 to 6.0               | 0.80V <sub>DD</sub>                |                 | V <sub>DD</sub>                            | V    |

| "L"-Level Input                                  | V <sub>IL</sub> (1)  | Port A                      | Output Nch Tr OFF                                      |                          | VSS                                |                 | 0.5                                        | V    |

| Voltage                                          | 14 (0)               |                             | 0                                                      | 3.0 to 6.0               | Vss                                |                 | 0.35                                       |      |

|                                                  | V <sub>IL</sub> (2)  | Ports C, D                  | Output Nch Tr OFF                                      |                          | Vss                                |                 | 0.30V <sub>DD</sub>                        | V    |

|                                                  | 14(2)                | Do-to E E C U               | Outsid Nah Ta OFF                                      | 3.0 to 6.0               | VSS                                |                 | 0.25V <sub>DD</sub>                        | V    |

|                                                  | V <sub>IL</sub> (3)  | Ports E, F, G, H            | Output Nch Tr OFF                                      | 3.0 to 6.0               | V <sub>SS</sub><br>V <sub>SS</sub> |                 | 0.25V <sub>DD</sub><br>0.20V <sub>DD</sub> | V    |

|                                                  | V <sub>IL</sub> (4)  | Port B                      | At internal                                            | 4.0 to 6.0               | VSS                                |                 | 0.35V <sub>DD</sub>                        | Ť    |

|                                                  | יונייי               | 10112                       | reference voltage<br>mode                              | 1.0 10 0.0               |                                    |                 | 0.00100                                    |      |

|                                                  | V <sub>IL</sub> (5)  | RES                         | Fig. 7                                                 | 4.5 to 6.0               | V <sub>SS</sub>                    |                 | 0.25V <sub>DD</sub>                        | V    |

|                                                  |                      |                             |                                                        | 1.8 to 6.0               | Vss                                |                 | 0.20V <sub>DD</sub>                        | V    |

|                                                  | V <sub>IL</sub> (6)  | OSC1, X1                    | Fig. 5, Fig. 6                                         | 4.5 to 6.0               | VSS                                |                 | 0.30V <sub>DD</sub>                        | V    |

|                                                  |                      |                             |                                                        | 3.0 to 6.0               | VSS                                |                 | 0.20V <sub>DD</sub>                        | V    |

|                                                  | V <sub>IL</sub> (7)  | TEST                        |                                                        | 4.5 to 6.0               |                                    |                 | 0.30V <sub>DD</sub>                        |      |

| Common Marie                                     |                      |                             | 04                                                     | 3.0 to 6.0               | V <sub>SS</sub>                    |                 | 0.25V <sub>DD</sub>                        |      |

| Common-Mode Input<br>Voltage Range               | Vсмм                 | Port B                      | Offset voltage<br>≦VOFS                                | 4.5 to 6.0               | V <sub>SS</sub> +1.0               |                 | V <sub>DD</sub> -1.5                       |      |

| Instruction Cycle Time                           | TCYC                 | 0001                        | (Note 1)                                               | (Note 1)                 | 0.92                               |                 | 67                                         |      |

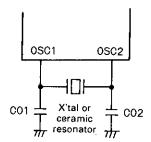

| Main Clock OSC<br>Frequency Range                | fosc                 | OSC1, OSC2                  | Crystal, ceramic resonator OSC (Note 1) Fig. 1         | 3.0 to 6.0               | 3.5                                | 4.19            | 4.2                                        | MHz  |

| Main Clock Input<br>Frequency Range              | fEOSC                | OSC1                        | External clock<br>(Note 1) Fig. 5                      | 3.0 to 6.0               | 2.0                                |                 | 4.33                                       | MH   |

| Main Clock Input "H"-Level Pulse Width           | twosch               | OSC1                        | External clock<br>Fig. 5                               | 3.0 to 6.0               | 100                                |                 |                                            | ns   |

| Main Clock Input "L"-Level Pulse Width           | twoscl               | OSC1                        | External clock<br>Fig. 5                               | 3.0 to 6.0               | 100                                |                 |                                            | ns   |

| Main Clock Rise Time                             | tOSCR                | OSC1                        | External clock<br>Fig. 5                               | 3.0 to 6.0               |                                    |                 | 30                                         | ns   |

### Continued from proceding page.

| Parameter                                | Symbol          | Applicable    | Conditions               |                     |      | Limits       |     |      |

|------------------------------------------|-----------------|---------------|--------------------------|---------------------|------|--------------|-----|------|

| raiameter                                | Syllibol        | Pins, Remarks | Conditions               | V <sub>DD</sub> [V] | min  | typ          | max | Unit |

| Main Clock Fall Time                     | tOSCF           | OSC1          | External clock<br>Fig. 5 | 3.0 to 6.0          |      |              | 30  | ns   |

| Main Clock OSC<br>Constant               | CO1, CO2        |               | Fig. 1                   | 3.0 to 6.0          | Refe | r to Table 1 |     | -    |

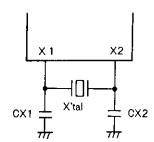

| Sub-clock OSC<br>Frequency Range         | fx              | X1, X2        | Crystal OSC<br>Fig. 2    | 2.7 to 6.0          | 30   | 32.768       | 35  | kHz  |

| Sub-clock Input<br>Frequency Range       | fEX             | X1            | External clock<br>Fig. 6 | 2.7 to 6.0          | 30   |              | 35  | kHz  |

| Sub-clock Input<br>"H"-Level Pulse Width | tWXH            | X1            | External clock<br>Fig. 6 | 2.7 to 6.0          | 6    |              | 34  | μs   |

| Sub-clock Input<br>"L"-Level Pulse Width | tWXL            | X1            | External clock<br>Fig. 6 | 2.7 to 6.0          | 6    |              | 34  | μs   |

| Sub-clock Input Rise<br>Time             | <sup>t</sup> XR | X1            | External clock<br>Fig. 6 | 2.7 to 6.0          |      |              | 0.2 | μs   |

| Sub-clock Input Fall<br>Time             | <sup>t</sup> XF | X1            | External clock<br>Fig. 6 | 2.7 to 6.0          |      |              | 0.2 | μs   |

| Sub-clock OSC<br>Constant                | CX1, CX2        |               | Fig. 2                   | 2.7 to 6.0          | Refe | r to Table 2 | 2.  | _    |

(Note 1) Since the frequency also depends on the supply voltage and operating cycle time, both must be referred to.

# 3. Electrical Characteristics at $T_a = -30$ to $+70^{\circ}$ C, $V_{SS} = 0$ V

| Parameter                                                                 | Symbol                        | Applicable                                                 | Conditions                                                | r                        |                             | Limits                                  |     | T        |

|---------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--------------------------|-----------------------------|-----------------------------------------|-----|----------|

|                                                                           | •                             | Pins, Remarks                                              |                                                           | V <sub>DD</sub> [V]      | min                         | týp                                     | max | Uni      |

| "H"-Level Input<br>Current                                                | I <sub>IH</sub> (1)           | Ports A, C, D, E2,<br>F to H of OD                         | Output Nch Tr OFF<br>(Including Nch Tr                    | 2.7 to 6.0               |                             |                                         | 5.0 | μΑ       |

|                                                                           |                               | type                                                       | OFF leakage<br>current)<br>V <sub>IN</sub> =+13.5V        |                          |                             |                                         |     |          |

|                                                                           | l <sub>iH</sub> (2)           | Ports EO, E1                                               | Output Nch Tr OFF<br>(Including Nch Tr                    | 2.7 to 6.0               |                             |                                         | 1.0 | μΔ       |

|                                                                           | li li                         |                                                            | OFF leakage<br>current)<br>ViN=VDD                        |                          |                             |                                         |     |          |

|                                                                           | I <sub>IH</sub> (3)           | Port B, RES<br>OSC1, X1                                    | V <sub>IN</sub> =V <sub>DD</sub>                          | 2.7 to 6.0               |                             |                                         | 10  |          |

| "L"-Level Input                                                           | I <sub>IL</sub> (1)           | Ports A, C to H of                                         | V <sub>IN</sub> =V <sub>DD</sub> Output Nch Tr OFF        |                          | -1.0                        |                                         | 10  | μA<br>μA |

| Current                                                                   | _                             | OD type                                                    | V <sub>IN</sub> =V <sub>SS</sub>                          | 0.700                    | 1                           |                                         |     | <u> </u> |

|                                                                           | I <sub>IL</sub> (2)           | Port B<br>Ports A, C to H of                               | V <sub>IN</sub> =V <sub>SS</sub> Output Nch Tr OFF        | 2.7 to 6.0               | -1.0<br>-1.3                | -0.35                                   |     | μA       |

|                                                                           |                               | PU type                                                    | V <sub>IN</sub> =V <sub>SS</sub>                          |                          |                             | -0.39                                   |     | mA       |

|                                                                           | Iլը(3)                        | OSC1, X1                                                   | V <sub>IN</sub> =V <sub>SS</sub>                          | 2.7 to 6.0               | -10                         |                                         |     | μΑ       |

| "H"-Level Output                                                          | I <sub>IL</sub> (4)<br>VOH(1) | RES<br>Ports A, C to H of                                  | V <sub>IN</sub> =V <sub>SS</sub><br>I <sub>OH</sub> =50μA | 2.7 to 6.0<br>4.0 to 6.0 | -60<br>V <sub>DD</sub> -1.2 | -25                                     |     | μA       |

| Voltage                                                                   |                               | PU type                                                    |                                                           |                          |                             |                                         |     |          |

|                                                                           | V <sub>OH</sub> (2)           | Ports A, C to H of PU type                                 | I <sub>OH</sub> =-10μA                                    | 3.0 to 6.0               | V <sub>DD</sub> -0.5        |                                         |     | V        |

|                                                                           | V <sub>OH</sub> (3)           | T0 to T11,<br>T12/S11 to<br>T15/S8                         | I <sub>OH</sub> =-20mA                                    | 4.0 to 6.0               | V <sub>DD</sub> -1.8        |                                         |     | V        |

|                                                                           | V <sub>OH</sub> (4)           | T0 to T11,<br>T12/S11 to<br>T15/S8                         | IOH=-1mA<br>IOH in other ports<br>is less than -1mA.      | 3.0 to 6.0               | V <sub>DD</sub> -1.0        |                                         |     | ٧        |

|                                                                           | V <sub>OH</sub> (5)           | S0 to \$7                                                  | I <sub>OH</sub> =~5mA                                     | 4.0 to 6.0               | V <sub>DD</sub> -1.8        | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     | V        |

|                                                                           | VOH(6)                        | S0 to S7                                                   | IOH=-1 mA<br>IOH in other ports<br>is less than -1 mA.    | 3.0 to 6.0               | V <sub>DD</sub> -1.0        |                                         |     | ٧        |

| "L"-Level Output<br>Voltage                                               | V <sub>OL</sub> (1)           | Ports C, D                                                 | I <sub>OL</sub> =20mA                                     | 4.0 to 6.0               |                             |                                         | 1.5 | V        |

|                                                                           | V <sub>OL</sub> (2)           | Ports C, D                                                 | IOL=2mA<br>IOL in other ports is<br>less than 1mA.        |                          |                             |                                         | 0.5 | ٧        |

|                                                                           | VOL(3)                        | Ports A, E to H                                            | IOL=5mA                                                   | 4.0 to 6.0               |                             |                                         | 1.5 |          |

|                                                                           | V <sub>OL</sub> (4)           | Ports A, E to H                                            | IOL=1 mA IOL in other ports is less than 1 mA.            | 3.0 to 6.0               |                             |                                         | 0.5 | V        |

| "L"-Level Output<br>Current<br>(Current flowing in<br>pull-down resistor) | IOL                           | T0 to T11,<br>T12/S11 to<br>T15/S8, S0 to S7<br>of PD type | Output Pch Tr OFF<br>VOUT=3.0V<br>Vp=-35V                 | 5.0                      | 190                         | 362                                     | 760 | μΑ       |

| Output OFF-State<br>Leakage Current                                       | IOFF(1)                       | TO to T11,<br>T12/S11 to<br>T15/S8, S0 to S7<br>of OD type | Output Pch Tr OFF<br>VOUT=VDD                             | 3.0 to 6.0               |                             |                                         | 30  | μΑ       |

| ,                                                                         | I <sub>OFF</sub> (2)          | T0 to T11,<br>T12/S11 to<br>T15/S8, S0 to S7<br>of OD type | Output Pch Tr OFF<br>VOUT=VDD-40V                         | 3.0 to 6.0               | -30                         |                                         |     | μΑ       |

| Resistance of Pull-up<br>MOS Transistor                                   | R <sub>Tru</sub>              | Ports A, C to H of<br>PU type                              |                                                           | 5.0                      | 6                           | 15                                      | 24  | kΩ       |

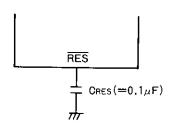

| Pull-up Resistance                                                        | Ru                            | RES                                                        |                                                           | 5.0                      | 100                         | 220                                     | 400 | _        |

| Pull-down Resistance                                                      | Rd                            | T0 to T11,<br>T12/S11 to<br>T15/S8, S0 to S7<br>of PD type |                                                           | 5.0                      | 50                          | 105                                     | 200 | kΩ       |

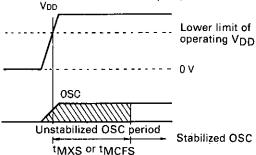

| Main Clock OSC<br>Stabilizing Period                                      | tMXS                          | OSC1, OSC2                                                 | 4.19MHz crystal<br>OSC                                    | 3.0 to 6.0               |                             |                                         | 30  | ms       |

|                                                                           | †MCFS                         | OSC1, OSC2                                                 | 4.0MHz ceramic resonator OSC                              | 3.0 to 6.0               |                             |                                         | 10  | ms       |

### Continued from proceding page.

| Parameter                                     | Symbol                              | Applicable<br>Pins, Remarks | Conditions                                                                                                          | V <sub>DD</sub> [V]      | min         | Limits             |           | 11  |

|-----------------------------------------------|-------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--------------------|-----------|-----|

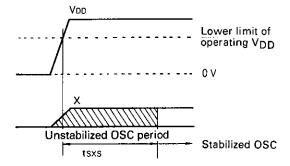

| Sub-clock OSC                                 | , -                                 | X1, X2                      | 32.768kHz crystal                                                                                                   | 2.7 to 6.0               | min         | typ                | max<br>10 | Uni |

| Stabilizing Period                            | tsxs                                | Λ1, Λ2                      | OSC Crystal                                                                                                         | 2.7 10 6.0               |             |                    | 10        | s   |

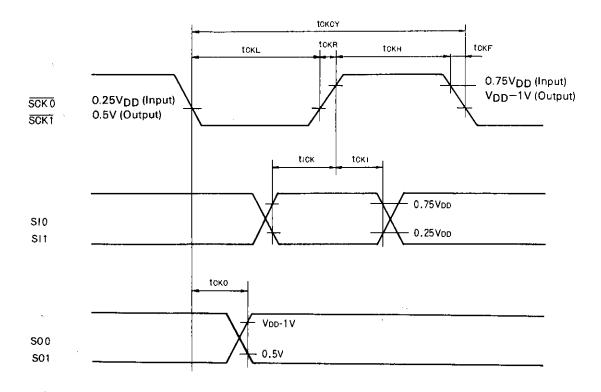

| Serial Clock                                  | 4                                   | COKO DOKA                   | F:- 0                                                                                                               | 4500                     | 4.0         |                    |           |     |

| Input Clock Cycle Output Clock Cycle          | tCKCY(1)                            | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0<br>4.5 to 6.0 | 1.6<br>1.84 |                    |           | μs  |

| Input Clock "L"-Level                         | tCKCY(2)<br>tCKL(1)                 | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               | 0.7         |                    |           | μs  |

| Pulse width (Note 2)                          |                                     |                             |                                                                                                                     |                          |             |                    |           | μs  |

| Output Clock "L"-Level Pulse Width            | tCKL(2)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               | 0.92        |                    |           | μs  |

| Input Clock "H"-Level<br>Pulse Width (Note 2) | tCKH(1)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               | 0.7         |                    |           | μs  |

| Output Clock<br>"H"-Level Pulse Width         | tCKH(2)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               | 0.92        |                    |           | μs  |

| Input Clock Rise Time                         | tCKR(1)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               |             |                    | 3.0       | μs  |

| Output Clock Rise<br>Time                     | tCKR(2)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               |             |                    | 0.1       | μs  |

| Input Clock Fall Time                         | tCKF(1)                             | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               | •           |                    | 3.0       | μs  |

| Output Clock Fall Time                        |                                     | SCKO, SCK1                  | Fig. 8                                                                                                              | 4.5 to 6.0               |             |                    | 0.1       | μs  |

| Serial Input  Data Setup Time                 | tICK                                | SIO, SI1                    | Specified for ∫ of SCK0, SCK1                                                                                       | 4.5 to 6.0               | 0.2         |                    |           | μs  |

| Data Hold Time                                | tCKI                                | SIO, SI1                    |                                                                                                                     | 4.5 to 6.0               | 0.2         |                    |           | μs  |

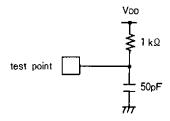

| Serial Output Output Delay Time               | tско                                | S00, S01                    | Specified from of SCKO, SCK1 External 1kΩ External 50pF Fig. 8                                                      | 4.5 to 6.0               |             |                    | 0.5       |     |

| Hysteresis Voltage                            | Vence                               | Ports E to H, RES           | 1 119. 0                                                                                                            | 3.0 to 6.0               |             | 0.1V <sub>DD</sub> |           | V   |

| Comparator Response                           | V <sub>HYS</sub><br>T <sub>RS</sub> | Port B                      | At 100mV                                                                                                            | 4.5 to 6.0               |             | 0.1700             | 50        |     |

| Speed                                         | .ua                                 | , 0.1 5                     | overdrive mode                                                                                                      |                          | •           |                    |           | "   |

| Comparator Input<br>Offset Voltage            | Vors                                | Port B                      | V <sub>IN</sub> =1.0V to<br>V <sub>DD</sub> -1.5V<br>V <sub>REF</sub> =1.0V to<br>V <sub>DD</sub> -1.5V             | 4.5 to 6.0               |             | ±20                | ±100      | mν  |

| Operating Current<br>Dissipation (Note 3)     | IDDOP(1)                            | V <sub>DD</sub>             | 4.19MHz x 1/1<br>high-speed<br>operation mode<br>(T <sub>CYC</sub> =0.95 µs)<br>32.768kHz sub-<br>clock oscillating | 4.5 to 6.0               |             | 4.5                | 10        | mA  |

|                                               | I <sub>DDOP</sub> (2)               | V <sub>DD</sub>             | 4.19MHz x 1/2<br>high-speed<br>operation mode<br>(T <sub>C</sub> YC=1.9\mus)<br>32.768kHz sub-<br>clock oscillating | 4.0 to 6.0               |             | 2.7                | 6         | mA  |

|                                               | IDDOP(3)                            | V <sub>DD</sub>             | 4.19MHz x 1/32                                                                                                      | 3.0                      |             | 0.35               | 0.7       |     |

|                                               |                                     |                             | low speed operation mode (TCYC=30.5µs) 32.768kHz subclock oscillating                                               | 6.0                      |             | 1.5                | 3         | mΑ  |

|                                               | IDDOP(4)                            | V <sub>DD</sub>             | 32.768kHz low-                                                                                                      | 2.7                      |             | 0.035              | 0.12      | mA  |

|                                               |                                     |                             | speed operation<br>mode<br>(T <sub>CYC</sub> =61 µs)                                                                | 6.0                      |             | 0.4                | 1.2       |     |

|                                               |                                     |                             | 4.19MHz main<br>clock stop                                                                                          |                          |             |                    |           |     |

(Note 2) When using the internal clock, T<sub>excus</sub> and T<sub>excus</sub> (pins SCKO and SCK1) have a minimum pulsewidth of 0.92  $\mu$ s. This value is, however, dependent on the pull-up resistor and may, in some cases, be less than the above rating. The value of the pull-up resistance should be selected to ensure a minimum pulsewidth for T<sub>excus</sub> and T<sub>excus</sub> that is greater than the rated 0.7  $\mu$ s.

### LC6538D

### Continued from preceding page.

|                                                | Symbol   | Applicable<br>Pins, Remarks | Conditions                                                       |                     |     | Limits |     |      |  |

|------------------------------------------------|----------|-----------------------------|------------------------------------------------------------------|---------------------|-----|--------|-----|------|--|

| Parameter Standby Current Dissipation (Note 3) |          |                             |                                                                  | V <sub>DD</sub> [V] | min | typ    | max | Unit |  |

| Standby Current                                | IDDST(1) | V <sub>DD</sub>             | 4.19MHz main                                                     | 2.7                 |     | 4      | 18  | μΑ   |  |

| Dissipation (Note 3)                           |          |                             | clock stop<br>32.768kHz sub-<br>clock oscillating<br>(HALT mode) | 6.0                 |     | 120    | 300 | μΑ   |  |

|                                                | IDDST(2) | $V_{DD}$                    | Complete standby                                                 | 1.8                 | ·   | 0.02   | 4   | μA   |  |

|                                                |          |                             | (HOLD mode)                                                      | 6.0                 |     | 0.05   | 10  |      |  |

(Note 3) The current flowing in the I/O port transistors and pull-up/pull-down resistors is excluded.

Fig. 1 Main Clock OSC Circuit

Fig. 2 Sub-clock Crystal OSC Circuit

Table 1 Main Clock OSC-Guaranteed Constants

| OSC Mode                           | Maker          | Resonator                                   | CO1              | CO2              |

|------------------------------------|----------------|---------------------------------------------|------------------|------------------|

| 4.194304 MHz                       | Tokyo<br>Denpa | HC-43/u<br>CL=18pF<br>Drive level<br>=100mW | 22pF             | 22pF             |

| crystal OSC                        | Kinseki        | HC-49/u<br>CL=16pF                          | 15pF             | 15pF             |

|                                    |                | HC-49/u<br>CL=24pF                          | 27pF             | 27pF             |

|                                    | Murata         | CSA-4.00MG                                  | 33pF             | 33pF             |

| 4.0MHz<br>ceramic<br>resonator OSC | Withata        | CST-4.00MG*1                                | Unnec-<br>essary | Unnec-<br>essary |

|                                    | Kyocera        | KBR-4.0MS                                   | 33pF             | 33pF             |

| resonator OSC                      | Ryocera        | KBR-4.0MES*1                                | Unnec-<br>essary | Unnec-<br>essary |

The differential between CO1 and CO2 should be within  $\pm$  10%, including wiring capacitance.

<sup>\*1: 3-</sup>pin ceramic resonator with on-chip capacitor

Fig. 3 Main Clock OSC Stalibizing Period

**OSC Mode** CX2 Maker CX1 Resonator KF-38G-13200 22pF 22pF CL=13pF 32.768kHz Kyocera crystal OSC KF-38G-10200 20pF 22pF CL=10pF Trimmer

Table 2 Sub-clock Crystal OSC-Guaranteed Constants

(Note) CL: Internal load capacitance of crystal resonator

Fig. 4 Sub-clock OSC Stabilizing Period

Fig. 5 Main Clock (External Clock) Input Waveform

Fig. 6 Sub-clock (External Clock) Input . . Waveform

(Note)

When the rise time of the power supply is 0, the reset time becomes 10ms to 100ms at  $C_{RES} = 0.1 \mu F$ .

If the rise time of the power supply is long, the value of CRES must be fixed so that the reset time becomes longer than the main clock OSC stabilizing period.

Fig. 7 Reset Circuit

Serial Output Load

Fig. 8 Serial Clock Timing

Notes for Program Evaluation

• When evaluating the LC6538D with the evaluation chip (LC6593, LC65PG38D), the following must be observed.

| Classrti-<br>cation                  | Item                                             | Fund                                                                                                               | Notes for evaluation                                                                                                                                             |                                                                                                                                                                                                                                                                                             |

|--------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cati                                 | i i i                                            | Mass-production chip                                                                                               | Notes for evaluation                                                                                                                                             |                                                                                                                                                                                                                                                                                             |

|                                      | Ports C, D<br>output level<br>at reset mode      | Ports C, D can be brought to "H" or "L" in a group of 4 bits.                                                      | Port C and port D can be brought to "H" or "L" by CHL pin and DHL pin, respectively.                                                                             | CHL pin and DHL pin must be set according to option specified for mass-production chip.                                                                                                                                                                                                     |

|                                      | Watchdog<br>reset<br>function                    | The presence or absence of time base timer-used watchdog reset function can be selected.                           | Whether or not to perform watchdog reset function with WDC pin can be determined.                                                                                | WDC pin must be set according to option specified for mass-production chip.                                                                                                                                                                                                                 |

| Notes for option                     | Port output<br>configuration<br>PU/OD            | PU or OD can be selected in bit units.                                                                             | Only Nch OD configuration without pull-up resistance                                                                                                             | (LC6593-applied evaluation) External resistor (10kohms) on evaluation chip board must be connected to necessary port. (LC65PG38D-applied evaluation) Resistor must be connected to necessary port on application board                                                                      |

|                                      | PU resistor<br>configuration                     | PU resistor brought to Hi-Z<br>at "L" output mode (Pch Tr is<br>turned OFF)                                        | PU resistor, being external<br>resistor, whose impedance<br>remains unchanged at "L"<br>output mode.                                                             | For mass-production chip, leakage current only flows in Pch Tr at "L" output mode; for evaluation chip, current continues flowing in PU resistor at "L" output mode.                                                                                                                        |

|                                      | Port output<br>configuration<br>PD/OD            | PD or OD can be selected in bit units.                                                                             | Only Pch OD configuration without pull-down resistance.                                                                                                          | (LC6593-applied evaluation) External resistor (100kohms) on evaluation chip board must be connected to necessary port. (LC65PG38D-applied evaluation) Resistor must be connected to necessary port on application board. Load power supply must be also supplied on application board side. |

| Notes for USC                        | Constants for main clock                         | (Crystal OSC), (Ceramic resonator OSC) Catalog-guaranteed constants provide OSC at frequency specified in catalog. | (Crystal OSC), (Ceramic resonator OSC) Different from mass-production chip in circuit design and characteristic. OSC may be made unstable by wiring capacitance. | (Crystal OSC), (Ceramic resonator OSC) External constants must be fine-adjusted according to service conditions. Refer to note given below.                                                                                                                                                 |

| Notes                                | Constants for<br>sub-clock                       | (Crystal OSC) Catalog-guaranteed constants provide OSC at frequency specified in catalog.                          | (Crystal OSC) Different from mass- production chip in circuit design and characteristic. OSC may be made unstable by wiring capacitance.                         | (Crystal OSC) External conostants must be fine-<br>adjusted according to service<br>conditions. Refer to note given below                                                                                                                                                                   |

| S                                    | OSC<br>frequency for<br>main clock,<br>sub-clock | OSC frequency characteristic as indicated in catalog                                                               | Different from mass-<br>production chip in circuit<br>design and characteristic.                                                                                 | ES, CS must be used to evaluate characteristic in detail.                                                                                                                                                                                                                                   |

| Notes for electrical characteristics | Operating<br>current,<br>standby<br>current      | Current characteristic as indicated in catalog                                                                     | Different from mass-<br>production chip in circuit<br>design and characteristic.                                                                                 | Standby current cannot be evaluate in detail. However, standby current can be confirmed roughly in the manner shown below. Be sure to confirm standby current. ES, CS must be used to evaluate characteristic in detail.                                                                    |

| Notes for ele                        | Operating voltage                                | Supply voltage range as indicated in catalog                                                                       | Restricted to the operating range of EPROM, other LSI                                                                                                            | Evaluation chip must be also used a $V_{DD} = 5V\pm5\%$ at which EPROM, other LSI are used. Therefore, $V_{DD}$ $5V\pm5\%$ only can be used for evaluation of mass-production microcomputers.                                                                                               |

|                                      | Operating temperature                            | Temperature range as<br>indicated in catalog                                                                       | Guaranteed temperature range: 10°C to 40°C                                                                                                                       | LC6593 and LC65PG38D must be used at 10°C to 40°C for evaluation                                                                                                                                                                                                                            |

#### < Confirmation methods for the standby function >

The standby current at the standby mode of the evaluation chip can be evaluated not exactly but approximately. Then, do the following steps.