CMOS LSI

SANYO

No. 3355A

LC7216M

PLL Frequency Synthesizer for Electronic Tuning

#### **Features**

Various reference frequencies, input/output ports, and a universal counter, and unlock detector.

- (1) Programmable divider

- FMIN pin: 130MHz: 70mVrms/160MHz: 110mVrms input (Prescaler built-in)

- AMIN pin: Pulse swallow and direct frequency-divide method.

- (2) Reference frequency: 10 user selectable reference frequencies.

100, 50, 25, 12.5, 6.25, 3.125, 10, 9, 5, and 1kHz

- (3) Output port: 5 ports

- 2 complementary outputs

3N-channel open drain outputs

- (4) Input port: 2 ports

- (5) Universal counter: Used to measure IF signals, etc. (The IF signals counting must be sure to use together with the SD (Station Detect) signals from IF-IC.)

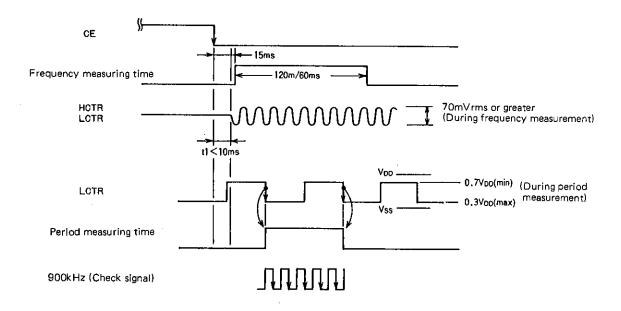

- HCTR pin: For frequency measurement (>70MHz input capable)

- · LCTR pin: For frequency or period measurement

- (6) Unlock detection for PLL: 0.55, 1.11, 2.22, 3.33 µsec phase difference

- (7) Package: MFP20 (Miniflat)

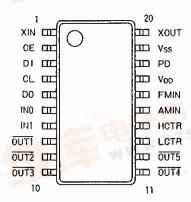

#### Pin Assignment

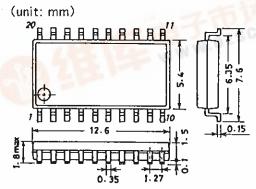

### Package Dimensions 3036B

SANYO: MFP20

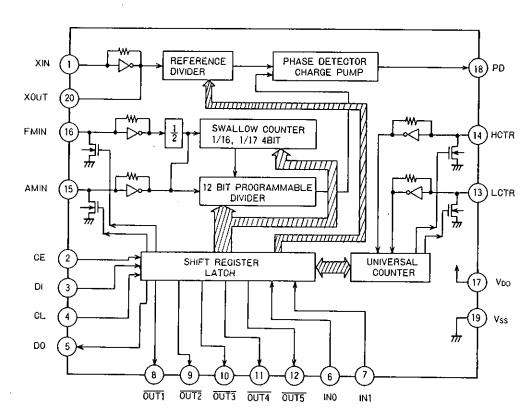

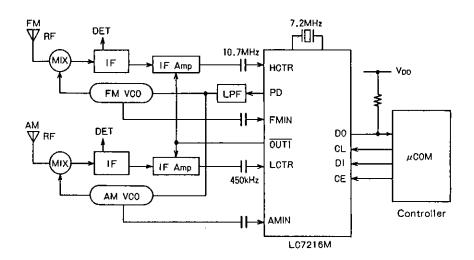

### **Block Diagram**

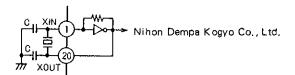

**%Sample Crystal Resonator:**

7.200MHz CL16pF (C=27pF)

- LN-X-0702 (NR-18 type)

- LN-P-0001 (AT-51 type)

Pin Description XIN, XOUT FMIN, AMIN CE, CL, DI, DO OUT1 to OUT5 IN0, IN1 HCTR, LCTR PD

:Crystal OSC (7.2MHz) :Local oscillating signal input

:Serial data input/output

:Output ports :Input ports

:Universal counter signal input

:Charge pump output

### Maximum Ratings at Ta=25°C, Vss=0V

|                             |                       |                                              |                          | unit |

|-----------------------------|-----------------------|----------------------------------------------|--------------------------|------|

| Maximum Supply Voltage      | V₀₀max                | V <sub>DD</sub>                              | -0.3 to $+7.0$           | V    |

| Input Voltage               | V <sub>1N</sub> (1)   | CE,CL,DI,IN0,IN1                             | -0.3 to $+7.0$           | V    |

|                             | V <sub>IN</sub> (2)   | Input ports other than $V_{IN}(1)$           | $-0.3$ to $V_{pp}+0.3$   | V    |

| Output Voltage              | $V_{out}(1)$          | DO                                           | -0.3 to $+7.0$           | ٧    |

|                             | V <sub>ou⊤</sub> (2)  | OUT1,OUT2                                    | $-0.3$ to $V_{pp} + 0.3$ | V    |

|                             | $V_{\text{out}}(3)$   | OUT3,OUT4,OUT5                               | -0.3  to  +15            | V    |

|                             | V <sub>ou T</sub> (4) | Output ports other than $V_{out}(1),(2),(3)$ | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable Power Dissipation | Pdmax                 | Ta≦85°C                                      | 200                      | mW   |

| Operating Temperature       | Topr                  |                                              | -40  to  +85             | °C   |

| Storage Temperature         | Tstg                  |                                              | -55 to +125              | °C   |

| Allowable Operating Condition | ns at Ta=            | =-40 to +85℃        | , V <sub>ss</sub> =0V                               |                        |         |                     |      |

|-------------------------------|----------------------|---------------------|-----------------------------------------------------|------------------------|---------|---------------------|------|

|                               |                      |                     |                                                     | min                    | typ     | max                 | unit |

| Supply Voltage                | $V_{DD}(1)$          | VDD                 |                                                     | 4.5                    |         | 6.5                 | V    |

|                               | $V_{oo}(2)$          | VDD                 | Crystal OSC                                         | 3.5                    |         | 6.5                 | V    |

| High Level Input Voltage      | V <sub>IH</sub> (1)  | CE,CL,DI<br>IN0,IN1 |                                                     | 2.2                    |         | 6.5                 | V    |

|                               | $V_{\rm tH}(2)$      | LCTR                | Pulse wave, DC                                      | 0.7V <sub>pp</sub> (1) | ١       | V <sub>DD</sub> (1) | ٧    |

|                               |                      |                     | coupling Note                                       |                        |         | . 50 ,              | •    |

| Low Level Input Voltage       | V <sub>IL</sub> (1)  | CE,CL,DI<br>IN0,IN1 |                                                     | 0                      |         | 0.7                 | V    |

|                               | V <sub>IL</sub> (2)  | LCTR                | Note 4                                              | 4) 0                   | 0.3     | √ <sub>00</sub> (1) | V    |

| Output Voltage                | V <sub>συτ</sub> (1) | DO                  |                                                     |                        |         | 6.5                 | v    |

| ,                             | V <sub>ουτ</sub> (2) | OUT3 to OU          | T <del>S</del>                                      |                        |         | 13                  | v    |

| Input Frequency               | fin(1)               | XIN                 | Sine wave, capacitive coupling, V <sub>DD</sub> (2) | 1.0                    | 7.2     | 8.0                 | MHz  |

|                               | f <sub>IN</sub> (2)  | FMIN                | Sine wave, capacitive                               | Note 1) 10             |         | 130                 | MHz  |

|                               | -111                 | , ,,,,,,,           | coupling, V <sub>oo</sub> (1)                       |                        | Note 5) |                     | MHz  |

|                               | f <sub>IN</sub> (3)  | AMIN                | Sine wave, capacitive coupling, $V_{op}(1)$         | Note 1)0.5             | -       | 40                  | MHz  |

|                               | $f_{1N}(4)$          | HCTR                | Sine wave, capacitive                               | Note 2) 10             |         | 60                  | MHz  |

|                               |                      |                     | coupling, V <sub>DD</sub> (1)                       | 11010 =/ 10            | Note 6) |                     | MHz  |

|                               | f <sub>IN</sub> (5)  | LCTR                | Sine wave, capacitive coupling, V <sub>PP</sub> (1) | Note 3) 15             | ,       | 500                 | kHz  |

|                               | f1N(6)               | LCTR                | Pulse wave, DC coupling                             | Note 4)1.0             | 20      | )×10³               | Hz   |

| Crystal Oscillator Frequency  | X'tal                | $X_{IN} - X_{OUT}$  | Cl≦50Ω                                              | 3.0                    | 7.2     | 8.0                 | MHz  |

| Input Amplitude               | V <sub>IN</sub> (1)  | Xin                 | Sine wave, capacitive coupling, V <sub>oc</sub> (1) | 0.5                    |         | 1.5                 | Vrms |

|                               | V <sub>1N</sub> (2)  | FMIN                | Sine wave, capacitive                               | 0.07                   |         | 0.5                 | Vrms |

|                               |                      |                     |                                                     | te 5)(0.11)            |         |                     | Vrms |

|                               | V <sub>IN</sub> (3)  | AMIN                | Sine wave, capacitive coupling, V <sub>DD</sub> (1) | 0.07                   |         | 0.5                 | Vrms |

|                               | $V_{IN}(4)$          | HCTR                | Sine wave, capacitive                               | Note 2)0.07            |         | 0.5                 | Vrms |

|                               |                      |                     |                                                     | ote 6)(0,11)           |         | 0                   | Vrms |

|                               | V <sub>IN</sub> (5)  | LCTR                | Sine wave, capacitive coupling, $V_{DD}(1)$         |                        |         | 0.5                 | Vrms |

Note 1) DV and SP represent 1 bit within serial data.

| * | : | Don't c | are |

|---|---|---------|-----|

|   |   |         |     |

| DV | SP | Input frequencyt  | 1/2 divider | 1 / 16,17 swallow | 12-bit main divider | Input pin |

|----|----|-------------------|-------------|-------------------|---------------------|-----------|

| 1  | *  | 10 to 130(160)MHz | 0           | 0                 | 0                   | (FMIN)    |

| 0  | 1  | 2 to 40 MHz       | _           | 0                 | 0                   | (AMIN)    |

| 0  | 0  | 0.5 to 10 MHz     | _           | _                 | 0                   | (AMIN)    |

Note 2) Frequency measurement

Note 3) Frequency measurement

Note 4) Period measurement

Note 5)  $f_{1N}(2)$  10 to 160MHz/ $V_{1N}(2)$

0.11Vrms (min)

Note 6)  $f_{IN}(4)$  10 to 70MHz/ $V_{IN}(4)$

0.11Vrms (min)

| Electrical Characteristics und        | er allowat           | le operating condi | tions                            |                      |       |                    |       |

|---------------------------------------|----------------------|--------------------|----------------------------------|----------------------|-------|--------------------|-------|

|                                       |                      |                    |                                  | min                  | typ   | max                | unit  |

| Built-in Feedback Resistance          | R <sub>t</sub> (1)   | XIN                |                                  |                      | 1.0   |                    | МΩ    |

|                                       | $R_{r}(2)$           | FMIN               |                                  |                      | 500   |                    | kΩ    |

|                                       | R <sub>r</sub> (3)   | AMIN               |                                  |                      | 500   |                    | kΩ    |

|                                       | $R_{r}(4)$           | HCTR               |                                  |                      | 500   |                    | kΩ    |

|                                       | $R_{r}(5)$           | LCTR               |                                  |                      | 500   |                    | kΩ    |

| Hysteresis Width                      | $V_{H}$              | LCTR               |                                  | 0.1V <sub>DD</sub>   | (     | 0.6V <sub>DD</sub> | V     |

| High Level Input Current              | I <sub>IH</sub> (1)  | CE,CL,DI           | V₁=6.5                           |                      |       | 5.0                | μА    |

|                                       | I <sub>1H</sub> (2)  | IN0,IN1            | $V_i = V_{oo}$                   |                      |       | 5.0                | μА    |

|                                       | I <sub>IH</sub> (3)  | XIN                | $V_1 = V_{DD}$                   |                      |       | 20                 | μА    |

|                                       | <sub>1H</sub> (4)    | FMIN, AMIN         | $V_1 = V_{00}$                   |                      |       | 40                 | μА    |

|                                       | I <sub>IH</sub> (5)  | HCTR,LCTR          | $V_1 = V_{DD}$                   |                      |       | 40                 | μА    |

| Low Level Input Current               | <sub>ու</sub> (1)    | CE,CL,D!           | $V_1 = V_{ss}$                   |                      |       | 5.0                | μА    |

|                                       | <sub>IL</sub> (2)    | IN0,IN1            | $V_1 = V_{ss}$                   |                      |       | 5.0                | μА    |

|                                       | I <sub>IL</sub> (3)  | XIN                | $V_1 = V_{ss}$                   |                      |       | 20                 | μA    |

|                                       | I <sub>IL</sub> (4)  | FMIN, AMIN         | $V_1 = V_{ss}$                   |                      |       | 40                 | μA    |

|                                       | I <sub>1L</sub> (5)  | HCTR,LCTR          | $V_1 = V_{sa}$                   |                      |       | 40                 | μA    |

| High Level Output Voltage             | V <sub>oH</sub> (1)  | OUT1,OUT2          | l₀=1mA                           | V <sub>DD</sub> -1.0 |       |                    | V     |

| - ,                                   | V <sub>он</sub> (2)  | PD                 | l₀=0.5mA                         | $V_{DD} - 1.0$       |       |                    | v     |

| Low Level Output Voltage              | V <sub>oL</sub> (1)  | OUT1,OUT2          | I <sub>o</sub> =1mA              | . 55                 |       | 1.0                | v     |

|                                       | V <sub>oL</sub> (2)  | PD                 | I <sub>o</sub> =0.5mA            |                      |       | 1.0                | v     |

|                                       | V <sub>0L</sub> (3)  | OUT3 to OUT5       | I <sub>o</sub> =5mA              |                      |       | 1.0                | v     |

|                                       | V <sub>DL</sub> (4)  | DO                 | I <sub>o</sub> =5mA              |                      |       | 1.0                | v     |

| Output Off Leak Current               | loff(1)              | OUT3 to OUT5       | V <sub>o</sub> =13V              |                      |       | 5.0                | μA    |

| •                                     | l <sub>off</sub> (2) | DO                 | V <sub>0</sub> =6.5V             |                      |       | 5.0                | μΑ    |

| High Level 3-State Off Leak           | I <sub>OFFH</sub>    | PD                 | $V_0 = V_{DD}$                   |                      | 0.01  | 10.0               | nA    |

| Current                               |                      |                    |                                  |                      |       |                    |       |

| Low Level 3-Stage Off Leak<br>Current | I <sub>OFFL</sub>    | PD                 | $V_0 = V_{ss}$                   |                      | 0.01  | 10.0               | пA    |

| Input Capacitance                     | Cin                  | FMIN, HCTR         |                                  | 1                    | 2     | 3                  | pF    |

| Supply Current                        | I <sub>00</sub> (1)  | Voo                | $f_{IN}(2) = 130 MHz$            | •                    | 20    | 30                 | mA    |

|                                       |                      | - 00               | V <sub>IN</sub> (2)=70mVrms      |                      |       |                    | 111/5 |

|                                       |                      |                    | Crystal 7.2MHz OSC i             | is                   |       |                    |       |

|                                       |                      | •                  | connected.                       |                      |       |                    |       |

|                                       |                      |                    | Other input pins=V <sub>ss</sub> |                      |       |                    |       |

|                                       |                      |                    | Output pins=Open                 |                      |       |                    |       |

|                                       | I <sub>DD</sub> (2)  | V <sub>DD</sub>    | PLL partially stops              |                      | 1.0   |                    | mΑ    |

|                                       | .007                 | . 00               | (PLL inhibit).                   |                      | . 1.0 |                    | ША    |

|                                       |                      |                    | Crystal OSC operates.            |                      |       |                    |       |

|                                       |                      |                    | Crystal 7.2MHz OSC i             |                      |       |                    |       |

|                                       |                      | •                  | connected.                       |                      |       |                    |       |

|                                       |                      |                    | Other input pins=V <sub>ss</sub> |                      |       |                    |       |

|                                       |                      |                    | Output pins=Open                 |                      |       |                    |       |

|                                       |                      |                    | Courbur hus-oben                 |                      |       |                    |       |

Note) Use a capacitor of 2000pF or more between power supplies  $V_{\text{DD}}$  and  $V_{\text{ss.}}$

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

# Pin Description

| Symbol          | Pin No. | Description                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input/output    |

|-----------------|---------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| XIN<br>XOUT     | 1 20    | X'tal OSC                      | Crystal oscillator (7.2MHz) is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input<br>Output |

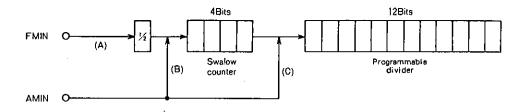

| FMIN            | 16      | Local oscillation signal input | <ul> <li>FMIN is selected by sepcifying serial data input: DV=1</li> <li>Frequency between 10 and 130MHz is input (70mVrms min).</li> <li>Signals are set to the swallow counter via built-in prescaler (1/2).</li> <li>From 256 to 65536 frequency divisions are selected but this value can be doubled with built-in prescaler (1/2).</li> </ul>                                                                                                                                                                                                                                                                            | Input           |

| AMIN            | 15      | Local oscillation signal input | <ul> <li>AMIN is selected by specifying serial data input: DV=0.</li> <li>When serial data input: SP=1 is specified.  — Input frequency is between 2 and 40 MHz (70mVrms min).  — Signals are not sent to built-in prescaler (1/2), but are directly transferred to swallow counter.  — From 256 to 65536 frequency divisions are selected and used as is.</li> <li>When serial data input: SP=0 is specified,  — Input frequency is between 0.5 and 10MHz (70mVrms min).  — Signals are directly transferred to a 12-bit programmable divider.  — From 4 to 4095 frequency divisions are selected and used as is.</li> </ul> | Input           |

| PD              | 18      | Charge pump output             | This is an output terminal for PLL charge pump signals. If the local oscillation signal frequency divided by N is higher than the reference frequency, high level signals are output from PD; if it is lower than the reference frequency, low level signals are output. If it is the same as the reference frequency, the signals are floated.                                                                                                                                                                                                                                                                               | 3 state         |

| V <sub>DD</sub> | 17      | Power supply                   | <ul> <li>Power is supplied to LC7216M via this<br/>pin. During PLL operation, 4.5 to 6.5V is<br/>applied.</li> <li>If only a crystal oscillation circuit is<br/>used for the controller clock and time<br/>base for the clock, the power supply<br/>can be reduced to a minimum of 3.5V.</li> </ul>                                                                                                                                                                                                                                                                                                                           | _               |

# LC7216M

| Continued | from | preceding | page. |

|-----------|------|-----------|-------|

|-----------|------|-----------|-------|

| Symbol                               | Pin No.                  | Description                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input/output                        |

|--------------------------------------|--------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| V <sub>SS</sub>                      | 19                       | Ground                                                       | This pin is tied to the ground of LC7216M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                   |

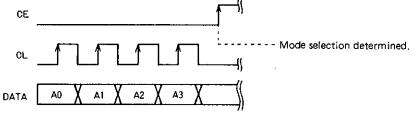

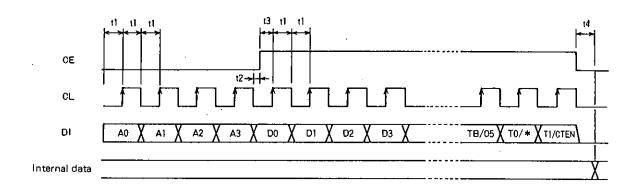

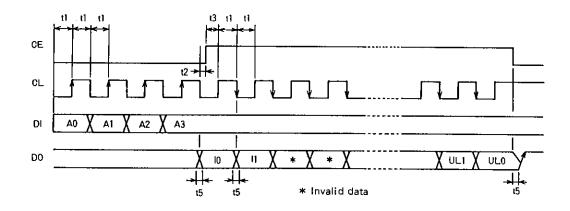

| CE                                   | 2                        | Chip enable                                                  | High level signals are input during serial data input (DI) or output (DO).                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input<br>*                          |

| CL                                   | 4                        | Clock                                                        | Data is synchronized by this clock signal<br>during serial data input (DI) or output<br>(DO).                                                                                                                                                                                                                                                                                                                                                                                                                           | Input<br>*                          |

| DI                                   | 3                        | Input data                                                   | <ul> <li>Serial data transferred from controller to<br/>LC7216M is input to this pin.</li> <li>A total of 36 bits of data should be input<br/>for initialization.</li> </ul>                                                                                                                                                                                                                                                                                                                                            | input<br>*                          |

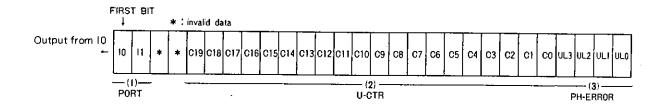

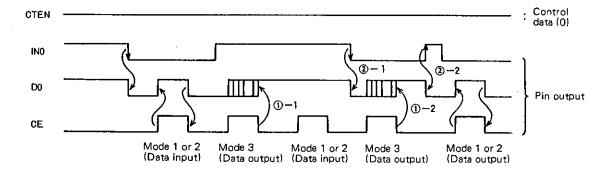

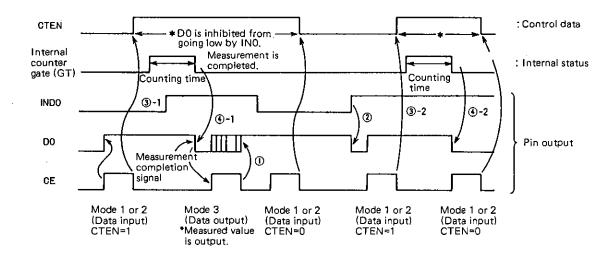

| DO                                   | 5                        | Output data                                                  | <ul> <li>Serial data transferred from the controller to LC7216M output from this pin.</li> <li>By synchronizing it with CL, 28 bits of the contents of the internal shift register can be output.</li> </ul>                                                                                                                                                                                                                                                                                                            | Output<br>(N-channel<br>open drain) |

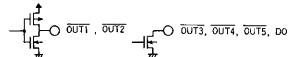

| OUT1<br>OUT2<br>OUT3<br>OUT4<br>OUT5 | 8<br>9<br>10<br>11<br>12 | Output port                                                  | Bits 01 to 05 of serial data, transferred from the controller, are latched, and the data is inverted and output in parallel.  OUT1 and OUT 2 are complementary out puts.  OUT3, OUT4, and OUT5 are N-ch open drain outputs (voltage durability: 13V).                                                                                                                                                                                                                                                                   | Output                              |

| IN0                                  | 6                        | Input port                                                   | Contents of input ports IN0 and IN1 are converted from parallel to serial form                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input                               |

| IN1                                  | 7                        |                                                              | and are output from output pin DO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | *                                   |

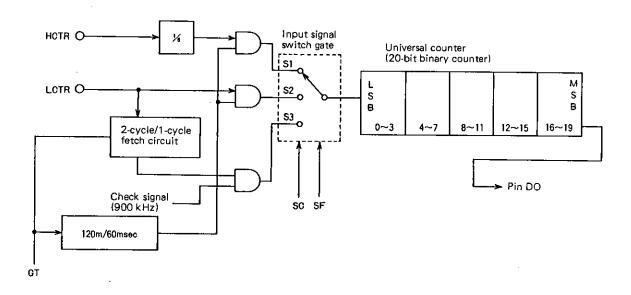

| HCTR                                 | 14                       | Universal counter<br>frequency measuring<br>signal input pin | <ul> <li>HCTR is selected by specifying spiral data input: SC=1.</li> <li>Input frequency is between 10 and 60 MHz (70mVrms min).</li> <li>Since signals are sent to a universal counter (20-bit binary counter) via a 1/8 of the actual frequency input to HCTR.</li> <li>When HCTR is selected, either 120msec or 60msec can be specified as the measuring time in the frequency measurement mode. (GT=1/0; 120/60msec)</li> <li>Result can be output from MSB of the universal counter via output pin DO.</li> </ul> | Input                               |

# Continued from preceding page.

| Symbol | Pin No. | Description                                                   | Function                                                                                                               | Input/output |

|--------|---------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------|

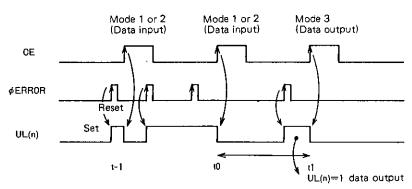

| LCTR   | 13      | Universal counter frequency period measuring signal input pin | <ul> <li>LCTR is selected by specifying serial data input: SC=0.</li> <li>If serial data input: SF=1 is set,</li></ul> | Input        |

<sup>\*</sup>High and low level input voltage to CE, CL, DI, IN0 and IN1 are held to the following range, respectively, regardless of the supply voltage (V<sub>DD</sub>):

$V_{IH}$ =2.2 to 6.5V,  $V_{IL}$ =0 to 0.7V

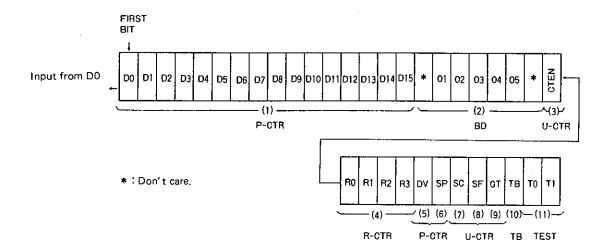

# Structure of Control Data (Serial Data Input)

The control serial data of LC7216M consists of 36 bits. When power is turned on, data should be entered on every one of these bits for initialization. However, the last two bits are not related to the user, because data on these bits is used for switching the test mode.

After initialization, only the contents of DO through CTEN (the first 24 bits) can be changed without affecting the rest of the bits (the last 12 bits) using the serial data input mode. Data is input at the DI pin.

| Symbol | Control section/data                                                                                                                                                                                                                                                             | Description                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                  |                         |    |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-------------------------|----|--|--|

|        |                                                                                                                                                                                                                                                                                  | • Used of th Data The (see               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                  |                         |    |  |  |

|        | Programmable divider data                                                                                                                                                                                                                                                        | DV                                       | SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LSB            | No. of divisions | Actual No. of divisions | DV |  |  |

| (1)    |                                                                                                                                                                                                                                                                                  | 1                                        | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D <sub>0</sub> | 256 to 65535     | Twice the set value     |    |  |  |

|        | D0 to D15                                                                                                                                                                                                                                                                        | 0                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D0             | 256 to 65535     | Set value               | SP |  |  |

|        |                                                                                                                                                                                                                                                                                  | 0                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D4             | 4 to 4095        | Set value               |    |  |  |

| (2)    | *: Don't care.  If the LSB is D4, the data in D0 to Evalue.  • Used to determine output from outout to OUT1 to OUT5.  O1 determines output from OUT1. Will OUT1 is set low; and when O1=0, Output port data  Output port data  (2)  • Can be used to switch bands and for value. |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                  |                         |    |  |  |

|        | O1 to O5                                                                                                                                                                                                                                                                         | • Used                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operat         |                  |                         |    |  |  |

| (3)    | Universal counter starting data  CTEN                                                                                                                                                                                                                                            | count put in When from or LC count Unive | <ul> <li>Used to operate the universal counter. When CTEN=0, the universal counter, or 20-bit binary counter is reset, and both HCTR and LCTR are put into the pull-down (GND) state.     When CTEN=1, the universal counter is released from reset, and counts signals input to HCTR or LCTR (which one is specified by the universal counter select data SC setting.).</li> <li>Universal counter is reset when CTEN=0, note that count data should be transferred to the controller while CTEN=1.</li> </ul> |                |                  |                         |    |  |  |

Continued from preceding page.

| Control section/data     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Related data                                                                                                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                        | Used to select a reference frequency from among 10 options, and inhibit PLL operation of LC7216M, i.e., put it into backup mode.      (unit: kHz)      R0 R1 R2 R3 Reference frequency     0 0 0 0 1 50     0 0 1 0 25     0 0 1 1 25     0 1 0 0 1 12.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

|                          | 0 1 0 1 6.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          |

|                          | 0 1 1 0 3.125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                          |

| Reference frequency data | 0 1 1 1 3.125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                          |

| R0 to R3                 | 1 0 0 0 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

|                          | VDI I MUDIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                          |

|                          | *PLL INHIBIT (Backup mode) Programmable divider stops, and both FMIN and AMIN are set to pull-down state (GND), charge pump output is floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                          |

| Divider select data      | <ul> <li>DV is used to select the input pin (either FMIN or AMIN) of local oscillation signal.</li> <li>SP is used to switch the input frequency range for AMIN selection.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

| DV                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

| Sensitivity select data  | and the state of t |                                                                                                                                                                                                          |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

| SP                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | †                                                                                                                                                                                                        |

|                          | U U AMIN U.5 to 10MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |