#### 捷多邦,专业PCB打样工厂,24小时加急出货

查询LC80101M供应商

#### CMOS LSI

# CCE

VICS LSI

LC80101M

# **Overview**

The LC80101M is a special-purpose descrambler LSI for use in VICS systems. FM multiplexed service data that has had VICS center scrambling applied can be descrambled and received by inserting this LSI in the serial interface between the LC72700E and the application CPU. This architecture also supports reception of regular transmissions that have not been scrambled. Note that sample evaluation and product manufacture using this LSI require a contract with the VICS Center organization.

WWW.DZSC.CO

# **Functions**

- VICS scrambled/unscrambled recognition circuit

- · Dedicated VICS descrambler circuit

- WWW.DZSC.COM • CPU interface circuit (CCB: serial)

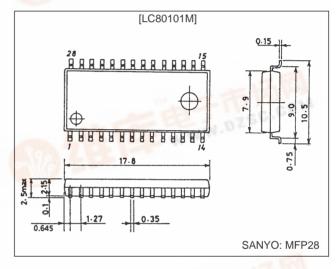

# Package Dimensions

unit: mm

#### 3091A-MFP28

## **Specifications Absolute Maximum Ratings**

| Parameter                   | Symbol              | Conditions                                                                                                      | Ratings                      | Unit |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                                                                                                 | -0.3 to +7.0                 | V    |

|                             | V <sub>IN</sub> 1   | The CL2, CE2, DI2, RST2, BACKUP, INT-R1, and DI1 pins                                                           | -0.3 to +7.0                 | V    |

| Input voltage               | V <sub>IN</sub> 2   | Input pins other than V <sub>IN</sub> 1                                                                         | -0.3 to V <sub>DD</sub> +0.3 | V    |

|                             | V <sub>OUT</sub> 1  | The DO2 pin                                                                                                     | -0.3 to +7.0                 | V    |

| Output voltage              | V <sub>OUT</sub> 2  | Output pins other than V <sub>OUT</sub> 1                                                                       | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Allowable power dissipation | Pdmax               | Ta ≤ 85°C                                                                                                       | 200                          | mW   |

| Operating temperature       | Topr                |                                                                                                                 | -40 to +85                   | °C   |

| Storage temperature         | Tstg                | in the second | -55 to +125                  | °C   |

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus

- addresses are controlled by SANYO.

PDF

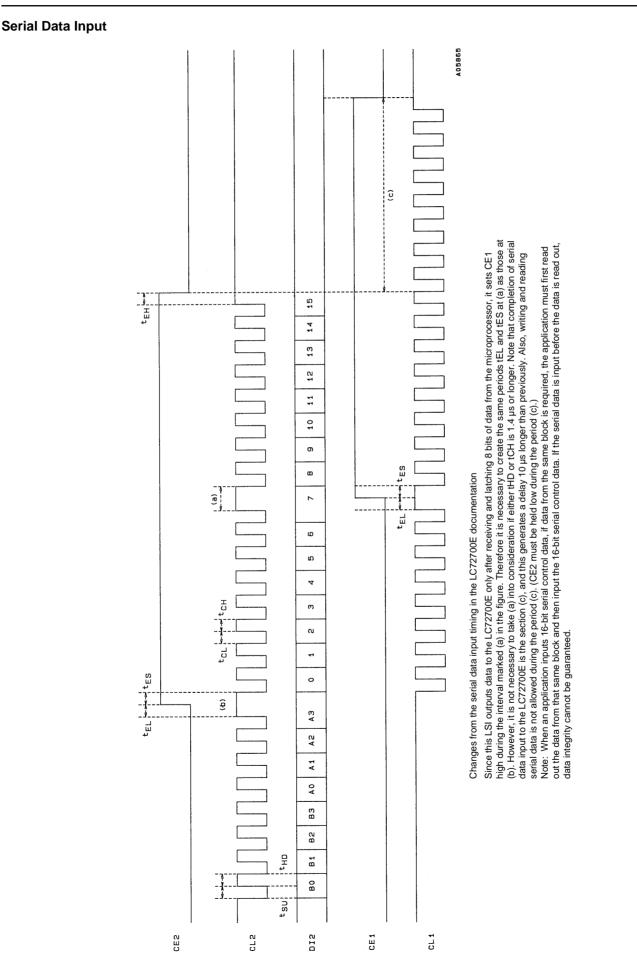

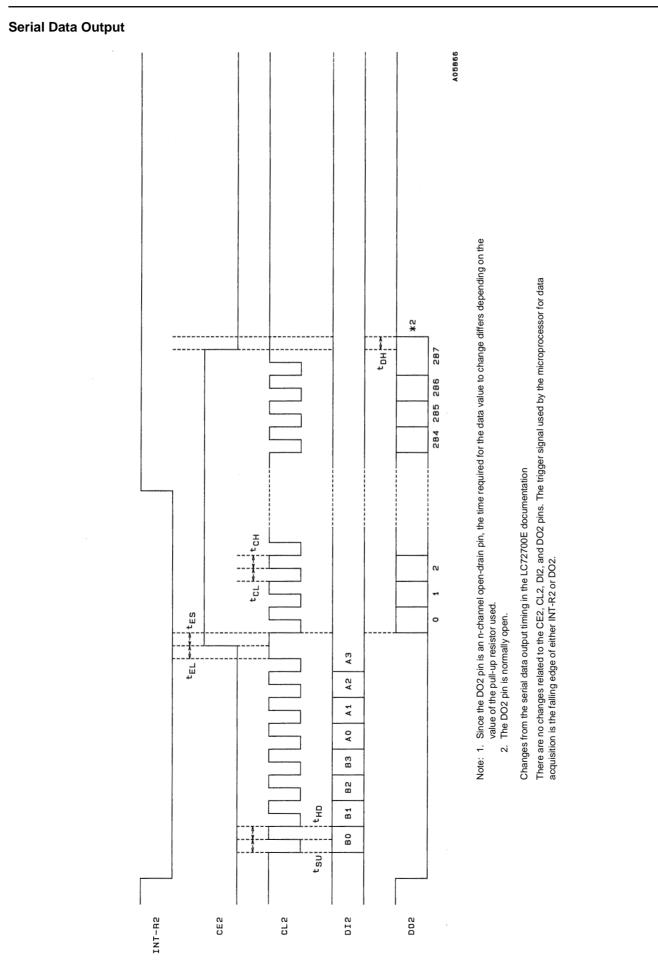

#### Serial Input and Output (See the serial data timing figures.)

| Parameter             | Symbol          | Conditions                                              | Ratings |     |     | Unit |

|-----------------------|-----------------|---------------------------------------------------------|---------|-----|-----|------|

|                       |                 |                                                         | min     | typ | max |      |

| Clock low-level time  | t <sub>CL</sub> | CL2                                                     | 0.7     |     |     | μs   |

| Clock high-level time | t <sub>CH</sub> | CL2                                                     | 0.7     |     |     | μs   |

| Data setup time       | t <sub>SU</sub> | CL2, DI2                                                | 0.7     |     |     | μs   |

| Data hold time        | t <sub>HD</sub> | CL2, DI2                                                | 0.7     |     |     | μs   |

| CE wait time          | t <sub>EL</sub> | CL2, CE2                                                | 0.7     |     |     | μs   |

| CE setup time         | t <sub>ES</sub> | CL2, CE2                                                | 0.7     |     |     | μs   |

| CE hold time          | t <sub>EH</sub> | CL2, CE2                                                | 0.7     |     |     | μs   |

| Data output time      | t <sub>DH</sub> | DO2: Varies with the value of the pull-up resistor used |         |     | 1   | μs   |

### Electrical Characteristics/Input and Output Levels at Ta = -40 to $+85^{\circ}C$ , $V_{DD} = 4.5$ to 5.5 V, $V_{SS} = 0$ V

| Parameter                 | Symbol            | Conditions                                              | Ratings               |      |                     | Unit |

|---------------------------|-------------------|---------------------------------------------------------|-----------------------|------|---------------------|------|

| Falameter                 | Symbol            | Symbol Conditions                                       | min                   | typ  | max                 | Unit |

| Input high-level voltage  | VIH               | CMOS-compatible Schmitt inputs                          | 0.8 V <sub>DD</sub>   |      |                     | V    |

| Input low-level voltage   | VIL               | Pull-down resistors: INT-R1, TEST1 to TEST4, and TESTON |                       |      | 0.2 V <sub>DD</sub> | V    |

| Input high-level voltage  | VIH               | CMOS-compatible Schmitt inputs:                         | 0.8 V <sub>DD</sub>   |      |                     | V    |

| Input low-level voltage   | VIL               | BACKUP, CE2, CL2, DI1, DI2, and RST2                    |                       |      | 0.2 V <sub>DD</sub> | V    |

| Output high-level voltage | V <sub>OH</sub>   | I <sub>OH</sub> = -4 mA: CE1, CL1, DO1, INT-R2          | V <sub>DD</sub> – 2.1 |      |                     | V    |

| Output low-level voltage  | V <sub>OL</sub>   | I <sub>OL</sub> = 4 mA: CE1, CL1, DO1, INT-R2           |                       |      | 0.4                 | V    |

| Output low-level voltage  | V <sub>OL</sub>   | I <sub>OL</sub> = 2 mA: DO2                             |                       |      | 0.4                 | V    |

| Standby current           | lsd               | With the BACKUP pin low                                 |                       | 0.01 | 10                  | μA   |

| Input sensitivity         | Vck               | Rf = 1 MΩ, FILCK1 = 3.6 MHz: FILCK1*1                   | 1.0                   |      | V <sub>DD</sub>     | Vp-p |

| Pull-down resistance      | Rd                | INT-R1, TEST1 to 4, TESTON                              | 70                    | 140  | 280                 | kΩ   |

| Current drain             | I <sub>DD</sub> 1 | Sine wave input: 1 V p-p, V <sub>DD</sub> = 5.0 V*2     |                       | 6    | 15                  | mA   |

|                           | I <sub>DD</sub> 2 | Sine wave input: 5 V p-p, V <sub>DD</sub> = 5.0 V*2     |                       | 2.5  | 7                   | mA   |

|                           | I <sub>DD</sub> 3 | Square wave input: 1 V p-p, V <sub>DD</sub> = 5.0 V*2   |                       | 5    | 13                  | mA   |

|                           | I <sub>DD</sub> 4 | Square wave input: 5 V p-p, V <sub>DD</sub> = 5.0 V*2   |                       | 1.5  | 4                   | mA   |

Note 1. Since this LSI operates based on the rising edge of the LC72700E 3.6 MHz output (the FILCK pin), the LC72700E 3.6 MHz output signal must be input to the FILCK1 pin without inverting the polarity.

The current drain varies with the input level and the shape of the clock signal input to the FILCK1 pin. The current drain can be reduced by using waveforms that are closer to square waves than to sine waves, and by using a signal level that is close to V<sub>DD</sub>. The LC72700E 3.6 MHz output is a square wave with an output level equal to V<sub>DD</sub>.

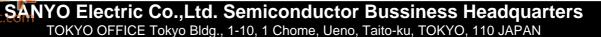

### **Block Diagram**

A05856

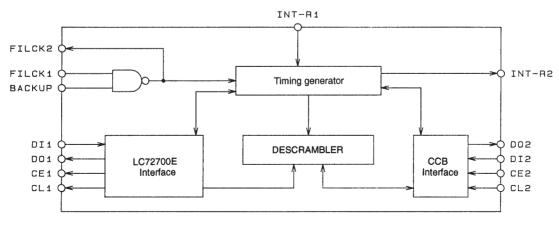

# Pin Assignments and Functions

| Pin No.  | Pin             | Function overview                                                                                             | Input or output circuit type |

|----------|-----------------|---------------------------------------------------------------------------------------------------------------|------------------------------|

|          | TEST1           | Test pin 1 (Must be connected to ground or left open in normal operation.)                                    |                              |

| 1        | TEST2           | Test pin 2 (Must be connected to ground or left open in normal operation.)                                    |                              |

| 9        | TEST3           | Test pin 3 (Must be connected to ground or left open in normal operation.)                                    |                              |

| 19       | TEST4           | Test pin 4 (Must be connected to ground or left open in normal operation.)                                    | ₹Rd                          |

| 27       | TESTON          | Test pin (Must be connected to ground in normal operation.)                                                   |                              |

| 13       |                 | Rd: Input pin internal pull-down resistor                                                                     | A05857                       |

| 5        | DI1             | Inputs the output of the LC72700E pin 32. An external pull-down resistor is required. See the following page. |                              |

| 20       | BACKUP          | Input that selects normal operation when high and backup mode when low.                                       |                              |

| 21       | CL2             | Clock input for the CCB serial interface                                                                      |                              |

| 22       | CE2             | Control input for the CCB serial interface                                                                    |                              |

| 23       | DI2             | Data input for the CCB serial interface                                                                       | A05858                       |

| 26       | RST2            | System reset input (negative logic)                                                                           |                              |

| 4        | INT-R1          | Inputs the output of the LC72700E pin 35.                                                                     |                              |

|          |                 | Rd: Input pin internal pull-down resistor                                                                     | Rd<br>→                      |

| <u> </u> | <b>DO1</b>      |                                                                                                               |                              |

| 6        | DO1             | Output to the LC72700E pin 31 input                                                                           |                              |

| 7        | CE1             | Output to the LC72700E pin 30 input                                                                           |                              |

| 8        | CL1             | Output to the LC72700E pin 29 input                                                                           | A05850                       |

| 25       | INT-R2          | Outputs an output data interrupt to the external CPU                                                          |                              |

| 24       | DO2             | Data output for the CCB serial interface                                                                      | A05861                       |

| 2        | FILCK1          | System clock generator input                                                                                  |                              |

| 3        | FICLK2          | System clock generator output                                                                                 |                              |

|          |                 |                                                                                                               |                              |

|          |                 | Rf: External feedback resistor, 510 k $\Omega$ to 1.5 M $\Omega$ (typical: 1 M $\Omega)$                      | Rf \$                        |

| 28       | V <sub>DD</sub> | Power supply (+4.5 to 5.5 V)                                                                                  |                              |

| 14       | V <sub>SS</sub> | Ground connection                                                                                             |                              |

|          | • • • •         |                                                                                                               |                              |

| 10, 11,  | NC              | No connection pins. These pins must be left open.                                                             |                              |

| 12, 15,  |                 |                                                                                                               |                              |

| 16, 17   |                 |                                                                                                               |                              |

| 18       |                 |                                                                                                               |                              |

|          |                 |                                                                                                               |                              |

|          |                 |                                                                                                               |                              |

|          |                 |                                                                                                               |                              |

LC80101M

#### **Pin Assignment**

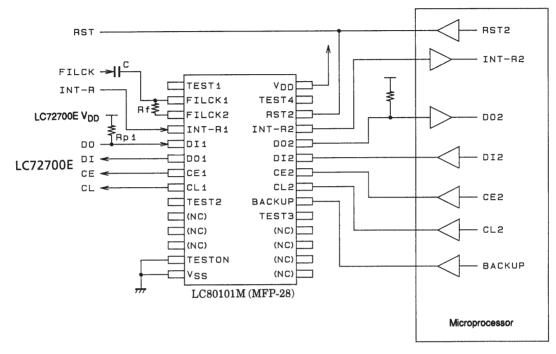

Notes on the pull-up resistor used between the LC72700E pin 32 (DO) and this LSI's pin 5 (DI1)

The value of the pull-up resistor Rp1 must be determined based on the printed circuit board's floating capacitance and the LC80101M's clock. The time  $t_{CL}$  for the LC80101M clock is 1.1 µs (corresponding to 450 kHz). This clock is used as the readout clock output to the LC72700E during the period discussed in note 1 for the basic timing of the external interface as discussed on page 7. If the  $t_{CL}$  of the CL2 clock from the microprocessor is longer than the  $t_{CL}$  of the LC80101M clock, a  $t_{CL}$  of 1.1 µs must be used in the formulas below. If the  $t_{CL}$  of that clock is shorter than that of the LC80101M clock, then the  $t_{CL}$  of CL2 must be substituted in the formulas below.

For example, in the configuration shown in the figure above, assuming the  $t_{CL}$  of CL2 is 1.0 µs (i.e. CL2 = 500 kHz), then:  $T = t_{CL} - 555$  ns (the LC72700E data output time)

Since  $T \approx 2.2 (C1 + C2) R$

$$Rp1 \approx \frac{445 \text{ ns}}{2.2 (C1 + C2)}$$

Assuming that C1 = 10 pF and C2 = 10 pF, then Rp1 will be  $\leq 10.1 \text{ k}\Omega$ . These considerations must be used as guidelines when determining the value of the pull-up resistor Rp1.

#### Figure 1

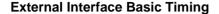

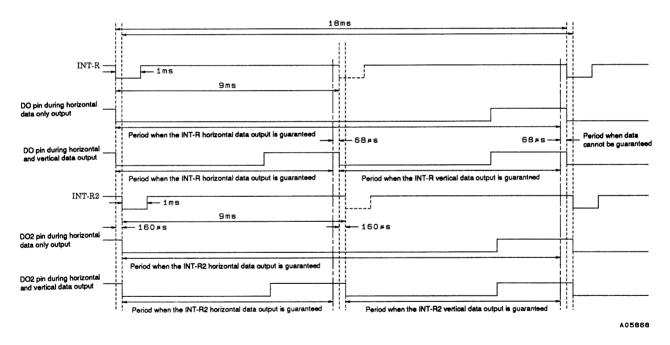

Figure 1 shows how the timing changes between the LC72700E INT-R output and this LSI's INT-R2 output. This LSI requires the period indicated as "Note 1", about 160 µs, following the detection of a falling edge on the INT-R signal to set up the descrambling processing. It outputs a falling edge on INT-R2 after the note 1 time has elapsed. Serial data reads and writes are disabled during this period.

Figure 2 shows the basic timing for the external interface. When this LSI is not used and the system is operated based on the INT-R trigger, if only horizontal data is output, there will be a data readout guaranteed period of 18 - 0.068 = 17.932 ms, and if both horizontal and vertical data are read out, there will be two 9 - 0.068 = 8.932 ms data readout guaranteed periods, one each for horizontal and vertical data output. When this LSI is used and the system is operated based on the INT-R2 trigger, these data readout guaranteed periods are shortened by exactly the amount the INT-R2 signal is delayed, namely 160 µs. When only horizontal data is output, the data readout guaranteed period will be 17.932 - 0.160 = 17.772 ms, and both horizontal and vertical data is output, the data readout guaranteed periods will be 8.932 - 0.160 = 8.772 ms for both horizontal and vertical data output.

#### **Usage Notes**

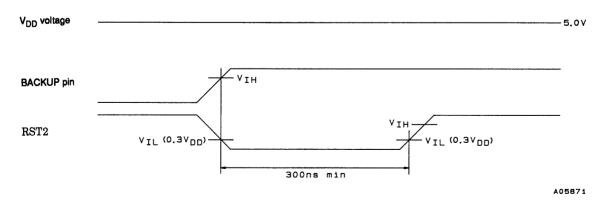

- Setting the BACKUP pin low switches the LC80101M to backup mode. This is a mode in which oscillator and chip operation are stopped to reduce current drain. This pin must be set high for normal operation. Also note that a reset must be applied after the BACKUP pin is returned to high from low. (See Figure 4 on page 8.) The BACKUP pin must be connected to the LC80101M V<sub>DD</sub> pin if backup mode is not used.

- 2. The lines connecting this LSI to the LC72700E must be dedicated lines only used by these two chips. Do not connect these lines to any other circuits via a bus or any other connection.

- 3. A reset must be applied when power is first applied. The LC72700E RST pin and this LSI's RST2 pin can be driven from a common signal. (See Figure 3 on page 8.)

- 4. The TESTON pin (pin 13) must be connected to ground.

#### **Operation During Reset**

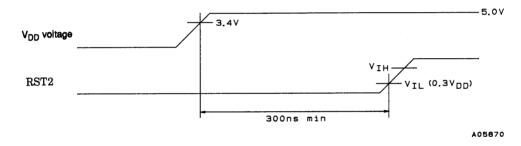

A reset signal is applied by setting the RST2 pin input level below  $V_{IL}$  for at least 300 ns when the power-supply voltage ( $V_{DD}$ ) is 3.4 V or higher. See Figure 3.

All registers other than those holding data required for descrambling are reset by a reset signal. The crystal oscillator circuit does not stop.

#### **BACKUP** Pin

A reset must be applied after the BACKUP pin is returned to high (for normal operation from low (backup mode, in which the oscillator is stopped). See the following figure.

LC80101M

A05869

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.