Ordering number : EN5663

**CMOSIC**

## LC83026E

# **Digital Signal Processor for Karaoke Systems**

### **Overview**

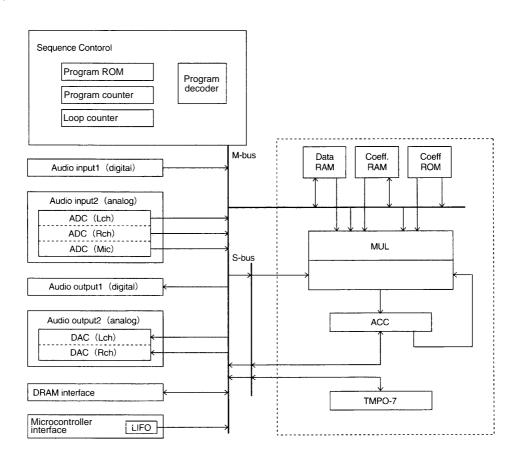

The LC83026E provides the audio signal processing required in karaoke systems, including pitch shift, microphone echo, voice muting, and simple surround simulation. It is a special-purpose DSP that implements karaoke processing with the addition of a single external 256-Kb DRAM. The LC83026E includes on-chip A/D and D/A converters and supports both digital and analog inputs and outputs. Its functions and characteristics can be modified to match the needs of the end product by sending coefficient data from the microcontroller over a serial interface.

#### **Features**

- Application features

- Pitch shift

The LC83026E supports pitch shifting of  $\pm 15$  quarter tone steps, or  $\pm 1$  octave in scale tone units as specified by command data. This pitch shifting can be applied either to the music track or to the microphone input. It is also possible to set up pitch shifting of  $\pm 1$  octave in arbitrary steps by setting coefficient values.

- Microphone echo

The LC83026E can apply echo processing to the input signal from the microphone A/D converter. The echo coefficients, including amount of echo and delay time, can be set.

Voice muting

The LC83026E provides attenuation of monaural components in the music signal. This allows CDs that include vocals to be used for karaoke. The voice muting function is turned on or off by command data transferred over the serial interface.

Simple surround

The LC83026E implements a simple surround simulation function by adding delay components to the music signal. The LC83026E includes six sets of simple surround coefficients as preset data, and these can be selected and switched using command data transferred over the serial interface. User-original surround effects can be implemented by setting

coefficients, but the algorithm is fixed.

— Versatile input mixing

The LC83026E supports hybrid mixing of digital music inputs and analog music inputs for both the left and right channels to support the processing of a wide range of disks.

· Audio inputs and outputs

Inputs: Digital One system (stereo)

A/D converters Three channels

Outputs: Digital One system (stereo)

D/A converters Two channels

A/D converters

Second-order delta-sigma modulation

Three channels

— D/A converters

2× oversampling digital filters + third-order noise shaper system Two channels

• Master clock: 768fs

- External memory: Up to two 256K (64K × 4 bits) external DRAMs can be used.

- Microcontroller input: Synchronous 8-bit serial data

- Power-supply voltage: 5V single-voltage supply

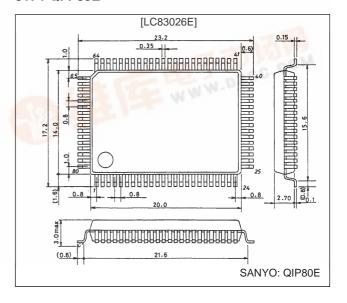

- Package: QFP80E

## Package Dimensions

unit: mm

#### 3174-QFP80E

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

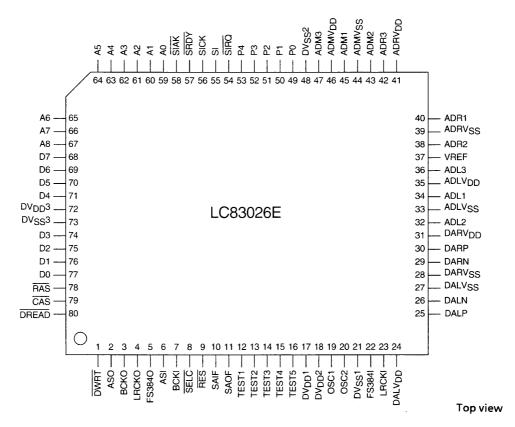

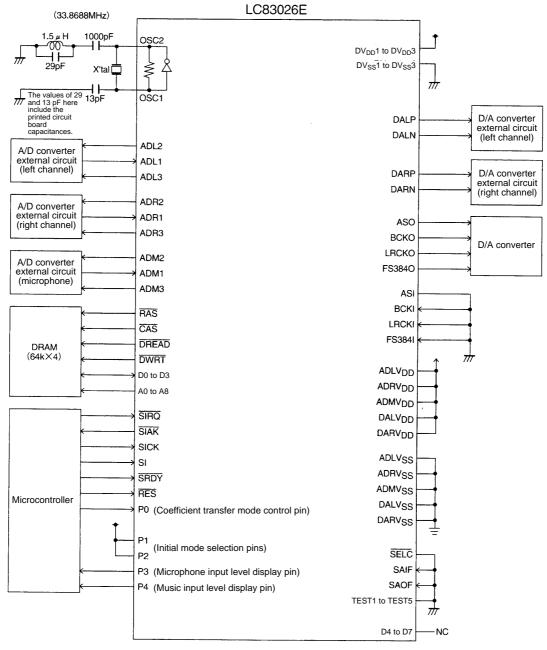

### **Pin Assignment**

A07310

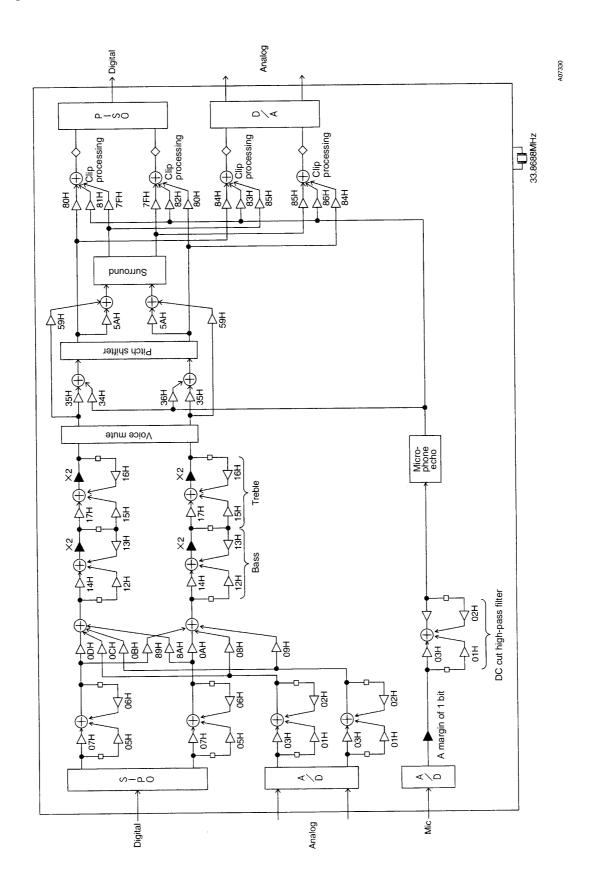

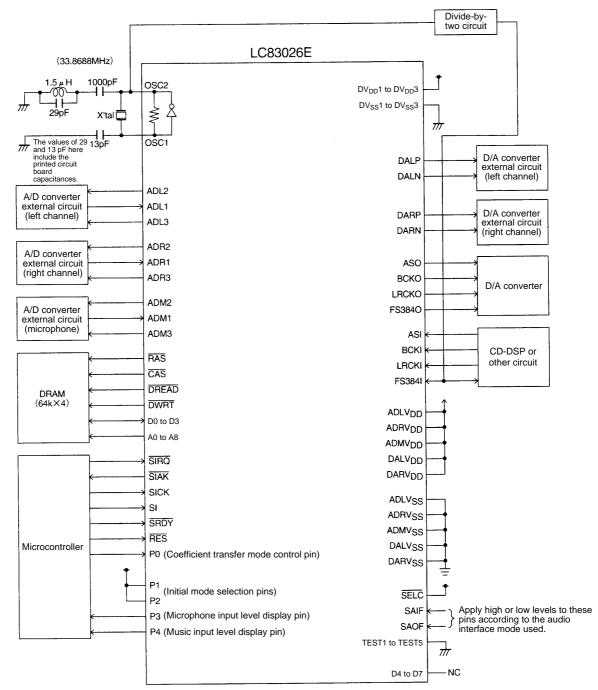

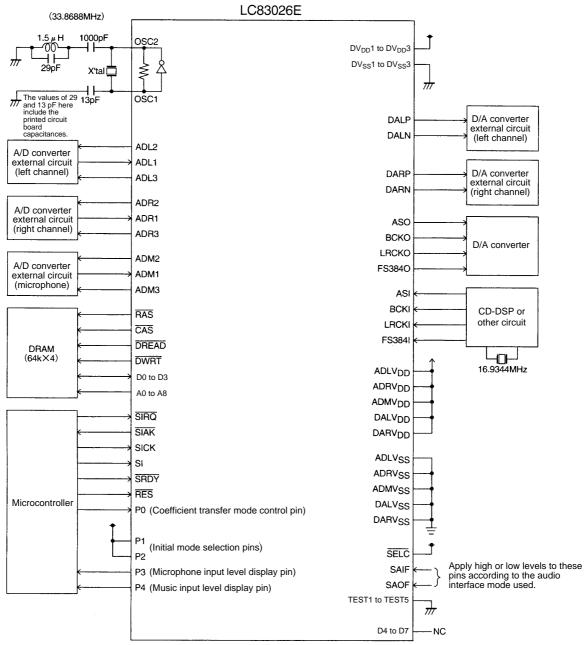

#### **Block Diagram**

A07311

### **Pin Functions**

|                           | Pin        | Pin No.   | I/O      | Function                                                                                                    |

|---------------------------|------------|-----------|----------|-------------------------------------------------------------------------------------------------------------|

|                           | OSC1       | 19        | ı        | Crystal oscillator connection (768fs)                                                                       |

|                           | OSC2       | 20        | 0        | Crystal oscillator connection (768fs)                                                                       |

|                           | FS384I     | 22        | ı        | 384fs input                                                                                                 |

|                           | SELC       | 8         | ı        | Audio clock source switching (High: external, low: internal)                                                |

| S                         | SAIF       | 10        | 1        | Digital audio input mode switching (Low: backward packing, high: forward packing)                           |

| pins                      | SAOF       | 11        | ı        | Digital audio output mode switching (Low: 48fs, high 64fs)                                                  |

| Control pins              | RES        | 9         | ı        | Reset                                                                                                       |

| Co                        | TEST5 to 1 |           | ı        | Test (Must be connected to ground during normal operation.)                                                 |

|                           | P0         | 49        | ı        | Coefficient transfer mode control                                                                           |

|                           | P2 to P1   | 51, 50    | ı        | Initial operating mode control (A high level should be applied for normal operation.)                       |

|                           | P3         | 52        | 0        | Microphone signal input level: Yes (low output)/No (high output) output                                     |

|                           | P4         | 53        | 0        | Music signal input level: Yes (low output)/No (high output)                                                 |

| e                         | RAS        | 78        | 0        | RAS signal output                                                                                           |

| erfa                      | CAS        | 79        | 0        | CAS signal output                                                                                           |

| y inf                     | DREAD      | 80        | 0        | External memory read signal output                                                                          |

| emol                      | DWRT       | 1         | 0        | External memory write signal output                                                                         |

| alu                       | A8 to A0   | 67 to 59  | 0        | Address output                                                                                              |

| External memory interface | D7 to D0   | 68 to 71, | I/O      | Data input and output (Normally only D0 to D3 are used)                                                     |

| ũ                         |            | 74 to 77  |          |                                                                                                             |

|                           | LRCKI      | 23        | I        | ASI L/R clock input (1fs)                                                                                   |

|                           | LRCKO      | 4         | 0        | ASO L/R clock output (1fs)                                                                                  |

|                           | BCKI       | 7         | ı        | ASI bit clock input (32fs or higher)                                                                        |

|                           | BCKO       | 3         | 0        | ASO bit clock output (48fs or 64fs)                                                                         |

|                           | FS384O     | 5         | 0        | ASO 384fs output                                                                                            |

|                           | ASI        | 6         | I        | Digital audio data input (16-bits, MSB first)                                                               |

|                           | ASO        | 2         | 0        | Digital audio data output (16-bits, MSB first, backward packed)                                             |

|                           | ADL1       | 34        | I        | A/D converter input (left channel)                                                                          |

| Audio interface           | ADL2       | 32        | 0        | A/D converter output (left channel)                                                                         |

| inter                     | ADL3       | 36        | 0        | A/D converter output (left channel)                                                                         |

| dio                       | ADR1       | 40        | ı        | A/D converter input (right channel)                                                                         |

| Au                        | ADR2       | 38        | 0        | A/D converter output (right channel)                                                                        |

|                           | ADR3       | 42        | 0        | A/D converter output (right channel)                                                                        |

|                           | ADM1       | 45        | I        | A/D converter input (microphone)                                                                            |

|                           | ADM2       | 43        | 0        | A/D converter output (microphone)                                                                           |

|                           | ADM3       | 47        | 0        | A/D converter output (microphone)                                                                           |

|                           | DALP       | 25        | 0        | D/A converter output (left channel)                                                                         |

|                           | DALN       | 26        | 0        | D/A converter output (left channel)                                                                         |

|                           | DARP       | 30        | 0        | D/A converter output (right channel)                                                                        |

|                           | DARN       | 29        | 0        | D/A converter output (right channel)                                                                        |

| ıface                     | SIRQ       | 54        | 1        | Input for the serial input request signal                                                                   |

| Microcontroller interface | SIAK       | 58        | 0        | Output that indicates that a serial input is in progress                                                    |

| ontrolle                  | SI         | 55        | <br>     | Serial data input from the control microcontroller (8-bit serial input)                                     |

| icrocc                    | SICK       | 56        | I<br>  . | SI pin transfer clock input                                                                                 |

| ≥                         | SRDY       | 57        | ı        | Ready signal input (from the control microcontroller) that indicates the completion of a serial data input. |

## Continued from preceding page.

|             | Pin                     | Pin No.    | I/O |                                                                                                                                                                                                                                         | Function                                                                                                              |                                                                                                                           |  |  |  |  |  |

|-------------|-------------------------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|             | DV <sub>DD</sub> 1 to 3 | 17, 18, 72 | _   | Digital block V <sub>DD</sub> (Must be connected to +5 V.)                                                                                                                                                                              | al block V <sub>DD</sub> (Must be connected to +5 V.)                                                                 |                                                                                                                           |  |  |  |  |  |

|             |                         |            |     | ke connections as short as possible so that no potential differences occur between any of the V <sub>DD</sub> pins.>                                                                                                                    |                                                                                                                       |                                                                                                                           |  |  |  |  |  |

|             | DV <sub>SS</sub> 1 to 3 | 21, 48, 73 | _   | Digital block V <sub>SS</sub> (Must be connected to ground.)                                                                                                                                                                            | ital block V <sub>SS</sub> (Must be connected to ground.)                                                             |                                                                                                                           |  |  |  |  |  |

|             |                         |            |     | <make as="" connections="" no="" possible="" poter<="" short="" so="" td="" that=""><td colspan="6">ake connections as short as possible so that no potential differences occur between any of the V<sub>SS</sub> pins.&gt;</td></make> | ake connections as short as possible so that no potential differences occur between any of the V <sub>SS</sub> pins.> |                                                                                                                           |  |  |  |  |  |

|             | ADLV <sub>DD</sub>      | 35         | _   | A/D converter V <sub>DD</sub> (left channel) (Connect to +5 V.)                                                                                                                                                                         |                                                                                                                       |                                                                                                                           |  |  |  |  |  |

| <u>&gt;</u> | ADRV <sub>DD</sub>      | 41         | _   | A/D converter V <sub>DD</sub> (right channel) (Connect to +5 V.)                                                                                                                                                                        | l                                                                                                                     | esign the wiring so that potential differences do                                                                         |  |  |  |  |  |

| supply      | $ADMV_{DD}$             | 46         | _   | A/D converter V <sub>DD</sub> (microphone) (Connect to +5 V.)                                                                                                                                                                           | , , ,                                                                                                                 | ot occur between the analog system V <sub>DD</sub> pins and ither other analog system V <sub>DD</sub> pins or the digital |  |  |  |  |  |

|             | DALV <sub>DD</sub>      | 24         | _   | D/A converter V <sub>DD</sub> (left channel) (Connect to +5 V.)                                                                                                                                                                         | l                                                                                                                     | ystem V <sub>DD</sub> pins.                                                                                               |  |  |  |  |  |

| Power       | DARV <sub>DD</sub>      | 31         | _   | D/A converter V <sub>DD</sub> (right channel) (Connect to +5 V.)                                                                                                                                                                        |                                                                                                                       | )                                                                                                                         |  |  |  |  |  |

|             | ADLV <sub>SS</sub>      | 33         | _   | A/D converter V <sub>SS</sub> (left channel) (Connect to ground.)                                                                                                                                                                       |                                                                                                                       | <u>`</u>                                                                                                                  |  |  |  |  |  |

|             | ADRV <sub>SS</sub>      | 39         | _   | A/D converter V <sub>SS</sub> (right channel) (Connect to ground.)                                                                                                                                                                      | D                                                                                                                     | esign the wiring so that potential differences do                                                                         |  |  |  |  |  |

|             | ADMV <sub>SS</sub>      | 44         | _   | A/D converter V <sub>SS</sub> (microphone) (Connect to ground.)                                                                                                                                                                         | l                                                                                                                     | ot occur between the analog system V <sub>SS</sub> pins and                                                               |  |  |  |  |  |

|             | DALV <sub>SS</sub>      | 27         | _   | D/A converter V <sub>SS</sub> (left channel) (Connect to ground.)                                                                                                                                                                       | l .                                                                                                                   | ither other analog system V <sub>SS</sub> pins or the digital ystem V <sub>SS</sub> pins.                                 |  |  |  |  |  |

|             | DARV <sub>SS</sub>      | 28         | _   | D/A converter V <sub>SS</sub> (right channel) (Connect to ground.)                                                                                                                                                                      | ( "                                                                                                                   | ,                                                                                                                         |  |  |  |  |  |

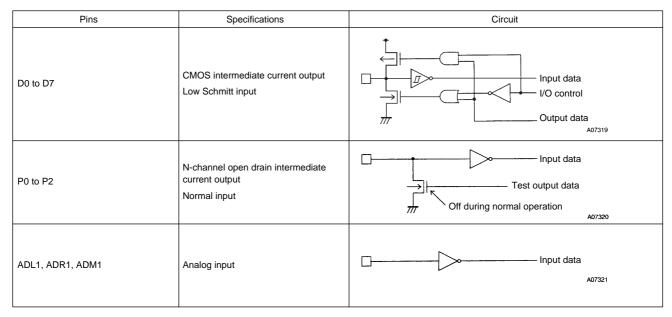

### **Pin Circuits**

| Pins                                                      | Specifications                         | Circuit                               |

|-----------------------------------------------------------|----------------------------------------|---------------------------------------|

| ASO, LRCKO, BCKO, RAS, CAS, DREAD, DWRT, FS384O, A0 to A8 | TTL output                             |                                       |

| P3, P4, SIAK                                              | CMOS intermediate current output       | Output data                           |

| ADL2, ADL3, ADM2, ADM3, ADR2, ADR3                        | Analog sydnyd                          | Output data                           |

| DALP, DALN, DARP, DARN                                    | - Analog output                        | Output data                           |

| SI, SICK, SIRQ, SRDY, (OSC1)                              | Schmitt input                          | □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ |

| FS384I, BCKI, ASI, LRCKI                                  | Low Schmitt input                      | A07315                                |

| TEST1 to TEST5                                            | Normal input                           | Input data                            |

| RES                                                       | Input with built-in pull-up resistor   | Input data A07317                     |

| SELC, SAIF, SAOF                                          | Input with built-in pull-down resistor | Input data  A07318                    |

Continued from preceding page.

# **Specifications**

# Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                   | Symbol              | Conditions                                                      | Ratings                      | Unit | Notes |

|-----------------------------|---------------------|-----------------------------------------------------------------|------------------------------|------|-------|

| Maximum supply voltage      | V <sub>DD</sub> max |                                                                 | -0.3 to +7.0                 | V    |       |

| Input voltage               | V <sub>IN</sub>     |                                                                 | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| Output voltage              | V <sub>O</sub> 1    | V <sub>O</sub> 1 OSC2 output                                    |                              | V    |       |

|                             | V <sub>O</sub> 2    | Outputs other than OSC2                                         | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

|                             | I <sub>OP</sub> 1   | Audio interface, external RAM interface                         | -2 to +4                     | mA   | 1     |

| Peak output current         | I <sub>OP</sub> 2   | Microcontroller interface, P3, P4                               | -2 to +10                    | mA   | 2     |

|                             | I <sub>OA</sub> 1   | Audio interface, external RAM interface: Per pin                | -2 to +4                     | mA   | 1     |

|                             | I <sub>OA</sub> 2   | Microcontroller interface, P3, P4: Per pin                      | -2 to +10                    | mA   | 2     |

| Average output current      | Σl <sub>OA</sub> 1  | FS384O, LRCKO, BCKO, ASO : Total                                | -10 to +10                   | mA   |       |

|                             | Σl <sub>OA</sub> 2  | DWRT, DREAD, RAS, CAS, A0 to A8, D0 to D7, SIAK, P3, P4 : Total | -10 to +10                   | mA   |       |

| Allowable power dissipation | Pd max              | Ta = -30 to +70°C                                               | 700                          | mW   |       |

| Operating temperature       | Topr                |                                                                 | -30 to +70                   | °C   |       |

| Storage temperature         | Tstg                |                                                                 | -40 to +125                  | °C   |       |

# Allowable Operating Ranges at Ta = -30 to $+70^{\circ}C$ , all $V_{DD} = 4.75$ to 5.25 V, all $V_{SS} = 0$ V unless otherwise specified

| Parameter                | Symbol            | Conditions                                    |                      | Linit | Notes                |       |       |

|--------------------------|-------------------|-----------------------------------------------|----------------------|-------|----------------------|-------|-------|

| Falametei                | Symbol            | Conditions                                    | min                  | typ   | max                  | Offic | Notes |

| Operating supply voltage | V <sub>DD</sub>   |                                               | 4.75                 |       | 5.25                 | V     |       |

|                          | V <sub>IH</sub> 1 | Audio interface and external RAM interface    | 2.4                  |       |                      | ٧     | 4     |

| Input high-level voltage | V <sub>IH</sub> 2 | P0 to P2, SELC, SAIF, SAOF,<br>TEST1 to TEST5 | 0.7 V <sub>DD</sub>  |       |                      | ٧     | 5     |

|                          | V <sub>IH</sub> 3 | RES, OSC1, and the microcontroller interface  | 0.75 V <sub>DD</sub> |       |                      | ٧     | 6     |

|                          | V <sub>IL</sub> 1 | Audio interface and external RAM interface    |                      |       | 0.8                  | ٧     | 4     |

| Input low-level voltage  | V <sub>IL</sub> 2 | P0 to P2, SELC, SAIF, SAOF,<br>TEST1 to TEST5 |                      |       | 0.3 V <sub>DD</sub>  | ٧     | 5     |

|                          | V <sub>IL</sub> 3 | RES, OSC1, and the microcontroller interface  |                      |       | 0.25 V <sub>DD</sub> | ٧     | 6     |

| Instruction cycle time   | t <sub>CYC</sub>  |                                               | 58                   |       | 59.11                | ns    |       |

## Continued from preceding page.

| Parameter                                   | Cumbal            | Symbol Conditions -                                                                |          | Ratings |       | Unit    | Natas |

|---------------------------------------------|-------------------|------------------------------------------------------------------------------------|----------|---------|-------|---------|-------|

| Parameter                                   | Symbol            | Conditions                                                                         | min      | typ     | max   | Uniii   | Notes |

| [External Clock Input Conditions]           |                   |                                                                                    |          |         |       |         |       |

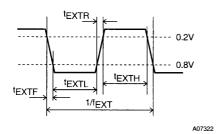

| Frequency                                   | f <sub>EXT</sub>  | Related to the FS384I pin. See Figure 1.                                           | 16.85    |         | 17.01 | MHz     |       |

| 5.1                                         | f <sub>EXTH</sub> | maximum: 44.1 kHz × 384 × 1.005                                                    | 23       |         |       | ns      |       |

| Pulse width                                 | f <sub>EXTL</sub> | minimum: 44.1 kHz × 384 × 0.995                                                    | 23       |         |       | ns      |       |

| Rise time                                   | t <sub>EXTR</sub> |                                                                                    |          |         | 9     | ns      |       |

| Fall time                                   | t <sub>EXF</sub>  |                                                                                    |          |         | 9     | ns      |       |

| [Self-Excited Oscillation Conditions(crysta | l oscillator)]    |                                                                                    |          |         |       |         |       |

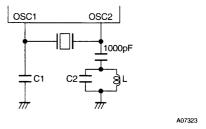

| Oscillator frequency                        | fosc              | OSC1 and OSC2. See Figure 2.                                                       | 33.84    |         | 40.55 | MHz     |       |

| Commuter frequency                          | 1080              | 44.1 kHz/48 kHz × 768 ±0.1%                                                        | 33.04    |         | 40.00 | 1411 12 |       |

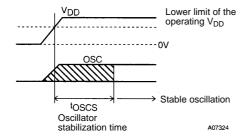

| Oscillator stabilization period             | toscs             | See Figure 3.                                                                      |          |         | 100   | ms      |       |

| [Audio Data Input Conditions]               | <u>.</u>          |                                                                                    | •        |         |       |         |       |

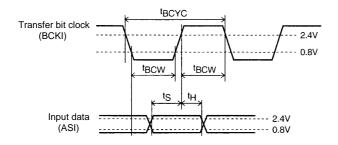

| Transfer bit clock period                   | t <sub>BCYC</sub> | Related to BCKI. See Figure 4.                                                     | 354      |         |       | ns      |       |

| Transfer bit clock pulse width              | t <sub>BCW</sub>  |                                                                                    | 100      |         |       | ns      |       |

| Data setup time                             | t <sub>S</sub>    |                                                                                    | 70       |         |       | ns      |       |

| Data hold time                              | t <sub>H</sub>    |                                                                                    | 70       |         |       | ns      |       |

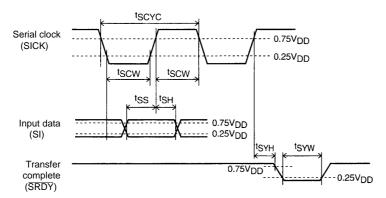

| [Serial I/O Clock Conditions]               |                   |                                                                                    |          |         |       |         |       |

| Serial clock period                         | t <sub>SCYC</sub> |                                                                                    | 480      |         |       | ns      |       |

| Serial clock pulse width                    | t <sub>SCW</sub>  | ]                                                                                  | 200      |         |       | ns      |       |

| Data setup time                             | t <sub>SS</sub>   | Related to the microcontroller interface.  See Figure 5. (Related to SICK, SI, and | 70       |         |       | ns      |       |

| Data hold time                              | t <sub>SH</sub>   | SRDY.)                                                                             | 70       |         |       | ns      |       |

| SRDY hold time                              | t <sub>SYH</sub>  |                                                                                    | 200      |         |       | ns      |       |

| SRDY pulse width                            | t <sub>SYW</sub>  |                                                                                    | 200      |         |       | ns      |       |

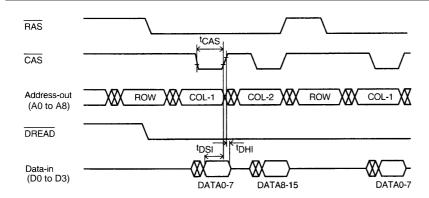

| [DRAM Input Conditions]                     |                   |                                                                                    | <u>'</u> |         |       | •       |       |

| Input data setup time                       | t <sub>DSI</sub>  | Related to external DRAM data input. See                                           | 20       |         |       | ns      |       |

| Input data hold time                        | t <sub>DHI</sub>  | Figure 6. (Related to CAS and D0 to D7.)                                           | 0        |         |       | ns      |       |

# Electrical Characteristics 1 at Ta = -30 to $+70^{\circ}$ C, all $V_{DD}$ = 4.75 to 5.25 V, all $V_{SS}$ = 0 V unless otherwise specified

| Dorometer                    | Cumbal            | Conditions                                                                                | Ratings              |       |     |      | Notes |

|------------------------------|-------------------|-------------------------------------------------------------------------------------------|----------------------|-------|-----|------|-------|

| Parameter                    | Symbol            | Conditions                                                                                | min                  | typ   | max | Unit | Notes |

| Input high-level current     | I <sub>IH</sub> 1 | SELC, SAIF, SAOF, V <sub>IN</sub> = V <sub>DD</sub> (Input pins with pull-down resistors) |                      | 100   | 250 | μА   | 8     |

| Input night-level current    | I <sub>IH</sub> 2 | P0 to P2, V <sub>IN</sub> = V <sub>DD</sub> (Nch transistor OFF)                          |                      |       | 10  | μA   |       |

|                              | I <sub>IH</sub> 3 | Other input-only pins                                                                     |                      |       | 10  | μA   |       |

|                              | I <sub>IL</sub> 1 | RES, V <sub>IN</sub> = V <sub>SS</sub> (Input pins with pull-up resistors)                | -250                 | -100  |     | μА   | 8     |

| Input low-level current      | I <sub>IL</sub> 2 | P0 to P2, V <sub>IN</sub> = V <sub>SS</sub>                                               | -10                  |       |     | μA   |       |

|                              | I <sub>IL</sub> 3 | Other input-only pins                                                                     | -10                  |       |     | μA   |       |

| 0                            | V <sub>OH</sub> 1 | I <sub>OH</sub> = -0.4 mA                                                                 | 4.0                  | 4.98  |     | V    | 1, 8  |

| Output high-level voltage    | V <sub>OH</sub> 2 | I <sub>OH</sub> = -50 μA                                                                  | V <sub>DD</sub> -1.2 | 4.997 |     | V    | 2,3,8 |

| 0                            | V <sub>OL</sub> 1 | I <sub>OL</sub> = 2 mA                                                                    |                      | 0.065 | 0.4 | V    | 1, 8  |

| Output low-level voltage     | V <sub>OL</sub> 2 | I <sub>OL</sub> = 10 mA                                                                   |                      | 0.32  | 1.5 | V    | 2,3,8 |

| Output off leakage current   | loff              | $V_O = V_{SS}, V_{DD}$                                                                    | -40                  |       | +40 | μA   |       |

| Input and output capacitance | C <sub>IO</sub>   |                                                                                           |                      |       | 10  | pF   |       |

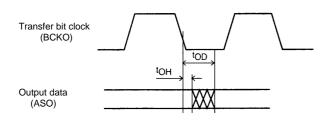

| [Audio Data Output Timing]   |                   |                                                                                           |                      |       |     |      |       |

| Output data hold time        | tон               | BCK0 and ASO. See Figure 7.                                                               | -30                  |       |     | ns   | 7     |

| Output data delay time       | t <sub>OD</sub>   | Botto and ASO. See Figure 7.                                                              |                      |       | 50  | ns   | 7     |

#### Continued from preceding page.

| Parameter                     | Cymphal          | Conditions                                                                                     |     | Ratings |     | Unit | Notes |

|-------------------------------|------------------|------------------------------------------------------------------------------------------------|-----|---------|-----|------|-------|

| Parameter                     | Symbol           | Conditions                                                                                     | min | typ     | max |      |       |

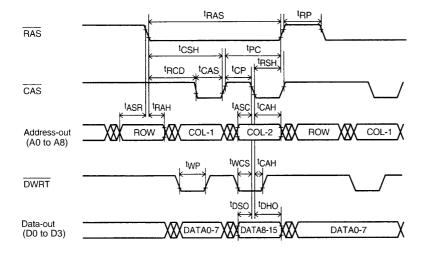

| [External DRAM Access Timing] | •                |                                                                                                |     |         |     |      |       |

| RAS high-level pulse width    | t <sub>RP</sub>  |                                                                                                | 80  |         |     | ns   | 7     |

| RAS low-level pulse width     | t <sub>RAS</sub> |                                                                                                | 700 |         |     | ns   | 7     |

| CAS high-level pulse width    | t <sub>CP</sub>  |                                                                                                | 50  |         |     | ns   | 7     |

| CAS low-level pulse width     | t <sub>CAS</sub> |                                                                                                | 95  |         |     | ns   | 7     |

| CAS cycle time                | t <sub>PC</sub>  |                                                                                                | 175 |         |     | ns   | 7     |

| RAS to CAS delay time         | t <sub>RCD</sub> |                                                                                                | 60  |         |     | ns   | 7     |

| CAS hold time                 | t <sub>CSH</sub> |                                                                                                | 170 |         |     | ns   | 7     |

| RAS hold time                 | t <sub>RSH</sub> | Output timing to the external DRAM.  See Figure 8.                                             | 95  |         |     | ns   | 7     |

| RAS address setup time        | t <sub>ASR</sub> |                                                                                                | 60  |         |     | ns   | 7     |

| RAS address hold time         | t <sub>RAH</sub> |                                                                                                | 20  |         |     | ns   | 7     |

| CAS address setup time        | t <sub>ASC</sub> |                                                                                                | 30  |         |     | ns   | 7     |

| CAS address hold time         | t <sub>CAH</sub> |                                                                                                | 90  |         |     | ns   | 7     |

| DWRT pulse width              | t <sub>WP</sub>  |                                                                                                | 95  |         |     | ns   | 7     |

| Write command setup time      | twcs             |                                                                                                | 12  |         |     | ns   | 7     |

| Write command hold time       | twch             |                                                                                                | 65  |         |     | ns   | 7     |

| Output data setup time        | t <sub>DSO</sub> | Output timing to the external DRAM.                                                            | 30  |         |     | ns   | 7     |

| Output data hold time         | t <sub>DHO</sub> | See Figure 8.                                                                                  | 100 |         |     | ns   | 7     |

|                               | C1               |                                                                                                |     | 13      |     | pF   | 8     |

| Crystal oscillator            | C2               | OSC1 and OSC2. See Figure 2.                                                                   |     | 29      |     | pF   | 8     |

|                               | L                |                                                                                                |     | 1.5     |     | μH   | 8     |

| Current drain                 | I <sub>DD</sub>  | For V <sub>DD</sub> 1, V <sub>DD</sub> 2, and V <sub>DD</sub> 3 when operating at 33.8688 MHz. |     | 60      | 95  | mA   | 9     |

### Electrical Characteristics 2 at Ta = $25^{\circ}$ C, all $V_{DD}$ = 5.0 V, all $V_{SS}$ = 0 V unless otherwise specified

| Parameter                 | Symbol  | Conditions     | Ratings |      |     | 1.1:4 | Notes |

|---------------------------|---------|----------------|---------|------|-----|-------|-------|

| Parameter                 | Symbol  | Conditions     | min     | typ  | max | Unit  | Notes |

| [A/D Converter Block]     |         |                |         |      |     |       |       |

| Total harmonic distortion | A-THD   | 1 kHz, at 0 dB |         | 0.05 |     | %     | 10    |

| Signal-to-noise ratio     | A-S/N   | 1 kHz, at 0 dB | 75      | 80   |     | dB    | 10,11 |

| Crosstalk                 | A-C · T | 1 kHz, at 0 dB |         | -75  |     | dB    | 10,11 |

| [D/A Converter Block]     |         |                |         |      |     |       |       |

| Total harmonic distortion | D-THD   | 1 kHz, at 0 dB |         | 0.01 |     | %     | 10    |

| Signal-to-noise ratio     | D-S/N   | 1 kHz, at 0 dB |         | 85   |     | dB    | 10,11 |

| Crosstalk                 | D-C · T | 1 kHz, at 0 dB |         | -80  |     | dB    | 10,11 |

Notes: 1. TTL output level pins: ASO, FS384O, BCKO, LRCKO, D0 to D7, A0 to A8,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{DREAD}$ ,  $\overline{DWRT}$

- 2. CMOS intermediate current output pins: P3, P4, SIAK

- 3. N-channel open drain intermediate current output pins: P0 to P2

- 4. Low Schmitt input pins: BCKI, ASI, LRCKI, D0 to D7, FS384I  $\,$

- 5. Normal input pins: P0 to P2, TEST1 to TEST5,  $\overline{\text{SELC}}$ , SAIF, SAOF

- 6. Schmitt input pins:  $\overline{RES}$ , SI, SICK,  $\overline{SIRQ}$ ,  $\overline{SRDY}$ , OSC1

- 7. When the load capacitance is 50 pF.

- 8. The values for the oscillator capacitors C1 and C2 include the line capacitances.

- 9. The typical values for the current drain are for  $V_{DD}$  = 5 V, room temperature, and typical samples.

- 10. Fs = 44.1 kHz and 20 kHz low-pass filter used. Measurement is with the external circuit structure and constants in the Sanyo evaluation board.

- 11. With the weight A filter used.

Figure 1 External Clock Input Waveform (FS384I)

**Figure 2 Crystal Oscillator Circuit**

**Figure 3 Oscillator Stabilization Time**

A07325

**Figure 4 Audio Data Input Conditions**

A07326

**Figure 5 Microcontroller Interface**

Figure 6 External DRAM Data Input Timing

A07327

A07328

Figure 7 Audio Data Output Timing

A07329

Figure 8 External DRAM Data Output Timing

### Differences between the LC83025E and the LC83026E

| Parameter                                                    | LC83025E                                                                                                                                                                                                                                                              | LC83026E                                                                                                                                |  |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                              | Decimation filter improved                                                                                                                                                                                                                                            |                                                                                                                                         |  |  |  |  |

|                                                              | Input compar                                                                                                                                                                                                                                                          | rator improved                                                                                                                          |  |  |  |  |

| A/D converter block                                          | *: The V <sub>REF</sub> pin was added in association with the improvements to the input comparator. The V <sub>REF</sub> pin external capacitor must be located as close as possible to the LC83026E, and must be connected with lines that are as short as possible. |                                                                                                                                         |  |  |  |  |

|                                                              | 4 × oversampling filters used                                                                                                                                                                                                                                         | 2 × oversampling filters used                                                                                                           |  |  |  |  |

| D/A converter block                                          | Second-order noise shaping                                                                                                                                                                                                                                            | Third-order noise shaping                                                                                                               |  |  |  |  |

|                                                              | Single-pin output used.                                                                                                                                                                                                                                               | Two-pin output operation                                                                                                                |  |  |  |  |

| Reset time                                                   | One or more sampling period                                                                                                                                                                                                                                           | Two or more sampling periods                                                                                                            |  |  |  |  |

| When no digital input is provided (when the SELC pin is low) | The LRCKI and BCKI pins must be connected to the LRCKO and BCKO pins.                                                                                                                                                                                                 | The LRCKI and BCKI pins must be connected to either $V_{DD}$ or $V_{SS}$ ; they do not need to be connected to the LRCKO and BCKO pins. |  |  |  |  |

# **Overall Signal Flow**

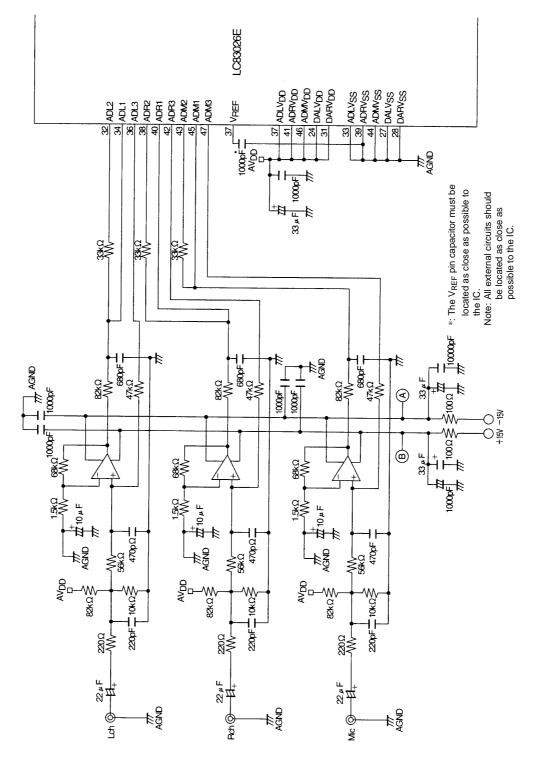

Figure 9 A/D Converter External Circuit Example

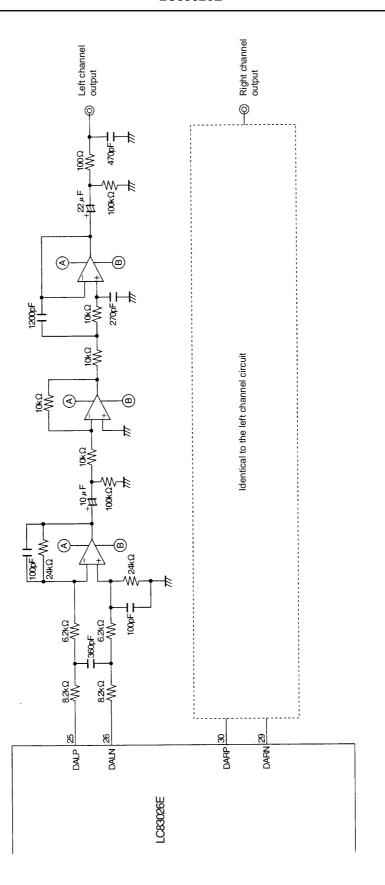

Figure 10 D/A Converter External Circuit Example

#### Application Circuit Example Outline (When digital input is not used)

Whether or not the digital inputs and/or analog outputs are used depends on the specifications of the application.

If any of these pins are not used, any unused input pins should be tied to high or low and any unused output pins should be left open.

### Application Circuit Example Outline (When digital input is used 1)

Whether or not the digital inputs and/or analog outputs are used depends on the specifications of the application.

If any of these pins are not used, any unused input pins should be tied to high or low and any unused output pins should be left open.

### Application Circuit Example Outline (When digital input is used 2)

Whether or not the digital inputs and/or analog outputs are used depends on the specifications of the application.

If any of these pins are not used, any unused input pins should be tied to high or low and any unused output pins should be left open.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1997. Specifications and information herein are subject to change without notice.