February 1995

\_F13006/LF13007 Digital Gain Set

National Semiconductor

# LF13006/LF13007 Digital Gain Set

## **General Description**

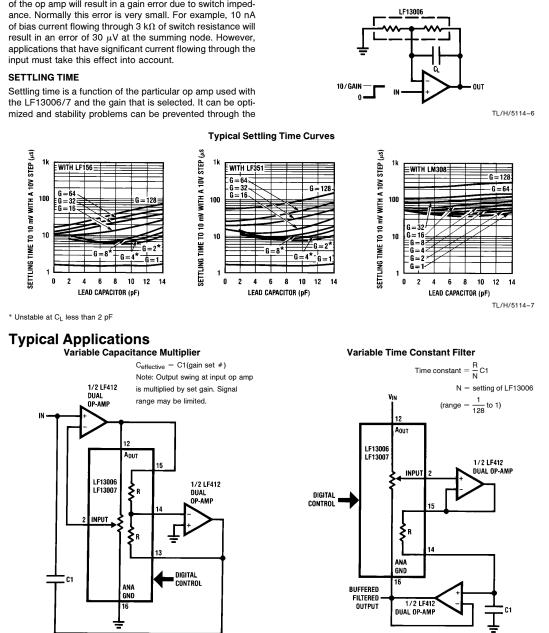

The LF13006 and LF13007 are precision digital gain sets used for accurately setting non-inverting op amp gains. Gains are set with a 3-bit digital word which can be latched in with  $\overline{WR}$  and  $\overline{CS}$  pins. All digital inputs are TTL and CMOS compatible.

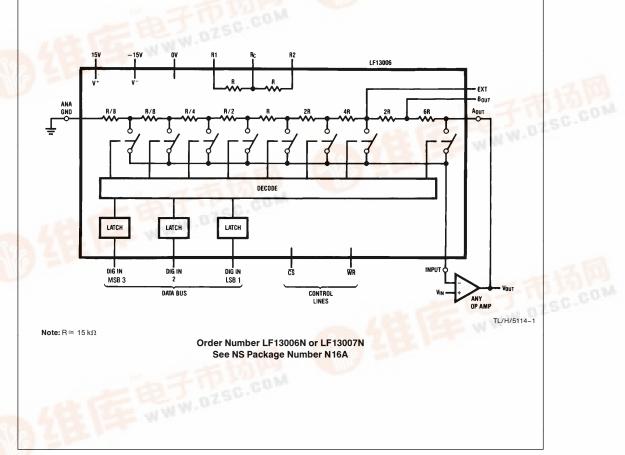

The LF13006 shown below will set binary scaled gains of 1, 2, 4, 8, 16, 32, 64, and 128. The LF13007 will set gains of 1, 2, 5, 10, 20, 50, and 100 (a common attenuator sequence). In addition, both versions have several taps and two uncommitted matching resistors that allow customization of the gain.

The gains are set with precision thin film resistors. The low temperature coefficient of the thin film resistors and their excellent tracking result in gain ratios which are virtually independent of temperature.

Block Diagram and Typical Application (LF13006)

The LF13006, LF13007 used in conjunction with an amplifier not only satisfies the need for a digitally programmable amplifier in microprocessor based systems, but is also useful for discrete applications, eliminating the need to find 0.5% resistors in the ratio of 100 to 1 which track each other over temperature.

### Features

- TTL and CMOS compatible logic levels

- Microprocessor compatible

- Gain error 0.5% max

- Binary or scope knob gains

- Wide supply range + 5V to ± 18V

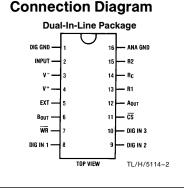

- Packaged in 16-pin DIP

©1995 National Semiconductor Corporation TL/H/5114

RRD-B30M115/Printed in U. S. A.

### Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage, V $^+$ to V $^-$ | 36V                    |

|----------------------------------|------------------------|

| Supply Voltage, V $^+$ to GND    | 25V                    |

| Voltage at Any Digital Input     | V <sup>+</sup> to GND  |

| Analog Voltage                   | $V^+$ to ( $V^-$ + 2V) |

**Operating Ratings** (Note 1)

**Operating Temperature Range** Lead Temp. (Soldering, 10 seconds)  $-40^{\circ}$ C to  $+85^{\circ}$ C 260°C

# **Electrical Characteristics (Note 2)**

| Parameter                                | Conditions                                                        | Typ<br>(Note 3) | Tested<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Units              |

|------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------------|-----------------------------|--------------------|

| Gain Error                               | $A_{OUT} = \pm 10V$<br>ANA GND = 0V<br>I <sub>INPUT</sub> < 10 nA | 0.3             | 0.5                         | 0.5                         | %(max)             |

| Gain Temperature Coefficient             | $A_{OUT} = \pm 10V$<br>ANA GND = 0V                               | 0.001           |                             |                             | %/°C               |

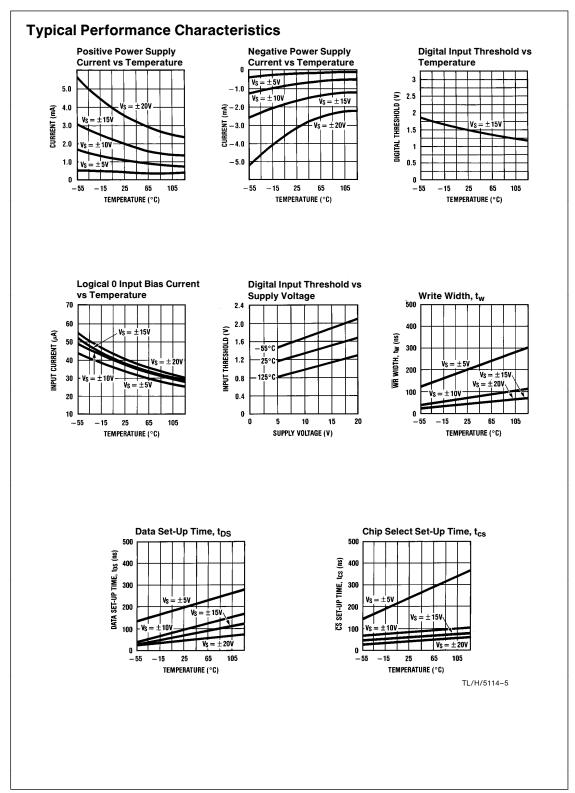

| Digital Input Voltage<br>Low<br>High     |                                                                   | 1.4<br>1.6      | 0.8<br>2.0                  | 0.8<br>2.0                  | V(max)<br>V(min)   |

| Digital Input Current<br>Low<br>High     | V <sub>IL</sub> =0V<br>V <sub>IH</sub> =5V                        | -38<br>0.0001   | -100<br>1                   | - 100<br>1                  | μΑ(max)<br>μΑ(max) |

| Positive Power Supply Current            | All Logic Inputs Low                                              | 2               | 5                           | 5                           | mA(max)            |

| Negative Power Supply Current            | All Logic Inputs Low                                              | - 1.7           | -5                          | -5                          | mA(max)            |

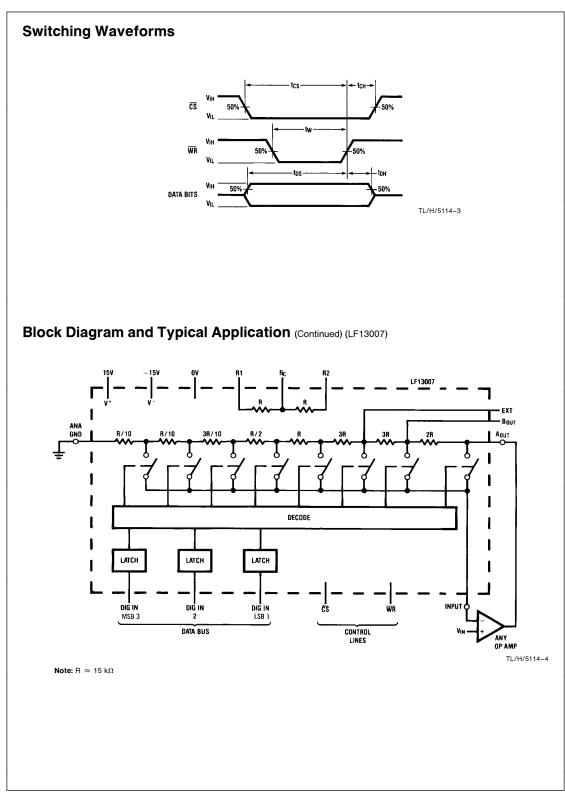

| Write Pulse Width, t <sub>W</sub>        | V <sub>IL</sub> =0V, V <sub>IH</sub> =5V                          |                 | 150                         |                             | ns(min)            |

| Chip Select Set-Up Time, t <sub>CS</sub> | $V_{IL}=0V, V_{IH}=5V$                                            |                 | 250                         |                             | ns(min)            |

| Chip Select Hold Time, t <sub>CH</sub>   | $V_{IL}=0V, V_{IH}=5V$                                            |                 | 0                           |                             | ns(min)            |

| DIG IN Set-Up Time, t <sub>DS</sub>      | V <sub>IL</sub> =0V, V <sub>IH</sub> =5V                          |                 | 150                         |                             | ns(min)            |

| DIG IN Hold Time, t <sub>DH</sub>        | V <sub>IL</sub> =0V, V <sub>IH</sub> =5V                          |                 | 60                          |                             | ns(min)            |

| Switching Time for Gain Change           | (Note 4)                                                          | 200             |                             |                             | ns(max)            |

| Switch On Resistance                     |                                                                   | 3               |                             |                             | kΩ                 |

| Unit Resistance, R                       |                                                                   | 15              | 12-18                       |                             | kΩ                 |

| R1 and R2 Mismatch                       |                                                                   | 0.3             | 0.5                         | 0.5                         | %(max)             |

| R1/R2 Temperature Coefficient            |                                                                   | 0.001           |                             |                             | %/°C               |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions. Note 2: Parameters are specified at V<sup>+</sup> = 15V and V<sup>-</sup> = -15V. Min V<sup>+</sup> to ground voltage is 5V. Min V<sup>+</sup> to V<sup>-</sup> voltage is 5V. Boldface numbers apply over full operating temperature ranges. All other numbers apply at  $T_A = T_j = 25^{\circ}C$ .

Note 3: Typicals are at 25°C and represent most likely parametric norm.

Note 4: Guaranteed and 100% production tested.

Note 5: Guaranteed (but not 100% production tested) over the operating temperature. These limits are not used to calculate outgoing quality levels.

Note 6: Settling time for gain change is the switching time for gain change plus settling time (see section on Settling Time).

Note 7: WR minimum high threshold voltage increases to 2.4V under the extreme conditions when all three digital inputs are simultaneously taken from 0V to 5V at a slew rate of greater than 500V/ $\mu$ S.

### GAIN TABLE

| Digital Input |          | Gain     |                  |         |                  |      |

|---------------|----------|----------|------------------|---------|------------------|------|

|               |          | LF13006  |                  | LF13007 |                  |      |

| DIG in 3      | DIG in 2 | DIG in 1 | A <sub>OUT</sub> | BOUT    | A <sub>OUT</sub> | BOUT |

| 0             | 0        | 0        | 1                | 1       | 1                | 1    |

| 0             | 0        | 1        | 2                | 1.25    | 1.25             | 1    |

| 0             | 1        | 0        | 4                | 2.5     | 2                | 1.6  |

| 0             | 1        | 1        | 8                | 5       | 5                | 4    |

| 1             | 0        | 0        | 16               | 10      | 10               | 8    |

| 1             | 0        | 1        | 32               | 20      | 20               | 16   |

| 1             | 1        | 0        | 64               | 40      | 50               | 40   |

| 1             | 1        | 1        | 128              | 80      | 100              | 80   |

### **Application Information**

### FLOW-THROUGH OPERATION

THE LF13006, LF13007 can be operated with control lines CS and WR grounded. In this mode new data on the digital inputs will immediately set the new gain value. Input data cannot be latched in this mode.

#### INPUT CURRENT

Current flowing through the input (pin 2) due to bias current of the op amp will result in a gain error due to switch imped-

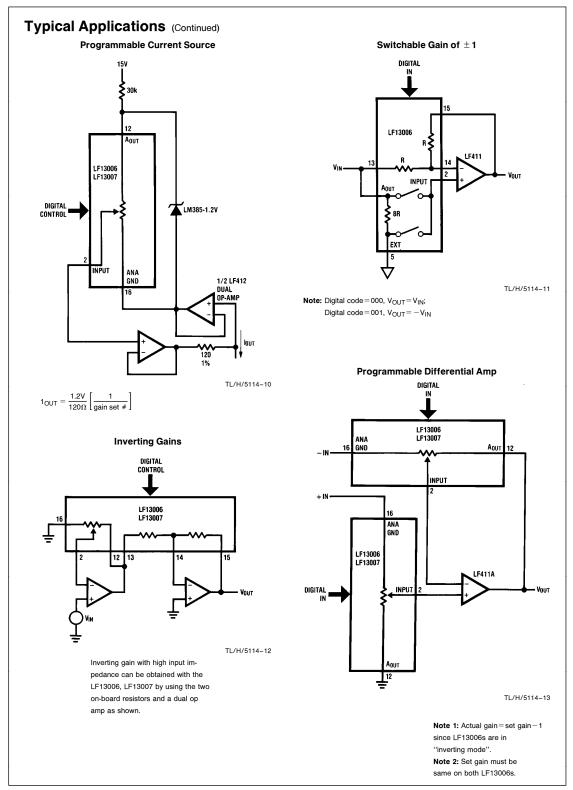

use of a lead capacitor from the inverting input to the output of the amplifier. A lead capacitor is effective whenever the feedback around an amplifier is resistive, whether with discrete resistors or with the LF13006/7. It compensates for the feedback pole created by the parallel resistance and capacitance from the inverting input of the op amp to AC around.

Settling Time Test Circuit

TL/H/5114-9

TL/H/5114-8

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.