**Integrated Circuits Group**

# LH52256CH-85LL

256K SRAM

(Model No.: LH525CL2)

Spec No.: EL095124

Issue Date: June 3, 1997

conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- · Office electronics

- · Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliances

- · Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail sale operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- · Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- · Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

```

OAccess Time

85 ns (Max.)

Operating current

40 mA (Max.)

10 mA (Max. trc. twc=1 \mus)

40 \mu A (Max.)

OStandby current

1.0 \mu A (Max. VCCDR = 3 V, Ta = 25°C)

OData retention current

4.5 V to 5.5 V

Owide operating voltage range

-40\% to +85\%

Operating temperature

OFully static operation

OThree-state output

ONot designed or rated as radiation hardened

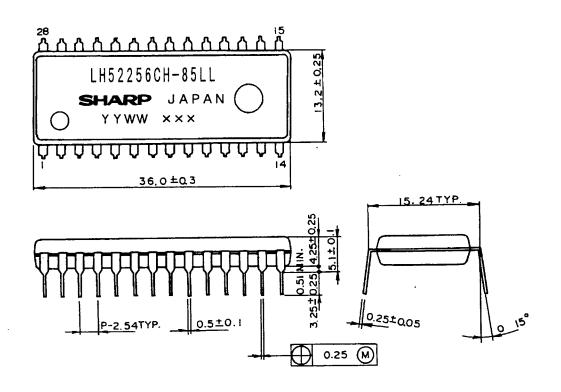

\bigcirc 2 8 pin DIP ( DIP 2 8 - P - 6 0 0 ) plastic package

ON-type bulk silicon

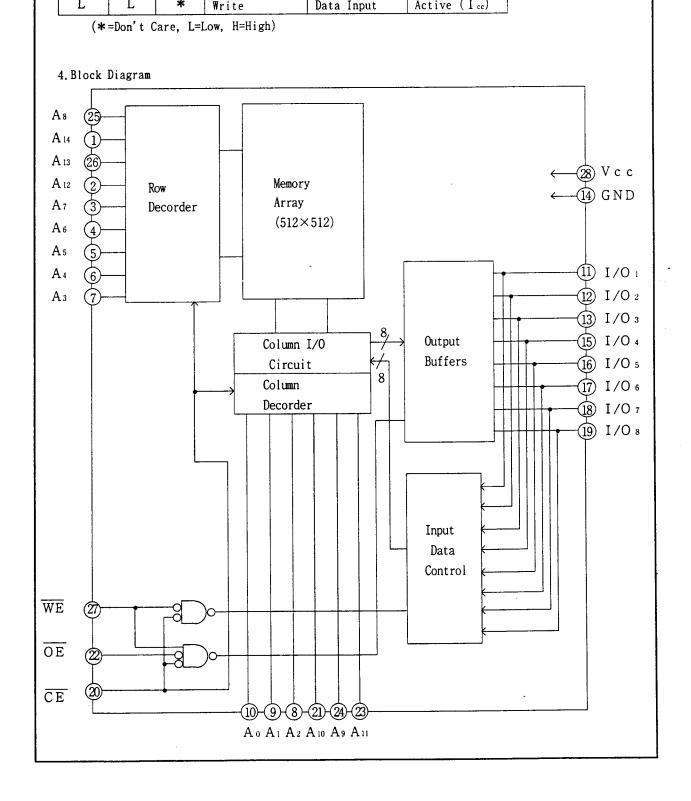

2. Pin Configuration

```

| A, 12          |        | ۷  | 21 |          | 44 17            |

|----------------|--------|----|----|----------|------------------|

| A 7            | $\Box$ | 3  | 26 |          | A 13             |

| A 6            | $\Box$ | 4  | 25 |          | A 8              |

| A 5            | $\Box$ | 5  | 24 |          | A 9              |

| A 4            | ㅁ      | 6  | 23 | Þ        | An               |

| <b>A</b> 3     | 디      | 7  | 22 |          | ΟE               |

| A <sub>2</sub> | $\Box$ | 8  | 21 |          | A 10             |

| Αı             |        | 9  | 20 |          | CE               |

| Αo             |        | 10 | 19 |          | I/O 8            |

| I/O 1          |        | 11 | 18 |          | I/O 7            |

| I/O 2          | $\Box$ | 12 | 17 |          | I/O 6            |

| I/O 3          | $\Box$ | 13 | 16 |          | I/O 5            |

| GND            | _      | 14 | 15 | $\vdash$ | T/O <sub>4</sub> |

(Top View)

| Pin Name    | Function            |

|-------------|---------------------|

| Ao to A14   | Address inputs      |

| CE          | Chip enable         |

| WE          | Write enable        |

| ŌE          | Output enable       |

| I/O1to I/O8 | Data inputs/outputs |

| Vcc         | Power supply        |

| GND         | Ground              |

|                     | 1       |       |         |     |

|---------------------|---------|-------|---------|-----|

| Chausan hammanahuna | 1 T     | _ 6 5 | to +150 | 1 % |

| Storage temperature | l 1 stg | - 65  | 10 7130 |     |

|                     |         |       |         |     |

Note) \*1. The maximum applicable voltage on any pin with respect to GND. \*2. Undershoot of -3.0V is allowed width of pluse bellow 50ns.

## 6. Recommended DC Operating Conditions

(Ta = -40 % to + 85 %)

| Parameter      | Symbol | Min.      | Typ. | Max.    | Unit |

|----------------|--------|-----------|------|---------|------|

| Supply voltage | Vcc    | 4.5       | 5.0  | 5.5     | V    |

| Input voltage  | VIH    | 2.2       |      | Vcc+0.5 | V    |

|                | VIL    | -0.5 (*3) |      | 0.8     | V    |

Note) \*3. Undershoot of -3.0V is allowed width of pluse below 50ns.

#### 7. DC Electrical Characteristics

$(T_2 = -4.0 \, \text{°C} \text{ to } + 8.5 \, \text{°C}, \text{Vcc} = 4.5 \, \text{V} \text{ to } 5.5 \, \text{V})$

| Parameter      | Symbol | Conditions                                                                 | Min. | Typ. (*4) | Max. | Unit |

|----------------|--------|----------------------------------------------------------------------------|------|-----------|------|------|

| Input leakage  | Ili    | V <sub>IN</sub> =OV to Vcc                                                 |      |           |      |      |

| current        |        |                                                                            | -1.0 |           | 1.0  | μΑ   |

| Output leakage | ILO    | CE =VIH OF OE =VIH                                                         |      |           |      |      |

| current        |        | V <sub>1/0</sub> =OV to V <sub>CC</sub>                                    | -1.0 |           | 1.0  | μА   |

| Operating      | Icc    | Minimum cycle                                                              |      |           |      |      |

| supply         |        | $V_{IN} = V_{IL}$ or $V_{IH}$ , $I_{I/0} = OmA$ , $\overline{CE} = V_{IL}$ |      | 2 5       | 4 0  | m A  |

| current        | Icci   | trc, two =1 $\mu$ s                                                        |      |           |      | ļ    |

|                |        | $V_{IN} = V_{IL}$ or $V_{IH}$ , $I_{I/0} = OmA$ , $\overline{CE} = V_{IL}$ |      |           | 1 0  | mA   |

| Standby        | IsB    | <u>CE</u> ≥V <sub>cc</sub> − 0. 2V                                         |      | 0.6       | 4 0  | μΑ   |

| current        | Isbi   | CE =VIH                                                                    |      |           | 3    | m A  |

| Output         | Vol    | Iot= 2.1mA                                                                 |      | . ,       | 0.4  | V    |

| voltage        | Vон    | I <sub>OH</sub> =-1. OmA                                                   | 2.4  |           |      | V    |

Note) \*4. Typical values at Vcc=5.0V, Ta=25 $^{\circ}$ C.

| input and output trains ker. Tever | 1.5 V                            |

|------------------------------------|----------------------------------|

| Output load                        | 1TTL+C <sub>L</sub> (100pF) (*5) |

Note) \*5. Including scope and jig capacitance.

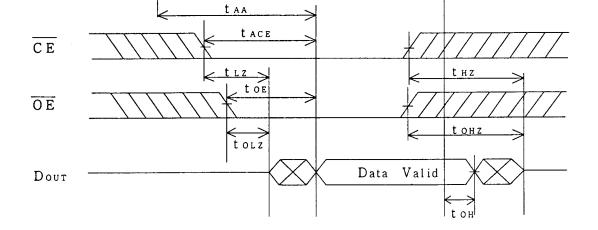

## Read cycle

| Parameter                           | Symbol | Min. | Max. | Unit |

|-------------------------------------|--------|------|------|------|

| Read cycle time                     | t RC   | 8 5  |      | ns   |

| Address access time                 | t a a  |      | 8 5  | ns   |

| CE access time                      | tace   |      | 8 5  | ns   |

| Output enable to output valid       | t o e  |      | 3 5  | ns   |

| Output hold from address change     | tон    | 1 0  |      | ns   |

| CE Low to output active             | tız    | 1 0  |      | ns   |

| OE Low to output active             | torz   | 5    |      | ns   |

| CE High to output in High impedance | tнz    | 0    | 3 0  | ns   |

| OE High to output in High impedance | tонz   | 0    | 3 0  | ns   |

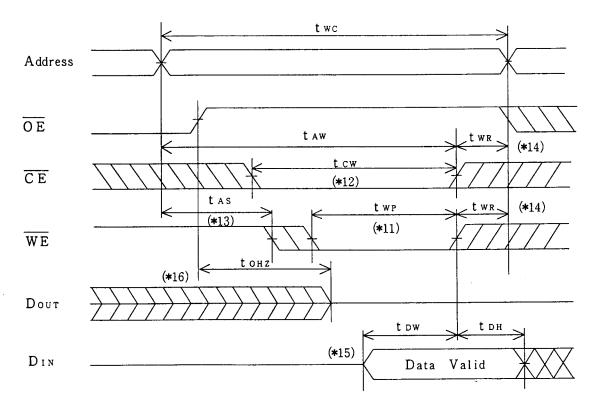

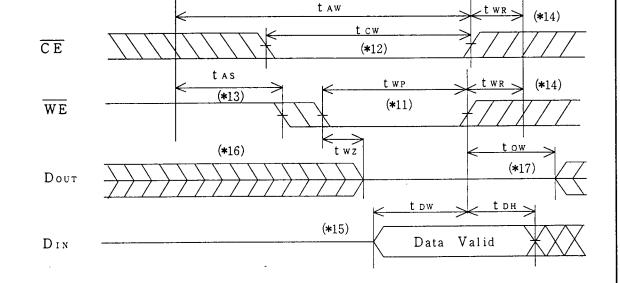

#### Write cycle

$(Ta = -4.0 \, \text{°C} \text{ to } + 8.5 \, \text{°C}, \text{Vcc} = 4.5 \, \text{V} \text{ to } 5.5 \, \text{V})$

6 6 6

| Parameter                           | Symbol | Min. | Max. | Unit |

|-------------------------------------|--------|------|------|------|

| Write cycle time                    | t wc   | 8 5  |      | ns   |

| CE Low to end of write              | t cw   | 5 5  |      | ns   |

| Address valid to end of write       | t aw   | 5 5  |      | ns   |

| Address setup time                  | tas    | 0    |      | ns   |

| Write pluse width                   | t wp   | 4 0  |      | ns   |

| Write recovery time                 | twr    | 0    |      | ns   |

| Input data setup time               | t ow   | 3 0  |      | ns   |

| Input data hold time                | t DH   | 0    |      | ns   |

| WE High to output active            | tow    | 5    |      | ns   |

| WE Low to output in High impedance  | t wz   | 0    | 3 0  | ns   |

| OE High to output in High impedance | tонz   | 0    | 3 0  | ns   |

Note) \*6. Active output to High impedance and High impedance to output active tests specified for a  $\pm 200 \text{mV}$  transition from steady state levels into the test load.

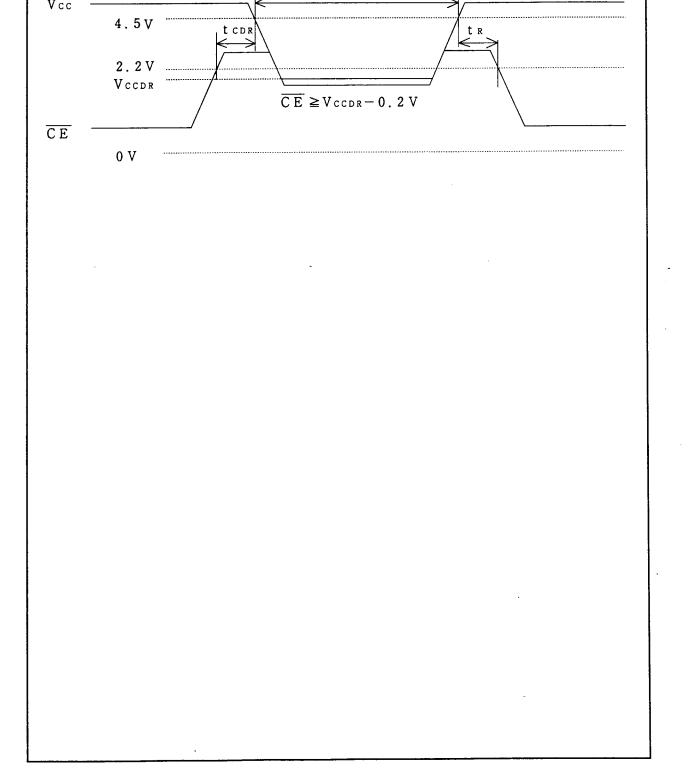

| Data Retention | LCCDR | Vccbr=3 V       | Ta = 25C       |      | 0.3 | 1.0 | μΑ  |

|----------------|-------|-----------------|----------------|------|-----|-----|-----|

| supply current |       |                 | T a = 70℃      |      |     | 1 5 | μΑ  |

|                |       | CE≥ Vccdr-0.2 V | <b>7 (*</b> 5) |      |     | 2 0 | μΑ  |

| Chip enable    | tcor  |                 |                |      |     |     |     |

| setup time     |       |                 |                | 0    |     |     | n s |

| Chip enable    | tr    |                 |                | (*8) |     |     |     |

| hold time      |       |                 |                | trc  |     |     | ns  |

Note) \* 7. Typical values at Ta=25 $^{\circ}$ C

\* 8. Read Cycle

## 10. Pin Capacitance

$(Ta=25 \, \text{C}, f=1 \, \text{MHz})$

| Parameter         | Symbol | Conditions      | Min. | Typ. | Max. | Unit |            |

|-------------------|--------|-----------------|------|------|------|------|------------|

| Input capacitance | CIN    | $V_{IN} = 0 V$  |      |      | 7    | рF   | <b>*</b> 9 |

| I/O capacitance   | C1/0   | $V_{I/O} = 0 V$ |      |      | 1 0  | рF   | <b>*</b> 9 |

Note) \*9. This parameter is sampled and not production tested.

Note) \*10.WE is high for Read cycle.

Write cycle timing chart - (OE Controlled)

- Note) \* 11. A write occurs during the overlap of a low  $\overline{\text{CE}}$ , and a low  $\overline{\text{WE}}$ ,

A write begins at the latest transition among  $\overline{\text{CE}}$  going low, and  $\overline{\text{WE}}$  going low.

A write ends at the earliest transition among  $\overline{\text{CE}}$  going high, and  $\overline{\text{WE}}$  going high.

two is measured from the beginning of write to the end of write.

- \* 12. tow is measured from the later of  $\overline{\text{CE}}$  going low to the end of write.

- \* 13. tas is measured from the address valid to the beginning of write.

- st 14. twn is measured from the end of write to the address change.

- \* 15. During this period, I/O pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- \* 16. If  $\overline{\text{CE}}$  goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain in high impedance state.

- \* 17. If  $\overline{\text{CE}}$  goes high simultaneously with  $\overline{\text{WE}}$  going high or before  $\overline{\text{WE}}$  going high, the outputs remain in high impedance state.

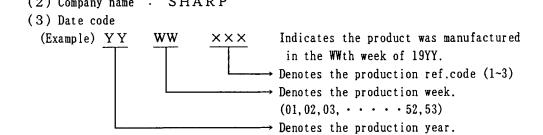

(Lower two digits of the year.)

(4) The marking of "JAPAN" indicates the country of origin.

#### 2-2. Marking layout

Refer to drawing No.AA852

(This layout does not define the dimensions of marking character and marking position.)

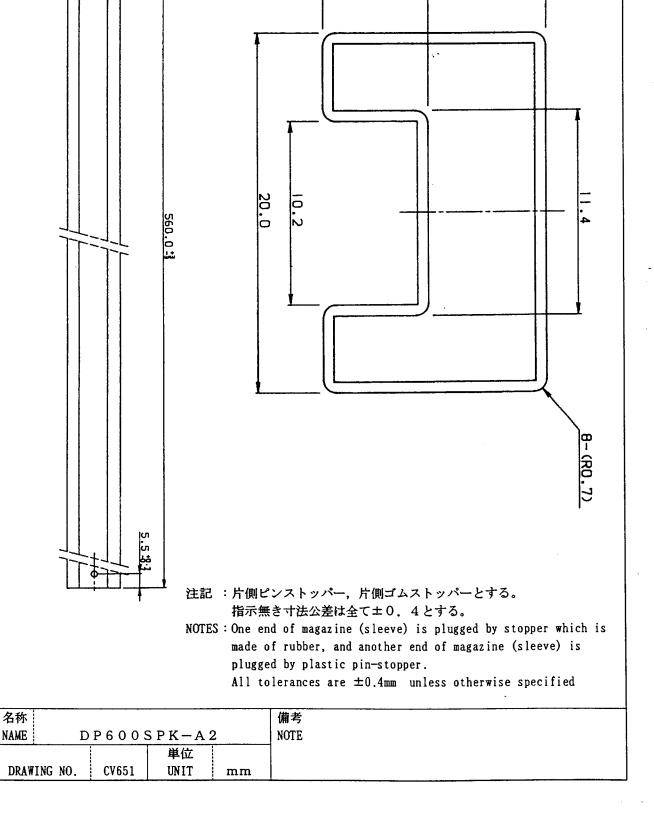

#### 3. Packing Specification

## 3-1. Packing materials

| Material Name | Material Specification                           | Purpose                                                       |

|---------------|--------------------------------------------------|---------------------------------------------------------------|

| Magaz ine     | Anti-static treated plastic (15devices/magazine) | Packing of device                                             |

| Stopper       | Plastic or rubber                                | Fixing of device                                              |

| Label         | Paper                                            | Indication of product name, quantity and date of manufacture. |

| Inner case    | Cardboard (600devices/cace)                      | Fixing of magazine                                            |

| Outer case    | Cardboard                                        | Outer packing of magazine                                     |

(Devices shall be inserted into a magazine (sleeve) in the same direction.)

#### 3-2. Outline dimension of magazine (sleeve)

Refer to attached drawing

## 4. Precaution For Unpacking

- Unpacking should be done on the stand as well as human body treated with anti-ESD.

- (2) Anti-ESD treatment is given to a magazine. Use the equivalent magazine, if it is changed to another one.

- (3) Be sure to fix two stoppers to both ends of a magazine when storage to prevent the devices from slipping.

| Solder gibbing       | 240 C of 1035, direction of 1005 than 5 becomes, alp, |               |

|----------------------|-------------------------------------------------------|---------------|

|                      | total of 5 seconds.                                   |               |

|                      | (Only the appropriate parts of leads for soldering    |               |

|                      | are immersed in the surface of a jet stream solder    |               |

|                      | bath. During soldering, the solder stream must not    |               |

|                      | come into direct contact with the plastic body of     |               |

|                      | package.)                                             |               |

| Manual soldering     | 260℃ or less, duration of less than 10 seconds.       | IC outer      |

| (soldering iron)     | (Only the appropriate parts of leads for soldering    | lead surface. |

| (Leal Land and Land, | are soldered with a soldering iron. During soldering, |               |

|                      | the soldering iron must not come into direct          |               |

|                      | contact with the plastic body of package.)            |               |

-

| 名称 |              |        | リード仕上      | TIN-LEAD | 備考   | プラスチックパッケージ外形寸法は、バリを含まないものとする。              |  |

|----|--------------|--------|------------|----------|------|---------------------------------------------|--|

|    | NAME DIP28-P | -600 L | EAD FINISH | PLATING  | NOTE | Plastic body dimensions do not include burr |  |

|    |              | :      | 単位         |          |      | of resin.                                   |  |

|    | DRAWING NO.  | AA852  | UNIT       | mm       |      |                                             |  |

Static SRAM RAM Random Access Memory LH52256CH-85LL 256K (32Kx8) (85 ns) (DIP)