SANYO

No. 3888

NMOS LSI

# LM7007M, LM7007HM

# **Dual-PLL Frequency Synthesizers**

#### **OVERVIEW**

The LM7007M and LM7007HM are dual-PLL frequency synthesizer ICs for use in 250 to 380 MHz cordless telephone transceivers.

The LM7007M and LM7007HM comprise two PLL circuits, 16-bit transmit and receive programmable dividers, a temperature-compensated crystal oscillator (TCXO) amplifier and two transistors for external low-pass filters (LPF). Each PLL comprises a dual charge pump and fast-lockup circuit. The standard TCXO frequencies are 10.625, 12.8 and 21.25 MHz. Serial data transfer is controlled from a three-wire, serial, computer control bus (C<sup>2</sup>B).

The LM7007H and LM7007HM operate from a 2.8 to 4.5 V supply and are available in 24-pin MFPs.

#### **FEATURES**

- Dual charge pump and fast-lockup circuit in each PLL for rapid locking

- 10.625, 12.8 and 21.25 MHz TCXO frequencies

- TCXO input amplifier

- Dual LPF transistors

- C<sup>2</sup>B serial interface

- 2.8 to 4.5 V supply

- 24-pin MFP

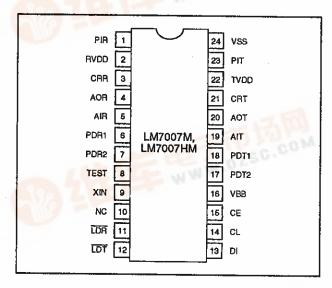

#### **PINOUT**

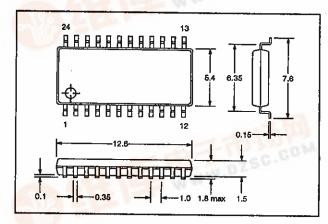

#### PACKAGE DIMENSIONS

Unit: mm

#### 3112-MFP24S

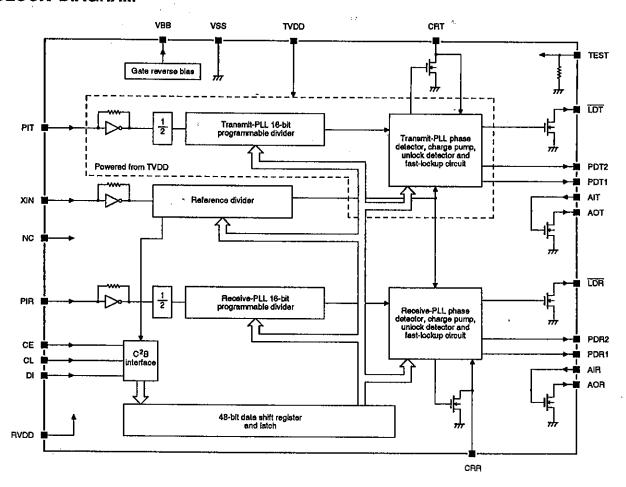

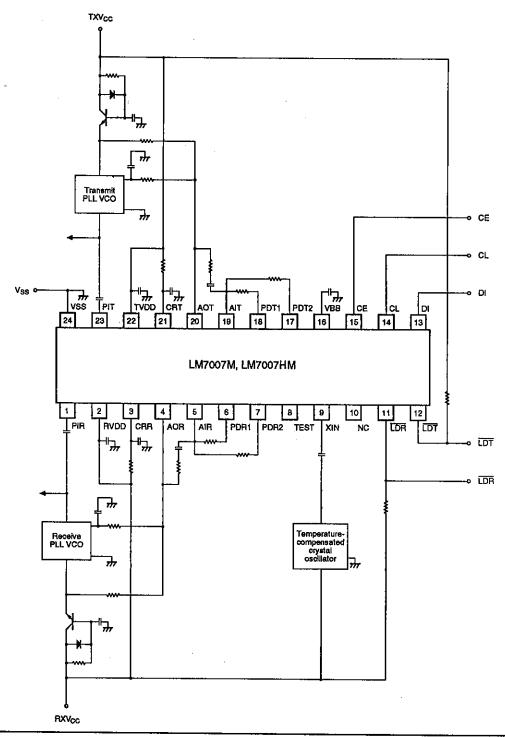

# **BLOCK DIAGRAM**

## PIN DESCRIPTION

| Number | Name | Description                                                        |  |  |  |

|--------|------|--------------------------------------------------------------------|--|--|--|

| 1      | PIR  | Receive-PLL local-oscillator input                                 |  |  |  |

| 2      | RVDD | Receive-PLL 2.8 to 4.5 V supply                                    |  |  |  |

| 3      | CRR  | Receive-PLi. fast-lockup circuit resistor and capacitor connection |  |  |  |

| 4      | AOR  | Receive-PLL LPF, n-channel MOS transistor output                   |  |  |  |

| 5      | AIR  | Receive-PLL LPF, n-channel MOS transistor input                    |  |  |  |

| 6      | PDR1 | Receive-PLL phase detector main tristate output                    |  |  |  |

| 7      | PDR2 | Receive-PLL phase detector secondary tristate output               |  |  |  |

| 8      | TEST | Test input                                                         |  |  |  |

| 9      | XIN  | Reference oscillator input                                         |  |  |  |

| 10     | NC   | No connection                                                      |  |  |  |

| 11     | LDR  | Receive-PLL unlock detector n-channel, open-drain output           |  |  |  |

| 12     | LDT  | Transmit-PLL unlock detector n-channel, open-drain output          |  |  |  |

| 13     | DI   | Serial data input                                                  |  |  |  |

| 14     | CL   | Clock input                                                        |  |  |  |

| 15     | CE   | Chip enable input                                                  |  |  |  |

| 16     | VBB  | Gate reverse-bias capacitor connection                             |  |  |  |

## LM7007M, LM7007HM

| Number          | Name  | Description                                                        |

|-----------------|-------|--------------------------------------------------------------------|

| 17              | PDT2  | Transmit-PLL phase detector secondary tristate output              |

| 18              | PDT1  | Transmit-PLL phase detector main tristate output                   |

| 19              | AIT   | Transmit-PLL LPF, n-channel MOS transistor input                   |

| <sup>-</sup> 20 | AOT   | Transmit-PLL LPF, n-channel MOS transistor output                  |

| 21              | CRT , | Transmit-PLL fast-lockup circuit resistor and capacitor connection |

| 22              | TVDD  | Transmit-PLL 2.8 to 4.5 V supply                                   |

| 23              | PIT   | Transmit-PLL local-oscillator input                                |

| 24              | VSS   | Ground                                                             |

## **SPECIFICATIONS**

## **Absolute Maximum Ratings**

| Parameter                                                                    | Symbol           | Rating      | Unit |

|------------------------------------------------------------------------------|------------------|-------------|------|

| Receive-PLL supply voltage range                                             | RV <sub>DD</sub> | 0.3 to 5.5  | ٧    |

| Transmit-PLL supply voltage range                                            | TV <sub>DD</sub> | -0.3 to 5,5 | ٧    |

| Gate reverse-bias voltage range                                              | V <sub>BB</sub>  | -4 to −1    | >    |

| XIN, TEST, PIR, PIT, AIR, AIT, CE, CL, DI, CRR and CRT input voltage range   | Vi               | -0.3 to 6.0 | ٧    |

| AOR, AOT, LDR, LDT, PDR1, PDR2, PDT1, PDT2, CRR and CRT output voltage range | Vo               | -0.3 to 6.0 | ٧    |

| AOR, AOT, LDR and LDT output current range                                   | lo               | 0 to 2      | mA   |

| Power dissipation                                                            | P <sub>D</sub>   | 350         | mW   |

| Operating temperature range                                                  | Topr             | -20 to 75   | °C   |

| Storage temperature range                                                    | T <sub>stp</sub> | 55 to 125   | °C   |

## **Recommended Operating Conditions**

$T_n = 25 \, ^{\circ}C$

| Parameter                         | Symbol           | Rating     | Unit |

|-----------------------------------|------------------|------------|------|

| Receive-PLL supply voltage range  | RV <sub>DD</sub> | 2.8 to 4.5 | ٧    |

| Transmit-PLL supply voltage range | TV <sub>DD</sub> | 2.8 to 4.5 | v    |

## **Electrical Characteristics**

$V_{DD}$  =  $RV_{DD}$  =  $TV_{DD}$  = 2.8 to 4.5 V,  $V_{SS}$  = 0 V,  $T_a$  = 25 °C unless otherwise noted

| Parameter                                          | Cumbal           | Condition             | Rating         |     |     | 1114 |

|----------------------------------------------------|------------------|-----------------------|----------------|-----|-----|------|

| T di diriotori                                     | Symbol           | Condition             | min            | typ | max | Unit |

| PVDD cumply oursel                                 | ,                | LM7007M. See note 1.  | _              | 17  | 22  | 1    |

| RVDD supply current                                | 1001             | LM7007HM. See note 1. |                | 20  | 25  | mA   |

| DVDD TVDD                                          |                  | LM7007M. See note 2.  | · <del>-</del> | 30  | 39  |      |

| RVDD + TVDD supply current                         | I <sub>DD2</sub> | LM7007MH. See note 2. | -              | 37  | 45  | mA   |

| CE, CL, DI, CRR and CRT<br>LOW-level input voltage | V <sub>IL</sub>  |                       | 0              | _   | 0.4 | ٧    |

# LM7007M, LM7007HM

| Parameter                                           | Symbol            | Condition                                                               |                    | Rating |      | 1 lmla                                |

|-----------------------------------------------------|-------------------|-------------------------------------------------------------------------|--------------------|--------|------|---------------------------------------|

|                                                     |                   | - Conduion &                                                            | mln                | typ    | max  | Unit                                  |

| CE, CL, DI, CRR and CRT<br>HIGH-level input voltage | V <sub>IH</sub>   |                                                                         | 2.0                | -      | 5.5  | v                                     |

| XIN rms input voltage                               | Vit               | Sinewave, capacitive coupling, 1, = 5 to 23 MHz                         | 50                 | -      | 1000 | mV                                    |

|                                                     |                   | Sinewave, capacitive coupling, f <sub>1</sub> = 200 to 400 MHz          | 70                 | _      | 500  |                                       |

| PIR and PIT rms input voltage                       | V <sub>12</sub>   | Sinewave, capacitive coupling, VDD = 2.8 to 3.3 V, It = 200 to 520 MHz  | 100                | -      | 500  | mV                                    |

| PDR1 and PDT1 LOW-level output voltage              | V <sub>OL1</sub>  | l <sub>O</sub> = 0.1 mA                                                 | -                  | -      | 0.3  | ٧                                     |

| PDR2 and PDT2 LOW-level output voltage              | Vol2              | lo = 5 mA                                                               | -                  | ~      | 1.5  | ٧                                     |

| LDR and LDT LOW-level output voltage                | Vola              | lo = 1 mA                                                               | -                  | _      | 1    | ν                                     |

| CRR and CRT LOW-level output voltage                | V <sub>OL4</sub>  | lo = 2 mA, V <sub>DD</sub> = 3 V                                        | 0.7                | 1.0    | 1.4  | ٧                                     |

| AOR and AOT LOW-level output                        | Vols              | I <sub>O</sub> = 0.5 mA,<br>V <sub>AIR</sub> = V <sub>AIY</sub> = 1.2 V | -                  | -      | 0.5  | v                                     |

| voltage                                             |                   | $l_0 = 1$ mA,<br>$V_{AIR} = V_{AIT} = 1.3$ V                            | -                  | _      | 0.5  |                                       |

| PDR1 and PDT1 HIGH-level output voltage             | Vohi              | lo = 0.1 mA                                                             | 0.6V <sub>DD</sub> | -      | -    | ٧                                     |

| PDR2 and PDT2 HIGH-level output                     | V <sub>OH2</sub>  | lo = 0.1 mA                                                             | 0.6V <sub>DD</sub> | -      | -    | · · · · · · · · · · · · · · · · · · · |

| voltage                                             | VOH2              | lo = 5 mA                                                               | 0.1V <sub>DD</sub> | -      | _    | ٧                                     |

| AOR, AOT, LDR, LDT, CRR and CRT oulput voltage      | Vo                |                                                                         | 0                  | -      | 5.5  | ٧                                     |

| CE, CL, DI, CRR and CRT<br>LOW-level input current  | liLi              | V <sub>i</sub> = 0 V                                                    | -                  |        | 5    | μА                                    |

| XIN LOW-level input current                         | l <sub>IL2</sub>  | V <sub>1</sub> = 0 V                                                    | 1                  | _      | 6    | μΑ                                    |

| PIR and PIT LOW-level input current                 | lita              | V <sub>i</sub> = 0 V                                                    | 2                  | ~      | 12   | μА                                    |

| AIR and AIT LOW-level Input current                 | lila              | V <sub>I</sub> = 0 V                                                    | -                  | 0.01   | 10.0 | лА                                    |

| TEST LOW-level input current                        | l <sub>ILS</sub>  | V <sub>I</sub> = 0 V                                                    | _                  | -      | 5    | μА                                    |

| CE, CL, DI, CRR and CRT<br>HIGH-level input current | lını              | V <sub>I</sub> = 4.5 V                                                  | -                  | _      | 5    | μА                                    |

| XIN HIGH-level input current                        | l <sub>IH2</sub>  | V <sub>1</sub> = 4.5 V                                                  | 1                  | -      | 6    | μΑ                                    |

| PIR and PIT HIGH-level input current                | fіна              | V <sub>I</sub> = 4.5 V                                                  | 2                  | -      | 12   | μА                                    |

| AIR and AIT HIGH-level input current                | 11114             | V <sub>I</sub> = 4.5 V                                                  |                    | 0.01   | 10.0 | nA                                    |

| TEST HIGH-level input current                       | lıns              | V <sub>I</sub> = 4.5 V                                                  |                    | 225    | _    | μΑ                                    |

| LDR, LDT, CRR and CRT output<br>leakage current     | loff1             | V <sub>O</sub> = 4.5 V                                                  | -                  | -      | 5    | μΑ                                    |

| AOR and AOT output leakage current                  | I <sub>OFF2</sub> | Vo = 4.5 V                                                              | _                  | _      | 10   | μΑ                                    |

| PDR1, PDT1, PDR2 and PDT2 output leakage current    | loff3             | V <sub>O</sub> = 0.4 V or 4.5 V                                         | _                  | 0.01   | 10.0 | nA                                    |

### LM7007M, LM7007HM

| Parameter                          | Symbol          | . Condition                                                                            | Rating |      |       |      |

|------------------------------------|-----------------|----------------------------------------------------------------------------------------|--------|------|-------|------|

| T dramotos                         | Symbol          | a. Condition                                                                           | min    | typ  | max   | Unit |

| XIN input frequency                | f <sub>l1</sub> | Sinewaye, capacitive coupling, V <sub>I</sub> = 60 mV                                  | 6      | -    | 23    | MHz  |

|                                    |                 | Sinewave, capacitive coupling, V <sub>I</sub> = 70 mV                                  | 200    | -    | 400   | MHz  |

| PIR and PIT input frequency        | f <sub>12</sub> | Sinewave, capacitive coupling, V <sub>DD</sub> = 2.8 to 3.2 V, V <sub>I</sub> = 100 mV | 200    | _    | . 520 |      |

| XIN feedback resistance            | R <sub>ff</sub> | V <sub>DD</sub> = 4.5 V                                                                | 750    | 1000 | 4500  | kΩ   |

| PIR and PIT feedback resistance    | R₂              | V <sub>DD</sub> = 4.5 V                                                                | 375    | 500  | 2250  | kΩ   |

| TEST pull-down resistance          | R₀              |                                                                                        | -      | 20   | -     | kΩ   |

| XIN, PIR and PIT input capacitance | Cı              |                                                                                        | _      | 2.5  | -     | pF   |

#### Notes

- 1.  $f_{\text{XIN}} = 12.8 \text{ MHz}$ ,  $V_{\text{PIR}} = 70 \text{ mV}$  at 400 MHz, all other inputs = 0 V, all outputs open

- 2.  $f_{XIN} = 12.8$  MHz,  $V_{PIR} = V_{PIT} = 70$  mV at 400 MHz, all other inputs = 0 V, all outputs open

## **FUNCTIONAL DESCRIPTION**

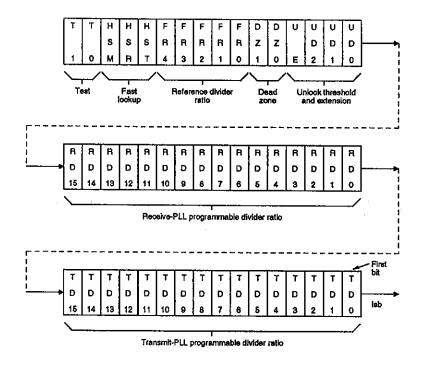

#### C<sup>2</sup>B Data Format

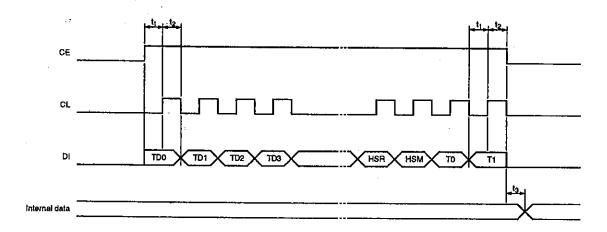

The C<sup>2</sup>B input data format is shown in figure 1, and the input timing, in figure 2. The input data comprises 48 bits input serially on DI. TD0 is the first bit received.

Figure 1. C2B data format

Figure 2. Serial data timing

The timing diagram parameters  $t_i$  ( $t_1$ ,  $t_2$  and  $t_3$ ) should all be greater than 32/ $f_{XIN}$ , where  $f_{XIN}$  is the XIN TCXO frequency. For TCXO frequencies of 10.625, 12.8 and 21.25 MHz,  $t_i$  should be greater than 3.02, 2.5 and 1.52  $\mu$ s, respectively.

The outputs are undefined until the frequency synthesizer is programmed. The serial data should be input only after RVDD and  $f_{\text{XIN}}$  have become stable. Note that CE, CL and DI HIGH-level and LOW-level voltages are independent of RVDD.

#### Reference Divider

Data bits FR0 to FR4 set the reference frequency divider ratio. The standard temperature-compensated crystal oscillator (TXCO) input frequencies,  $f_{XIN}$ , are 12.8, 10.625 and 21.25 MHz.

The reference divider ratios for  $f_{\rm ref}=6.25$  kHz with 12.5 kHz channel spacing for  $f_{\rm XIN}$  are shown in table 1. Table 1. Reference divider ratios

| f <sub>XIN</sub> (MHz) | FR4 | FR3 | FR2 | FR1 | FR0 | Divider ratio |

|------------------------|-----|-----|-----|-----|-----|---------------|

| 12.8                   | 0   | 0   | 0   | 0   | 0   | 2048          |

| 10.625                 | 1   | 1   | 1   | 1   | 1   | 1700          |

| 21.25                  | 0   | 0   | 1   | 1   | 1   | 3400          |

## Unlock-detector Threshold

Data bits UD0 to UD2 determine the unlock-detector threshold. The PLL unlock-detector output,  $\overline{LDT}$  ( $\overline{LDR}$ ), is pulled LOW when the phase error between the refer-

Table 3. Unlock-detector thresholds

ence and the divided input,  $\phi_E$ , exceeds the threshold. The threshold values for the standard frequencies are shown in table 3.

**Transmit- and Receive-PLL Programmable Dividers**

Data bits TD0 to TD15 and RD0 to RD15 set the transmit- and receive-PLL programmable divider ratios, respectively. Bits TD0 and RD0 are the least significant bits

The allowable divider ratios are in the range 256 to 65535. The PLL frequency divisions are two times the division setting of  $f_{OSC}/12.5$  kHz.

#### **Phase Detector**

The phase detector output states of PDT1 (PDR1) are shown in table 2. When the PLL unlocks,  $\overline{LDT}$  ( $\overline{LDR}$ ) is pulled down and PDT2 (PDR2) has the same output state as PDT1 (PDR1).

Table 2. Phase detector output states

| Cond                                               | Condition   |                |  |

|----------------------------------------------------|-------------|----------------|--|

| f <sub>IM</sub> /N <sub>T</sub> > f <sub>ref</sub> | Leading     | HIGH           |  |

| f <sub>IN</sub> /N <sub>T</sub> < f <sub>ref</sub> | Lagging     | LOW            |  |

| $f_{\rm BN}/N_{\rm T} = f_{\rm ref}$               | Coincidence | High impedance |  |

| UD2 UD1 | UD1 UD0 | Phase-error threshold (µs) |                             |                               |                              |

|---------|---------|----------------------------|-----------------------------|-------------------------------|------------------------------|

|         |         | 550                        | f <sub>XIN</sub> = 12.8 MHz | f <sub>XIN</sub> = 10.625 MHz | 1 <sub>XIN</sub> = 21.25 MHz |

| 0       | 0       | 0                          | 0                           | . 0                           | 0                            |

| 0       | 0       | 1                          | 0.15                        | 0.19                          | 0.09                         |

| 0       | 1       | 0                          | 0.3                         | iliegal                       | 0,19                         |

Table 3. Unlock-detector thresholds-continued

| UD2 | UD1 | UDO  |                             | Phase-error threshold (µs)    |                              |

|-----|-----|------|-----------------------------|-------------------------------|------------------------------|

|     | וטט |      | f <sub>XIN</sub> = 12.8 MHz | f <sub>XIN</sub> = 10.625 MHz | f <sub>XIN</sub> = 21.25 MHz |

| 0   | . 1 | 1    | lllegal                     | lliegal                       | lllegal                      |

| 1   | 0   | 0    | 1.25                        | 0.94 ±0.19                    | 0.94 ±0.19                   |

| 1   | 0 - | 1. , | 1.25                        | 0.94 ±0.19                    | 0.94 ±0.19                   |

| 1   | 1   | 0    | б                           | 4.70 ±0.94                    | 4.70 ±0.94                   |

| 1   | 1   | 1    | 5                           | 4.70 ±0.94                    | 4.70 ±0.94                   |

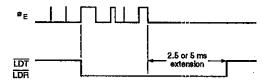

#### Unlock Extension

Data bit UE selects the unlock extension period. The period is extended by 2.5 ms, when UE = 0, and by 5 ms, when UE = 1, as shown in figure 3. The unlock extension is ignored when UD0 = UD1 = UD2 = 0.

Figure 3. Unlock extension

#### **Dead-zone Mode**

Data bits DZ0 and DZ1 select the phase-insensitive bandwidth, or dead zone, of the PLL phase comparator as shown in table 4. Modes DZB, DZC and DZD have successively larger dead zones.

Table 4. Dead-zone modes

| DZ1 | DZ0 | Dead-zone mode |

|-----|-----|----------------|

| 0   | 0   | lllegal        |

| 0   | 1   | DZB            |

| 1   | 0   | OZC            |

| 1   | 1   | DZD            |

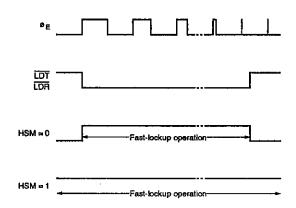

#### Fast-lockup Control

Data bits HST and HSR select fast-lockup mode for the transmit and receive PLLs, respectively. Fast-lockup mode is selected when each data bit is 1, and deselected, when 0.

Data bit HSM selects the fast-lockup operating mode as shown in figure 4. Fast-lockup operates continuously,

when HSM = 1, and during unlock only, when HSM = 0.

Figure 4. Fast-lockup operating modes

When fast lockup is not selected, CRT and CRR should be either open or tied to ground.

#### **Power Supply**

TVDD supplies the transmit-PLL programmable divider, phase detector, unlock detector and fast-lockup circuits. RVDD supplies the C<sup>2</sup>B interface, reference divider and receive-PLL circuits.

#### **LPF** Transistors

Open-drain transistors are provided for the transmit- and receive-PLL loop filters.

#### Test Mode (T0, T1)

Data bits T0 and T1 are normally not used and should be set to 0. Also, TEST should be open or tied to ground.

#### **DESIGN INFORMATION**

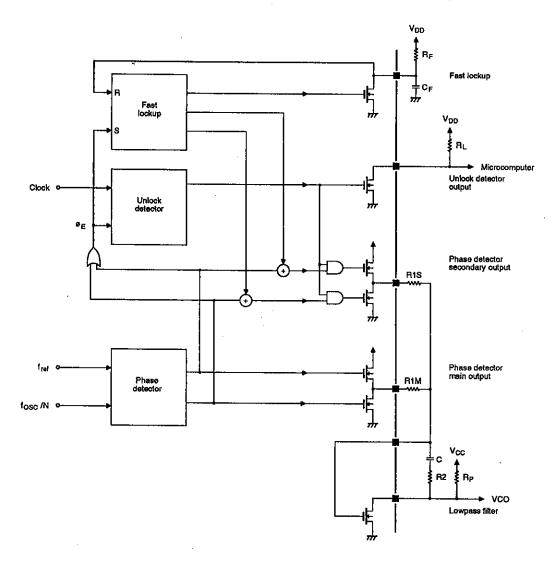

# Dual Charge Pump and Fast-lockup Circuit

The dual charge pump and fast-lockup circuit is shown in figure 5. The phase detector secondary output goes active after a channel change causes the PLL to unlock. R1 becomes R1MlR1S, reducing the LPF time constant and decreasing the PLL lock time.

When the PLL locks, the phase detector secondary output becomes high impedance and R1 becomes R1M, thereby increasing the LPF time constant and improving sideband and FM response.

Figure 5. Dual charge pump and fast-lockup circuit

## Phase-error Threshold

The phase-error threshold should be small during channel change to ensure precise phase-error checking and phase-detector secondary output operation. Unlocking caused by phase error is unlikely during FM operation. The phase-error threshold should be large after the PLL locks.

## Gate Reverse Bias

A 0.01  $\mu F$  capacitor should be connected between VBB and ground for the gate reverse bias.

## TYPICAL APPLICATION

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- 2 Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.