### 查询LM9800供应商

💦 National Semiconductor

# LM9800 8-Bit Greyscale/24-Bit Color Linear CCD Sensor Processor

### **General Description**

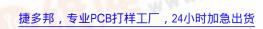

The LM9800 is a high performance integrated signal processor/digitizer for linear CCD image scanners. The LM9800 performs all the analog processing (correlated double sampling for black level and offset compensation, pixel-by-pixel gain adjust, and 8-bit analog-to-digital conversion) necessary to maximize the performance of a wide range of linear CCD sensors.

The LM9800 can be digitally programmed to work with a wide variety of CCDs from different manufacturers. An internal configuration register sets CCD and sampling timing to maximize performance, simplifying the design and manufacturing processes.

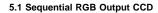

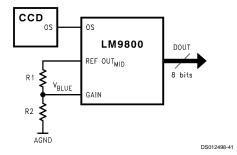

The LM9800 can be used with sequential or parallel output color CCDs. Coarse gain switching brings weak Blue signals up to Red/Green levels for best performance. For complementary voltage reference see the LM4041.

### Applications

- Color and Greyscale Flatbed and Sheetfed Scanners

- General Purpose CCD Imaging

### **Features**

- 2.5 million pixels/s conversion rate

- Implements Correlated Double Sampling for minimum noise and offset error

.M9800 8-Bit Greyscale/24-Bit Color Linear

CCD

Sensor Processor

8 Bits

2.5MHz

+5V ±5%

September 1997

- Pixel-to-pixel gain correction for individual pixels maximizes dynamic range and resolution, even on "weak" pixels

- Reference and signal sampling points digitally controlled in 25ns increments for maximum performance

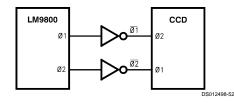

- Generates all necessary CCD clock signals

- Compatible with a wide range of linear CCDs

- TTL/CMOS input/output compatible

### **Key Specifications**

- Resolution

- Pixel Conversion Rate

- Supply Voltage

- Supply Voltage (Digital I/O) +3.3V ±10% or +5V ±5%

- Power Dissipation

210 mW (typ)

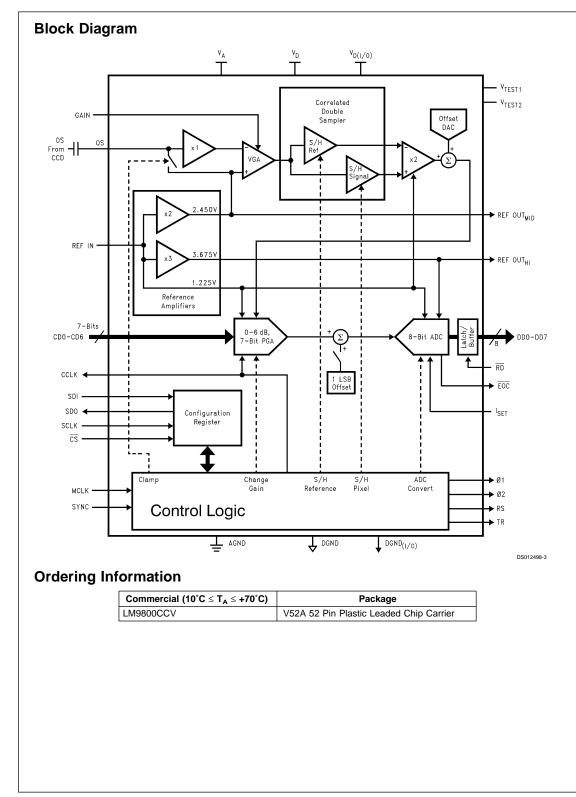

- **Connection Diagram** DGND NC CD6 CD5 CD4 CD3 CD3 CD2 CD1 \_0 CDO V<sub>TEST1</sub> CCLK TEST2 NC MCL K DD7 GAIN DD6 ٧٨ 12 ΔGND - DD5 LM9800CCV DD4 05 40 (PLCC) DD3 NC 15 39 NC 38 - DD2 16 - DD1 REF OUT<sub>MID</sub> 37 - DDO REF OUT<sub>HI</sub> 36 REF IN . 19 35 - NC 20 • NC REF IN 3. 23 24 25 26 27 28 29 30 3 Т SCLK SDI (0/I)d DGND(1/0) SYNC RD NC DS012498-1

TRI-STATE<sup>®</sup> is a registered trademark of National Semiconductor Corporation MICROWIRE<sup>™</sup> is a trademark of National Semiconductor Corporation.

| Absolute Maximu | m Ratings (Notes 1, |  |

|-----------------|---------------------|--|

| 2)              | -                   |  |

### Operating Ratings (Note 1) (Note 2)

| - | -)                                                |                              | Operating Temperature               |                                       |

|---|---------------------------------------------------|------------------------------|-------------------------------------|---------------------------------------|

|   | Positive Supply Voltage (V+ = $V_A = V_E$         | $_{\rm D} = V_{\rm D(I/O)})$ | Range                               | $T_{MIN} \le T_A \le T_{MAX}$         |

|   | With Respect to GND = AGND = DC                   | GND =                        | LM9800CCV, LM9800CCVF               | 10°C ≤ T <sub>A</sub> ≤ +70°C         |

|   | DGND <sub>(I/O</sub> )                            | 6.5V                         | V <sub>A</sub> Supply Voltage       | +4.75V to +5.25V                      |

| 1 | /oltage On Any Input or Output Pin                | 0.3V to V <sup>+</sup> +0.3V | V <sub>D</sub> Supply Voltage       | +4.75V to +5.25V                      |

|   | nput Current at any pin (Note 3)                  | ±25 mA                       | V <sub>D(I/O)</sub> Supply Voltage  | +2.7V to +5.25V                       |

| F | Package Input Current (Note 3)                    | ±50 mA                       | V <sub>A</sub> -V <sub>D</sub>      | ≤100 mW                               |

|   | Package Dissipation at T <sub>A</sub> = 25°C (Not | e 4)                         | V <sub>A</sub> -V <sub>D(I/O)</sub> | ≥ –100 mV                             |

| E | ESD Susceptibility (Note 5)                       |                              | OS, REF IN Voltage Range            | -0.05V to V <sub>A</sub> + 0.05V      |

|   | Human Body Model                                  | 3000V                        | CD0-CD6, MCLK, SYNC,                |                                       |

| 1 | Soldering Information                             |                              | SDI, SCLK, CS , RD                  |                                       |

|   | Infrared, 10 seconds (Note 6)                     | 300°C                        | Voltage Range                       | -0.05V to V <sub>D(I/O)</sub> + 0.05V |

| 1 | Storage Temperature                               | –65°C to +150°C              | - 0                                 | 2(00)                                 |

## **Electrical Characteristics**

The following specifications apply for AGND = DGND = DGND<sub>(I/O)</sub> = 0V,  $V_A = V_D = +5.0V_{DC}$ ,  $V_{D(I/O)} = +5.0V$  or  $+3.0V_{DC}$ , REF IN =  $+1.225V_{DC}$ ,  $f_{MCLK} = 20MHz$ ,  $R_s = 25\Omega$ . Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$  (Note 8)

| Symbol             | Parameter                                                            | Conditions                                                             | Typical  | Limits    | Units      |

|--------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|----------|-----------|------------|

|                    |                                                                      |                                                                        | (Note 9) | (Note 10) | (Limits)   |

| CCD Sou            | rce Requirements for Full Specified Accu                             | racy and Dynamic Range (Note 12)                                       | )        |           |            |

| V <sub>WHITE</sub> | Maximum Peak CCD Differential                                        | VGA Bypassed                                                           |          | 1.1       | V (min)    |

|                    | Signal Range                                                         | VGA On (V <sub>GAIN</sub> = 2.0V)                                      |          | 0.5       | V (min)    |

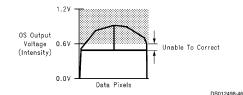

|                    | Correctable Range of CCD Pixel-to-Pixel V <sub>WHITE</sub> Variation |                                                                        |          | 6         | dB (max)   |

| V <sub>RFT</sub>   | CCD Reset Feed Through Amplitude                                     |                                                                        | 2        |           | V (max)    |

| ADC Cha            | racteristics                                                         | •                                                                      |          |           |            |

|                    | Resolution with No Missing Codes                                     |                                                                        |          | 8         | Bits (min) |

| ILE                | Integral Linearity Error (Note 11)                                   |                                                                        | ±0.5     | ±1        | LSB (max)  |

| DNL                | Differential Non-Linearity                                           |                                                                        | ±0.5     | ±1        | LSB (max)  |

| PGA Cha            | racteristics                                                         | •                                                                      | •        |           |            |

|                    | Monotonicity                                                         |                                                                        |          | 7         | bits (min) |

|                    | Gain Range                                                           | $Gain_{PGA} = 20log_{10} \left(1 + \frac{PGA code}{128}\right)$        |          | 0         | dB (min)   |

|                    |                                                                      | 0411PGA = 2010g10 (1 + 128 )                                           |          | 6         | dB (max)   |

|                    | Gain Error at any gain                                               |                                                                        |          | 1.0       | % (max)    |

| VGA Cha            | racteristics                                                         | 1                                                                      |          | 1         |            |

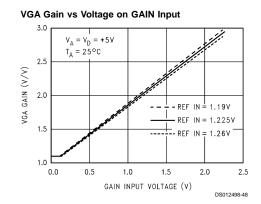

|                    | VGA Gain Error vs. Formula                                           | $Gain_{VGA} = 1 + 2\left(\frac{V_{GAIN} + 0.12V}{REFOUT_{MID}}\right)$ |          | ±6        | % (max)    |

| Coarse C           | Offset Trim Characteristics                                          | L                                                                      |          |           |            |

|                    | Offset DAC LSB Size                                                  |                                                                        | 1        |           | LSB        |

| System C           | Characteristics                                                      |                                                                        |          |           |            |

|                    | Full Channel Offset Error (Adjusted)                                 | Offset DAC, Offset Add<br>Adjusted                                     |          | ±1        | LSB (max)  |

|                    | Full Channel Gain Error                                              | PGA Gain = 0 dB                                                        |          | -5        | % (min)    |

|                    |                                                                      |                                                                        |          | +10       | % (max)    |

| Referenc           | e and Analog Input Characteristics (Note                             | 7)                                                                     |          | 1         |            |

|                    | OS Input Capacitance                                                 |                                                                        | 5        |           | pF         |

|                    | OS Input Leakage Current                                             | Measured with OS = $2.45V_{DC}$                                        | 2        | 20        | nA (max)   |

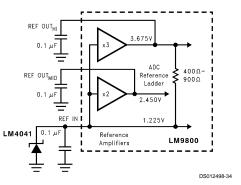

| R <sub>REF</sub>   | ADC Reference Ladder (REF OUT <sub>HI</sub>                          |                                                                        | 4000     | 500       | Ω (min)    |

|                    | to REF IN) Impedance                                                 |                                                                        | 1000     | 2000      | Ω (max)    |

| REF IN             | Reference Voltage (Note 12)                                          |                                                                        | 4.005    | 1.19      | V (min)    |

|                    |                                                                      |                                                                        | 1.225    | 1.26      | V (max)    |

| Symbol              | Parameter                           | Conditions                                              | Typical<br>(Note 9) | Limits<br>(Note 10) | Units<br>(Limits) |

|---------------------|-------------------------------------|---------------------------------------------------------|---------------------|---------------------|-------------------|

| CD0-CD6             | , MCLK, SYNC, SDI, SCLK, CS , RI    | Digital Input Characteristics                           | 1                   |                     | 1                 |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | $V_{D(I/O)} = 5.25V$                                    |                     | 2.0                 | V (min)           |

|                     |                                     | $V_{D(I/O)} = 3.6V$                                     |                     | 2.0                 | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | V <sub>D(I/O)</sub> = 4.75V                             |                     | 0.8                 | V (max)           |

|                     |                                     | $V_{D(I/O)} = 2.7V$                                     |                     | 0.7                 | V (max)           |

| I <sub>IN</sub>     | Input Leakage Current               | $V_{IN} = V_{D}$                                        | 0.1                 |                     | μA                |

|                     |                                     | V <sub>IN</sub> = DGND                                  | -0.1                |                     | μA                |

| CIN                 | Input Capacitance                   |                                                         | 5                   |                     | pF                |

| DD0-DD7             | , EOC , CCLK, SDO Digital Output    | Characteristics                                         | <b>.</b>            | •                   |                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | V <sub>D(I/O)</sub> = 4.75V, I <sub>OUT</sub> = -360 μA |                     | 2.4                 | V (min)           |

|                     |                                     | V <sub>D(I/O)</sub> = 4.75V, I <sub>OUT</sub> = -10 μA  |                     | 4.4                 | V (min)           |

|                     |                                     | V <sub>D(I/O)</sub> = 2.7V, I <sub>OUT</sub> = -360 μA  |                     | 2.1                 | V (min)           |

|                     |                                     | $V_{D(I/O)} = 2.7V, I_{OUT} = -10 \ \mu A$              |                     | 2.5                 | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | V <sub>D(I/O)</sub> = 5.25V, I <sub>OUT</sub> = 1.6 mA  |                     | 0.4                 | V (max)           |

|                     |                                     | $V_{D(I/O)} = 3.6V, I_{OUT} = 1.6 \text{ mA}$           |                     | 0.4                 | V (max)           |

| I <sub>OUT</sub>    | TRI-STATE® Output Current           | V <sub>OUT</sub> = DGND                                 | 0.1                 |                     | μA                |

|                     | (DD0-DD7 only)                      | $V_{OUT} = V_{D}$                                       | -0.1                |                     | μA                |

| C <sub>OUT</sub>    | TRI-STATE Output Capacitance        |                                                         | 5                   |                     | pF                |

|                     | , TR Digital Output Characteristics |                                                         |                     |                     |                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | V <sub>D</sub> = 4.75V, I <sub>OUT</sub> = -360 μA      |                     | 2.4                 | V (min)           |

|                     |                                     | V <sub>D</sub> = 4.75V, I <sub>OUT</sub> = -10 μA       |                     | 4.4                 | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | V <sub>D</sub> = 5.25V, I <sub>OUT</sub> = 1.6 mA       |                     | 0.4                 | V (max)           |

| Power Su            | pply Characteristics                |                                                         | - <b>I</b>          |                     |                   |

| I <sub>A</sub>      | Analog Supply Current               | Operating                                               | 32                  | 42                  | mA (max           |

|                     |                                     | Standby                                                 | 20                  |                     | μA                |

| I <sub>D</sub>      | Digital Supply Current              | Operating                                               | 6                   | 10                  | mA (max           |

|                     |                                     | Standby                                                 | 4                   |                     | mA                |

| I <sub>D(I/O)</sub> | Digital I/O Supply Current          | Operating, $V_{D(I/O)} = 5.0V$                          | 3.5                 | 6                   | mA (max           |

|                     |                                     | Operating, $V_{D(I/O)} = 3.0V$                          | 1.6                 | 2                   | mA (max           |

|                     |                                     | Standby, $V_{D(I/Q)} = 5.0V \text{ or } 3.0V$           | 0.5                 |                     | mA                |

AC Electrical Characteristics, MCLK Independent The following specifications apply for AGND = DGND = DGND<sub>(I/O)</sub> = 0V,  $V_A = V_D = V_{D(I/O)} = +5.0V_{DC}$ , REF IN = +1.225V<sub>DC</sub>,  $f_{MCLK} = 20MHz$ ,  $t_{MCLK} = 1/f_{MCLK}$ ,  $t_c = t_c = 5ns$ ,  $R_s = 25\Omega$ ,  $C_L$  (databus loading) = 50 pF/pin. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol                              | Parameter                          | Conditions | Typical  | Limits    | Units     |

|-------------------------------------|------------------------------------|------------|----------|-----------|-----------|

|                                     |                                    |            | (Note 9) | (Note 10) | (Limits)  |

| f <sub>MCLK</sub>                   | Maximum MCLK Frequency             |            |          | 20        | MHz (min) |

|                                     | Minimum MCLK Frequency             |            |          | 5         | MHz (max) |

|                                     | MCLK Duty Cycle                    |            | 30       | 40        | % (min)   |

|                                     |                                    |            | 70       | 60        | % (max)   |

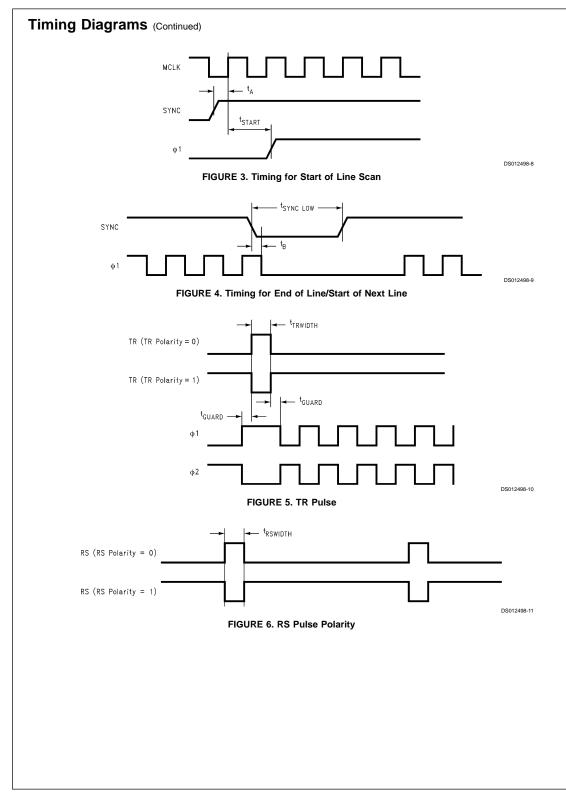

| t <sub>A</sub>                      | SYNC setup of MCLK                 |            | 5        | 10        | ns (min)  |

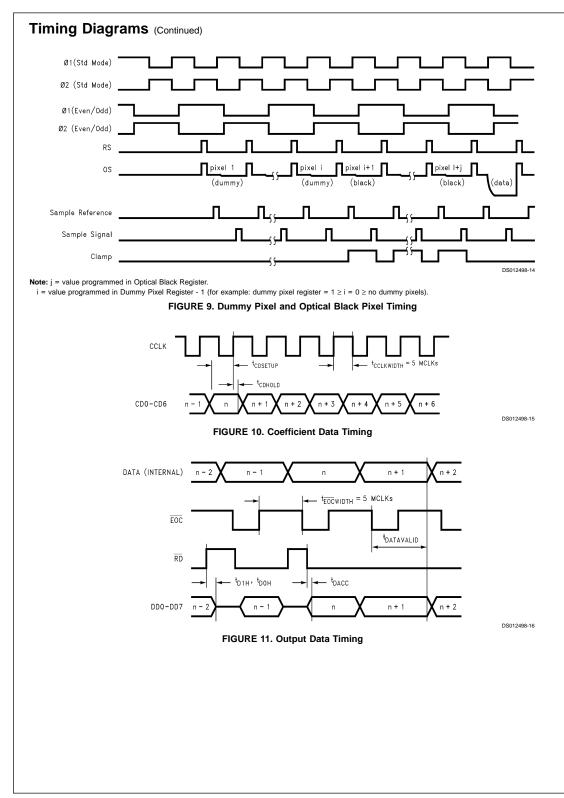

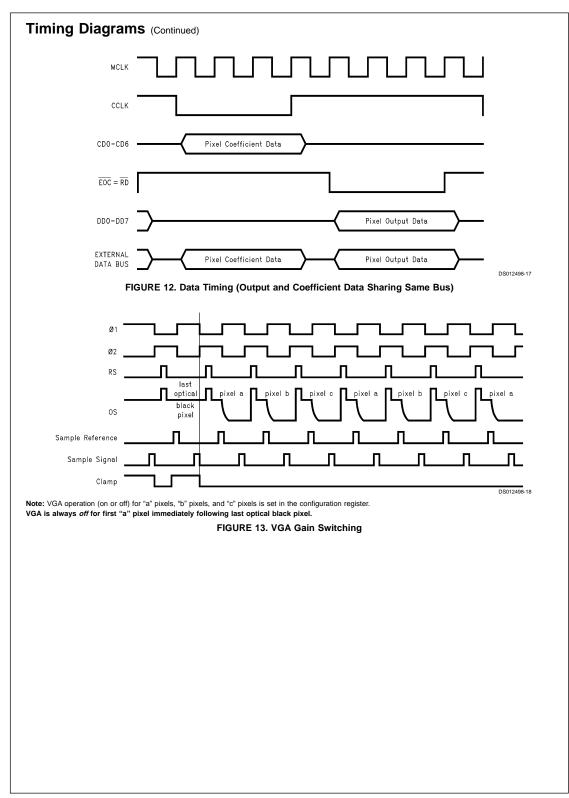

| t <sub>CDSETUP</sub>                | Correction Data valid to CLK Setup |            | 14       | 20        | ns (min)  |

| t <sub>CDHOLD</sub>                 | Correction Data valid to CLK Hold  |            | -12      | 0         | ns (min)  |

| t <sub>D1H</sub> , t <sub>D0H</sub> | RD High to DD0–DD7 TRI-STATE       |            | 7        | 15        | ns (max)  |

| Symbol                              | g specifications apply for AGND = DGND =<br>MHz, t <sub>MCLK</sub> = 1/f <sub>MCLK</sub> , t <sub>r</sub> = t <sub>f</sub> = 5ns, R <sub>s</sub> = 25<br><b>D</b> T <sub>MAX</sub> ; all other limits T <sub>A</sub> = T <sub>J</sub> = 25°C.<br>Parameter | Conditions                                  | Typical  | Limits              | Units                |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|---------------------|----------------------|

|                                     |                                                                                                                                                                                                                                                            |                                             | (Note 9) | (Note 10)           | (Limits)             |

| t <sub>DACC</sub>                   | Access Time Delay from RD Low to<br>DD0–DD7 Data Valid                                                                                                                                                                                                     |                                             | 20       | 40                  | ns (max)             |

| f <sub>SCLK</sub>                   | Maximum SCLK Frequency                                                                                                                                                                                                                                     |                                             |          | 2.5                 | MHz (max             |

|                                     | SCLK Duty Cycle                                                                                                                                                                                                                                            |                                             |          | 40<br>60            | % (min)              |

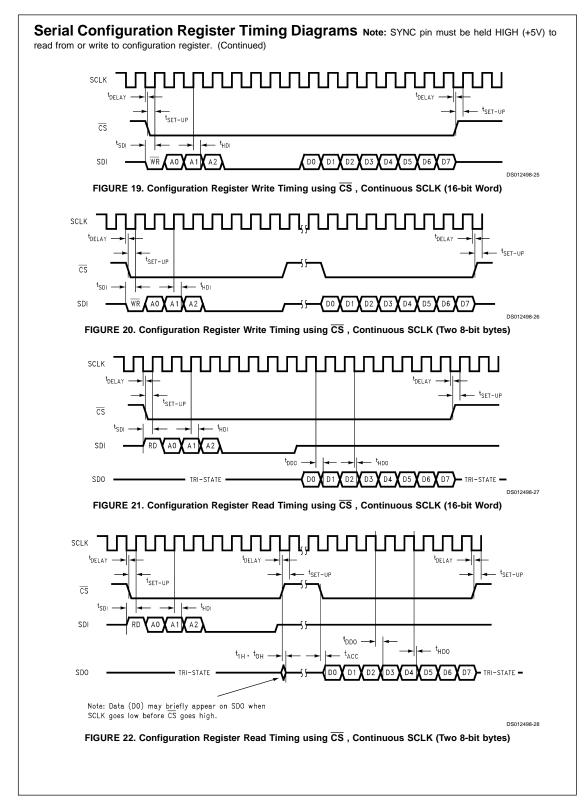

| t <sub>SDI</sub>                    | SDI Set-Up Time from SCLK<br>Rising Edge                                                                                                                                                                                                                   | SDI Set-Up Time from SCLK     3     10      |          | % (max)<br>ns (min) |                      |

| t <sub>HDI</sub>                    | SDI Hold Time from SCLK<br>Rising Edge                                                                                                                                                                                                                     |                                             | 2        | 15                  | ns (min)             |

| t <sub>DDO</sub>                    | Delay from SCLK Falling Edge to<br>SDO Data Valid                                                                                                                                                                                                          |                                             | 35       | 55                  | ns (max)             |

| t <sub>HDO</sub>                    | SDO Hold Time from SCLK                                                                                                                                                                                                                                    | $R_{L} = 3K, C_{L} = 25 \text{ pF}$         | 21       | 55<br>5             | ns (max)             |

| t <sub>DELAY</sub>                  | Falling Edge DELAY from SCLK Falling Edge to CS Rising or Falling Edge                                                                                                                                                                                     |                                             | 2        | 5                   | ns (min)<br>ns (min) |

| t <sub>SETUP</sub>                  | Set-Up Time of CS Rising or Falling<br>Edge to SCLK Rising Edge                                                                                                                                                                                            |                                             | -2       | 10                  | ns (min)             |

| t <sub>SACC</sub>                   | Access Time Delay from CS Falling<br>Edge to SDO Data Valid                                                                                                                                                                                                |                                             | 20       | 40                  | ns (max)             |

| t <sub>s1н</sub> , t <sub>soн</sub> | Delay from CS Rising Edge to SDO<br>TRI-STATE                                                                                                                                                                                                              | $R_{L} = 3K, C_{L} = 50 \text{ pF}$         | 40       | 100                 | ns (max)             |

| t <sub>RDO</sub>                    | SDO Rise Time, TRI-STATE to High                                                                                                                                                                                                                           | R <sub>L</sub> = 3K, C <sub>L</sub> = 50 pF | 20       |                     | ns                   |

|                                     | SDO Rise Time, Low to High                                                                                                                                                                                                                                 |                                             | 20       |                     | ns                   |

| t <sub>FDO</sub>                    | SDO Fall Time, TRI-STATE to Low                                                                                                                                                                                                                            | $R_{L} = 3K, C_{L} = 50 \text{ pF}$         | 20       |                     | ns                   |

|                                     | SDO Fall Time, High to Low                                                                                                                                                                                                                                 |                                             | 20       |                     | ns                   |

| Symbol                 | Parameter                    | Conditions        | Typical  | Limits                | Units                  |  |

|------------------------|------------------------------|-------------------|----------|-----------------------|------------------------|--|

| -                      |                              |                   | (Note 9) | (Note 10)             | (Limits)               |  |

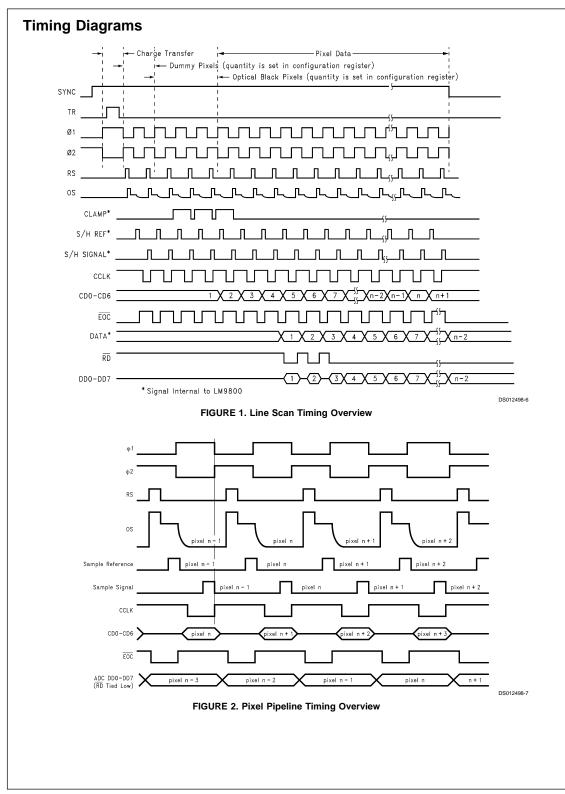

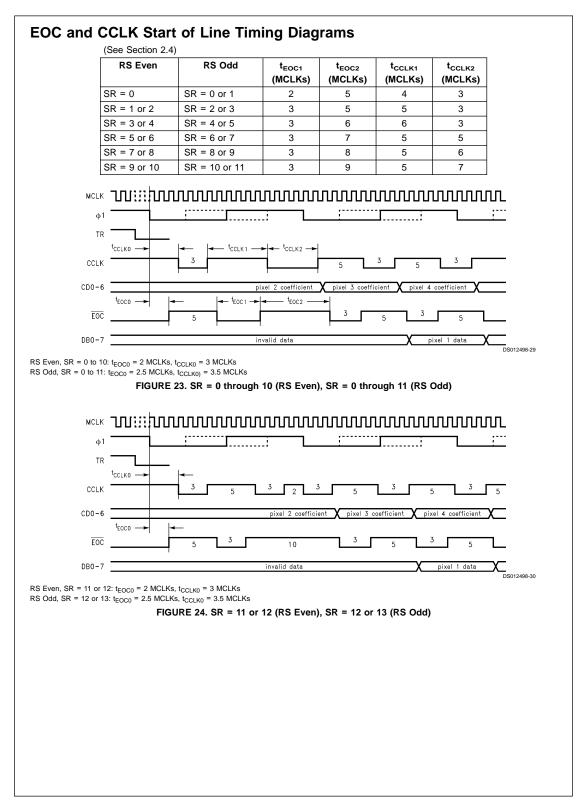

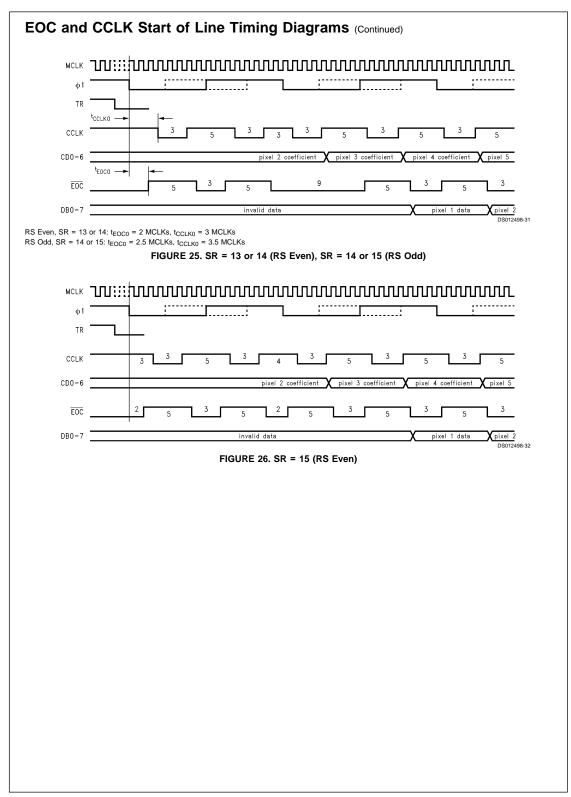

| t <sub>START</sub>     | MCLK to first                |                   | 50ns     | 1                     | t <sub>MCLK</sub>      |  |

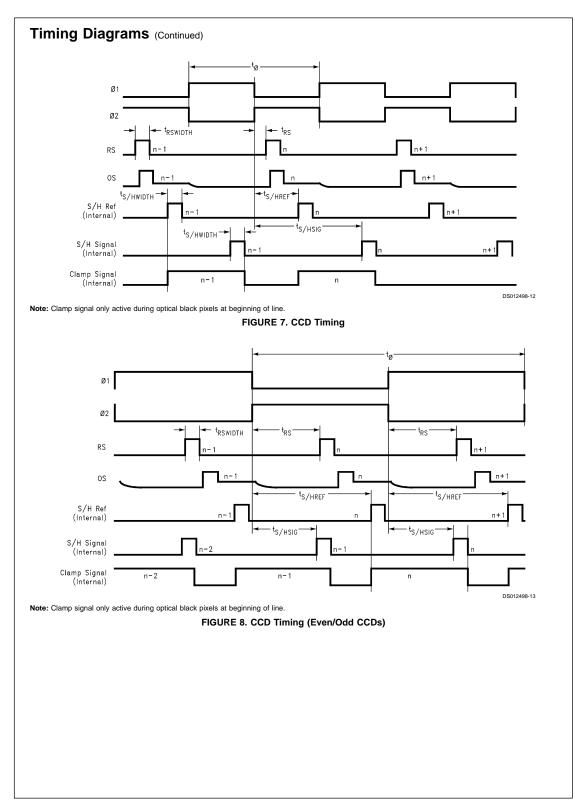

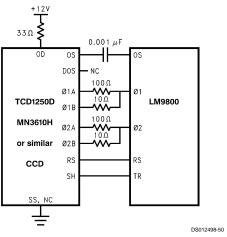

| t <sub>o</sub>         | φ1, φ2 Clock Period          | Standard CCD Mode | 400ns    | 8                     | t <sub>MCLK</sub>      |  |

|                        |                              | Even/Odd CCD Mode | 800ns    | 16                    | t <sub>MCLK</sub>      |  |

| t <sub>TRWIDTH</sub>   | Transfer Pulse (TR) Width    |                   |          | C.R.                  | μs                     |  |

| t <sub>GUARD</sub>     | φ1 to TR, TR to φ1 Guardband |                   |          | C.R.                  | ns                     |  |

| t <sub>RSWIDTH</sub>   | Reset Pulse (RS) Width       |                   |          | C.R.                  | ns                     |  |

| t <sub>RS</sub>        | Falling Edge of              | Standard CCD Mode |          | C.R.                  | ns                     |  |

|                        | Either Edge of               | Even/Odd CCD Mode |          |                       |                        |  |

| t <sub>S/HREF</sub>    | Falling Edge of              | Standard CCD Mode |          | C.R.                  | ns                     |  |

|                        | Either Edge of               | Even/Odd CCD Mode |          |                       |                        |  |

| t <sub>s/HSIG</sub>    | Falling Edge of              | Standard CCD Mode |          | C.R.                  | ns                     |  |

|                        | Either Edge of               | Even/Odd CCD Mode |          |                       |                        |  |

| t <sub>S/HWIDTH</sub>  | Sample Pulse Width           |                   | 50ns     | 1                     | t <sub>MCLK</sub>      |  |

|                        | (Acquisition Time)           |                   |          |                       |                        |  |

| t <sub>SYNCLOW</sub>   | SYNC Low Between Lines       |                   | 100ns    | 2                     | t <sub>MCLK</sub> (min |  |

| t <sub>B</sub>         | SYNC Setup of                |                   |          | 2                     | t <sub>MCLK</sub> (max |  |

| t <sub>CCLKWIDTH</sub> | CCLK Pulse Width             |                   | 250ns    | 5                     | t <sub>MCLK</sub>      |  |

| t <sub>DATAVALID</sub> | Data Valid Time from EOC Low |                   |          | 300                   | ns (min)               |  |

| t                      | EOC Pulse Width              |                   | 250ns    | 5                     | t <sub>MCLK</sub>      |  |

|                        | φ1 and φ2 Frequency          | Standard CCD Mode | 2.5MHz   | f <sub>мськ</sub> /8  | Hz                     |  |

|                        |                              | Even/Odd CCD Mode | 1.25MHz  | f <sub>мс∟к</sub> /16 | Hz                     |  |

|                        | φ1 and φ2 Duty Cycle         |                   |          | 50                    | %                      |  |

#### ..... **~** . . . . .

### **Electrical Characteristics (Notes)**

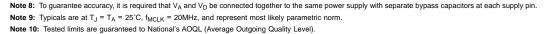

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to  $GND = AGND = DGND = DGND_{(I/O)} = 0V$ , unless otherwise specified.

Note 3: When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sub>A</sub> or V<sub>D</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

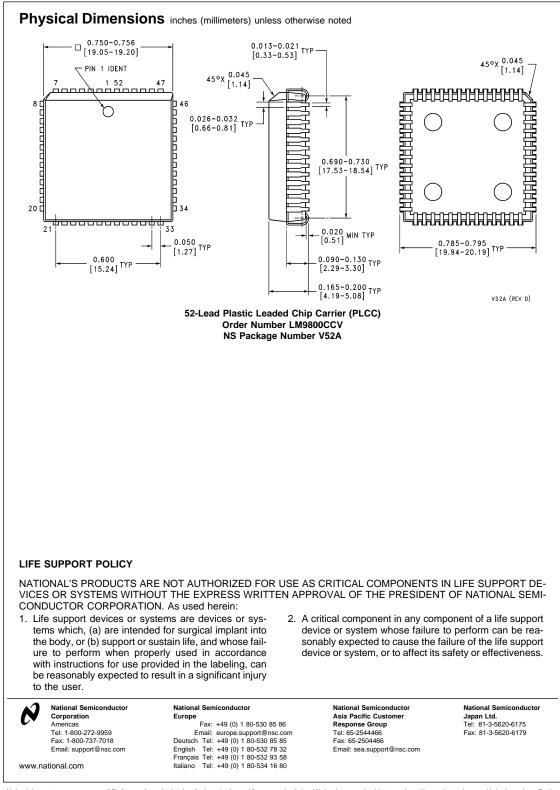

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{Jmax} - T_A)/\theta_{JA}$ .  $T_{Jmax} = 150^{\circ}C$  for this device. The typical thermal resistance  $\theta_{JA}$  of this part when board mounted is 52°C/W for the V52A PLCC package.

Note 5: Human body model, 100 pF capacitor discharged through a  $1.5\Omega$  resistor.

Note 6: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in any post 1986 National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

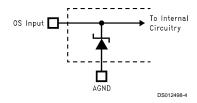

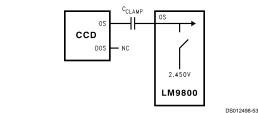

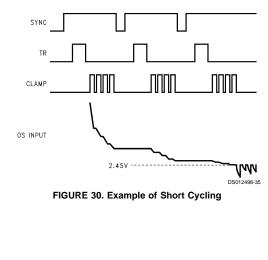

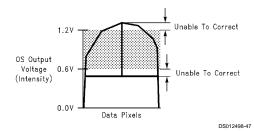

Note 7: A Zener diode clamps the OS analog input to AGND as shown below. This input protection, in combination with the external clamp capacitor and the output impedance of the CCD, prevents damage to the LM9800 from transients during power-up.

## Electrical Characteristics (Notes) (Continued)

Note 11: Integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function of the ADC.

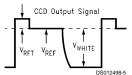

Note 12: V<sub>REF</sub> is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse. V<sub>WHITE</sub> is defined as the peak CCD pixel output voltage for a white (full scale) image with respect to the reference level, V<sub>REF</sub>. V<sub>REF</sub> is defined as the peak positive deviation above V<sub>REF</sub> of the reset feedthrough pulse. The maximum correctable range of pixel-to-pixel V<sub>WHITE</sub> variation is defined as the maximum variation in V<sub>WHITE</sub> (due to PRNU, light source intensity variation, optics, etc.) that the LM9800 can correct for using its internal PGA.

Note 13: Reference voltages below 1.19V may decrease SNR. Reference voltages above 1.26V may cause clipping errors inside the LM9800. The LM4041EIM3-1.2 (SOT-23 package) or the LM4041EIZ-1.2 (TO-92 package) bandgap voltage references are recommended for this application.

## **Typical Performance Characteristics**

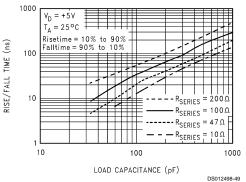

# $\phi 1,\,\phi 2,\,RS,\,TR$ Rise and Fall Times Through a Series Resistance vs. Load Capacitance

### **Pin Descriptions**

|            | CCD Driver Signals                                                                                                                                                                   |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| φ1         | Digital Output. CCD clock signal, phase 1.                                                                                                                                           |  |  |  |  |

| φ2         | Digital Output. CCD clock signal, phase 2.                                                                                                                                           |  |  |  |  |

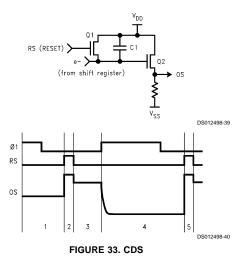

| RS         | Digital Output. Reset pulse for the CCD.                                                                                                                                             |  |  |  |  |

| TR         | Digital Output. Transfer pulse for the CCD.                                                                                                                                          |  |  |  |  |

| Analog I/O |                                                                                                                                                                                      |  |  |  |  |

| OS         | Analog Input. This is the OS (Output<br>Signal) from the CCD. The maximum<br>peak signal that can be accurately<br>digitized is equal to the voltage at REF<br>IN, typically 1.225V. |  |  |  |  |

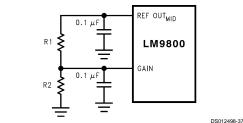

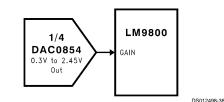

| GAIN       | Analog Input. The voltage on this pin<br>determines the gain of the VGA when<br>the VGA is enabled. This input should<br>be bypassed to AGND using a 0.1 µF<br>monolithic capacitor. |  |  |  |  |

| REF IN                 | Analog Inputs. These two pins are the system reference voltage inputs and should be tied together to a 1.225V voltage source and bypassed to AGND with a 0.1 µF monolithic capacitor.                                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF OUT <sub>HI</sub>  | Analog Output. This reference voltage is developed internally by the LM9800, and is equal to 3 times REF IN. It should be bypassed to AGND with a 0.1 $\mu$ F monolithic capacitor.                                                                                                                        |

| REF OUT <sub>MID</sub> | Analog Output. This reference voltage is developed internally by the LM9800, and is equal to 2 times REF IN. It should be bypassed to AGND using a 0.1 $\mu$ F monolithic capacitor. This pin can source up to 250 $\mu$ A when used to power a voltage divider for setting the voltage at the GAIN input. |

| I <sub>SET</sub>       | Analog Input. This input is used to set<br>internal bias currents inside the LM9800.<br>It should be connected to $V_A$ through a<br>75 k $\Omega$ resistor.                                                                                                                                               |

| V <sub>test1</sub> ,    | Analog Inputs/Outputs. These pins are                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>TEST2</sub>      | used for testing the device during                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                         | manufacture and should be left                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                         | unconnected.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                         | Configuration Register I/O                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SDI                     | Digital Input. Serial Data Input pin.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SDO                     | Digital Output. Serial Data Output pin.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| SCLK                    | Digital Input. This is the serial data<br>clock, used to clock data in through SDI<br>and out through SDO. SCLK is<br>asynchronous to MCLK. Input data is<br>latched and output data is changed on<br>the rising edge of SCLK.                                                                                                                                                                             |  |  |  |  |

| <u>CS</u>               | Digital Input. This is the Chip Select<br>signal for writing to the Configuration<br>Register through the serial interface.<br>This input must be low in order to<br>communicate with the Configuration<br>Register. This pin is used for serial I/O<br>only–it has no effect on any other<br>section of the chip. Note: The SYNC<br>pin must be high to read or write<br>from the Configuration register. |  |  |  |  |

| General Digital I/O     |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MCLK                    | Digital Input. This is the 20 MHz (typical master system clock.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SYNC                    | Digital Input. A low-to-high transition on<br>this input begins a line scan operation.<br>The line scan operation terminates when<br>this input is taken low. A low-to-high<br>transition on this input will also reset the<br>serial I/O port to the Configuration<br>Register. The SYNC pin must be high to<br>read or write from the Configuration<br>register.                                         |  |  |  |  |

|                         | Digital Coefficient I/O                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| CD0 (LSB)–<br>CD6 (MSB) | Digital Inputs. Correction Coefficient<br>Databus. This is the 7-bit data path for<br>the gain adjust PGA, used during line<br>scan.                                                                                                                                                                                                                                                                       |  |  |  |  |

| CCLK                    | Digital Output. This is the signal that is<br>used to clock the Gain coefficients into<br>the LM9800. Data is latched on the<br>rising edge of CCLK.                                                                                                                                                                                                                                                       |  |  |  |  |

|                         | Digital Output I/O                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DD0 (LSB)-<br>DD7 (MSB) | Digital Outputs. Pixel Output Databus.<br>This data bus outputs the 8-bit digital<br>output data during line scan.                                                                                                                                                                                                                                                             |  |  |  |  |

| EOC                     | Digital Output. This is the End of<br>Conversion signal from the ADC<br>indicating that new pixel data is<br>available.                                                                                                                                                                                                                                                        |  |  |  |  |

| RD                      | Digital Input. Taking this input low<br>places the data stored in the output<br>latch on the bus. When this input is high<br>the DD0–DD7 bus is in TRI-STATE.                                                                                                                                                                                                                  |  |  |  |  |

|                         | Analog Power                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>A</sub>          | This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1 $\mu$ F monolithic capacitor in parallel with a 10 $\mu$ F tantalum capacitor.                                                                                                                                                        |  |  |  |  |

| AGND                    | This is the ground return for the analog supply.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Digital Power           |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| V <sub>D</sub>          | This is the positive supply pin for the digital supply. It should be connected to a voltage source of $+5V$ and bypassed to DGND with a 0.1 $\mu$ F monolithic capacitor.                                                                                                                                                                                                      |  |  |  |  |

| DGND                    | This is the ground return for the digital supply.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| V <sub>D(I/O)</sub>     | This is the positive supply pin for the digital supply for the LM9800's I/O. It should be connected to a voltage source of +3V to +5V and bypassed to $DGND_{(I/O)}$ with a 0.1 $\mu$ F monolithic capacitor. If the supply for this pin is different than the supply for V <sub>A</sub> and V <sub>D</sub> , it should also be bypassed with a 10 $\mu$ F tantalum capacitor. |  |  |  |  |

| DGND <sub>(I/O)</sub>   | This is the ground return for the digital supply for the LM9800's I/O.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|    |    |    |                                         | TABLE                     | 1. Configurati  | on Register A           | ddress Tab  | le                     |                              |           |

|----|----|----|-----------------------------------------|---------------------------|-----------------|-------------------------|-------------|------------------------|------------------------------|-----------|

| A2 | A1 | A0 | D7                                      | D6                        | D5              | D4                      | D3          | D2                     | D1                           | D0        |

| 0  | 0  | 0  | Standard<br>Mode or<br>Even/Odd<br>Mode | Pu                        | S<br>Ise<br>dth | RS<br>Pulse<br>Polarity |             |                        | se Position<br>n Value is 1) |           |

|    |    |    | MODE                                    | RSW1                      | RSW0            | RSPOL                   | RSPOS3      | RSPOS2                 | RSPOS1                       | RSPOS0    |

| •  | •  |    |                                         | Sample Reference Position |                 |                         |             | Sample Signal Position |                              |           |

| 0  | 0  | 1  | SR3                                     | SR2                       | SR1             | SR0                     | SS3         | SS2                    | SS1                          | SS0       |

|    |    |    | φ1                                      | φ2                        | RS              | TR                      | 70.0        |                        | TR-ø1                        | TR        |

| 0  | 1  | 0  | Enable                                  | Enable                    | Enable          | Enable                  |             | Ilse Width             | Guardband                    | Polarity  |

|    |    |    | ¢1EN                                    | ¢2EN                      | RSEN            | TREN                    | TRW1        | TRW0                   | TRGRD                        | TRPOL     |

| 0  | 1  | 1  | Dummy Pixels (Minir                     |                           |                 |                         | num Value i | s 1)                   |                              |           |

| 0  | I  | I  | BLS7                                    | BLS6                      | BLS5            | BLS4                    | BLS3        | BLS2                   | BLS1                         | BLS0      |

| 4  | 0  | 0  |                                         | •                         | Optical B       | lack Pixels (Mi         | nimum Valu  | e is 1)                |                              |           |

| 1  | 0  | 0  | BLL7                                    | BLL6                      | BLL5            | BLL4                    | BLL3        | BLL2                   | BLL1                         | BLL0      |

| 1  | 0  | 1  |                                         |                           |                 | PGA Gain Co             | efficient   |                        | •                            |           |

| I  | 0  | I  | 0                                       | GAIN6                     | GAIN5           | GAIN4                   | GAIN3       | GAIN2                  | GAIN1                        | GAIN0     |

|    |    |    | PGA Gain                                | Test                      | Power-          | Offset                  | VGA         | VGA State              | VGA State                    | VGA State |

| 1  | 1  | 0  | Source                                  | Mode                      | down            | Add                     | On/Off      | Pixel c                | Pixel b                      | Pixel a   |

|    |    |    | PGASRC                                  | 0                         | PD              | OFFADD                  | VGA         | G3                     | G2                           | G1        |

|    |    |    | Offset DAC                              | Offset DAC                | Offset DAC      | Offset DAC              |             | Toe                    | t Modes                      |           |

| 1  | 1  | 1  | Sign                                    | MSB                       |                 | LSB                     |             | Tes                    |                              |           |

|    |    |    | ODSIGN                                  | VOS2                      | VOS1            | VOS0                    | 0           | 0                      | 0                            | 0         |

|                                    |      | TAE | BLE 2. Configuration | n Register | Paramete | rs                          |                                                            |  |

|------------------------------------|------|-----|----------------------|------------|----------|-----------------------------|------------------------------------------------------------|--|

| Parameter                          |      |     | Contr                | ol Bits    |          |                             | Result                                                     |  |

| MODE                               | MODE |     | Contra               | or bits    |          |                             | Result                                                     |  |

| MODE                               | 0    |     |                      |            | Standard | I CCD (                     | $= f_{MOUV}(8)$                                            |  |

|                                    | 1    |     |                      |            |          | d CCD (                     |                                                            |  |

| RS Pulse Width                     | RS1  | RS0 |                      |            |          | (+                          |                                                            |  |

| (t <sub>RSWIDTH</sub> )            | 0    | 0   |                      |            |          |                             | 1 t <sub>MCLK</sub> (50ns)                                 |  |

|                                    | 0 1  |     |                      |            |          | 2 t <sub>MCLK</sub> (100ns) |                                                            |  |

|                                    | 1    | 0   |                      |            |          |                             | 3 t <sub>MCLK</sub> (150ns)                                |  |

|                                    | 1    | 1   |                      |            |          |                             | 4 t <sub>MCLK</sub> (200ns)                                |  |

| RS Pulse Polarity                  | RSF  | POL |                      |            |          |                             |                                                            |  |

|                                    | C    | )   |                      |            |          |                             | RS                                                         |  |

|                                    | 1    |     |                      |            |          |                             | RS                                                         |  |

| RS Pulse Position                  | RSP  | OS3 | RSPOS2               | RSP        | OS1      | RSPOS0                      |                                                            |  |

| (t <sub>RS</sub> )                 | C    | )   | 0                    | (          | 0        | 0                           | Not Valid                                                  |  |

| <b>Note:</b> Minimum<br>Value is 1 | 0    | )   | 0                    | 0          | 0        | 1                           | 0.5t <sub>MCLK</sub> (25 ns                                |  |

|                                    | 0    |     | 0                    | 1          |          | 0                           | 1.0t <sub>MCLK</sub> (50ns                                 |  |

|                                    | C    | )   | 0                    |            | 1        | 1                           | 1.5t <sub>MCLK</sub> (75ns                                 |  |

|                                    | 0    |     | 1                    | (          | C        | 0                           | 2.0t <sub>MCLK</sub> (100ns                                |  |

|                                    | 0    |     | 1                    | 0          | 0        | 1                           | 2.5t <sub>MCLK</sub> (125ns                                |  |

|                                    | 0    |     | 1                    |            | 1        | 0                           | 3.0t <sub>MCLK</sub> (150ns                                |  |

|                                    | 0    | )   | 1                    |            | 1        | 1                           | 3.5t <sub>MCLK</sub> (175ns                                |  |

|                                    | 1    |     | 0                    |            | 0        | 0                           | 4.0t <sub>MCLK</sub> (200ns                                |  |

|                                    | 1    |     | 0                    |            | )        | 1                           | 4.5t <sub>MCLK</sub> (225ns                                |  |

|                                    | 1    |     | 0                    |            | 1        | 0                           | 5.0t <sub>MCLK</sub> (250ns                                |  |

|                                    |      |     | 0                    | 1          |          | 1                           | 5.5t <sub>MCLK</sub> (275ns                                |  |

|                                    | 1    |     | 1                    | 0          |          | 0                           | 6.0t <sub>MCLK</sub> (300 n                                |  |

|                                    | 1    |     | 1                    |            |          | 1                           | 6.5t <sub>MCLK</sub> (325 n                                |  |

|                                    | 1    |     | 1<br>1               |            | 1<br>1   | 0                           | 7.0t <sub>MCLK</sub> (350 n                                |  |

| Sample Reference                   | SF   |     | SR2                  | SF         |          | SR0                         | 7.5t <sub>MCLK</sub> (375 n                                |  |

| Position (t <sub>S/HREF</sub> )    |      |     | 0                    |            | 0        | 0                           | 0.0t (0.ps)                                                |  |

| (G/IIKEF/                          |      |     | 0                    |            | 5        | 1                           | 0.0t <sub>MCLK</sub> (0 ns)<br>0.5t <sub>MCLK</sub> (25 ns |  |

|                                    |      |     | 0                    |            | 1        | 0                           | 1.0t <sub>MCLK</sub> (50 ns                                |  |

|                                    |      |     | 0                    |            | 1        | 1                           | 1.5t <sub>MCLK</sub> (75 ns                                |  |

|                                    |      |     |                      |            | 0 0      |                             | 2.0t <sub>MCLK</sub> (100 n                                |  |

|                                    | 0    |     |                      |            | 0 1      |                             | 2.5t <sub>MCLK</sub> (125 n                                |  |

|                                    | 0    |     | 1                    |            | 1        | 0                           | 3.0t <sub>MCLK</sub> (150 n                                |  |

|                                    | c    |     | 1                    |            | 1        |                             | 3.5t <sub>MCLK</sub> (175 n                                |  |

|                                    | 1    |     | 0                    |            | 0        |                             | 4.0t <sub>MCLK</sub> (200 n                                |  |

|                                    | 1    |     |                      |            | 0 1      |                             | 4.5t <sub>мськ</sub> (225 n                                |  |

|                                    | 1    |     |                      |            | 1        | 0                           | 5.0t <sub>MCLK</sub> (250 n                                |  |

|                                    | 1    |     | 0                    | ·          | 1        | 1                           | 5.5t <sub>MCLK</sub> (275 n                                |  |

|                                    | 1    |     | 1                    | 0          | C        | 0                           | 6.0t <sub>MCLK</sub> (300 n                                |  |

|                                    | 1    |     | 1                    | 0          | C        | 1                           | 6.5t <sub>MCLK</sub> (325 n                                |  |

|                                    | 1    |     | 1                    | ·          | 1        | 0                           | 7.0t <sub>MCLK</sub> (350 n                                |  |

|                                    | 1    |     | 1                    |            | 1        | 1                           | 7.5t <sub>MCLK</sub> (375 n                                |  |

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | Contro | ol Bits |     | Result                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|---------|-----|-------------------------------|--|

| Sample Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SS3   | SS2    | SS1     | SS0 |                               |  |

| Position (t <sub>S/HSIG</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0      | 0       | 0   | 0.0t <sub>MCLK</sub> (0 ns)   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0      | 0       | 1   | 0.5t <sub>MCLK</sub> (25 ns)  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0      | 1       | 0   | 1.0t <sub>MCLK</sub> (50 ns)  |  |

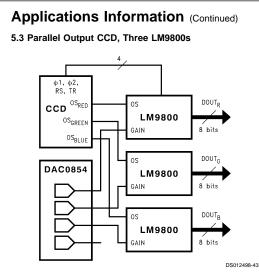

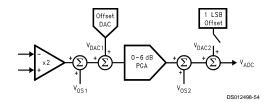

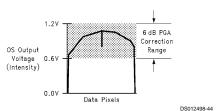

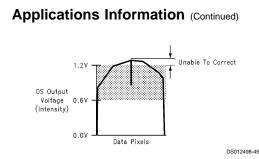

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0      | 1       | 1   | 1.5t <sub>MCLK</sub> (75 ns)  |  |