## **PRELIMINARY**

June 1999

# LMX2350/LMX2352 PLLatinum™ Fractional N RF / Integer N IF Dual Low Power Frequency Synthesizer

LMX2350 2.5 GHz/550 MHz LMX2352 1.2 GHz/550 MHz

## **General Description**

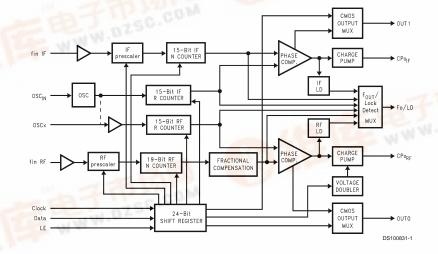

The LMX2350/2352 is part of a family of monolithic integrated fractional N/ Integer N frequency synthesizers designed to be used in a local oscillator subsystem for a radio transceiver. It is fabricated using National's 0.5µ ABiC V silicon BiCMOS process. The LMX2350/2352 contains dual modulus prescalers along with modulo 15 or 16 fractional compensation circuitry in the RF divider. A 16/17 or 32/33 prescale ratio can be selected for the LMX2350, and the LMX2352 provides 8/9 or 16/17 prescale ratios. The IF circuitry for both the LMX2350 and LMX2352 contains an 8/9 prescaler, and is fully programmable. Using a fractional N phase locked loop technique, the LMX2350 /52 can generate very stable low noise control signals for UHF and VHF voltage controlled oscillators (VCO's).

For the RF PLL, a highly flexible 16 level programmable charge pump supplies output current magnitudes from 100µA to 1.6mA. Two uncommitted CMOS outputs can be used to provide external control signals, or configured to FastLock™ mode. Serial data is transferred into the LMX2350/2352 via a three wire interface (Data, LE, Clock). Supply voltage can range from 2.7 V to 5.5 V. The LMX2350/

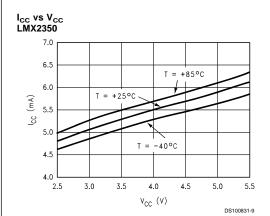

2352 family features very low current consumption; typically LMX2350 (2.5 GHz) 6.75 mA, LMX2352 (1.2 GHz) 5.00 mA at 3.0V. The LMX2350/2352 are available in a 24-pin TSSOP surface mount plastic package.

## **Features**

- 2.7 V to 5.5 V operation

- Low current consumption LMX2350: Icc = 6.75mA typ at 3v LMX2352: Icc = 5.00mA typ at 3v

- Programmable or logical power down mode lcc = 5 µA typ at 3v

- Modulo 15 or 16 fractional RF N divider supports ratios of 1, 2, 3, 4, 5, 8, 15, or 16

- Programmable charge pump current levels RF 100μA to 1.6mA in 100μA steps

IF 100μA or 800 μA

- Digital filtered lock detect

## **Applications**

- Portable wireless communications (PCS/PCN, cordless)

- Dual mode cellular telephone systems

- Zero blind slot TDMA systems

- Spread spectrum communication systems (CDMA)

- Cable TV Tuners (CATV)

## **Block Diagram**

FastLock™ is a trademark of National Semiconductor Corporation.

MICROWIRE™ is a trademark of National Semiconductor Corporation.

PLtatinum™ is a trademark of National Semiconductor Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

## **Connection Diagram**

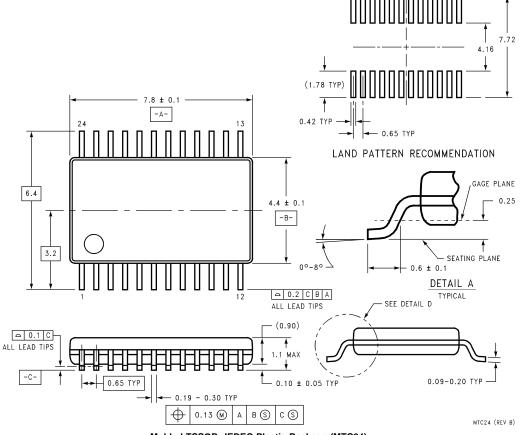

Order Number LMX2350TM or LMX2352TM NS Package Number MTC24

## Pin Descriptions

| Pin<br>No. | Pin<br>Name       | I/O | Description                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OUT0              | 0   | Programmable CMOS output. Level of the output is controlled by IF_N [17] bit.                                                                                                                                                                                                                                                               |

| 2          | Vcc <sub>RF</sub> | -   | RF PLL power supply voltage input. Must be equal to Vcc <sub>IF</sub> . May range from 2.7 V to 5.5 V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                                                                                                                   |

| 3          | V <sub>PRF</sub>  | -   | Power supply for RF charge pump. Must be ≥V <sub>ccRF</sub> and V <sub>ccIF</sub> .                                                                                                                                                                                                                                                         |

| 4          | CP <sub>oRF</sub> | 0   | RF charge pump output. Connected to a loop filter for driving the control input of an external VCO.                                                                                                                                                                                                                                         |

| 5          | GND               | -   | Ground for RF PLL digital circuitry.                                                                                                                                                                                                                                                                                                        |

| 6          | fin RF            | I   | RF prescaler input. Small signal input from the VCO.                                                                                                                                                                                                                                                                                        |

| 7          | fin RF            | I   | RF prescaler complimentary input. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane.                                                                                                                                                                                       |

| 8          | GND               | -   | Ground for RF PLL analog circuitry.                                                                                                                                                                                                                                                                                                         |

| 9          | OSCx              | I/O | Dual mode oscillator output or RF R counter input. Has a Vcc/2 input threshold when configured as an input and can be driven from an external CMOS or TTL logic gate. Can also be configured as an output to work in conjunction with OSCin to form a crystal oscillator. (See functional description 1.1 and programming description 3.1.) |

| 10         | OSCin             | I   | Oscillator input which can be configured to drive both the IF and RF R counter inputs or only the IF R counter depending on the state of the OSC programming bit. (See functional description 1.1 and programming description 3.1.)                                                                                                         |

| 11         | FoLD              | 0   | Multiplexed output of N or R divider and RF/IF lock detect. Active High/Low CMOS output except in analog lock detect mode. (See programming description 3.1.5.)                                                                                                                                                                             |

| 12         | RF_EN             | I   | RF PLL Enable. Powers down RF N and R counters, prescaler, and will TRI-STATE® the charge pump output when LOW. Bringing RF_EN high powers up RF PLL depending on the state of RF_CTL_WORD. (See functional description 1.9.)                                                                                                               |

| 13         | IF_EN             | I   | IF PLL Enable. Powers down IF N and R counters, prescaler, and will TRI-STATE the charge pump output when LOW. Bringing IF_EN high powers up IF PLL depending on the state of IF_CTL_WORD. (See functional description 1.9.)                                                                                                                |

| 14         | CLOCK             | I   | High impedance CMOS Clock input. Data for the various counters is clocked into the 24 - bit shift register on the rising edge.                                                                                                                                                                                                              |

| 15         | DATA              | I   | Binary serial data input. Data entered MSB first. The last two bits are the control bits. High impedance CMOS input.                                                                                                                                                                                                                        |

| 16         | LE                | I   | Load enable high impedance CMOS input. Data stored in the shift registers is loaded into one of the 4 internal latches when LE goes HIGH. (See functional description 1.7.)                                                                                                                                                                 |

| Conr | Connection Diagram (Continued) |     |                                                                                                          |  |  |  |  |  |  |  |  |  |

|------|--------------------------------|-----|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin  | Pin                            | I/O | Description                                                                                              |  |  |  |  |  |  |  |  |  |

| No.  | Name                           |     |                                                                                                          |  |  |  |  |  |  |  |  |  |

| 17   | GND                            | -   | Ground for IF analog circuitry.                                                                          |  |  |  |  |  |  |  |  |  |

| 18   | fin IF                         | I   | IF prescaler complimentary input. A bypass capacitor should be placed as close as possible               |  |  |  |  |  |  |  |  |  |

|      |                                |     | to this pin and be connected directly to the ground plane.                                               |  |  |  |  |  |  |  |  |  |

| 19   | fin IF                         | - 1 | IF prescaler input. Small signal input from the VCO.                                                     |  |  |  |  |  |  |  |  |  |

| 20   | GND                            | -   | Ground for IF digital circuitry.                                                                         |  |  |  |  |  |  |  |  |  |

| 21   | CPo <sub>IF</sub>              | 0   | IF charge pump output. For connection to a loop filter for driving the input of an external VCO.         |  |  |  |  |  |  |  |  |  |

| 22   | Vp <sub>IF</sub>               | -   | Power supply for IF charge pump. Must be $\geq V_{cc_{RF}}$ and $V_{cc_{IF}}$ .                          |  |  |  |  |  |  |  |  |  |

| 23   | Vcc <sub>IF</sub>              | -   | IF power supply voltage input. Must be equal to Vcc <sub>RF</sub> . Input may range from 2.7 V to 5.5 V. |  |  |  |  |  |  |  |  |  |

|      |                                |     | Bypass capacitors should be placed as close as possible to this pin and be connected directly            |  |  |  |  |  |  |  |  |  |

|      |                                |     | to the ground plane.                                                                                     |  |  |  |  |  |  |  |  |  |

| 24   | OUT1                           | 0   | Programmable CMOS output. Level of the output is controlled by IF_N [18] bit.                            |  |  |  |  |  |  |  |  |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

|                                       |                   |      | Value |           |       |

|---------------------------------------|-------------------|------|-------|-----------|-------|

| Parameter                             | Symbol            | Min  | Тур   | Max       | Units |

| Power Supply Voltage                  | Vcc <sub>RF</sub> | -0.3 |       | 6.5       | V     |

|                                       | Vcc <sub>IF</sub> | -0.3 |       | 6.5       | V     |

|                                       | Vp <sub>RF</sub>  | -0.3 |       | 6.5       | V     |

|                                       | Vp <sub>IF</sub>  | -0.3 |       | 6.5       | V     |

| Voltage on any pin with GND = 0 volts | Vi                | -0.3 |       | Vcc + 0.3 | V     |

| Storage Temperature Range             | Ts                | -65  |       | +150      | C°    |

| Lead Temperature (Solder 4 sec.)      | T <sub>L</sub>    |      |       | +260      | C°    |

| ESD - Whole Body Model (Note 2)       |                   |      | 2     |           | Kev   |

## **Recommended Operating Conditions**

| Parameter             | Symbol            | Min               | Тур | Max               | Units |

|-----------------------|-------------------|-------------------|-----|-------------------|-------|

| Power Supply Voltage  | Vcc <sub>RF</sub> | 2.7               |     | 5.5               | V     |

|                       | Vcc <sub>IF</sub> | Vcc <sub>RF</sub> |     | Vcc <sub>RF</sub> | V     |

|                       | Vp <sub>RF</sub>  | Vcc               |     | 5.5               | V     |

|                       | Vp <sub>IF</sub>  | Vcc               |     | 5.5               | V     |

| Operating Temperature | TA                | -40               |     | + 85              | С     |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

**Note 2:** This Device is a high performance RF integrated circuit and is ESD sensitive. Handling and assembly of this device should only be done at ESD-free workstations.

## **Electrical Characteristics** ( $V_{cc_{RF}} = V_{cc_{IF}} = V_{P_{RF}} = V_{P_{IF}} = 3.0V$ ; -40° C < T<sub>A</sub>< 85° C except as specified)

| Sym-<br>bol          | Parameter              |            | Conditions                              | Min  | Тур  | Max             | Units    |  |  |  |

|----------------------|------------------------|------------|-----------------------------------------|------|------|-----------------|----------|--|--|--|

| General              |                        |            |                                         |      |      |                 |          |  |  |  |

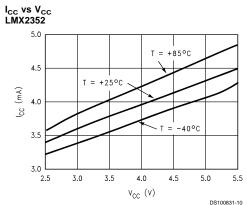

| I <sub>cc</sub>      | Power Supply Current   | LMX2350    | RF and IF, $V_{cc}$ = 2.7V to 5.5V      |      | 6.75 | 7.75            | mA       |  |  |  |

|                      |                        | LMX2352    | RF and IF, $V_{cc}$ = 2.7V to 5.5V      |      | 5.0  | 6.0             | mA       |  |  |  |

|                      |                        | LMX2350/52 | IF only, V <sub>cc</sub> = 2.7V to 5.5V |      | 1.25 | 1.45            | mA       |  |  |  |

| I <sub>CC-PWDN</sub> | Power Down Current     |            | RF_EN = IF_EN = LOW                     |      | 5    |                 | μA       |  |  |  |

| f <sub>in</sub> RF   | RF Operating           | LMX2350    | Prescaler = 32 (Note 3)                 | 1.2  |      | 2.5             | GHz      |  |  |  |

|                      | Frequency              |            | Prescaler = 16 (Note 3)                 | 0.5  |      | 1.2             | GHz      |  |  |  |

|                      |                        | LMX2352    | Prescaler = 16 (Note 3)                 | 0.5  |      | 1.2             | GHz      |  |  |  |

|                      |                        |            | Prescaler = 8 (Note 3)                  | 0.25 |      | 0.5             | GHz      |  |  |  |

| f <sub>in</sub> IF   | IF Operating Frequency |            |                                         | 10   |      | 550             | MHz      |  |  |  |

| fosc                 | Oscillator Frequency   |            | No load on OSCx (Note 3)                | 2    |      | 50              | MHz      |  |  |  |

|                      |                        |            | With resonator load on OSCx (Note 3)    | 2    |      | 20              | MHz      |  |  |  |

| fφ                   | Phase Detector Frequen | су         | RF and IF                               |      |      | 10              | MHz      |  |  |  |

| Pf <sub>in RF</sub>  | RF Input Sensitivity   |            | V <sub>CC</sub> = 3.0V                  | -15  |      | 0               | dBm      |  |  |  |

|                      |                        |            | V <sub>CC</sub> = 5.0V                  | -10  |      | 0               | dBm      |  |  |  |

| Pf <sub>in IF</sub>  | IF Input Sensitivity   |            | 2.7 V≤V <sub>CC</sub> ≤ 5.5V            | -10  |      | 0               | dBm      |  |  |  |

| Vosc                 | Oscillator Sensitivity |            | OSCin, OSCx                             | 0.5  |      | V <sub>cc</sub> | $V_{PP}$ |  |  |  |

**Electrical Characteristics** ( $V_{cc_{RF}} = V_{cc_{IF}} = V_{P_{RF}} = V_{P_{IF}} = 3.0V$ ; -40° C <  $T_A$ < 85° C except as specified) (Continued)

| Symbol                                                  | Parameter                             | Conditions                                         |                                       | Min                  | Тур  | Max     | Units |

|---------------------------------------------------------|---------------------------------------|----------------------------------------------------|---------------------------------------|----------------------|------|---------|-------|

| Charge Pun                                              | ıp                                    |                                                    |                                       |                      |      |         |       |

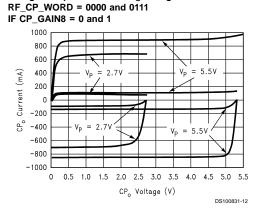

| ICPo- <sub>source</sub><br>RF                           | RF Charge Pump Output Current (see    | VCPo Vp/2, RF_CP_                                  | _WORD = 0000                          |                      | -100 |         | μΑ    |

| ICPo- <sub>sink RF</sub>                                | Programming                           | VCPo = Vp/2, RF_C                                  | P_WORD = 0000                         |                      | 100  |         | μA    |

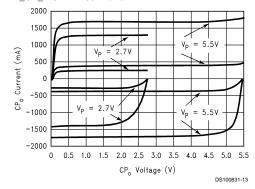

| CPo- <sub>source</sub>                                  | Description 3.2.2)                    | VCPo = Vp/2, RF_C                                  | P_WORD = 1111                         |                      | -1.6 |         | mA    |

| CPo- <sub>sink RF</sub>                                 | 1                                     | VCPo = Vp/2, RF_C                                  | P_WORD = 1111                         |                      | 1.6  |         | mA    |

| CPo- <sub>source</sub>                                  | IF Charge Pump Output<br>Current (see | VCPo = Vp/2, CP_G                                  | AIN_8 = 0                             |                      | -100 |         | μА    |

| CPo- <sub>sink IF</sub>                                 | Programming                           | VCPo = Vp/2, CP_G                                  | AIN_8 = 0                             |                      | 100  |         | μA    |

| CPo- <sub>source</sub>                                  | Description 3.1.4)                    | VCPo = Vp/2, CP_G                                  | AIN_8 = 1                             |                      | -800 |         | μА    |

| CPo- <sub>sink IF</sub>                                 | -                                     | VCPo = Vp/2, CP_G                                  | AIN_8 = 1                             |                      | 800  |         | μA    |

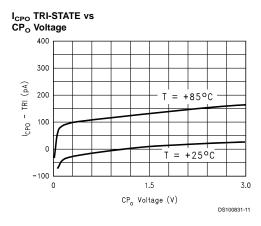

| CPo- <sub>Tri</sub>                                     | Charge Pump<br>TRI-STATE Current      | 0.5 ≤ VCPo ≤ Vp - 0<br>-40° C < TA < 85° (         |                                       | -2.5                 |      | 2.5     | nA    |

| ICPo- <sub>sink</sub><br>vs.<br>ICPo- <sub>source</sub> | CP Sink vs. Source<br>Mismatch        | VCPo = Vp/2<br>TA = 25° C                          | RFICPo<br>= 400 μA - 1.6 mA           |                      | 3    | 10      | %     |

| ICPo vs.<br>VCPo                                        | CP Current vs. Voltage                | 0.5 ≤ VCPo ≤ Vp -<br>0.5<br>T <sub>A</sub> = 25° C | RFICPo<br>= 800 μA - 1.6 mA           |                      | 8    | 15      | %     |

| CPo vs. T                                               | CP Current vs<br>Temperature          | VCPo = Vp/2<br>-40° C < TA < 85° (                 | · · · · · · · · · · · · · · · · · · · |                      | 8    |         | %     |

| Digital Inter                                           | face                                  |                                                    |                                       | •                    |      | •       |       |

| V <sub>IH</sub>                                         | High-level Input Voltage              | (Note 4)                                           |                                       | 0.8 Vcc              |      |         | V     |

| / <sub>IL</sub>                                         | Low-level Input Voltage               | (Note 4)                                           |                                       |                      |      | 0.2 Vcc | V     |

| IH                                                      | High-level Input Current              | $V_{IH} = V_{CC} = 5.5 \text{ V}, (N)$             | lote 4)                               | -1.0                 |      | 1.0     | μA    |

| IL                                                      | Low-level Input Current               | $V_{IL} = 0, V_{CC} = 5.5 V,$                      | (Note 4)                              | -1.0                 |      | 1.0     | μA    |

| IН                                                      | Oscillator Input Current              | $V_{IH} = V_{CC} = 5.5 V$                          |                                       |                      |      | 100     | μA    |

| IL                                                      | Oscillator Input Current              | $V_{IL} = 0, V_{CC} = 5.5 V$                       |                                       | -100                 |      |         | μΑ    |

| V <sub>OH</sub>                                         | High-level Output<br>Voltage          | I <sub>OH</sub> = -500 μA                          |                                       | V <sub>CC</sub> -0.4 |      |         | V     |

| V <sub>OL</sub>                                         | High-level Output<br>Voltage          | I <sub>OL</sub> = 500 μA                           |                                       |                      |      | 0.4     | V     |

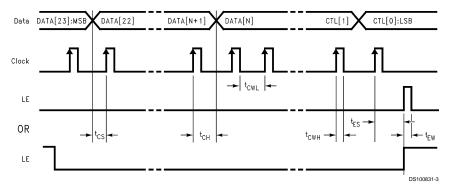

| MICROWIRE                                               | Timing                                |                                                    |                                       | •                    | •    | •       |       |

| cs                                                      | Data to Clock Setup<br>Time           | See Data Input Timir                               | 50                                    |                      |      | ns      |       |

| СН                                                      | Data to Clock Hold<br>Time            | See Data Input Timii                               | ng                                    | 10                   |      |         | ns    |

| CWH                                                     | Clock Pulse Width High                | See Data Input Timir                               | ng                                    | 50                   |      |         | ns    |

| CWL                                                     | Clock Pulse Width Low                 | See Data Input Timir                               | ng                                    | 50                   |      |         | ns    |

| Es                                                      | Clock to Load Enable<br>Set Up Time   | See Data Input Timii                               | ng                                    | 50                   |      |         | ns    |

| t <sub>EW</sub>                                         | Load Enable Pulse<br>Width            | See Data Input Timii                               | ng                                    | 50                   |      |         | ns    |

Note 3: Minimum operating frequencies are not production tested - only characterized.

Note 4: except fin, OSCin and OSCx

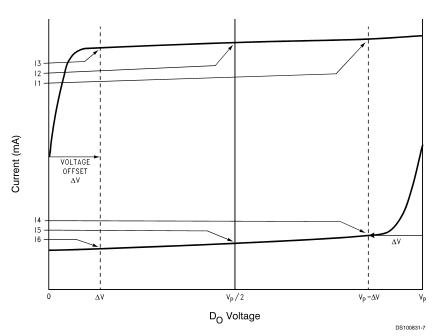

$$\begin{split} & \text{I1 = CP sink current at V}_{\text{Do}} = \text{Vp} - \Delta \text{V} \\ & \text{I2 = CP sink current at V}_{\text{Do}} = \text{Vp/2} \\ & \text{I3 = CP sink current at V}_{\text{Do}} = \Delta \text{V} \end{split}$$

I4 = CP source current at  $V_{Do}$  =  $Vp - \Delta V$

I5 = CP source current at V<sub>Do</sub> = Vp/2

I6 = CP source current at  $V_{Do} = \Delta V$   $\Delta V = Voltage$  offset from positive and negative rails. Dependent on VCO tuning range relative to  $V_{CC}$  and ground. Typical values are between 0.5V and 1.0V. Note 5:  $I_{D0}$  vs  $V_{D0}$  = Charge Pump Output Current magnitude variation vs Voltage =  $[\frac{1}{2}*{\{||1|-||3|\}}/[\frac{1}{2}*{\{||1|+||3|\}}]*100\%$  and  $[\frac{1}{2}*{\{||4|-||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{||4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}*{\{|4|+||6|\}}/[\frac{1}{2}$

||6|}] \* 100% Note 6:  $I_{Do\text{-sink}}$  vs  $V_{Do\text{-source}}$  = Charge Pump Output Current Sink vs Source Mismatch = [||2| - ||5|]/[1/2 \* {||2| + ||5|}] \* 100%

Note 7:  $I_{D_0}$  vs  $T_A$  = Charge Pump Output Current magnitude variation vs Temperature = [||2 @ temp| - ||2 @ 25°C||/||2 @ 25°C||\* 100% and [||5 @ temp| - ||5 @ 25°C||/||5 @ 25°C| \* 100%

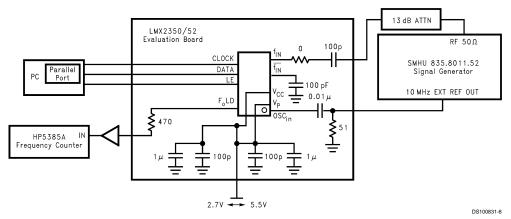

## **RF Sensitivity Test Block Diagram**

**Note:** N = 10,000 R = 50 P = 64

**Note:** Sensitivity limit is reached when the error of the divided RF output,  $F_0LD$ , is  $\geq 1$  Hz.

## **Typical Performance Characteristics**

Charge Pump Current vs CP<sub>O</sub> Voltage

## **Typical Performance Characteristics** (Continued)

# Charge Pump Current vs CP<sub>o</sub> Voltage RF\_CP\_WORD = 0011 and 1111

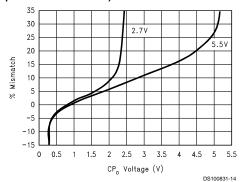

## Sink vs Source Mismatch (See (Note 6) under Charge Pump Current Specification Definitions)

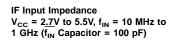

RF Input Impedance  $V_{CC} = 2.7V$  to 5.5V,  $f_{IN} = 50$  MHz to 3 GHz ( $f_{IN}$  Capacitor = 100 pF)

Marker 3 = 3 GHz, Real = 25, Imaginary = -32

Marker 3 = 3 GHz, Real = 246, Imaginary = -203

DS100831-15

Marker 1 = 100 MHz, Real = 461, Imaginary = -272

Marker 2 = 200 MHz, Real = 357, Imaginary = -238

Marker 3 = 300 MHz, Real = 290, Imaginary = -226

Marker 4 = 500 MHz, Real = 213, Imaginary = -191

DS100831-16

## **Typical Performance Characteristics** (Continued)

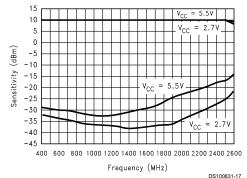

## LMX2350 RF Sensitivity vs Frequency

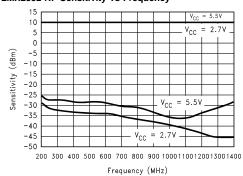

## LMX2352 RF Sensitivity vs Frequency

DS100831-18

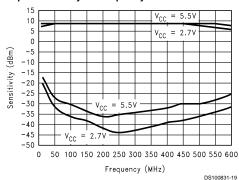

## IF Input Sensitivity vs Frequency

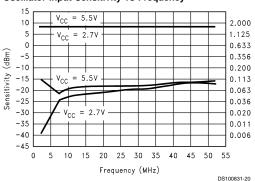

## Oscillator Input Sensitivity vs Frequency

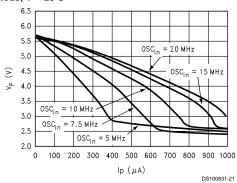

## LMX2350 V<sub>P</sub> Voltage vs V<sub>P</sub> Load Current in Vdoubler Mode, T = 25°C

## **Functional Description**

#### 1.0 General

The basic phase-lock-loop (PLL) configuration consists of a high-stability crystal reference oscillator, a frequency synthesizer such as the National Semiconductor LMX2350/52, a voltage controlled oscillator (VCO), and a passive loop filter. The frequency synthesizer includes a phase detector, current mode charge pump, as well as programmable reference [R] and feedback [N] frequency dividers. The VCO frequency is established by dividing the crystal reference signal down via the R counter to obtain a frequency that sets the comparison frequency. This reference signal, fr, is then presented to the input of a phase/frequency detector and compared with another signal, fp, the feedback signal, which was obtained by dividing the VCO frequency down by way of the N counter and fractional circuitry. The phase/frequency detector's current source outputs pump charge into the loop filter, which then converts the charge into the VCO's control voltage. The phase/frequency comparator's function is to adjust the voltage presented to the VCO until the feedback signal's frequency (and phase) match that of the reference signal. When this 'phase-locked' condition exists, the RF VCO's frequency will be N+F times that of the comparison frequency, where N is the integer divide ratio and F is the fractional component. The fractional synthesis allows the phase detector frequency to be increased while maintaining the same frequency step size for channel selection. The division value N is thereby reduced giving a lower phase noise referred to the phase detector input, and the comparison frequency is increased allowing faster switching times.

## 1.1 Reference Oscillator Inputs

The reference oscillator frequency for the RF and IF PLL's is provided by either an external reference through the OSCin pin and OSCx pin, or an external crystal resonator across the OSCin and OSCx pins. OSCin/OSCx block can operate to 50MHz with an input sensitivity of 0.5Vpp. The OSC bit (see programming description 3.1.1), selects whether the oscillator input pins OSCin and OSCx drive the IF and RF R counters separately (Low) or by a common input signal path (Hi). The common OSC mode allows the user to form a local crystal oscillator circuit or drive the OSCin pin from an external signal source. When a crystal resonator is connected between OSCin and OSCx along with 2 external capacitors to form a crystal oscillator both reference chains are driven simultaneously. When a TCXO is connected only at the OSCin input pin and not at the OSCx pin, the TCXO drives both IF R counter and RF R counter. When configured as separate inputs, the OSCin pin drives the IF R counter while the OSCx drives the RF R counter. The inputs have a Vcc/2 input threshold and can be driven from an external CMOS or TTL

## 1.2 Reference Dividers (R Counters)

The RF and IF R Counters are clocked through the oscillator block either separately or in common. The maximum frequency is 50MHz. Both R Counters are 15 bit CMOS counters with a divide range from 3 to 32,767. (See programming description 3.1.3.)

## 1.3 Programmable Dividers (N Counters)

The RF and IF N Counters are clocked by the small signal fin RF and fin IF input pins respectively. The LMX2350 RF N counter is 19 bits with 15 bits integer divide and 4 bits fractional. The integer part is configured as a 5 bit A Counter and

a 10 bit B Counter. The LMX2350 is capable of operating from 500 MHz to 1.2 GHz with the 16/17 prescaler offering a continuous integer divide range from 272 to 16399, and 1.2 GHz to 2.5 GHz with the 32/33 prescaler offering a continuous integer divide range from 1056 to 32767. The LMX2352 RF N counter is 18 bits with 14 bits integer divide and 4 bits fractional. The integer part is configured as a 4 bit A Counter and a 10 bit B Counter. The LMX2352 is capable of operating from 250 MHz to 500 MHz with the 8/9 prescaler offering a continuous integer divide range from 72 to 8199, and 500MHz to 1.2 GHz with 16/17 prescaler offering a continuous integer divide range from 272 to 16383. The RF counters for the LMX2350 family also contain fractional compensation, programmable in either 1/15 or 1/16 modes. Both LMX2350 and LMX2352 IF N counters are 15 bit integer dividers configured with a 3 bit A Counter and a 12 bit B Counter offering a continuous integer divide range from 56 to 32,767 over the frequency range of 10 MHz to 550 MHz. The IF N counters do not include fractional compensation.

#### 1.3.1 Prescaler

The RF and IF inputs to the prescaler consist of fin and /fin; which are complimentary inputs to differential pair amplifiers. The complimentary inputs are internally coupled to ground with a 10 pF capacitor. These inputs are typically AC coupled to ground through external capacitors as well. The input buffer drives the A counter's ECL D-type flip flops in a dual modulus configuration. A 16/17 or 32/33 prescale ratio can be selected for the LMX2350, and the lower frequency LMX2352 provides 8/9 or 16/17 prescale ratios. The IF circuitry for both the LMX2350 and LMX2352 contain an 8/9 prescaler. The prescaler clocks the subsequent CMOS flipflop chain comprising the fully programmable A and B counters.

## 1.3.2 Fractional Compensation

The fractional compensation circuitry of the LMX2350 and LMX2352 RF dividers allow the user to adjust the VCO's tuning resolution in 1/16 or 1/15 increments of the phase detector comparison frequency. A 4 bit register is programmed with the fractions desired numerator, while another bit selects between fractional 15 and 16 modulo base denominator (see programming description 4.2.4). An integer average is accomplished by using a 4 bit accumulator. A variable phase delay stage compensates for the accumulated integer phase error, minimizing the charge pump duty cycle, and reducing spurious levels. This technique eliminates the need for compensation current injection in to the loop filter. Overflow signals generated by the accumulator are equivalent to 1 full VCO cycle, and result in a pulse swallow.

## 1.4 Phase/Frequency Detector

The RF and IF phase(/frequency) detectors are driven from their respective N and R counter outputs. The maximum frequency at the phase detector inputs is about 2 MHz for some high frequency VCO due to the minimum continuous divide ratio of the dual modulus prescaler (i.e. If the VCO output frequency is 2.4816 GHz, the maximum phase detector input frequency is 2.35 MHz because the minimum continuous divide ratio of the LMX2350 with 32/33 prescaler is 1056). The phase detector outputs control the charge pumps. The polarity of the pump-up or pump-down control is programmed using RF\_PD\_POL or IF\_PD\_POL depending on whether RF/IF VCO characteristics are positive or negative (see programming descriptions 3.1.4 and 3.2.2). The phase detector also receives a feedback signal from the charge pump, in order to eliminate dead zone.

## Functional Description (Continued)

#### 1.5 Charge Pump

The phase detector's current source outputs pump charge into an external loop filter, which then converts the charge into the VCO's control voltage. The charge pumps steer the charge pump output, CPo, to Vcc (pump-up) or ground (pump-down). When locked, CPo is primarily in a TRI-STATE® mode with small corrections. The RF charge pump output current magnitude is programmable from 100  $\mu A$  to 1.6 mA in 100  $\mu A$  steps as shown in table in programming description 3.2.2. The IF charge pump is set to either  $100\mu A$  or  $800\mu A$  levels using bit IF\_R [19] (see programming description 3.1.4).

#### 1.6 Voltage Doubler

The VpRF pin is normally driven from an external power supply over a range of Vcc to 5.5v to provide current for the RF charge pump circuit. An internal voltage doubler circuit connected between the Vcc and VpRF supply pins alternately allows Vcc = 3v (± 10%) users to run the RF charge pump circuit at close to twice the Vcc power supply voltage. The voltage doubler mode is enabled by setting the V2\_EN bit (RF\_R [22]) to a HIGH level. The voltage doubler's charge pump driver originates from the RF oscillator input (OSCx). The device will not totally powerdown until the V2\_EN bit is programmed low. The average delivery current of the doubler is less than the instantaneous current demand of the RF charge pump when active and is thus not capable of sustaining a continuous out of lock condition. A large external capacitor connected to  $\ensuremath{\text{Vp}_{\text{RF}}}$  is therefore needed to control power supply droop when changing frequencies. Refer to the application note AN-1119 for more details.

#### 1.7 MICROWIRE™ Serial Interface

The programmable functions are accessed through the MI-CROWIRE serial interface. The interface is made of 3 functions: clock, data and latch enable (LE). Serial data for the various counters is clocked in from data on the rising edge of clock, into the 24- bit shift register. Data is entered MSB first. The last two bits decode the internal register address. On the rising edge of LE, data stored in the shift register is loaded into one of the 4 appropriate latches (selected by address bits). A complete programming description is included in the following sections.

## 1.8 Fo/LD Multifunction Output

The Fo/LD output pin can deliver several internal functions including analog/digital lock detects, and counter outputs. See programming description 3.1.5 for more details.

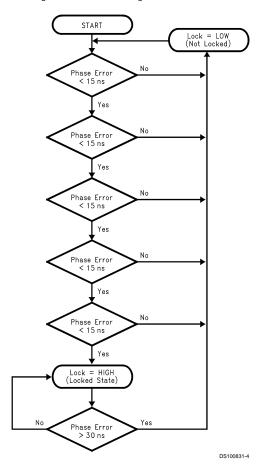

#### 1.8.1 Lock Detect

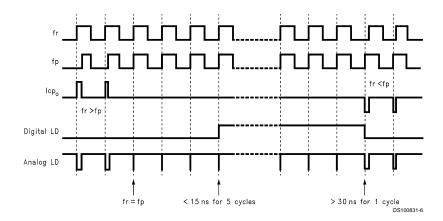

A digital filtered lock detect function is included with each phase detector through an internal digital filter to produce a logic level output available on the Fo/LD output pin if selected. The lock detect output is high when the error between the phase detector inputs is less than 15 nsec for 5 consecutive comparison cycles. The lock detect output is low when the error between the phase detector outputs is more than 30 nsec for one comparison cycle. An analog lock detect signal is also selectable. The lock detect output is always low when the PLL is in power down mode. See programming descriptions 3.1.5, 4.6 - 4.8 for more details.

#### 1.9 Power Control

Each PLL is individually power controlled by device enable pins or MICROWIRE power down bits. The enable pins override the power down bits except for the V2\_EN bit. The RF\_EN pin controls the RF PLL; IF\_EN pin controls the IF PLL. When both pins are high, the power down bits determine the state of power control (see programming description 3.2.1.2). Activation of any PLL power down mode results in the disabling of the respective N counter and de-biasing of its respective Fin input (to a high impedance state). The R counter functionality also becomes disabled when the power down bit is activated. The reference oscillator block powers down and the OSCin pin reverts to a high impedance state when both RF and IF enable pins or power down bit's are asserted, unless the V2\_EN bit (RF\_R[22]) is high. Power down forces the respective charge pump and phase comparator logic to a TRI-STATE condition. A power down counter reset function resets both N and R counters. Upon powering up the N counter resumes counting in "close" alignment with the R counter (The maximum error is one prescaler cycle). The MICROWIRE control register remains active and capable of loading and latching in data during all of the power down modes.

## **Programming Description**

#### 2.0 INPUT DATA REGISTER

The descriptions below describe the 24-bit data register loaded through the MICROWIRE Interface. The data register is used to program the 15-bit IF\_R counter register, and the 15-bit RF\_R counter register, the 15-bit IF\_N counter register, and the 19-bit RF\_N counter register. The data format of the 24-bit data register is shown below. The control bits CTL [1:0] decode the internal register address. On the rising edge of LE, data stored in the shift register is loaded into one of the 4 appropriate latches (selected by address bits). Data is shifted in MSB first

| MSB         |   | LSB       |

|-------------|---|-----------|

| DATA [21:0] |   | CTL [1:0] |

| 23 2        | 1 | 0         |

#### 2.1 Register Location Truth Table

| CTL | [1:0] | DATA Location |

|-----|-------|---------------|

| 1   | 0     |               |

| 0   | 0     | IF_R register |

| 0   | 1     | IF_N register |

| 1   | 0     | RF_R register |

| 1   | 1     | RF_N register |

## 2.2 Register Content Truth Table

|      | Fire     | First Bit |    |     |                |      |    |                       | REGISTER BIT LOCATION       |    |    |    |    |      |     |     | Last Bit |   | it |   |   |   |   |

|------|----------|-----------|----|-----|----------------|------|----|-----------------------|-----------------------------|----|----|----|----|------|-----|-----|----------|---|----|---|---|---|---|

|      | 23       | 22        | 21 | 20  | 19             | 18   | 17 | 16                    | 15                          | 14 | 13 | 12 | 11 | 10   | 9 8 | 8 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |

| IF_R | OSC      | FRAC_16   | F  | OLD | oLD IF_CP_WORD |      |    | IF_R_CNTR             |                             |    |    |    |    |      |     |     | 0        | 0 |    |   |   |   |   |

| IF_N | IF_CTL   | _WORD     |    |     |                | CMOS |    | IF_NB_CNTR IF_NA_CNTR |                             |    |    |    |    |      |     | NTR | 0        | 1 |    |   |   |   |   |

| RF_R | DLL_MODE | V2_EN     |    | R   | RF_CP_WORD     |      |    |                       |                             |    |    |    | F  | RF_R | _CN | ITR |          |   |    |   |   | 1 | 0 |

| RF_N | RF_CTI   | L_WORD    |    |     | RF_NB_         |      |    |                       | B_CNTR RF_NA_CNTR FRAC_CNTR |    |    |    |    |      |     | ITR | 1        | 1 |    |   |   |   |   |

## 3.0 PROGRAMMABLE REFERENCE DIVIDERS

## 3.1 IF\_R Register

If the Control Bits (CTL [1:0]) are 0 0, when LE is transitioned high data is transferred from the 24-bit shift register into a latch which sets the IF PLL 15-bit R counter divide ratio. The divide ratio is programmed using the bits IF\_R\_CNTR as shown in table 3.1.3. The ratio must be  $\geq$  3. The IF\_CP\_WORD [1:0], programs the IF charge pump magnitude and polarity shown in 3.1.4. The OSC bit is used to enable the crystal oscillator mode. FoLD [2:0] is used to set the function of the Lock Detect output (pin 11), according to table 3.1.3.

| MSB |         |        |      |         |            |         |            |   | LSB |

|-----|---------|--------|------|---------|------------|---------|------------|---|-----|

| OSC | FRAC_16 | FoLD [ | 2:0] | IF_CP_\ | WORD [1:0] | IF_R_CI | NTR [14:0] | 0 | 0   |

| 23  | 22      | 21     | 19   | 18      | 17         | 16      | 2          | 1 | 0   |

## 3.1.1 OSC (IF\_R[23])

The OSC bit, IF\_R [23], selects whether the oscillator input pins OSCin and OSCx drive the IF and RF R counters separately or by a common input signal path. When the OSC bit = 1, a crystal resonator can be connected between OSCin and OSCx together with 2 capacitors to form a crystal oscillator. When OSC = 0, the OSCin pin drives the IF R counter while the OSCx drives the RF R counter.

#### 3.1.2 FRAC\_16 (IF\_R[22])

The FRAC\_16 bit, IF\_R [22], is used to set the fractional compensation at either 1/16 and 1/15 resolution. When FRAC-16 is set to one, the fractional modulus is set to 1/16 resolution, and FRAC\_16 = 0 corresponds to 1/15 (See section 4.2.4).

## 3.1.3 15-BIT PROGRAMMABLE REFERENCE DIVIDER RATIO (R COUNTER)

(IF\_R[2]-[16])

|              | IF_R_CNTR/RF_R_CNTR |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------|---------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Divide Ratio | 14                  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 3            | 0                   | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4            | 0                   | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| -            | -                   | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | - |

| 32,767       | 1                   | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Notes: Divide ratio: 3 to 32,767 (Divide ratios less than 3 are prohibited). RF\_R\_CNTR/IF\_R\_CNTR These bits select the divide ratio of the programmable reference dividers.

## 3.1.4 IF\_CP\_WORD

(IF\_R[17]-[18])

| IF_CP_WORD | (IF_R [17] - [18] ) |

|------------|---------------------|

| CP_GAIN_8  | IF_PD_POL           |

| BIT       | LOCATION  | FUNCTION                    | 0        | 1        |

|-----------|-----------|-----------------------------|----------|----------|

| CP_GAIN_8 | IF_R [18] | IF Charge Pump Current Gain | 1X       | 8X       |

| IF_PD_POL | IF_R [17] | IF Phase Detector Polarity  | Negative | Positive |

CP\_GAIN\_8 is used to toggle the IF charge pump current magnitude between 1x mode (100 uA typ) and 8x mode (800uA typ). IF\_PD\_POL is set to one when IF VCO characteristics are positive. When IF VCO frequency decreases with increasing control voltage IF\_PD\_POL should set to zero.

#### 3.1.5 FoLD\* Programming Truth Table

(IF\_R[19]-[21])

| FoLD  | Fo/LD OUTPUT STATE                        |

|-------|-------------------------------------------|

| 0 0 0 | IF and RF Analog Lock Detect (Open Drain) |

| 1 0 0 | IF Digital Lock Detect                    |

| 0 1 0 | RF Digital Lock Detect                    |

| 1 1 0 | IF and RF Digital Lock Detect             |

| 0 0 1 | IF R counter                              |

| 1 0 1 | IF N counter                              |

| 0 1 1 | RF R counter                              |

| 1 1 1 | RF N counter                              |

<sup>\*</sup>FoLD - Fout/Lock Detect PROGRAMMING BITS

## 3.2 RF\_R Register

If the Control Bits (CTL [1:0]) are 1 0, data is transferred from the 24-bit shift register into the RF\_R register latch which sets the RF PLL 15-bit R counter divide ratio. The divide ratio is programmed using the RF\_R\_CNTR word as shown in table 3.1.3. The divide ratio must be ≥ 3. The bits used to control the voltage doubler (V2\_EN) and RF Charge Pump (RF\_CP\_WORD) are detailed in 3.2.2.

| MSB      |       |                  |    |                  |   |   | LSB |

|----------|-------|------------------|----|------------------|---|---|-----|

| DLL_MODE | V2_EN | RF_CP_WORD [4:0] |    | RF_R_CNTR [14:0] |   | 1 | 0   |

| 23       | 22    | 21               | 17 | 16               | 2 | 1 | 0   |

## 3.2.1 (RF\_R [22 - 23])

| DLL_MODE | V2_EN |

|----------|-------|

| BIT      | LOCATION  | FUNCTION                            | 0        | 1       |

|----------|-----------|-------------------------------------|----------|---------|

| DLL_MODE | RF_R [23] | Delay Line Loop Calibration<br>Mode | Slow     | Fast    |

| V2_EN    | RF_R [22] | RF_Voltage Doubler Enable           | Disabled | Enabled |

<sup>1.</sup> V2\_EN bit when set high enables the voltage doubler for the RF Charge Pump supply.

## 3.2.2 RF\_CP\_WORD (RF\_R[17]-[21])

| CP_8X | CP_4X | CP_2X | CP_1X | RF_PD_POL |

|-------|-------|-------|-------|-----------|

RF\_PD\_POL ( RF\_R[17] ) should be set to one when RF VCO characteristics are positive. When RF VCO frequency decreases with increasing control voltage RF\_PD\_POL should be set to zero.

CP\_1x, CP\_2x, CP\_4x, and CP\_8x are used to step the RF Charge Pump output current magnitude from 100 uA to 1.6 mA in 100uA steps as shown in the table below.

## **RF Charge Pump Output Truth Table**

| ICPo uA (typ) | CP8x     | CP4x     | CP2x     | CP1x     |

|---------------|----------|----------|----------|----------|

|               | RF_R[21] | RF_R[20] | RF_R[19] | RF_R[18] |

| 100           | 0        | 0        | 0        | 0        |

| 200           | 0        | 0        | 0        | 1        |

| 300           | 0        | 0        | 1        | 0        |

| 400           | 0        | 0        | 1        | 1        |

| -             | -        | -        | -        | -        |

| 900           | 1        | 0        | 0        | 0        |

| -             | -        | -        | -        | -        |

| 1600          | 1        | 1        | 1        | 1        |

## 4.0 PROGRAMMABLE DIVIDERS (N COUNTERS)

#### 4.1 IF\_N Register

If the Control Bits (CTL [1:0]) are 01, data is transferred from the 24-bit shift register into the IF\_N register latch which sets the PLL 15 bit programmable N counter value and various control functions. The IF\_N counter consists of the 3-bit swallow counter (A counter), and the 12 bit programmable counter (B counter). Serial data format is shown below in tables 4.1.2 and 4.1.3. The divide ratio (IF\_NB\_CNTR) must be  $\geq$ 3. The divide ratio is programmed using the bits IF\_N\_CNTR as shown in tables 4.1.2 and 4.1.3. The divide ratio must be  $\geq$ 56. The CMOS [3:0] bits program the 2 CMOS outputs detailed in section 4.4.

| MSB            |      |        |       |          |            |                  |   |   | LSB |

|----------------|------|--------|-------|----------|------------|------------------|---|---|-----|

| IF_CTL_WORD [2 | 2:0] | CMOS [ | [3:0] | IF_NB_C1 | NTR [11:0] | IF_NA_CNTR [2:0] |   | 0 | 1   |

| 23             | 21   | 20     | 17    | 16       | 5          | 4                | 2 | 1 | 0   |

## 4.1.1 IF\_CTL\_WORD (IF\_R[21]-[23])

| MSB        |         | LSB       |  |

|------------|---------|-----------|--|

| IF_CNT_RST | PWDN_IF | PWDN_MODE |  |

Note: See section 4.2.1.2 for IF control word truth table.

DLL\_MODE bit should be set to one for normal usage.

## 4.1.2 3-BIT IF SWALLOW COUNTER DIVIDE RATIO (IF A COUNTER)

(IF\_N[2]-[4])

| Swallow Count | IF_NA_CNTR |   |   |  |  |  |  |

|---------------|------------|---|---|--|--|--|--|

| (A)           | 2          | 1 | 0 |  |  |  |  |

| 0             | 0          | 0 | 0 |  |  |  |  |

| 1             | 0          | 0 | 1 |  |  |  |  |

| -             | -          | - | - |  |  |  |  |

| 7             | 1          | 1 | 1 |  |  |  |  |

Note: Swallow Counter Value: 0 to 7

IF NB CNTR > IF NA CNTR

Minimum continuous count = 56 ( A=0, B=7)

## 4.1.3 12-BIT IF PROGRAMMABLE COUNTER DIVIDE RATIO (IF B COUNTER)

(IF\_N[5]-[16])

|              | IF_NB_CNTR |    |   |   |   |   |   |   |   |   |   |   |

|--------------|------------|----|---|---|---|---|---|---|---|---|---|---|

| Divide Ratio | 11         | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 3            | 0          | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4            | 0          | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| -            | -          | -  | - | - | - | - | - | - | - | - | - | - |

| 4,095        | 1          | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Note: Divide ratio: 3 to 4095 (Divide ratios less than 3 are prohibited)

IF\_NB\_CNTR ≥ IF\_NA\_CNTR

N divider continuous integer divide ratio 56 to 32,767.

## 4.2 RF\_N Register

If the control bits (CTL[2:0]) are 11, data is transferred from the 24-bit shift register into the RF\_N register latch which sets the RF PLL 19 bit programmable N counter register and various control functions. The RF N counter consists of the 5-bit swallow counter (A counter) the 10 bit programmable counter (B counter), and 4 bit fractional counter. Serial data format is shown below. The divide ratio (RF\_NB\_CNTR) must be  $\geq$ 3, and must be  $\geq$  the swallow counter value + 2; RF\_NB\_CNTR $\geq$  (RF\_NA\_CNTR+2).

| MSB                                |    |    |    |         |           |         |          |   | LSB |

|------------------------------------|----|----|----|---------|-----------|---------|----------|---|-----|

| RF_CTL_WORD [2:0] RF_NB_CNTR [9:0] |    |    |    | RF_NA_C | NTR [4:0] | FRAC_CO | NT [3:0] | 1 | 1   |

| 23                                 | 21 | 20 | 11 | 10      | 6         | 5       | 2        | 1 | 0   |

## 4.2.1.1 RF\_CTL\_WORD (RF\_N[21]-[23])

| MSB        | LSB     |           |  |

|------------|---------|-----------|--|

| RF_CNT_RST | PWDN_RF | PRESC_SEL |  |

#### 4.2.1.2 RF/IF Control Word Truth Table

| BIT                   |  | FUNCTION                 | FUNCTION 0                  |                            |  |

|-----------------------|--|--------------------------|-----------------------------|----------------------------|--|

| IF_CNT_RST/RF_CNT_RST |  | IF/RF counter reset      | Normal Operation            | Reset                      |  |

| PWDN_IF/PWDN_RF       |  | IF/RF power down         | Powered up                  | Powered down               |  |

| PWDN_MODE             |  | Power down mode select   | Asynchronous power down     | Synchronous power down     |  |

| PRESC LMX2350         |  | Prescaler Modulus select | 16/17                       | 32/33                      |  |

|                       |  |                          | (0.5 to 1.2 GHz operation)  | (1.2 to 2.5 GHz operation) |  |

| LMX2352               |  |                          | 8/9                         | 16/17                      |  |

|                       |  |                          | (0.25 to 0.5 GHz operation) | (0.5 to 1.2 GHz operation) |  |

The **Counter Reset** enable bit when activated allows the reset of both N and R counters. Upon powering up, the N counter resumes counting in "close" alignment with the R counter (the maximum error is one prescaler cycle).

Activation of the PLL **power down** bits result in the disabling of the respective N counter divider and de-biasing of its respective fin inputs (to a high impedance state). The respective R counter functionality also becomes disabled when the power down bit is activated. The OSCin pin reverts to a high impedance state when both RF and IF power down bits are asserted. Power down forces the respective charge pump

and phase comparator logic to a TRI-STATE condition. The MICROWIRE control register remains active and capable of loading and latching in data during all of the power down modes

Both synchronous and asynchronous power down modes are available with the LMX2350 family in order to adapt to different types of applications. The power down mode bit IF\_N[21] is used to select between synchronous and asynchronous power down. The MICROWIRE control register remains active and capable of loading and latching in data during all of the power down modes.

#### Synchronous Power down Mode

One of the PLL loops can be synchronously powered down by first setting the power down mode bit HIGH (IF\_N[21] = 1) and then asserting its power down bit (IF\_N[22] or RF\_N[22] = 1). The power down function is gated by the charge pump. Once the power down bit is loaded, the part will go into power down mode upon the completion of a charge pump pulse event

#### Asynchronous Power down Mode

One of the PLL loops can be asynchronously powered down by first setting the power down mode bit LOW (IF\_N[21] = 0) and then asserting its power down bit (IF\_N[22] or RF\_N[22] = 1). The power down function is NOT gated by the charge pump. Once the power down bit is loaded, the part will go into power down mode immediately.

**Prescaler select** is used to set the RF prescaler. The LMX2350 is capable of operating from 500 MHz to 1.2 GHz with the 16/17 prescaler, and 1.2 GHz to 2.5 GHz with the 32/33 prescaler selection. The LMX2352 is capable of operating from 250 MHz to 500 MHz with the 8/9 prescaler, and 500MHz to 1.2GHz with 16/17 prescaler selection.

# 4.2.2 5-BIT RF SWALLOW COUNTER DIVIDE RATIO (RF A COUNTER) (RF\_N[6]-[10])

| Swallow Count | RF_NA_CNTR |   |   |   |   |

|---------------|------------|---|---|---|---|

| (A)           | 4          | 3 | 2 | 1 | 0 |

| 0             | 0          | 0 | 0 | 0 | 0 |

| 1             | 0          | 0 | 0 | 0 | 1 |

| -             | -          | - | - | - | - |

| 31            | 1          | 1 | 1 | 1 | 1 |

Note: Swallow Counter Value LMX2350: 0 to 31; LMX2352: 0 to 15 RF NB CNTR ≥ RF NA CNTR + 2

# 4.2.3 10-BIT RF PROGRAMMABLE COUNTER DIVIDE RATIO (RF B COUNTER) (RF\_N[11]-[20])

| RF_NB_CNTR   |   |   |   |   |   |   |   |   |   |   |

|--------------|---|---|---|---|---|---|---|---|---|---|

| Divide Ratio | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 3            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| -            | - | - | - | - | - | - | - | - | - | - |

| 1,023        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Note: Divide ratio: 3 to 1023 (Divide ratios less than 3 are prohibited)

RF\_NB\_CNTR ≥ RF\_NA\_CNTR + 2

## 4.2.4 FRACTIONAL MODULUS ACCUMULATOR (FRAC CNTR)

#### (RF\_N[2]-[5])

| Fractiona  | Ratio (F)  | FRAC_CNTR |         |         |         |  |  |

|------------|------------|-----------|---------|---------|---------|--|--|

| Modulus 15 | Modulus 16 | RF_N[5]   | RF_N[4] | RF_N[3] | RF_N[2] |  |  |

| 0          | 0          | 0         | 0       | 0       | 0       |  |  |

| 1/15       | 1/16       | 0         | 0       | 0       | 1       |  |  |

| 2/15       | 2/16       | 0         | 0       | 1       | 0       |  |  |

| -          | -          | -         | -       | -       | -       |  |  |

| 14/15      | 14/16      | 1         | 1       | 1       | 0       |  |  |

| N/A        | 15/16      | 1         | 1       | 1       | 1       |  |  |

## 4.3 PULSE SWALLOW FUNCTION

fvco = [N + F] x [fosc / R]N = (P x B) + A

- F: Fractional ratio (contents of FRAC\_CNTR divided by the fractional modulus)

- fvco: Output frequency of external voltage controlled oscillator (VCO)

- B: Preset divide ratio of binary 10-bit programmable counter

- A: Preset value of binary 4 or 5-bit swallow counter (0  $\leq$  A  $\leq$  31 {RF}, 0  $\leq$  A  $\leq$  15 {IF}, A+2  $\leq$  B {RF}, A  $\leq$  B {IF})

- fosc: Output frequency of the external reference frequency oscillator

- R: Preset divide ratio of binary 15-bit programmable reference counter (3 to 16383)

- P: Preset modulus of dual modulus prescaler (LMX2350:RF P=16 or 32, IF P=8)

- (LMX2352:RF P=8 or 16, IF P=8)

## 4.4 CMOS (Programmable CMOS outputs) (IF\_N[17]-[20])

| MSB      | LSB  |       |       |

|----------|------|-------|-------|

| FastLock | TEST | OUT_1 | OUT_0 |

Note: Test bit is reserved and should be set to zero for normal usage.

## 4.4.1 Programmable CMOS Output Truth Table

| BIT      | LOCATION | FUNCTION                   | 0           | 1             |

|----------|----------|----------------------------|-------------|---------------|

| OUT_0    | IF_N[17] | OUT0 CMOS output pin level | LOW         | HIGH          |

|          |          | set                        |             |               |

| OUT_1    | IF_N[18] | OUT1 CMOS output pin level | LOW         | HIGH          |

|          |          | set                        |             |               |

| FastLock | IF_N[20] | FastLock mode select       | CMOS output | FastLock mode |

When the FastLock bit is set to one, **OUT\_0** and **OUT\_1** are don't care bits. FastLock mode utilizes the OUT0 and OUT1 output pins to synchronously switch between active low and TRI-STATE. The OUT0 = LOW state occurs whenever the RF loop's CP\_8X is selected HIGH while the FastLock bit is set HIGH (see programming description 3.2.2). The OUT0 pin reverts to TRI-STATE when the CP\_8X bit is LOW. Similarly for the IF loop, the synchronous activation of OUT1= LOW or TRI-STATE, is dependent on whether the CP\_GAIN\_8 is high or low respectively (see programming description 3.1.4).

## 4.5 SERIAL DATA INPUT TIMING

Note: Data shifted into register on clock rising edge. Data is shifted in MSB first.

TEST CONDITIONS: The Serial Data Input Timing is tested using a symmetrical waveform around Vcc/2. The test waveform has an edge rate of 0.6 V/nsec with amplitudes of 2.2V @ Vcc=2.7 V and 2.6V @ Vcc = 5.5 V.

## 4.6 LOCK DETECT DIGITAL FILTER

The Lock Detect Digital Filter compares the difference between the phase of the inputs of the phase detector to a RC generated delay of approximately 15nS. To enter the locked state (Lock = HIGH) the phase error must be less than the 15nS RC delay for 5 consecutive reference cycles. Once in lock (Lock = HIGH), the RC delay is changed to approximately 30nS. To exit the locked state (Lock = LOW), the phase error must become greater than the 30nS RC delay. When the PLL is in the power down mode, Lock is forced LOW. A flow chart of the digital filter is shown at right.

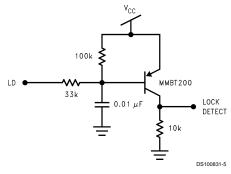

## 4.7 ANALOG LOCK DETECT FILTER

When the Fo/LD output is configured in analog lock detect mode an external lock detect circuit is needed in order to provide a steady LOW signal when the PLL is in the locked state. A typical circuit is shown below. The fold output is active low (open drain) only when analog lock detect mode is selected.

## 4.8 TYPICAL LOCK DETECT TIMING

## Physical Dimensions inches (millimeters) unless otherwise noted

Molded TSSOP, JEDEC Plastic Package (MTC24) Order Number LMX2350TM or LMX2352TM NS Package MTC24

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

Europe Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.