[查询LST62832供应商](#)

[捷多邦，专业PCB打样工厂，24小时加急出货](#)

**LinkSmart**

**LST62832

32K × 8

5 VOLT CMOS STATIC RAM**

**PRELIMINARY**

**A**

### **Revision history**

| Rev. No. | Approved date | History       | Remark (purpose) |

|----------|---------------|---------------|------------------|

| A        | Sep 10 2001   | Initial issue | Preliminary      |

**Features**

- High-speed: 70 ns

- Low DC operating current of 15mA

- Low Power Dissipation:

-TTL Standby: 3 mA (Max.)

-CMOS Standby: 20  $\mu$  A (Max.)

- Fully static operation

- All inputs and outputs directly compatible

- Three-state outputs

- Ultra low data retention current ( $V_{CC} = 2V$ )

- Single 5V  $\pm 10\%$  Power Supply

- Packages

-28-pin 600 mil PDIP

-28-pin 300 mil SOP

-28-pin 330 mil SOP

-28-pin TSOP(standard)

**Description**

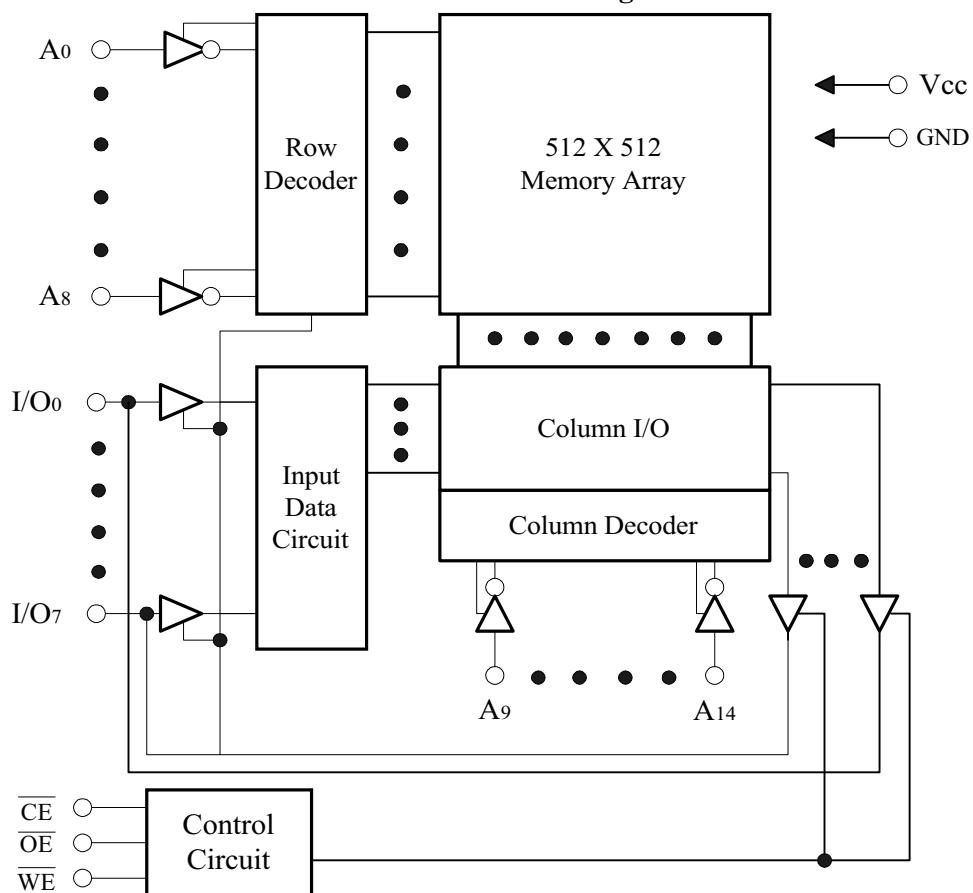

The LST62832 is a 262,144-bit static random access memory organized as 32,768 words by 8 bits. It is built with LinkSmart's high performance CMOS process. Inputs and three-state outputs are TTL compatible and allow for direct interfacing with common system bus structures.

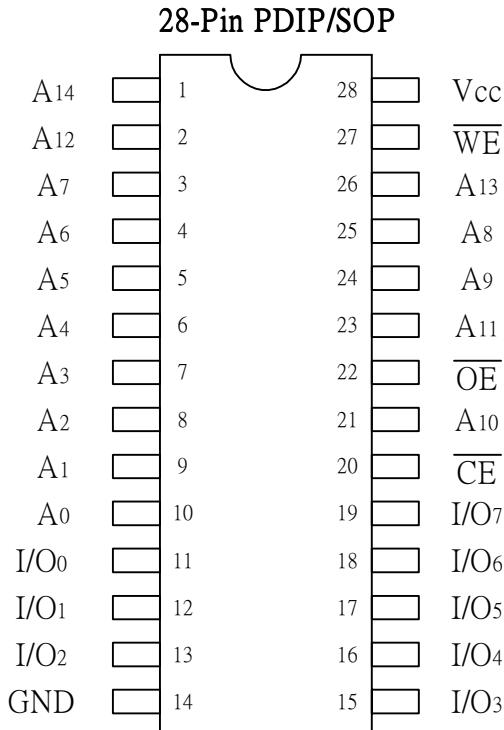

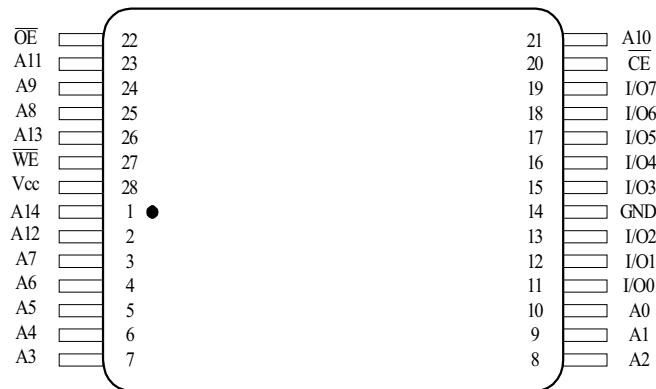

**Pin Configurations (Top View)****Functional Block Diagram**

**Pin Descriptions****A<sub>0</sub>-A<sub>14</sub> Address Inputs**

These 15 pins address inputs select one of the 32,768×8 bit segments data I/O in the RAM

**CE Chip Enable Inputs**

CE is an active LOW input. Chip Enable must be LOW when reading from or writing to the device. When HIGH, the device is in standby mode with I/O pins in the high impedance state.

**OE Output Enable Input**

The Output Enable input is active LOW. When OE is LOW with CE LOW and WE HIGH, data of the selected memory location will be available on the I/O pins. When OE is HIGH, the I/O pins will be in the high impedance state.

**WE****Write Enable Input**

An active LOW input, WE input controls read and write operations. When CE and WE inputs are both LOW, the data present on the I/O pins will be written into the selected memory location.

**I/O<sub>0</sub>-I/O<sub>7</sub> Data Input and Data Output Ports**

These 8 bi-directional ports are used to read data from and write data into the RAM.

**V<sub>CC</sub> Power Supply****GND Ground****28-Pin TSOP(Standard)**

### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Parameter                    | Commercial            | Industrial            | Units |

|-------------------|------------------------------|-----------------------|-----------------------|-------|

| V <sub>CC</sub>   | Supply Voltage               | -0.5 to +7            | -0.5 to +7            | V     |

| V <sub>IN</sub>   | Input Voltage                | -0.5 to +7            | -0.5 to +7            | V     |

| V <sub>DQ</sub>   | Input/output Voltage Applied | V <sub>CC</sub> + 0.5 | V <sub>CC</sub> + 0.5 | V     |

| T <sub>BIAS</sub> | Temperature Under Bias       | -10 to +125           | -65 to +135           | °C    |

| T <sub>STG</sub>  | Storage Temperature          | -65 to +150           | -65 to +150           | °C    |

**NOTE:**

- Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Capacitance

TA = 25°C, f = 1.0MHz

| Symbol           | Parameter          | Conditions           | Max | Unit |

|------------------|--------------------|----------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> =0V  | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>I/O</sub> =0V | 8   | pF   |

NOTE : This parameter is guaranteed by design and not tested

### Truth Table

| Mode    | $\overline{CE}$ | $\overline{OE}$ | $\overline{WE}$ | I/O Operation   |

|---------|-----------------|-----------------|-----------------|-----------------|

| Standby | H               | ×               | ×               | High-Z          |

| Read    | L               | L               | H               | DOUT            |

| Read    | L               | H               | H               | High-Z          |

| Write   | L               | ×               | L               | D <sub>IN</sub> |

NOTE: x=Don't Care, L=LOW, H=HIGH

### DC Electrical Characteristics (over all temperature ranges, V<sub>CC</sub>= 5V ± 10%)

| Symbol          | Parameter                          | Test Conditions                                                                            | Min. | Typ. | Max. | Units |

|-----------------|------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IL</sub> | Input LOW Voltage <sup>(1,2)</sup> |                                                                                            | -0.5 | -    | 0.8  | V     |

| V <sub>IH</sub> | Input HIGH Voltage <sup>(1)</sup>  |                                                                                            | 2.2  | -    | 6    | V     |

| I <sub>IL</sub> | Input Leakage Current              | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0V to V <sub>CC</sub>                             | -2   | -    | 2    | µA    |

| I <sub>OL</sub> | Output Leakage Current             | V <sub>CC</sub> = Max, $\overline{CE} = V_{IH}$ , V <sub>OUT</sub> = 0V to V <sub>CC</sub> | -2   | -    | 2    | µA    |

| V <sub>OL</sub> | Output LOW Voltage                 | V <sub>CC</sub> = Min, I <sub>OL</sub> = 2.1mA                                             | -    | -    | 0.4  | V     |

| V <sub>OH</sub> | Output HIGH Voltage                | V <sub>CC</sub> = Min, I <sub>OH</sub> = -1mA                                              | 2.4  | -    | -    | V     |

## **DC Electrical Characteristics, continued**

| Symbol           | Parameter                                                                                                           | Power | Com.(4) | Ind.(4) | Units   |    |

|------------------|---------------------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|----|

| I <sub>CC</sub>  | Average Operating Current, $\overline{CE} = V_{IL}$                                                                 | READ  | -       | 15      | 16      | mA |

|                  | Output Open, $V_{CC} = \text{Max.}$ , $f = 0$                                                                       | WRITE | -       | 40      | 50      |    |

| I <sub>CC1</sub> | Average Operating Current, $\overline{CE} \leq V_{IL}$ Output Open,<br>$V_{CC} = \text{Max.}$ , $f = f_{MAX}^{(3)}$ | -     | 60      | 70      | mA      |    |

| I <sub>SB</sub>  | TTL Standby Current<br>$\overline{CE} \geq V_{IH}$ , $V_{CC} = \text{Max.}$                                         | LL    | 3       | 4       | mA      |    |

| I <sub>SB1</sub> | CMOS Standby Current, $\overline{CE} \geq V_{CC} - 0.2V$ ,                                                          | L     | 60      | 70      | $\mu A$ |    |

|                  | $V_{IN} \geq V_{CC} - 0.2V$ or $V_{IN} \leq 0.2V$ , $V_{CC} = \text{Max.}$                                          | LL    | 20      | 30      |         |    |

---

**NOTES:**

1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

2.  $V_{IL}$  (Min.) = -3.0V for pulse width <20 ns.

3.  $f_{MAX} = 1/trc$ .

4. Maximum values.

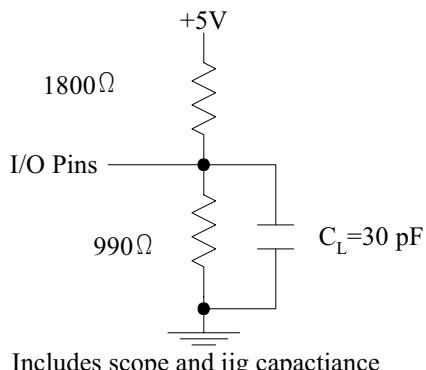

### AC Test Conditions

|                         |           |

|-------------------------|-----------|

| Input Pulse Levels      | 0 to 3V   |

| Input Rise Fall Times   | 3ns       |

| Timing Reference Levels | 1.5V      |

| Output Load             | See below |

## AC Test Loads and Waveforms

Includes scope and jig capacitance

## Key to Switching Waveforms

| Waveform | Inputs                           | Outputs                                   |

|----------|----------------------------------|-------------------------------------------|

|          | Must be steady                   | Will be steady                            |

|          | May change from H to L           | Will be changing from H to L              |

|          | May change from L to H           | Will be changing from L to H              |

|          | Don't care: any change permitted | Changing state unknown                    |

|          | Don't not apply                  | Center line is high impedance "OFF" state |

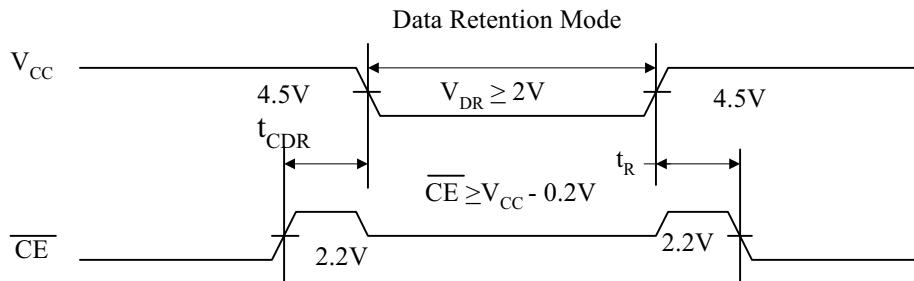

### Data Retention Characteristics

| Symbol     | Parameter                                                      | Min            | Typ. <sup>(2)</sup> | Max. | Units   |

|------------|----------------------------------------------------------------|----------------|---------------------|------|---------|

| $V_{DR}$   | $V_{CC}$ for Data Retention $\overline{CE} \geq V_{CC} - 0.2V$ | 2.0            | -                   | 5.5  | V       |

| $I_{CCDR}$ | Data Retention Current                                         | Com'I          | -                   | 0.5  | $\mu A$ |

|            | $V_{DR}=3.0V, \overline{CE} \geq V_{DR} - 0.2V$                | Ind.           | -                   | 2    |         |

| $t_{CDR}$  | Chip Deselect to Data Retention Time                           | 0              | -                   | -    | ns      |

| $t_R$      | Operation Recovery Time (see Retention Mode)                   | $t_{RC}^{(1)}$ | -                   | -    | ns      |

**Note:** 1.  $t_{RC}$ = Read Cycle Time

2.  $T_A = +25^\circ C$

### Low $V_{CC}$ Data Retention Waveform

**AC Electrical Characteristics**

(Over all temperature ranges)

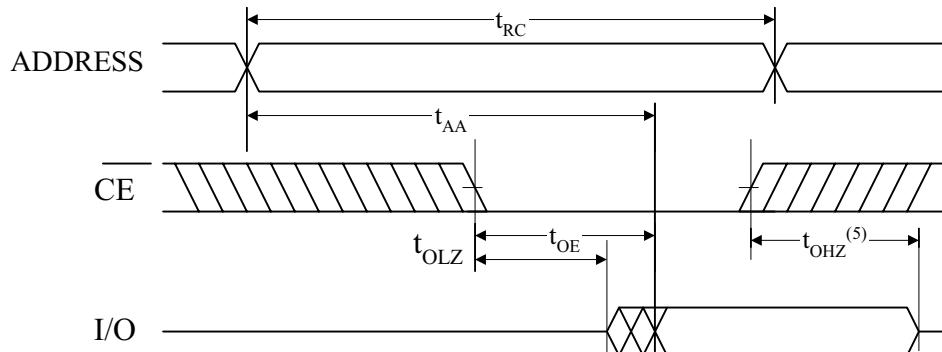

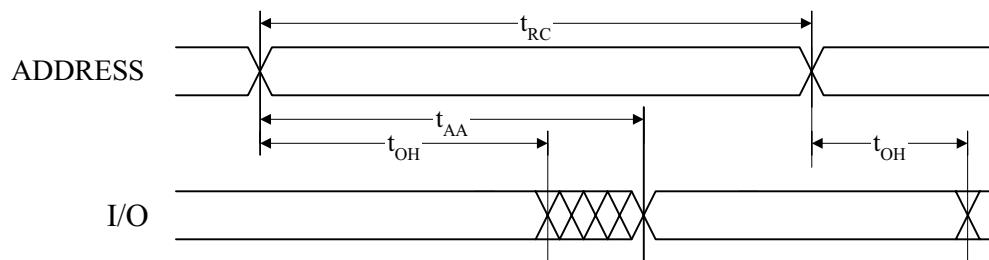

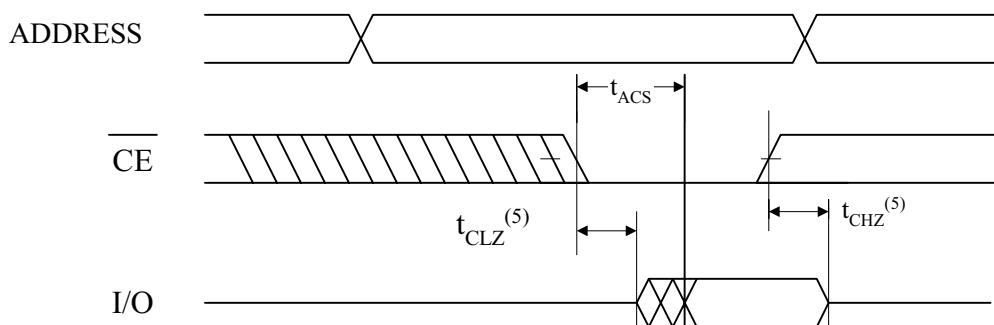

**Read Cycle**

| Parameter Name | Parameter                          | Min. | Max. | Unit |

|----------------|------------------------------------|------|------|------|

| $t_{RC}$       | Read Cycle Time                    | 70   | -    | ns   |

| $t_{AA}$       | Address Access Time                | -    | 70   | ns   |

| $t_{ACS}$      | Chip Enable Access Time            | -    | 70   | ns   |

| $t_{OE}$       | Output Enable to Output Valid      | -    | 30   | ns   |

| $t_{CLZ}$      | Chip Enable to Output in Low Z     | 5    | -    | ns   |

| $t_{OLZ}$      | Output Enable to Output in Low Z   | 5    | -    | ns   |

| $t_{CHZ}$      | Chip Disable to Output in High Z   | 0    | 20   | ns   |

| $t_{OHZ}$      | Output Disable to Output in High Z | 0    | 20   | ns   |

| $t_{OH}$       | Output Hold from Address Change    | 5    | -    | ns   |

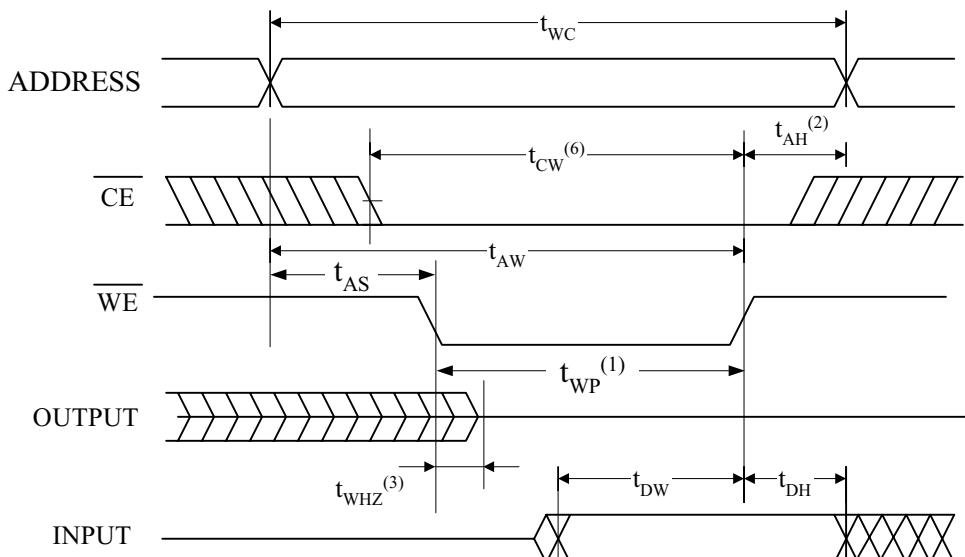

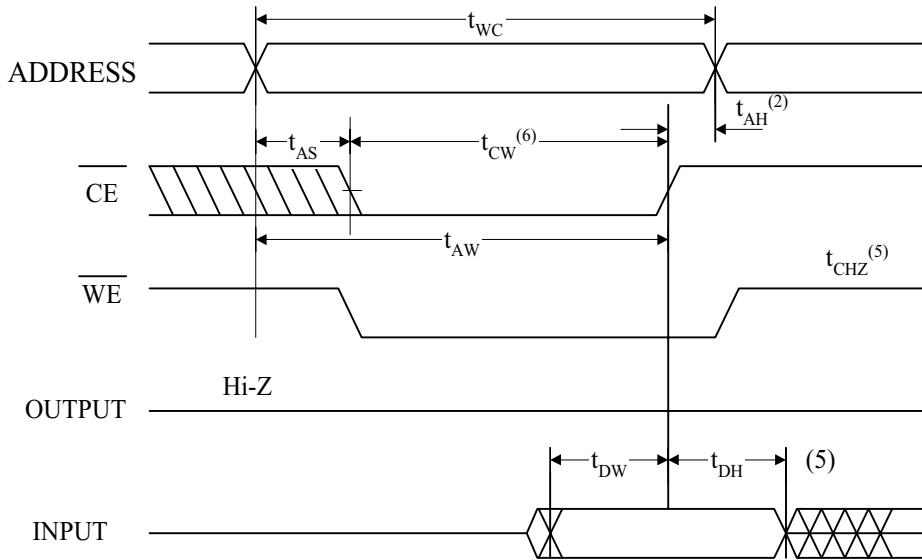

**Write Cycle**

| Parameter Name | Parameter                          | Min. | Max. | Unit |

|----------------|------------------------------------|------|------|------|

| $t_{WC}$       | Write Cycle Time                   | 70   | -    | ns   |

| $t_{CW}$       | Chip Enable to End of Write        | 60   | -    | ns   |

| $t_{AS}$       | Address Setup Time                 | 0    | -    | ns   |

| $t_{AW}$       | Address Valid to End of Write      | 60   | -    | ns   |

| $t_{WP}$       | Write Pulse Width                  | 50   | -    | ns   |

| $t_{WR}$       | Write Recovery Time                | 0    | -    | ns   |

| $t_{WHZ}$      | Write to Output High-Z             | 0    | 25   | ns   |

| $t_{DW}$       | Data Setup to End of Write         | 30   | -    | ns   |

| $t_{DH}$       | Data Hold from End of Write        | 0    | -    | ns   |

| $t_{OHZ}$      | Output Disable to Output in High Z | 0    | 30   | ns   |

| $t_{ow}$       | Output Active from End of Write    | 5    | -    | ns   |

**Switching Waveforms (read Cycle)**

**Read Cycle 1<sup>(1,2)</sup>**

**Read Cycle 2<sup>(1,2,4)</sup>**

**Read Cycle 3<sup>(1,3,4)</sup>**

**NOTES:**

1.  $\overline{WE} = V_{IH}$ .

2.  $CE = V_{IL}$ .

3. Address valid prior to or coincident with  $\overline{CE}$  transition LOW.

4.  $OE = V_{IL}$

5. Transition is measured  $\pm 500\text{mV}$  from steady state with  $C_L = 5\text{pF}$ . This parameter is guaranteed and not 100% tested.

**Switching Waveforms (Write Cycle)****Write Cycle 1( $\overline{WE}$  Controlled)<sup>(4)</sup>**

### Write Cycle 2 ( $\overline{CE}$ Controlled)<sup>(4)</sup>

#### NOTES:

1. The internal write time of the memory is defined by the overlap of  $\overline{CE}$  active and  $\overline{WE}$  low. Both signals must be active to initiate and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.

2.  $t_{WR}$  is measured from the earlier of  $\overline{CE}$  f or  $\overline{WE}$  going HIGH.

3. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

4.  $OE = V_{IL}$  or  $V_{IH}$ . However it is recommended to keep  $\overline{OE}$  at  $V_{IH}$  during write cycle to avoid bus contention.

5. If  $\overline{CE}$  is LOW during this period; I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.

6.  $t_{CW}$  is measured from  $\overline{CE}$  going LOW to the end of write.

**LinkSmart**

**LST62832

32K × 8

5 VOLT CMOS STATIC RAM**

**PRELIMINARY**

**A**

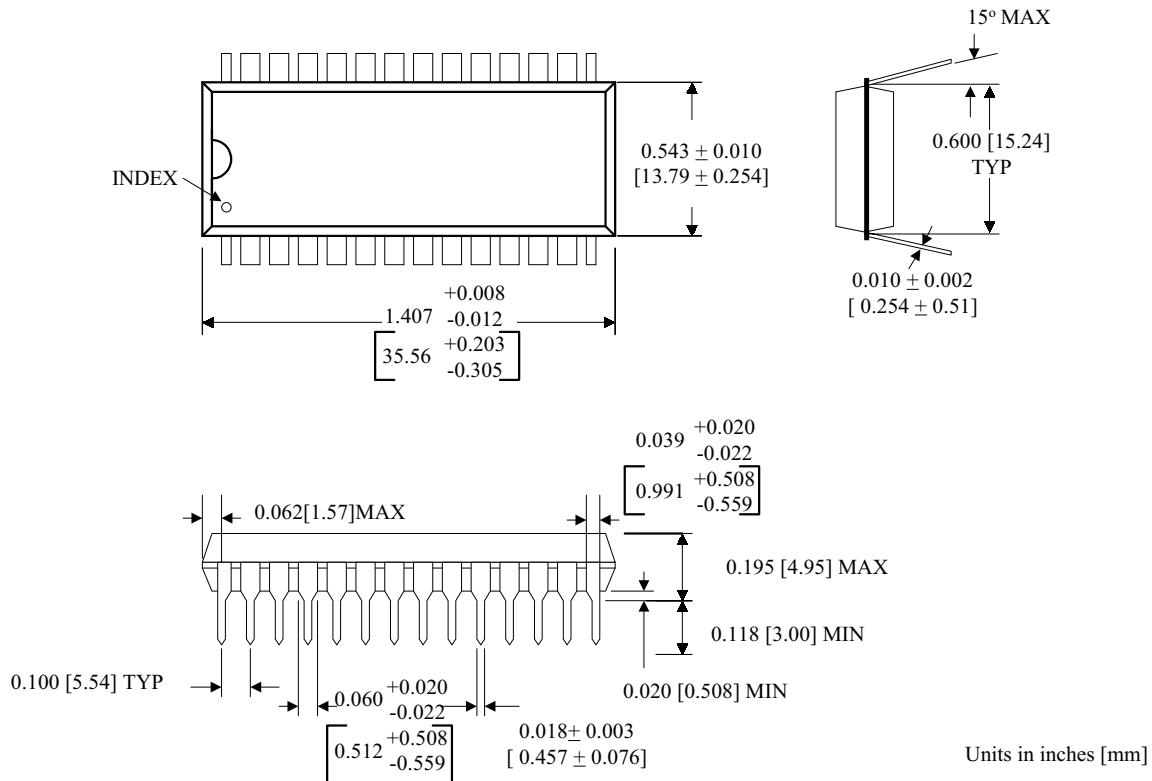

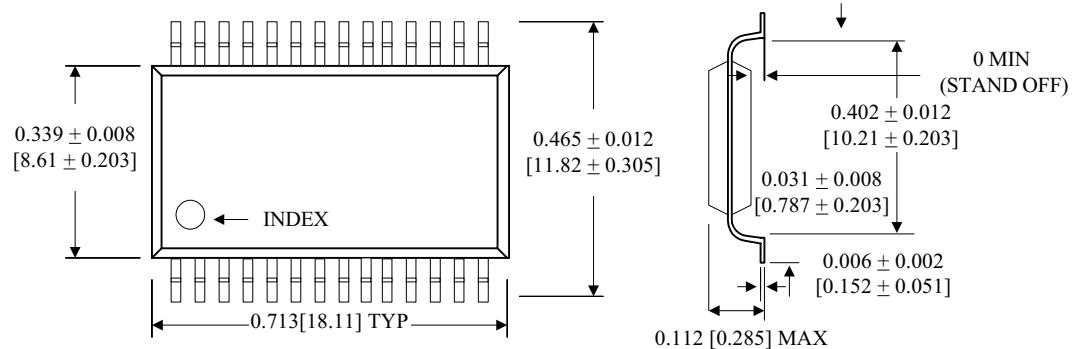

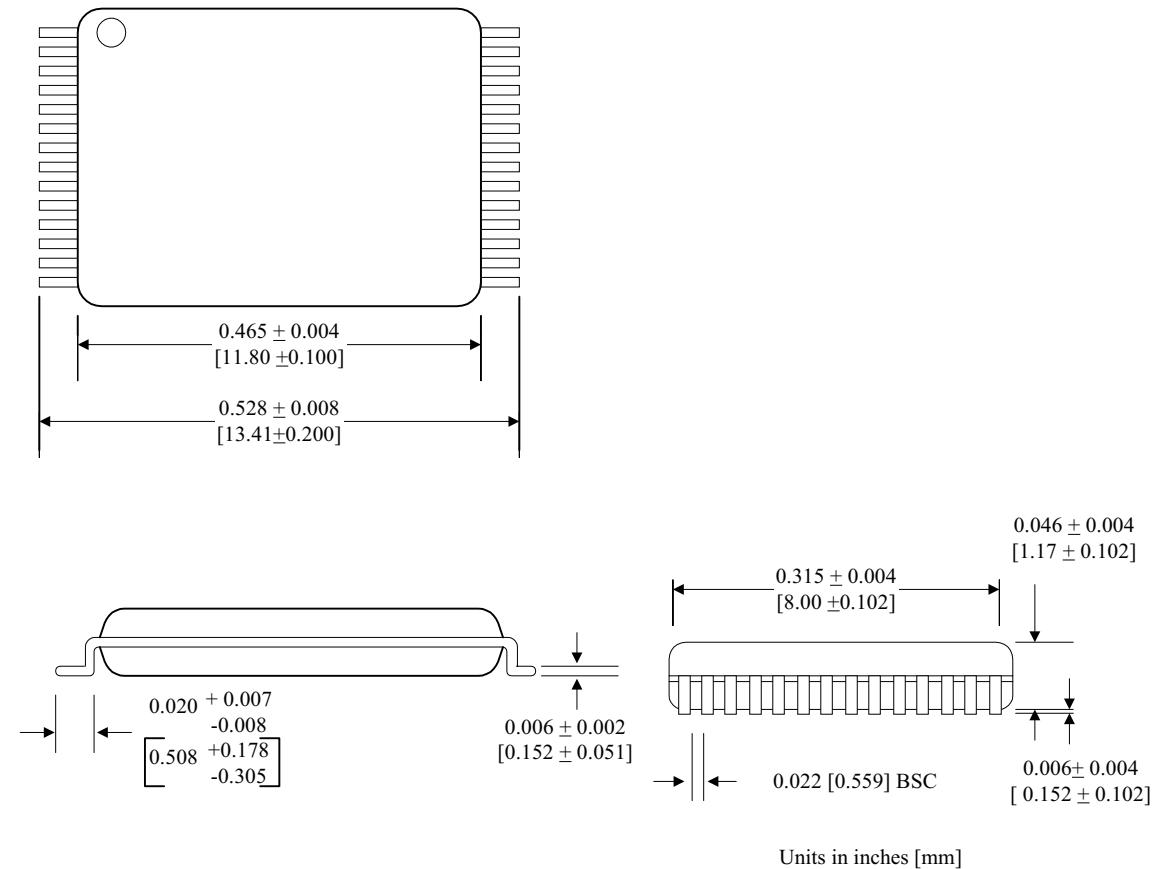

**Package diagram**

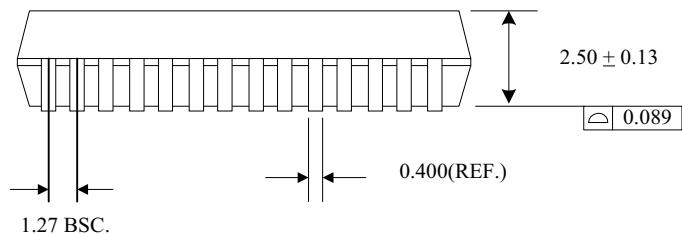

**28-pin 600 mil Plastic DIP**

*LinkSmart*

**LST62832

32K × 8

5 VOLT CMOS STATIC RAM**

**PRELIMINARY**

**A**

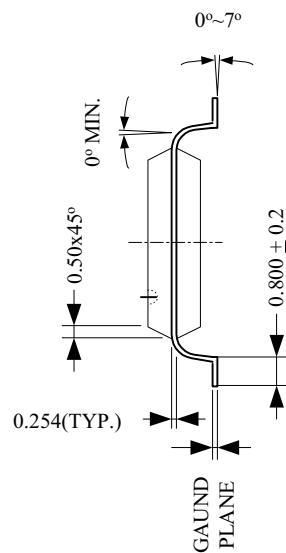

**28-pin 300 mil SOP**

Units : mm

*LinkSmart*

**LST62832

32K × 8

5 VOLT CMOS STATIC RAM**

**PRELIMINARY**

**A**

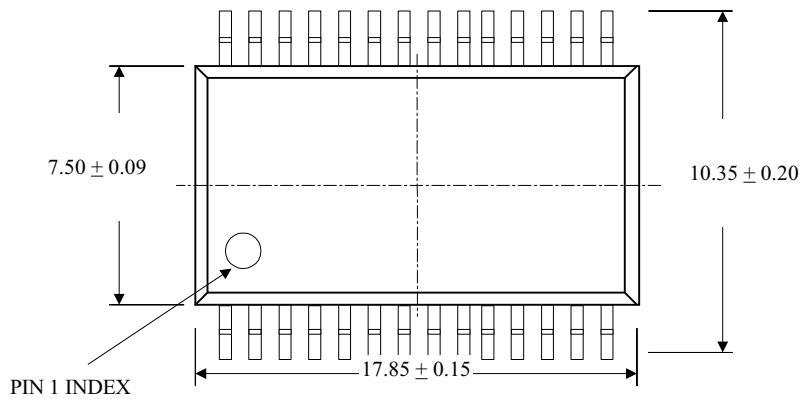

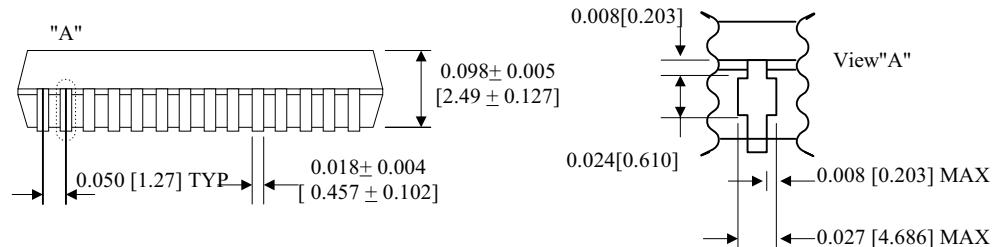

**28-pin 330 mil SOP**

**28-Pin TSOP 8\*13.4**

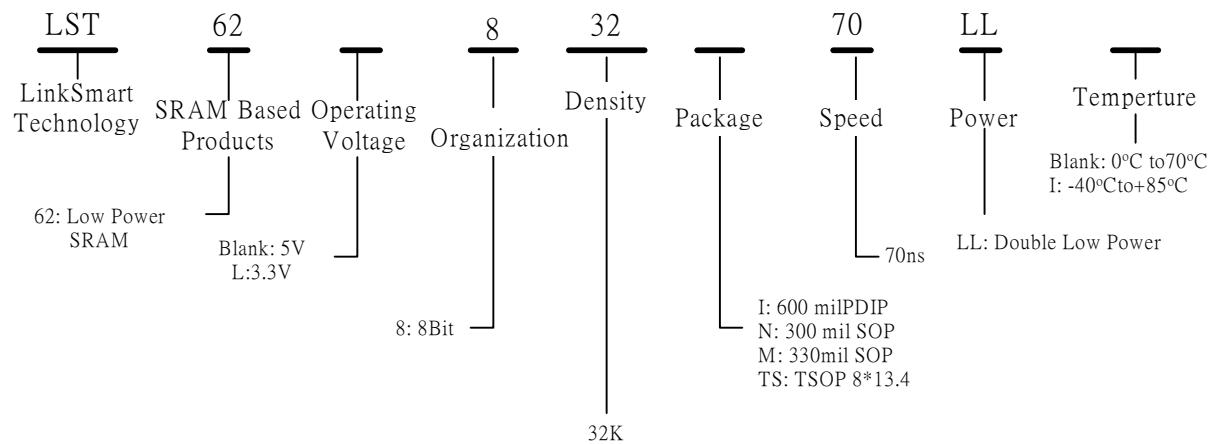

**Part Number Information**