Ordering number : EN5889

Monolithic Linear IC

# **Dolby Prologic Decoder**

## Overview

The LV1041M is a Dolby Prologic Surround signal-processing IC that implements in a single chip the functions of the Sanyo LV1016 and LA2786 ICs and a master volume control for the center and surround channels. This IC allows both systems of Dolby Prologic surround and digital surround to be formed into a single IC.

WW.DZSC.CO

#### **Features**

- Implements a Prologic surround decoder in a single chip.

- Wide dynamic range

- All modes can be controlled from control data transmitted serially over four lines: CLOCK, DATA, ENABLE, and ENABLE2. This function is compatible with the LV1016 and the LA2786.

### **Functions**

- · Adaptive matrix

- Center mode control (normal, phantom, wide)

- 4/3 channel logic control

- Auto-balance (on/off)

- Prologic off mode (bypass and full bypass)

- Center trim (0 to -31 dB in 1-dB steps)

- On-chip memory: (8K SRAM)

- Variable delay time: 15, 20, 25, 30, 40, or 50 ms (15, 20, 25, or 30 ms for Dolby Prologic surround)

- New A/D and D/A converter circuits adopted

- On-chip Dolby B noise reduction

- On-chip input and output filters

- Built-in V<sub>DD</sub> circuit

- Surround trim (0 to -31 dB in 1-dB steps)

- · Input and output muting functions

- Master volume control for the center and surround channels (0 to -44 dB in -2-dB steps, -44 to -76 dB in -4-dB steps, and muted)

Note \*: Dolby and the double D symbol are registered trademarks of the Dolby Laboratories Licensing Corporation. This IC can only be used by Dolby licensees. Licensing information and corresponding technical information is available from:Dolby Licensing Corporation

San Francisco, CA 94103-4813 USA

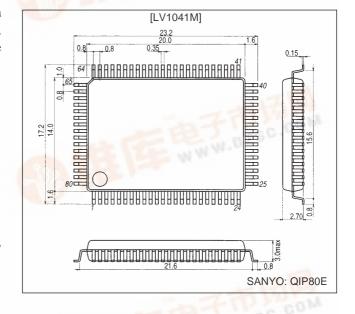

# **Package Dimensions**

unit: mm

3174-QFP80E

# **Specifications**

Maximum Ratings at  $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                                                                                | Ratings     | Unit |

|-----------------------------|---------------------|-------------------------------------------------------------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |                                                                                           | 12          | V    |

| Allowable power dissipation | Pd max              | Ta ≤ 70°C When mounted on a 114.3 × 76.1 × 1.6 mm fiberglass epoxy printed circuit board. | 1300        | mW   |

| Operating temperature       | Topr                |                                                                                           | -20 to +70  | °C   |

| Storage temperature         | Tstg                |                                                                                           | -40 to +150 | °C   |

### Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                      | Symbol               | Conditions | Ratings    | Unit  |

|--------------------------------|----------------------|------------|------------|-------|

| Recommended supply voltage     | V <sub>CC</sub>      |            | 9          | V     |

| Operating supply voltage range | V <sub>CC</sub> op   |            | 8 to 10    | V     |

| Input high-level voltage       | V <sub>IH</sub>      |            | 3.5 to 5.5 | V     |

| Input low-level voltage        | V <sub>IL</sub>      |            | 0 to 1.0   | V     |

| Dolby level                    | V <sub>O</sub> Dolby |            | 300        | mVrms |

### **Operating Conditions**

at Ta =  $25^{\circ}$ C,  $V_{CC}$  = 9 V,  $V_{IN}$  = 300 mV rms (left and right inputs),  $0.707 \times 300$  mV rms (center and surround inputs), f = 1 kHz, center trim = 0 dB, surround trim = 0 dB, delay time = 20 ms, in wide mode, and with the center and surround master volume set to 0 dB.

| Devenueton                                        | Symbol             | 0 155                                                    | Ratings |       |       | 11.3 |

|---------------------------------------------------|--------------------|----------------------------------------------------------|---------|-------|-------|------|

| Parameter                                         |                    | Conditions                                               | min     | typ   | max   | Unit |

| Quiescent current                                 | Icc                | No signal                                                |         | 80    | 110   | mA   |

| Center channel output level                       | V <sub>oc</sub>    | C input                                                  | -2      | 0     | +2    | dB   |

| Output level deviation                            | V <sub>OL</sub>    | L, R, Sch from Cch, matrix output                        | -0.5    | 0     | +0.5  | dB   |

| Matrix rejection (L)                              | R <sub>jL</sub>    | L input                                                  |         | -40   | -25   | dB   |

| Matrix rejection (C)                              | R <sub>jC</sub>    | C input                                                  |         | -40   | -25   | dB   |

| Matrix rejection (R)                              | R <sub>jR</sub>    | R input                                                  |         | -40   | -25   | dB   |

| Matrix rejection (S)                              | R <sub>jS</sub>    | S input                                                  |         | -40   | -25   | dB   |

| Total harmonic distortion (L)                     | THDL               | L 24-pin output                                          |         | 0.02  | 0.09  | %    |

| Total harmonic distortion (C)                     | THD <sub>C</sub>   | C 31-pin output                                          |         | 0.02  | 0.09  | %    |

| Total harmonic distortion (R)                     | THD <sub>R</sub>   | R 21-pin output                                          |         | 0.02  | 0.09  | %    |

| Total harmonic distortion (S)                     | THD <sub>S2</sub>  | S delay 33-pin output                                    |         | 0.1   | 0.7   | %    |

| Signal-to-noise ratio (L)                         | SN/L               | L 24-pin output, CCIR/ARM, $R_S = 10 \text{ k}\Omega$    |         | -76   | -71   | dB   |

| Signal-to-noise ratio (C)                         | SN/ <sub>C</sub>   | C 31-pin output, CCIR/ARM, $R_S = 10 \text{ k}\Omega$    |         | -77   | -71   | dB   |

| Signal-to-noise ratio (R)                         | SN/ <sub>R</sub>   | R 21-pin output, CCIR/ARM, $R_S = 10 \text{ k}\Omega$    |         | -76   | -71   | dB   |

| Signal-to-noise ratio (S)                         | SN/ <sub>S</sub>   | S delay 33-pin output                                    |         | -75   | -65   | dB   |

| Signal handling (L)                               | SHL                | L 24-pin output, V <sub>CC</sub> = 8.5 V, THD = 1%       | 15      | 16    |       | dB   |

| Signal handling (C)                               | SH <sub>C</sub>    | C 31-pin output, V <sub>CC</sub> = 8.5 V, THD = 1%       | 15      | 17    |       | dB   |

| Signal handling (R)                               | SH <sub>R</sub>    | R 21-pin output, V <sub>CC</sub> = 8.5 V, THD = 1%       | 15      | 16    |       | dB   |

| Signal handling (S)                               | SH <sub>S</sub>    | V <sub>CC</sub> = 8.5 V, THD = 3%, output 33-pin S delay | 15      | 16    |       | dB   |

| Noise sequencer output level                      | Vns                | Each matrix out                                          | 53      | 60    | 90    | mV   |

| Noise reduction frequency characteristics         | Dec1               | 0 dB, 1 kHz                                              | -1.5    | 0.0   | +1.5  | dB   |

|                                                   | Dec2               | –20 dB, 1 kHz                                            | -24.0   | -22.5 | -21.0 | dB   |

|                                                   | Dec3               | 0 dB, 5 kHz                                              | -1.5    | 0.0   | +1.5  | dB   |

|                                                   | Dec4               | –20 dB, 5 kHz                                            | -23.3   | -21.8 | -20.3 | dB   |

|                                                   | Dec5               | -40 dB, 5 kHz                                            | -46.8   | -45.3 | -43.8 | dB   |

| [Prologic Off Mode]                               |                    |                                                          |         |       |       |      |

| Left and right channels total harmonic distortion | THD <sub>OFF</sub> | L, R, 400 to 30 kHz BPF                                  |         | 0.01  | 0.03  | %    |

| Left and right channels signal-to-<br>noise ratio | S/N <sub>OFF</sub> | L, R, CCIR/ARM                                           |         | -90   | -80   | dB   |

| Left and right channels signal handling           | Shoff              | L, R, V <sub>CC</sub> = 8.5 V, THD = 1%                  | 15      | 16    |       | dB   |

| Master volume muting attenuation                  | V <sub>MUTE</sub>  | V <sub>IN</sub> = 1 Vrms                                 |         | -92   | -80   | dB   |

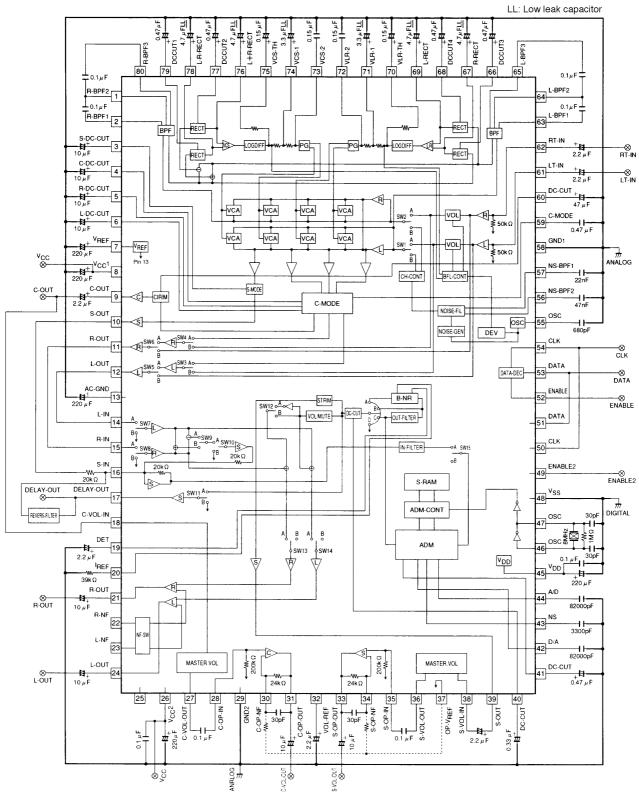

#### **Sample Application Circuit**