# LZ23J3V

## DESCRIPTION

The LZ23J3V is a 1/2.7-type (6.72 mm) solid-state image sensor that consists of PN photo-diodes and CCDs (charge-coupled devices). With approximately 1 310 000 pixels (1 344 horizontal x 971 vertical), the sensor provides a stable high-resolution color image.

## **FEATURES**

• Optical size: 6.72 mm (aspect ratio 4:3)

Interline scan format

Square pixel

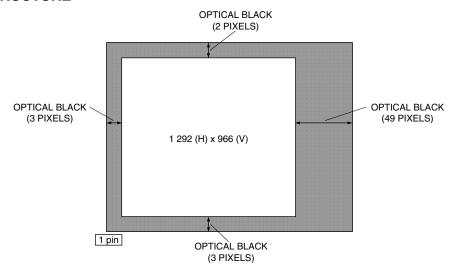

Number of effective pixels: 1 292 (H) x 966 (V)

Number of optical black pixels

Horizontal: 3 front and 49 rearVertical: 3 front and 2 rear

· Number of dummy bits

Horizontal: 28Vertical: 2

• Pixel pitch : 4.2 μm (H) x 4.2 μm (V)

• R, G, and B primary color mosaic filters

Supports monitoring mode

Low fixed-pattern noise and lag

· No burn-in and no image distortion

Blooming suppression structure

· Built-in output amplifier

- Built-in overflow drain voltage circuit and reset gate voltage circuit

- · Variable electronic shutter

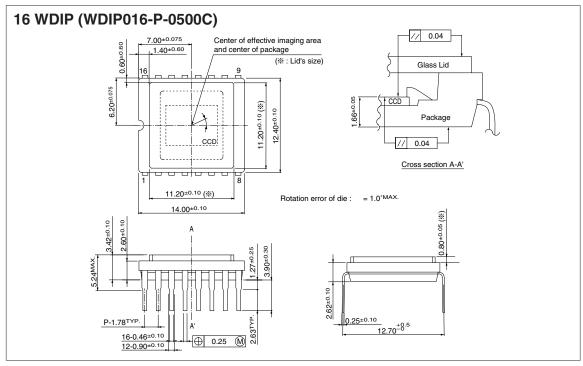

- Package :

16-pin shrink-pitch WDIP [Plastic] (WDIP016-P-0500C)

Row space: 12.70 mm

# 1/2.7-type Interline Color CCD Area Sensor with 1 310 k Pixels

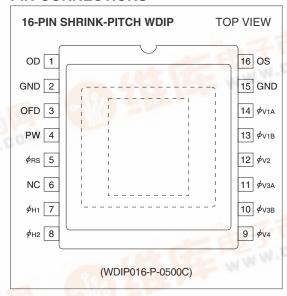

## PIN CONNECTIONS

#### **PRECAUTIONS**

- The exit pupil position of lens should be 15 to 50 mm from the top surface of the CCD.

- Refer to "PRECAUTIONS FOR CCD AREA SENSORS" for details.

# **PIN DESCRIPTION**

| SYMBOL                           | PIN NAME                        |  |  |  |  |

|----------------------------------|---------------------------------|--|--|--|--|

| OD                               | Output transistor drain         |  |  |  |  |

| OS                               | Output signals                  |  |  |  |  |

| <b>¢</b> RS                      | Reset transistor clock          |  |  |  |  |

| φν1Α, φν1Β, φν2, φν3Α, φν3Β, φν4 | Vertical shift register clock   |  |  |  |  |

| φH1, φH2                         | Horizontal shift register clock |  |  |  |  |

| OFD                              | Overflow drain                  |  |  |  |  |

| PW                               | P-well                          |  |  |  |  |

| GND                              | Ground                          |  |  |  |  |

| NC                               | No connection                   |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

(TA = +25 °C)

| PARAMETER                                            | SYMBOL                                         | RATING          | UNIT | NOTE |

|------------------------------------------------------|------------------------------------------------|-----------------|------|------|

| Output transistor drain voltage                      | Vod                                            | 0 to +18        | V    |      |

| Overflow drain voltage                               | Vofd                                           | Internal output | V    | 1    |

| Reset gate clock voltage                             | V∳RS                                           | Internal output | V    | 2    |

| Vertical shift register clock voltage                | VφV                                            | Vpw to +18      | V    |      |

| Horizontal shift register clock voltage              | V∳H                                            | -0.3 to +12     | V    |      |

| Voltage difference between P-well and vertical clock | Vpw-V∮v                                        | -29 to 0        | V    |      |

| Voltage difference between vertical clocks           | <b>V</b> <i>φ</i> <b>V-V</b> <i>φ</i> <b>V</b> | 0 to +17        | V    | 3    |

| Storage temperature                                  | Тѕтс                                           | -40 to +85      | °C   |      |

| Ambient operating temperature                        | Topr                                           | -20 to +70      | °C   |      |

- 1. Do not connect to DC voltage directly. When OFD is connected to GND, connect Vop to GND. Overflow drain clock is applied below 33 Vp-p.

- Do not connect to DC voltage directly. When ₱RS is connected to GND, connect Vop to GND. Reset gate clock is applied below 8 Vp-p.

- 3. When clock width is below 10 µs, and clock duty factor is below 0.1%, voltage difference between vertical clocks will be below 28 V.

# RECOMMENDED OPERATING CONDITIONS

| P                                       | ARAMETER               | SYMBOL                                         | MIN.      | TYP.  | MAX. | UNIT | NOTE |

|-----------------------------------------|------------------------|------------------------------------------------|-----------|-------|------|------|------|

| Ambient operating                       | temperature            | Topr                                           |           | 25.0  |      | °C   |      |

| Output transistor                       | drain voltage          | Vod                                            | 15.0      | 15.5  | 16.0 | V    |      |

| Overflow drain clock                    | p-p level              | V∳OFD                                          | 30.0      | 32.0  | V    | 1    |      |

| Ground                                  |                        | GND                                            | 0.0       |       | V    |      |      |

| P-well voltage                          |                        | VPW                                            | -10.0     |       | V∳VL | V    | 2    |

|                                         | LOW level              | V¢V1AL, V¢V1BL, V¢V2L<br>V¢V3AL, V¢V3BL, V¢V4L | -8.5      | -8.0  | -7.5 | ٧    |      |

| Vertical shift register clock           | INTERMEDIATE level     | V¢V1AI, V¢V1BI, V¢V2I<br>V¢V3AI, V¢V3BI, V¢V4I |           | 0.0   |      | ٧    |      |

|                                         | HIGH level             | V¢∨1AH, V¢∨1BH<br>V¢∨3AH, V¢∨3BH               | 15.0      | 15.5  | 16.0 | V    |      |

| Horizontal shift                        | LOW level              | evel Vøhll, Vøhll                              |           | 0.0   | 0.05 | V    |      |

| register clock                          | HIGH level             | VøH1H, VøH2H                                   | V∳H2H 4.5 |       | 5.5  | V    |      |

| Reset gate clock p-p level              |                        | V∳RS                                           | 4.5       | 5.0   | 5.5  | V    | 1    |

| Vertical shift register clock frequency |                        | føV1A, føV1B, føV2<br>føV3A, føV3B, føV4       |           | 7.87  |      | kHz  |      |

| Horizontal shift re                     | gister clock frequency | føH1, føH2                                     |           | 12.27 |      | MHz  |      |

| Reset gate clock                        | requency               | f∳RS                                           |           | 12.27 |      | MHz  |      |

- 1. Use the circuit parameter indicated in "SYSTEM CONFIGURATION EXAMPLE", and do not connect to DC voltage directly.

- 2. VPw is set below V / VL that is low level of vertical shift register clock, or is used with the same power supply that is connected to VL of V driver IC.

- \* To apply power, first connect GND and then turn on Vop. After turning on Vop, turn on PW first and then turn on other powers and pulses. Do not connect the device to or disconnect it from the plug socket while power is being applied.

## CHARACTERISTICS (Drive method: 1/30 s frame accumulation)

$(TA = +25 \, ^{\circ}C, Operating conditions : The typical values specified in "RECOMMENDED OPERATING CONDITIONS". Color temperature of light source : 3 200 K, IR cut-off filter (CM-500, 1 mmt) is used.)$

| PARAMETER                       | SYMBOL | MIN. | TYP. | MAX. | UNIT | NOTE |

|---------------------------------|--------|------|------|------|------|------|

| Standard output voltage         | Vo     |      | 150  |      | mV   | 2    |

| Photo response non-uniformity   | PRNU   |      |      | 10   | %    | 3    |

| Saturation output voltage       | Vsat   | 470  | 550  |      | mV   | 4    |

| Saturation output voltage       | VSAI   | 340  | 420  |      | mV   | 5    |

| Dark output voltage             | Vdark  |      | 0.5  | 3.0  | mV   | 1, 6 |

| Dark signal non-uniformity      | DSNU   |      | 0.5  | 2.0  | mV   | 1, 7 |

| Sensitivity (green channel)     | R      | 140  | 200  |      | mV   | 8    |

| Smear ratio                     | SMR    |      | -75  | -65  | dB   | 9    |

| Image lag                       | Al     |      |      | 1.0  | %    | 10   |

| Blooming suppression ratio      | ABL    | 500  |      |      |      | 11   |

| Output transistor drain current | lod    |      | 4.0  | 8.0  | mA   |      |

- Within the recommended operating conditions of Vod, Vofd of the internal output satisfies with ABL larger than 500 times exposure of the standard exposure conditions, and VsAT larger than 340 mV.

- 1.  $TA = +60 \, ^{\circ}C$

- The average output voltage of G signal under uniform illumination. The standard exposure conditions are defined as when Vo is 150 mV.

- 3. The image area is divided into 10 x 10 segments under the standard exposure conditions. Each segment's voltage is the average output voltage of all pixels within the segment. PRNU is defined by (Vmax – Vmin)/Vo, where Vmax and Vmin are the maximum and minimum values of each segment's voltage respectively.

- 4. The image area is divided into 10 x 10 segments. Each segment's voltage is the average output voltage of all pixels within the segment. VSAT is the minimum segment's voltage under 10 times exposure of the standard exposure conditions. The operation of OFDC is high. (for still image capturing)

- 5. The image area is divided into 10 x 10 segments. Each segment's voltage is the average output voltage of all pixels within the segment. VSAT is the minimum segment's voltage under 10 times exposure of the standard exposure conditions. The operation of OFDC is low.

- The average output voltage under non-exposure conditions.

- The image area is divided into 10 x 10 segments under non-exposure conditions. DSNU is defined by (Vdmax – Vdmin), where Vdmax and Vdmin are the maximum and minimum values of each segment's voltage respectively.

- The average output voltage of G signal when a 1 000 lux light source with a 90% reflector is imaged by a lens of F4, f50 mm.

- 9. The sensor is exposed only in the central area of V/10 square with a lens at F4, where V is the vertical image size. SMR is defined by the ratio of the output voltage detected during the vertical blanking period to the maximum output voltage in the V/10 square.

- 10. The sensor is exposed at the exposure level corresponding to the standard conditions. All is defined by the ratio of the output voltage measured at the 1st field during the non-exposure period to the standard output voltage.

- 11. The sensor is exposed only in the central area of V/10 square, where V is the vertical image size. ABL is defined by the ratio of the exposure at the standard conditions to the exposure at a point where blooming is observed.

# **PIXEL STRUCTURE**

# **COLOR FILTER ARRAY**

Pin arrangement of the vertical readout clock

| (1, 966)     |   |   |   |   |   |  |   |   |   |           |   | (1 292, 966) |

|--------------|---|---|---|---|---|--|---|---|---|-----------|---|--------------|

| <b>ф</b> VЗА | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>∮</b> V1B | R | G | R | G | R |  | G | R | G | R         | G |              |

| <b>ф</b> V3В | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>∳</b> V1A | R | G | R | G | R |  | G | R | G | R         | G |              |

| <b>ф</b> ∨за | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>∳</b> V1B | R | G | R | G | R |  | G | R | G | R         | G |              |

|              |   |   |   |   |   |  |   |   |   |           |   |              |

| <b>∕</b> ∨за | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>φ</b> V1B | R | G | R | G | R |  | G | R | G | R         | G |              |

| <b>ф</b> V3В | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>∳</b> V1A | R | G | R | G | R |  | G | R | G | R         | G |              |

| <b>ф</b> ∨за | G | В | G | В | G |  | В | G | В | G         | В |              |

| <b>∳</b> V1B | R | G | R | G | R |  | G | R | G | R         | G |              |

| (4.4)        |   |   |   |   |   |  |   |   |   | (1.000.1) |   |              |

(1, 1) (1 292, 1)

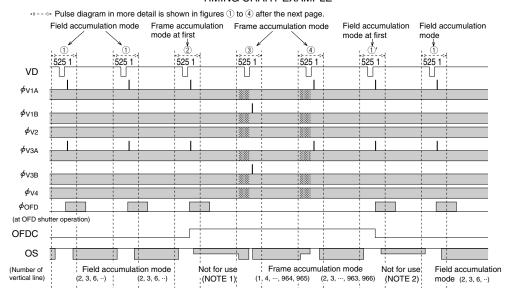

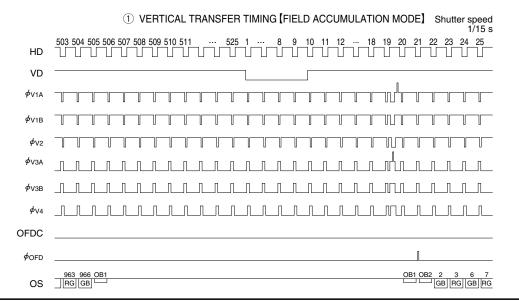

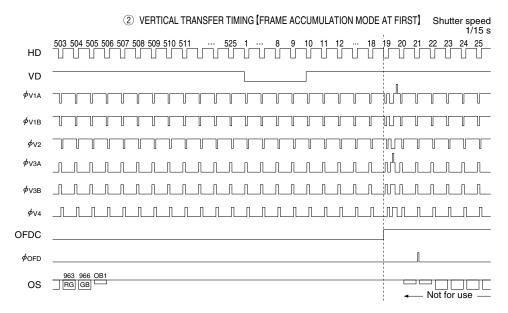

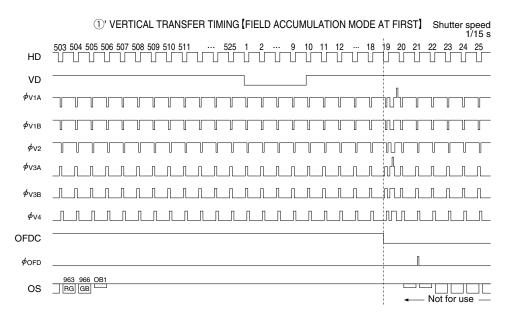

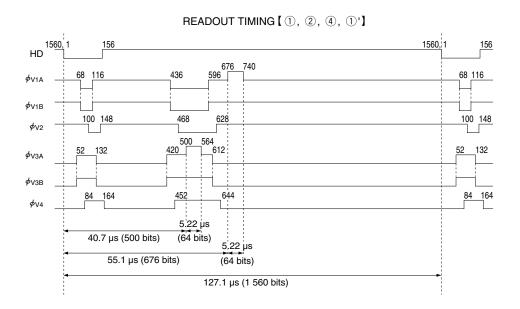

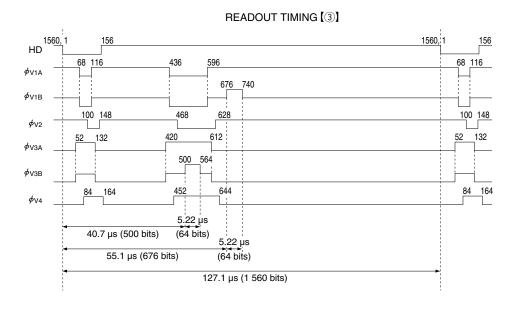

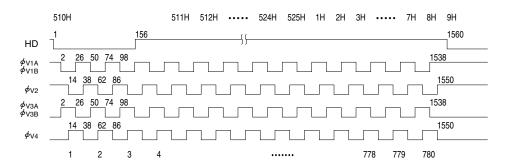

## **TIMING CHART**

#### TIMING CHART EXAMPLE

- Do not use these signals immediately after field accumulation mode is transferred to frame accumulation mode for still image capturing.

- Do not use these signals immediately after frame accumulation mode is transferred to field accumulation mode for monitoring image.

- \* Start the exposure period after 10 ms later that OFDC is high, and finish before charge swept transfer.

- \* Apply at least an OFD shutter pulse to OFD in each field accumulation mode.

\* Do not use the frame signals immediately after field accumulation mode is transferred to frame accumulation mode.

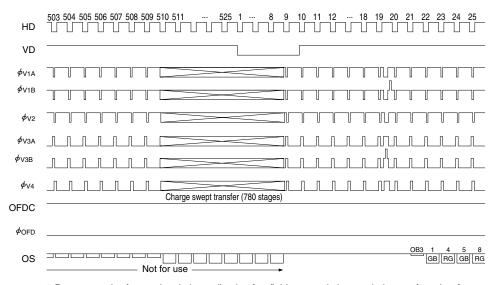

#### 3 VERTICAL TRANSFER TIMING [FRAME ACCUMULATION MODE]

\* Do not use the frame signals immediately after field accumulation mode is transferred to frame accumulation mode.

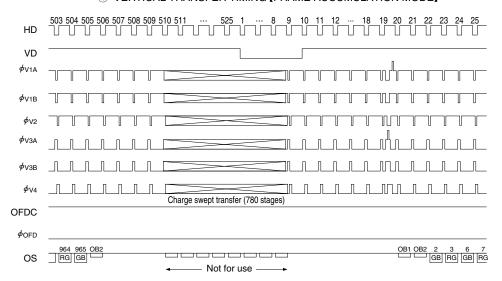

## 4 VERTICAL TRANSFER TIMING [FRAME ACCUMULATION MODE]

\* Do not use the field signals immediately after frame accumulation mode is transferred to field accumulation mode.

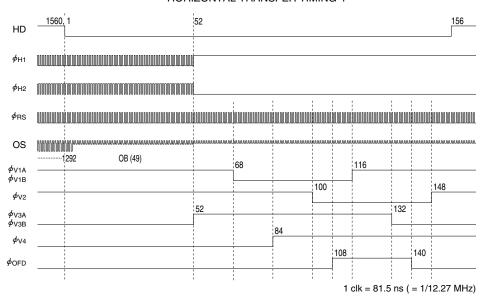

#### **HORIZONTAL TRANSFER TIMING-1**

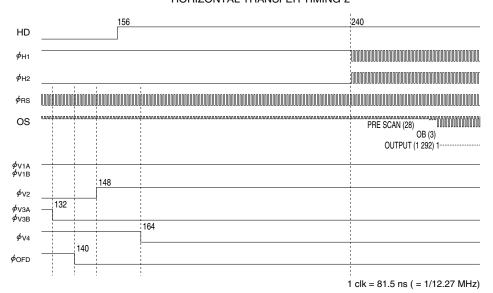

## HORIZONTAL TRANSFER TIMING-2

#### CHARGE SWEPT TRANSFER TIMING

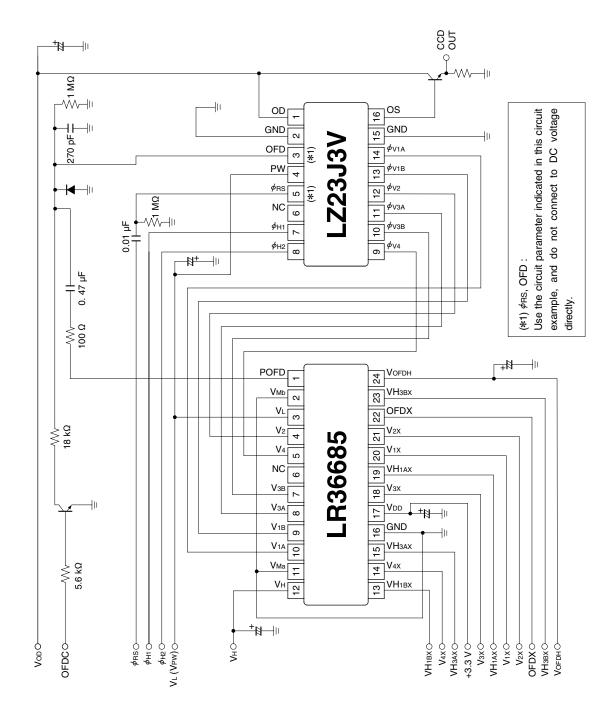

# SYSTEM CONFIGURATION EXAMPLE

PACKAGE (Unit: mm)

#### PRECAUTIONS FOR CCD AREA SENSORS

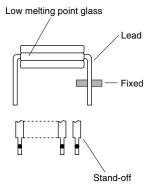

## 1. Package Breakage

In order to prevent the package from being broken, observe the following instructions:

- The CCD is a precise optical component and the package material is ceramic or plastic. Therefore,

- Take care not to drop the device when mounting, handling, or transporting.

- Avoid giving a shock to the package.

Especially when leads are fixed to the socket or the circuit board, small shock could break the package more easily than when the package isn't fixed.

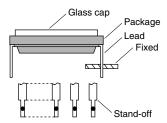

- 2) When applying force for mounting the device or any other purposes, fix the leads between a joint and a stand-off, so that no stress will be given to the jointed part of the lead. In addition, when applying force, do it at a point below the stand-off part.

(In the case of ceramic packages)

The leads of the package are fixed with low melting point glass, so stress added to a lead could cause a crack in the low melting point glass in the jointed part of the lead.

(In the case of plastic packages)

The leads of the package are fixed with package body (plastic), so stress added to a lead could cause a crack in the package body (plastic) in the jointed part of the lead.

- When mounting the package on the housing, be sure that the package is not bent.

- If a bent package is forced into place between a hard plate or the like, the package may be broken.

- If any damage or breakage occurs on the surface of the glass cap, its characteristics could deteriorate.

Therefore,

- Do not hit the glass cap.

- Do not give a shock large enough to cause distortion.

- Do not scrub or scratch the glass surface.

- Even a soft cloth or applicator, if dry, could cause dust to scratch the glass.

# 2. Electrostatic Damage

As compared with general MOS-LSI, CCD has lower ESD. Therefore, take the following anti-static measures when handling the CCD:

- 1) Always discharge static electricity by grounding the human body and the instrument to be used. To ground the human body, provide resistance of about 1 M $\Omega$  between the human body and the ground to be on the safe side.

- When directly handling the device with the fingers, hold the part without leads and do not touch any lead.

- 3) To avoid generating static electricity,

- a. do not scrub the glass surface with cloth or plastic.

- b. do not attach any tape or labels.

- c. do not clean the glass surface with dustcleaning tape.

- When storing or transporting the device, put it in a container of conductive material.

#### 3. Dust and Contamination

Dust or contamination on the glass surface could deteriorate the output characteristics or cause a scar. In order to minimize dust or contamination on the glass surface, take the following precautions:

- Handle the CCD in a clean environment such as a cleaned booth. (The cleanliness level should be, if possible, class 1 000 at least.)

- 2) Do not touch the glass surface with the fingers. If dust or contamination gets on the glass surface, the following cleaning method is recommended:

- Dust from static electricity should be blown off with an ionized air blower. For antielectrostatic measures, however, ground all the leads on the device before blowing off the dust.

- The contamination on the glass surface should be wiped off with a clean applicator soaked in Isopropyl alcohol. Wipe slowly and gently in one direction only.

- Frequently replace the applicator and do not use the same applicator to clean more than one device.

- Note: In most cases, dust and contamination are unavoidable, even before the device is first used. It is, therefore, recommended that the above procedures should be taken to wipe out dust and contamination before using the device.

#### 4. Other

- Soldering should be manually performed within 5 seconds at 350 °C maximum at soldering iron.

- Avoid using or storing the CCD at high temperature or high humidity as it is a precise optical component. Do not give a mechanical shock to the CCD.

- Do not expose the device to strong light. For the color device, long exposure to strong light will fade the color of the color filters.