# 捷多邦,专业PCB打样**MS**多数**59P** 急出货

#### 512-BIT(32-WORD BY 16-BIT) ELECTRICALLY ALTERABLE ROM

#### DESCRIPTION

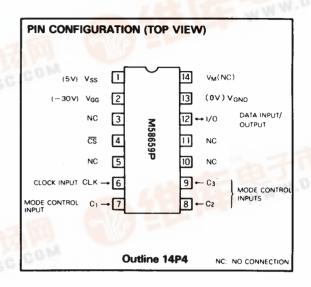

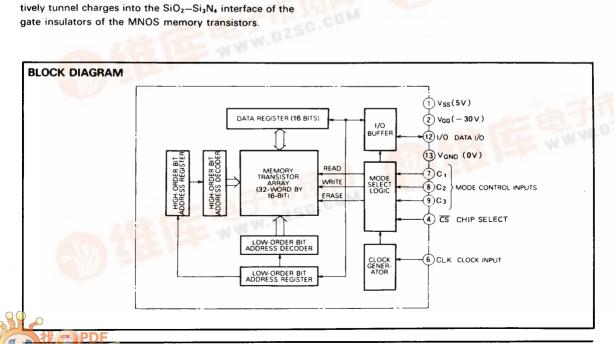

The M58659P is a serial input/output 512 bit electrically erasable and reprogrammable ROM organized as 32 words of 16 bits, and fabricated using MNOS technology. Data and addresses are transferred serially via a one-bit bidirectional bus.

#### **FEATURES**

- Word-by-word electrically alterable

- Non-volatile data storage . . . . . . . . . 10 years (min)

- Typical power supply voltages . . . . . . . -30V, +5V

- Number of erase-write cycles . . . . . . . 10<sup>5</sup> times (min)

- Number of read access unrefreshed. . .109 times (min)

- 5V I/O interface

#### **APPLICATION**

Non-volatile channel memories for electronic tuning systems and field-reprogrammable read-only memory systems

#### **FUNCTION**

The address is designated by one-of-four and one-of-eight coded digits. Seven modes—accept address, accept data, shift data output, erase, write, read, and standby—are all selected by a 3-bit code applied to  $C_1$ ,  $C_2$ , and  $C_3$ . Data is stored by internal negative writing pulses that selectively tunnel charges into the  $SiO_2-Si_3N_4$  interface of the gate insulators of the MNOS memory transistors.

### PIN DESCRIPTION

| Pin                             | Name                   | Functions                                                                                                                                                                                  |

|---------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/0                             | 1/0                    | In the accept address and accept data modes, used for input. In the shift data output mode, used for output. In the standby, read, erase and write modes, this pin is in a floating state. |

| VM                              | Test                   | Used for testing purposes only - It should be left unconnected during normal operation                                                                                                     |

| V <sub>SS</sub>                 | Chip substrate voltage | Normally connected to +5V                                                                                                                                                                  |

| V <sub>G</sub> G                | Power supply voltage   | Normally connected to -30V                                                                                                                                                                 |

| CLK                             | Clock input            | Required for all operating modes, when $\overline{\text{CS}}$ is low                                                                                                                       |

| C <sub>1</sub> ~ C <sub>3</sub> | Mode control input     | Used to select the operation mode                                                                                                                                                          |

| V <sub>GND</sub>                | Ground voltage         | Connected to ground (OV)                                                                                                                                                                   |

| ĈŜ                              | Chip select            | Used for chip selection in "L"                                                                                                                                                             |

### **OPERATION MODES**

| Cı | C2 | C3 | Functions                                                                                                                                                                                                                                 |

|----|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| н  | н  | н  | Standby mode. The contents of the address registers and the data register remain unchanged. The output buffer is held in the floating state.                                                                                              |

| H  | н  | L  | Not used                                                                                                                                                                                                                                  |

| н  | L  | н  | Erase mode: The word stored at the addressed location is erased. The data bits after erasing are all low-level                                                                                                                            |

| н  | Ł  | L  | Accept address mode. Data presented at the I/O pin is shifted into the address registers one bit with each clock pulse. The address is designated by one-of-four and one-of-eight-coded digits. 32-word address is assigned in this mode. |

| L  | н  | н  | Read mode. The addressed word is read from the memory into the data register                                                                                                                                                              |

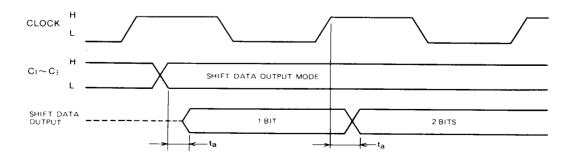

| L  | н  | L  | Shift data output mode. The output driver is enabled and the contents of the data register are shifted to the I/O pin one bit with each clock pulse.                                                                                      |

| L  | L  | н  | Write mode. The data contained in the data register is written into the location designated by the address registers                                                                                                                      |

| L  | L  | L  | Accept data mode: The data register accepts serial data from the I/O pin one bit with each clock pulse. The address registers remain unchanged.                                                                                           |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter             | Conditions          | Ratings    | Unit |

|-----------------|-----------------------|---------------------|------------|------|

| V <sub>GG</sub> | Supply voltage        |                     | 0.3~-40    | V    |

| VI              | Input voltage         | With respect to VSS | 0.3 ~- 20  | V    |

| Vo              | Output voltage        |                     | 0.3~-20    | V    |

| Tstg            | Storage temperature   |                     | - 40 ~ 125 | τ    |

| Topr            | Operating temperature |                     | - 10 ~70   | τ    |

#### RECOMMENDED OPERATING CONDITIONS (Ta = - 10~70°C, unless otherwise noted)

| Symbol                           | Parameter                |                      | Unit              |                      |      |

|----------------------------------|--------------------------|----------------------|-------------------|----------------------|------|

|                                  | rarameter                | Min                  | Nom               | Max                  | Onit |

| V <sub>GG</sub> -V <sub>SS</sub> | Supply voltage           | 32.2                 | <sub>4</sub> - 35 | - 37.8               | V    |

| Vss-VgND                         | Supply voltage           | 4.75                 | 5                 | 6                    | ٧    |

| VIH                              | High-level input voltage | V <sub>SS</sub> - 1  |                   | V <sub>SS</sub> +0.3 | ٧    |

| VIL                              | Low-level input voltage  | V <sub>SS</sub> -6.5 |                   | V SS-4.25            | V    |

**ELECTRICAL CHARACTERISTICS** ( $T_a = -10 - 70 \, \text{C}$ ,  $V_{GG} - V_{SS} = -35 \, \text{V} \pm 8 \, \text{\%}$ ,  $V_{SS} - V_{GND} = 5 \, \text{V} - 5 \, \text{\%}$ , unless otherwise noted)

| Symbol | Parameter                                           | Test conditions                         | Limits              |     |                        |      |

|--------|-----------------------------------------------------|-----------------------------------------|---------------------|-----|------------------------|------|

|        | - didinates                                         | Test conditions                         | Min                 | Тур | Max                    | Unit |

| ViH    | High-level input voltage                            |                                         | V <sub>SS</sub> - 1 |     | V <sub>SS</sub> + 0.3  | ٧    |

| VIL    | Low-level input voltage                             |                                         | Vss-6.5             |     | Vss-4.25               | V    |

| IIL    | Low-level input current CLK, C1, C2, C3, I/O        | $V_1 - V_{SS} = -6.5V$                  | -10                 |     | + 10                   | μA   |

| Rı     | Input pull-up resistance, CS                        |                                         |                     | 30  |                        | kΩ   |

| lozL   | Off-state output current, low-level voltage applied | V <sub>0</sub> -V <sub>SS</sub> = -6.5V | -10                 |     | + 10                   | μА   |

| VoH    | High-level output voltage                           | $I_{OH} = -200\mu A$                    | V <sub>SS</sub> - 1 |     |                        | ٧    |

| VoL    | Low-level output voltage                            | I <sub>OL</sub> = 80µA                  |                     |     | V <sub>GND</sub> + 0.5 | ٧    |

| Igg    | Supply current from VGG                             | $I_{O} = 0\mu\Delta$                    |                     | 5.5 | 8.8                    | mA   |

Note 1: Typical values are at Ta = 25°C and VGG-VSS = -35V.

TIMING REQUIREMENTS ( $T_a = -10 \sim 70 \, \text{C}$ .  $V_{GG} - V_{SS} = -35 \, \text{V} \pm 8 \, \text{\%}$ ,  $V_{SS} - V_{GND} = 5 \, \text{V} - 5 \, \text{\%}$ , unless otherwise noted.)

| Symbol                         | Parameter                                             | Test conditions |     | Limits |     |      |

|--------------------------------|-------------------------------------------------------|-----------------|-----|--------|-----|------|

|                                | Farameter                                             |                 | Min | Тур    | Max | Unit |

| $T_{L(\phi)}$                  | Negative clock pulse width                            |                 | 30  |        |     | μS   |

| Τ <sub>Η(φ)</sub>              | Positive clock pulse width                            |                 | 33  |        |     | μS   |

| T <sub>(ø)</sub>               | Clock period                                          |                 |     |        | 300 | μS   |

| t w                            | Write time                                            |                 | 16  | 20     | 24  | ms   |

| t <sub>E</sub>                 | Erase time                                            |                 | 16  | 20     | 24  | ms   |

| t <sub>r,</sub> t <sub>f</sub> | Risetime, fall time                                   |                 |     |        | 1   | μS   |

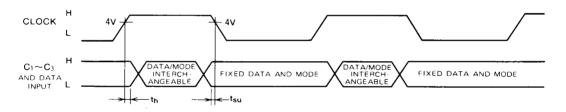

| t <sub>su</sub>                | Control setup time before the fall of the clock pulse |                 | 1   |        |     | μS   |

| th                             | Control hold time after the rise of the clock pulse   |                 | 0   |        |     | μS   |

| tss                            | Clock control setup time before the fall of CS        |                 | 1   |        |     | μS   |

| t <sub>hs</sub>                | Clock control hold time after the rise of CS          |                 | 1   |        |     | μs   |

SWITCHING CHARACTERISTICS (Ta =  $-10 \sim 70 \, \text{C}$ .  $V_{GG} = -35 \text{V} \pm 8 \, \%$ . unless otherwise noted )

| Symbol          | Parameter                                 | Alternative symbols | Test conditions                                                            | Limits          |     |     |       |

|-----------------|-------------------------------------------|---------------------|----------------------------------------------------------------------------|-----------------|-----|-----|-------|

|                 |                                           |                     | rest conditions                                                            | Min             | Typ | Max | Unit  |

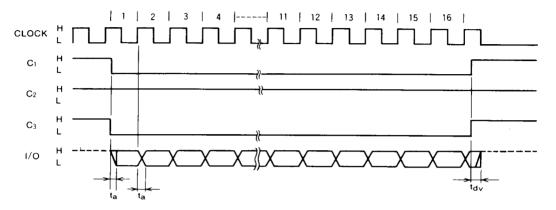

| ta(c)           | Read access time                          | tew                 | $C_L = 100pF$ $V_{OH} = V_{SS} - 2V$<br>$V_{OL} = V_{GND} + 1.5V$          |                 |     | 20  | μs    |

| ts              | Unpowered nonvolatile data retention time | Ts                  | $N_{EW} = 10^4$ , $t_{W(W)} = 20 \text{ ms}$<br>$t_{W(E)} = 20 \text{ ms}$ | 10              |     |     | Year  |

|                 |                                           | Ts                  | $N_{EW} = 10^5$ , $t_{W(W)} = 20 \text{ ms}$<br>$t_{W(E)} = 20 \text{ ms}$ | 1               |     |     | 1601  |

| NEW             | Number of erase/write cycles              | Nw                  |                                                                            | 10 <sup>5</sup> | Ī   |     | Times |

| N <sub>RA</sub> | Number of read access unrefreshed         | NRA                 |                                                                            | 109             |     |     | Times |

| tdv             | Data valid time                           | tew                 |                                                                            |                 |     | 20  | μS    |

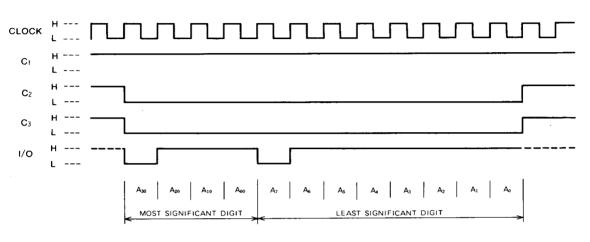

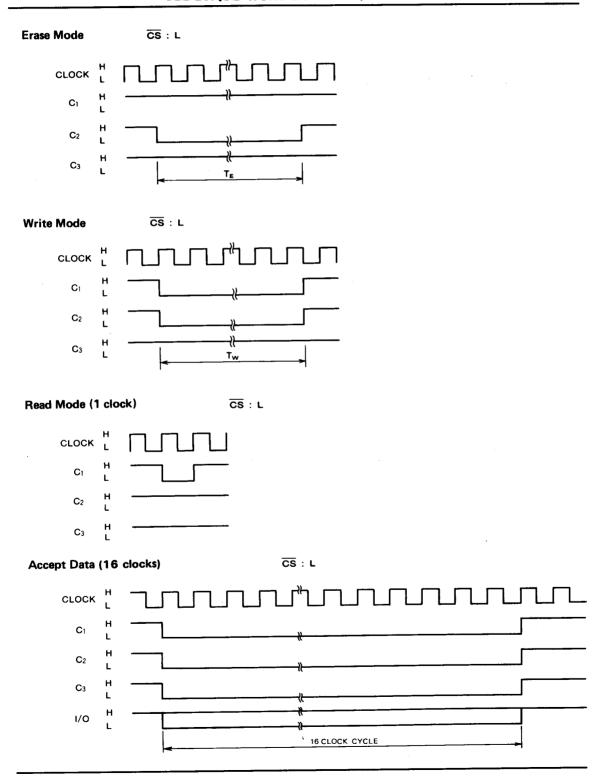

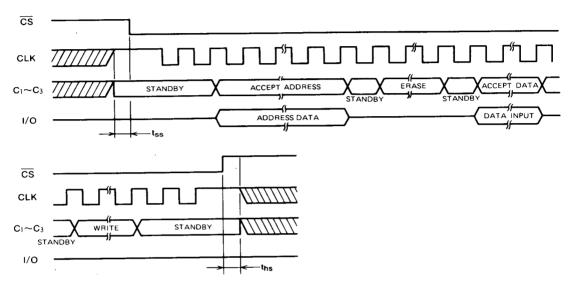

### **TIMING DIAGRAM**

Accept Address Mode (12 clocks)

CS : L

Note 2: The addresses from  $A_{00}$  to  $A_{37}$  are designated by one-of-four and one-of-eight coded digits. The above figure shows designation of address  $A_{37}$

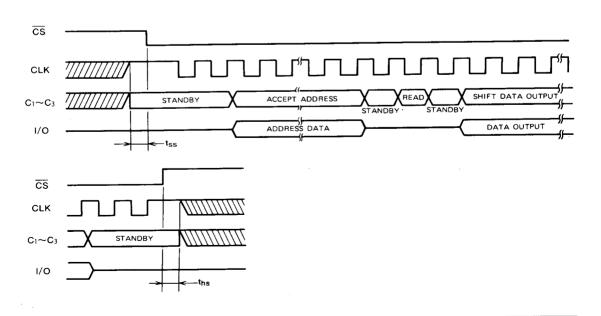

### Shift Data Output Mode (16 clocks) CS: L

## Timing of clock, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>, and data input

Note 3  $|C_1| \sim |C_3|$  and accept data are interchnageable while the clock is set high.

# Timing of clock, $\mathbf{C_1}$ , $\mathbf{C_2}$ , $\mathbf{C_3}$ , and data input

## **Operation flowchart**

### **Rewriting flowchart**

Note 4: One or more clock are required for standby between modes.

- 5: Set  $\overline{\text{CS}}$  to the low level after the lapse of  $t_{\text{SS}}$  and CLK has been set high and  $C_1 \sim C_3$  have been set to

- the standby mode.

- 6: Keep CLK to the high level and  $C_1 \sim C_3$  to "standby" from the time when  $\overline{CS}$  is set high to the lapse of ths

#### Read Flowchart

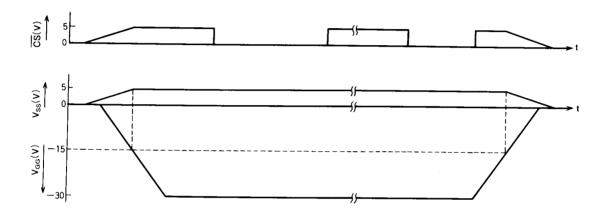

### **Power-on/off Conditions**

With power-on,  $V_{GG}$  is applied after  $V_{SS}$  has been applied. With power-off,  $V_{SS}$  is cut after  $V_{GG}$  has been cut. For power-on and off, hold  $\overline{CS}$  in  $V_{SS}$  or floating state. The recommended timing chart for power-on and off is as follows.