# M61006FP

# DISTANCE DETECTION SIGNAL PROCESSING FOR 3 V SUPPLY VOLTAGE

REJ03F0039-0100Z Rev.1.0 Sep.16.2003

## **Description**

M61006FP is a semiconductor integrated circuit including distance detection signal processing circuit for 3 V supply voltage. This device transforms each optical inflow current I1 and I2 from PSD SENSOR into the voltage, and integrates the output after doing calculation corresponds to I1 / (I1+I2), and outputs it as the voltage data.

#### **Features**

- Wide supply voltage range: Vcc = 2.2 to 5.5 V

- Including clamp level switching circuit

(It is possible to set a clamp level to 15 points with outside control.)

- Including infinity discrimination function (clamp on detection function)

- Including POWER ON RESET function

- Including simple temperature detection function

(It is possible to correct temperature with transmitting this output to the microcomputer.)

## **Application**

Auto focus control for a camera, short distance sensor, etc.

## **Recommended Operating Condition**

- Supply voltage range ..... 2.2 V to 5.5 V

- Rated supply voltage ..... 3.0 V

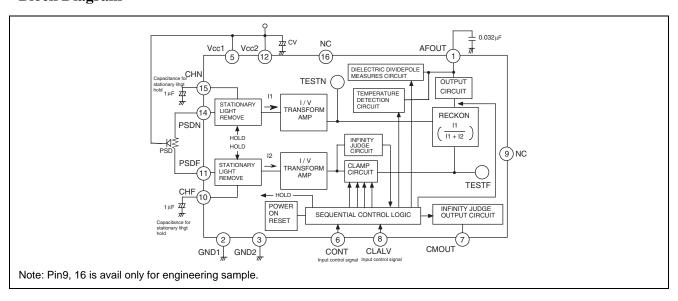

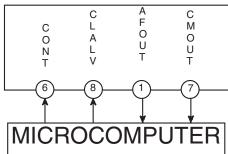

## **Block Diagram**

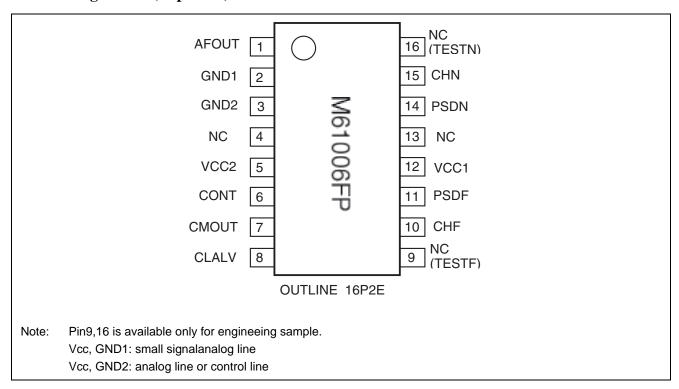

# **Pin Configuration (Top View)**

## **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C \text{ unless otherwise noted})$

| Parameter             | Symbol          | Rating                    | Unit    | Remark             |

|-----------------------|-----------------|---------------------------|---------|--------------------|

| Supply voltage        | V <sub>CC</sub> | 7.0                       | V       | Note1              |

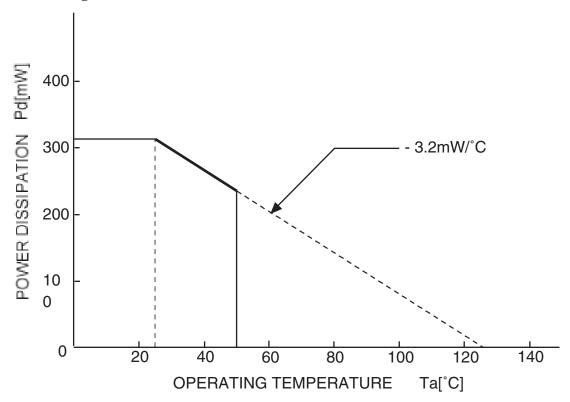

| Power dissipation     | Pd              | 320                       | mW      | Ta = 25°C          |

| Thermal derating      | Κθ              | -3.2                      | mW / °C | Ta ≥ 25°C          |

| Pin supply voltage    | V <sub>IF</sub> | 7.0                       | V       | Pin 6, 7, 8        |

| Another terminal      | VI / O          | 0 to V <sub>CC</sub> +0.3 | V       | Note2              |

| Output inflow current | Icmout          | 0.5                       | mA      | NPN open collector |

| Operating temperature | Topr            | –10 to 50                 | °C      |                    |

| Storage temperature   | Tstg            | -40 to 125                | °C      |                    |

Notes: 1. As a principle, do not provide a supply voltage reversely.

## **Thermal Derating Curve**

<sup>2.</sup> As a principle, do not provide the terminals with the voltage over supply voltage or under ground voltage.

# **Electrical Characteristics - 1**

$(Ta = 25^{\circ}C)$

| Classi-<br>ficatin | Parameter                                               | Symbol Test conditions |                                                         |       | Limits |                              |    | V <sub>CC</sub> (V) | No<br>te |

|--------------------|---------------------------------------------------------|------------------------|---------------------------------------------------------|-------|--------|------------------------------|----|---------------------|----------|

|                    |                                                         |                        |                                                         | Min   | Тур    | Max                          | =  |                     |          |

|                    | Operating supply voltage range                          | VCC                    |                                                         | 2.2   | 3.0    | 5.5                          | V  | 3.0                 |          |

| Consum-            | Usual consuming current                                 | ICC1                   |                                                         | _     | 3.9    | 5.1                          | mA |                     | *6       |

| ing<br>Current     | Rapid charge consuming current 1                        | ICC2                   | AFOUT rapid charge<br>consuming current<br>VAFOUT = 0 V | _     | 9.5    | 12.5                         | mA |                     | *1<br>*6 |

|                    | Rapid charge consuming current 2                        | ICC3                   | CH rapid charge consuming current                       | _     | 10.5   | 13.7                         | mA |                     | *1<br>*6 |

| CONT               | CONT "H" input voltage                                  | VCOH                   |                                                         | 1.1   | _      | 7.0                          | V  |                     |          |

| pin                | CONT "L" input voltage                                  | VCOL                   |                                                         | 0     | _      | 0.3                          | V  |                     |          |

|                    | CONT "H" input current                                  | ICOH                   | VIH = 5.5 V                                             | _     | _      | 1.0                          | μΑ |                     | *6       |

|                    | CONT "L" input current                                  | ICOL                   | VIL = 0 V                                               | -84   | -64    | -44                          | μΑ |                     |          |

| CLALV              | CLALV "H" input voltage                                 | VCLH                   |                                                         | 1.1   | _      | 7.0                          | V  |                     |          |

| pin                | CLALV "L" input voltage                                 | VCLL                   |                                                         | 0     | _      | 0.3                          | V  |                     |          |

|                    | CLALV "H" input current                                 | ICLH                   | VIH = 5.5 V                                             | _     | _      | 1.0                          | μΑ |                     | *6       |

|                    | CLALV "L" input current                                 | ICLL                   | VIL = 0 V                                               | -84   | -64    | -44                          | μΑ |                     |          |

| HOLD C             | CH rapid charge current                                 | ICHQC                  | IPSD = 5 μA<br>VCH = 0 V                                | -2000 | -1000  | -500                         | μΑ |                     |          |

|                    | CH stationary charge current                            | ICHC                   | VCH = 0 V                                               | -33   | -22    | <b>–11</b>                   | μΑ |                     |          |

|                    | CH stationary discharge current                         | ICHD                   | VCH = 1.5 V                                             | 11    | 22     | 33                           | μΑ |                     |          |

| Integra-           | AFOUT reset current                                     | I <sub>RAFOUT</sub>    | VAFOUT = 0.5 V                                          | 600   | 1200   | 2400                         | μΑ |                     |          |

| tion<br>circuit    | AFOUT integrating off current                           | I <sub>OFFAFOUT</sub>  | VAFOUT = 0.5 V                                          | _     | _      | 1.0                          | μΑ |                     | *6       |

|                    | AFOUT integrating current (maximum integration current) | I <sub>INTAFOUT</sub>  | VAFOUT = 0.5 V<br>VCHF = 2.0 V,<br>VCHN = 0 V           | -13.0 | -10.0  | -7.0                         | μА |                     |          |

|                    | Distance measurement integration current stability      | $\Delta l_{INT}$       |                                                         | _     | 3.0    | 6.0                          | %  |                     | *2<br>*6 |

|                    | AFOUT temperature revision integration current          | I <sub>t</sub> AFOUT   | VAFOUT = 0.5 V                                          | -6.5  | -5.0   | -3.5                         | μΑ |                     |          |

|                    | The stability of temperature integration current        | Δlt                    |                                                         | _     | 3.0    | 6.0                          | %  |                     | *2<br>*6 |

|                    | Dynamic rage of AFOUT pin                               | D <sub>AFOUT</sub>     |                                                         | _     | _      | 2.7<br>(V <sub>CC</sub> 0.3) | V  | •                   | *7       |

# **Electrical Characteristics - 2**

$(Ta = 25^{\circ}C)$

| Classifi-<br>cation    | Parameter                  | rameter Symbol Test conditions |                                           | Limits  |       |       | Unit | Vcc      | Note |

|------------------------|----------------------------|--------------------------------|-------------------------------------------|---------|-------|-------|------|----------|------|

| Cation                 |                            |                                |                                           | Min Typ |       | Max   | -    | (V)      |      |

| AF Input<br>Condition1 | AF output voltage (9:1) -1 | D (9:1) - 1                    | Near side 9: far side 1<br>IP = 100 nA    | 1.26    | 1.81  | 2.36  | V    | 3.0      | *3   |

|                        | AF output voltage (6:4) -1 | D (6:4) - 1                    | Near side 6: far side 4<br>IP = 100 nA    | 0.83    | 1.19  | 1.55  | V    |          | *3   |

|                        | AF output voltage (3:7) -1 | D (3:7) - 1                    | Near side 3: far side 7<br>IP = 100 nA    | 0.41    | 0.59  | 0.77  | V    |          | *3   |

|                        | AF slope - 1               | ΔAF - 1                        |                                           | 0.85    | 1.22  | 1.59  | V    |          | *3   |

|                        | AF linearity - 1           | LAF - 1                        |                                           | 0.875   | 0.975 | 1.075 | _    |          | *3   |

| AF input condition2    | AFoutput time<br>(9:1) - 2 | D (9:1) - 2                    | Near side 9: Far side1<br>IP = 50 nA      | 1.26    | 1.81  | 2.36  | V    |          | *3   |

|                        | AFoutput time<br>(6:4) - 2 | D (6:4) - 2                    | Near side 6: Far side4<br>IP = 50 nA      | 0.83    | 1.19  | 1.55  | V    |          | *3   |

|                        | AFoutput time<br>(3:7) - 2 | D (3:7) - 2                    | Near side 3: Far side7<br>IP = 50 nA      | 0.41    | 0.59  | 0.77  | V    |          | *3   |

|                        | AF slope - 2               | ΔAF - 2                        |                                           | 0.85    | 1.22  | 1.59  | V    |          | *3   |

|                        | AF linearity - 2           | LAF - 2                        |                                           | 0.875   | 0.975 | 1.075 | _    |          | *3   |

| AF input condition3    | AFoutput time<br>(9:1) - 3 | D (9:1) - 3                    | Near side 9: Far side1<br>IP = 50 nA      | 1.26    | 1.81  | 2.36  | V    |          | *3   |

|                        | AFoutput time (6:4) - 3    | D (6:4) - 3                    | Near side 6: Far side4<br>IP = 50 nA      | 0.83    | 1.19  | 1.55  | V    |          | *3   |

|                        | AFoutput time<br>(3:7) - 3 | D (3:7) - 3                    | Near side 3: Far side7<br>IP = 50 nA      | 0.41    | 0.59  | 0.77  | V    |          | *3   |

|                        | AF slope - 3               | ΔAF - 3                        |                                           | 0.85    | 1.22  | 1.59  | μΑ   |          | *3   |

|                        | AF linearity - 3           | LAF - 3                        |                                           | 0.875   | 0.975 | 1.075 | V    |          | *3   |

| AF input condition     | AFoutput time<br>(9:1) - 3 | D (9:1) - 3                    | Near side 9: Far side1 (condition 1 to 3) | -0.022  | _     | 0.022 | _    |          | *3   |

| 1 to 2                 | AFoutput time<br>(6:4) - 3 | D (6:4) - 3                    | Near side 6: Far side4 (condition 1 to 3) | -0.022  | _     | 0.022 | _    |          | *3   |

|                        | AFoutput time<br>(3:7) - 3 | D (3:7) - 3                    | Near side 3: Far side7 (condition 1 to 3) | -0.022  | _     | 0.022 |      | <b>V</b> | *3   |

# **Electrical Characteristics - 3**

$(Ta = 25^{\circ}C)$

| Classifi-<br>cation | Parameter                          | Symbol                    | Test conditions                                           | Limit       | s   |     | Unit | V <sub>CC</sub><br>(V) | Note |

|---------------------|------------------------------------|---------------------------|-----------------------------------------------------------|-------------|-----|-----|------|------------------------|------|

| Cation              |                                    |                           |                                                           | Min         | Тур | Max |      | (*)                    |      |

| Clamp               | CMOUT leak current                 | ICMOUTH                   | VCMOUT = 5.5 V                                            | _           | _   | 1.0 | μΑ   | 3.0                    | *6   |

| determin ation      | CMOUT saturation current           | VCMOUTL                   | ICMOUT = 500 μA                                           | _           | _   | 0.3 | V    |                        | *6   |

| SENSOR              | Signal ray maximum current         | $\Delta INF$              |                                                           | _           | _   | 3.0 | μΑ   |                        | *4   |

|                     |                                    |                           |                                                           |             |     |     |      |                        | *8   |

|                     | Capacity of the current to extract | IPSD                      |                                                           | _           | _   | 30  | μΑ   |                        | *4   |

|                     | stationary rays                    |                           |                                                           |             |     |     |      |                        | *8   |

|                     | Clamp level                        | ICLAM                     | The change values about TYP current (Design target value) | <b>–</b> 50 | _   | 50  | %    |                        |      |

| Clout for           | Nch Response speed of Circuit for  | $\Delta T_{\text{TESTN}}$ |                                                           | _           | _   | 26  | μsec |                        | *5   |

| measure             | measurement rays                   |                           |                                                           |             |     |     |      |                        | *6   |

| ment rays           | Fch Response speed of Circuit for  | $\Delta T_{\text{TESTF}}$ |                                                           | _           | _   | 26  | μsec | 1                      | *5   |

|                     | measurement rays                   |                           |                                                           |             |     |     |      | •                      | *6   |

\*1 Rapid charge consuming current 1 and 2 are measured with the following conditions:

- Rapid charge consuming current 1

- = (Rapid charge current for integration capacitance AFOUT dielectric absorption) + (Usual consuming current)

- Rapid charge consuming current 2

- = (mainly Rapid charge current for hold capacitance CHN, CHF) + (Usual consuming current)

Shorten hold capacitance CHN, CHF pin, integration capacitance AFOUT pin and GND at measurement rapid charge consuming current 1 and hold capacitance CHN, CHF pin and GND at measurement rapid charge consuming current 2 to leave rapid charge current on stationary. But in practical uses it runs as the follows:

- Rapid charge current for hold capacitance CHN, CHF:

Use in a constant current charge. The current remain consuming in IC after completing charge.

- Rapid charge current for integration capacitance AFOUT dielectric absourption:

Transition current. It flows until completing charge.

- \*2 Charging rate of distance measurement integration current and temperature integration current when the voltage of AFOUT changes.

$$\Delta IAFOUT1 = (1 - \frac{\text{distance measurement current (at AFOUT = 0.5V)}}{\text{distance measurement current (at AFOUT = VCC-0.3V)}} / (VCC-0.3V-0.5V) \times 100\%$$

$$\Delta IAFOUT2 = (1 - \frac{\text{distance measurement current (at AFOUT = 0V)}}{\text{distance measurement current (at AFOUT = VCC-0.3V)}} / (VCC-0.3V-0.5V) \times 100\%$$

#### M61006FP

\*3 Set a current output from PHOTOCUPPLER to following input conditions, and input the varied resistance ratio. AF slope, linearity is calculated with following equations by measuring AFOUT output voltage.

Input condition1: I<sub>PSD</sub> (Stationary light current) = 0 I1:I2 = 100 nA Input condition2: I<sub>PSD</sub> (Stationary light current) = 0 I1:I2 = 50 nA Input condition3: I<sub>PSD</sub> (Stationary light current) = 10  $\mu$ A I1:I2 = 100 nA

D (9:1).....The AFOUT output voltage at input with I1:I2 = 9:1 D (6:4).....The AFOUT output voltage at input with I1:I2 = 6:4 D (3:7).....The AFOUT output voltage at input with I1:I2 = 3:7

AF slope:  $\triangle AF = D (9:1) - D (3:7)$

AF linearity: L(AF) = (D(9:1) - (6:4)) / (D(6:4) - (3:7))

PSD quite resistance: 120 k $\Omega$

- \*4 Input current of one side channel without saturating stationary light remove circuit and I / V transform amplifier circuit.

- \*5 Confirm not to change the output data at measuring AF input condition (1 to 4), when you shorten intervals between stationary ray hold and distance measurement integration beginning to MIN 26 μS.

- \*6 The value in this item is less than "max" value at any cases.

- \*7 Set AFOUT capacity, distance measurement integration time, and the number of integration under max value, because the "max" value in this item indicates a maximum of IC dynamic range.

- \*8 Establish optional system to be input current to IC less than standard value, because this item's value indicates maximum input current to IC.

# **Interface Table**

$(Vcc = 3.0 \text{ V}, Ta = 25^{\circ}\text{C})$

AF – IC side

|          | -               |                    |        |     |           |      | Test              |

|----------|-----------------|--------------------|--------|-----|-----------|------|-------------------|

|          |                 |                    | Limits |     |           | _    | conditions and    |

| Pin name | Circuit diagram | Parameter          | Min    | Тур | Max       | Unit | note              |

| CONT     | <del>)</del>    | "H" input voltage  | 1.1    | _   | 7.0       | V    |                   |

| CLALV    | <b>Ş</b> I      | "L" input voltage  | 0      | _   | 0.3       | _    |                   |

|          | $\Gamma$        | "H" input voltage  | _      | _   | 1.0       | μΑ   | VH = 5.5 V        |

|          | ¥ ¥             | "L" input voltage  | -84    | -64 | -44       | _    | VF = 0 V          |

|          | <b>\$ \$</b> _  |                    |        |     |           |      |                   |

|          |                 |                    |        |     |           |      |                   |

|          | *               |                    |        |     |           |      |                   |

|          | <i></i>         |                    |        |     |           |      |                   |

| AFOUT    |                 | "H" input voltage  | _      | _   | Vcc       | V    |                   |

|          | <b>₹</b> →      |                    |        |     | -0.3      | _    |                   |

|          |                 | "L" input voltage  | 0      |     | 0.3       |      |                   |

|          | \               | Integration        | _      | _   | 1.0       | μΑ   | VF = 0.5 V        |

|          |                 | OFF current        |        |     |           | _    |                   |

|          |                 | Integration        | -13    | -10 | <b>–7</b> |      | VF = 0.5 V        |

|          | <i>i</i>        | ON current         |        |     |           |      |                   |

|          |                 | (Ratio10:0)        |        |     |           |      |                   |

| CMOUT    |                 | "L" output voltage |        |     | 0.3       | V    | $IOL = 500 \mu A$ |

|          | $\perp$         |                    |        |     |           |      |                   |

|          | 1 7             | "H" leak current   | _      | _   | 1.0       | μΑ   | VIN = 5.5 V       |

|          | m - m           |                    |        |     |           |      |                   |

|          |                 |                    |        |     |           |      |                   |

## **Controls**

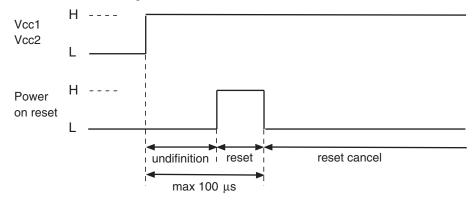

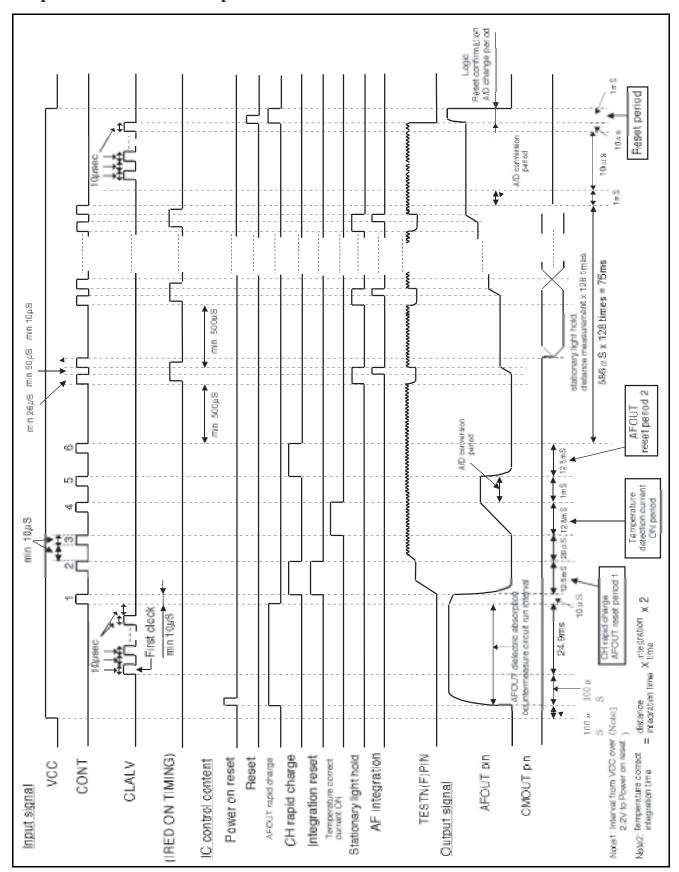

## (1) $V_{CC}(Vcc1+Vcc2)$

The power on reset circuit with a built in IC work by this pin turned on, and the whole IC including a part of logic circuit is done reset. Also the workings of power on reset circuit complete by less than  $100 \,\mu\text{S}$  from rise edge of VCC1, 2 (VCC1, VCC2 greater than  $2.2 \,\text{V}$ ).

Note: Regard as rising supply voltage in establishing the timing if uses of this IC is in connecting large capacitance with supply pin.

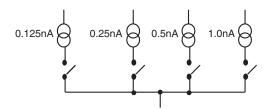

#### (2) CLALV:

Do reset the whole IC including the clamp level set and the part of logic. This IC include D / A converter for 4 bits, and it is possible to establish clamp level to 15 points by clock input after cancel of reset (including none clamp). And also, the whole IC including parts of logic is reset by 15th clump level setting pulse (at intervals of 16 click after this clamp)

Values of each bit current are established as the right side. The number of input clock and clamp level are as follows.

| bit | Set up current (Typ.) |

|-----|-----------------------|

| 1   | 0.130nA               |

| 2   | 0.260nA               |

| 3   | 0.520nA               |

| 4   | 1.040nA               |

| Clock value | Clamp level(Typ.) |

|-------------|-------------------|

| 0           | None clamp        |

| 1           | 0.130 nA          |

| 2           | 0.260 nA          |

| 3           | 0.390 nA          |

| 4           | 0.520 nA          |

| 5           | 0.650 nA          |

| 6           | 0.780 nA          |

| 7           | 0.910 nA          |

| 8           | 1.040 nA          |

| 9           | 1.170 nA          |

| 10          | 1.300 nA          |

| 11          | 1.430 nA          |

| Clock value | Clamp level(Typ.)      |

|-------------|------------------------|

| 12          | 1.560 nA               |

| 13          | 1.690 nA               |

| 14          | 1.820 nA               |

| 15          | None clamp,Logic reset |

| 16          | 0.130 nA               |

| 17          | 0.260 nA               |

| 18          | 0.390 nA               |

| 19          | 0.520 nA               |

| 20          | 0.650 nA               |

| 1<br>1      | I<br>I                 |

| !<br>!      | I<br>I                 |

| I<br>I      | <br>                   |

Clamp level is established with fall edge of input clock. It repeats the same value after 15 clock.

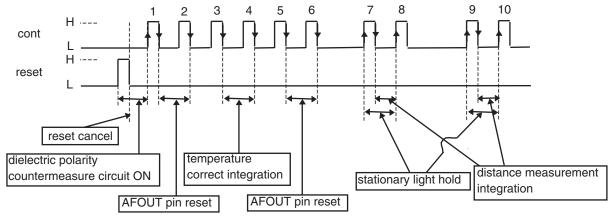

#### (3) CONT:

By the clock input of the this terminal after canceling the IC reset, it begin to control the whole IC as following function without establishing clamp level. And it repeat to switch over stationary hold and distance measurement integration current after 7th clock

- a) ON / OFF of dielectric polarity countermeasure circuit integration capacitance

- b) ON / OFF of CH rapid charge

- c) ON / OFF of AFOUT pin reset

- d) ON / OFF of temperature correct integration

- e) ON / OFF of stationary light hold

- f) ON / OFF of distance measurement integration

a. The dielectric polarty contermeasure of integlation capacitance:

The dielectric polarity contermeasure circuit of integration capacitance run between reset and rise edge of first CONT pin.

#### b. CH rapid charge:

After reset cancel, CH capacitance is charged rapidy between the fall edge of first clock and second ones.

### c. AFOUT pin reset:

After reset cannel, accumulated chage at capacitance added to AFOUT pin is removed between the fall clock edges of 1 to 2 and 5 to 6.

#### d. Temperrature correct integlation:

After reset cannel, temperature correct integration is carried out betweeen the fall edge of 3rd clock and 4th clock. This voltage of temperature corrent integration mentioned above is maintained at AFOUT pin. This voltage is currected temperature (including time charge correct of AFOUT pin added capacotance) as compared with base voltage estabilished previously.

#### e. Stationaly light hold:

After 7th clock from reset cuncel (from 7th clock rise to 8th clock rise), stationary light hold is carried out over and over.

#### f. Distance measurement integration:

After 7th clock from reset cancel (from 7th clock fall to 8th clock rise), distance measurement integration is carried out over and over.

#### (4) AFOUT:

After reset cancel, the voltage is outputted at intervals of temperature correct integration and distance measurement integration from about 0 V to above a D range of this pin. The output is carried out linearly by integration current or integration time.

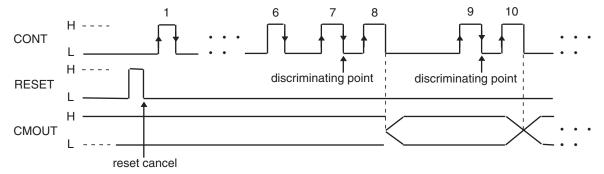

#### (5) CMOUT:

After the CONT pin input 7th clock fall from reset cancel, the signal current at PSDF side is distinguished from the clamp level in terms of the values. The result is outputted at each discrimination as the follows.

And after the CONT pin input 7th clock fall, the discrimination is carried out with the beginning of distance measurement start. After reset cancel, until CONT pin input 8th clock "H" is further outputted.

| PSDF side signal current | CMOUT output |

|--------------------------|--------------|

| Greater than clamp level | Н            |

| Less than clamp level    | L            |

Notes:

- 1. It is necessary to contact a control signal for IRED with the control signal mentioned above.

- 2. Connect NC terminals (4, 9, 12, 16 pin) to Vcc1 terminal or GND.

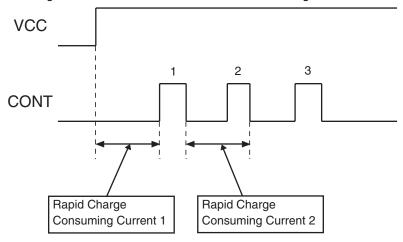

## **Sequential Time Chart Example**

## **Mask Option**

#### 1) Control terminal variation

1 Full spec (typical)

This type uses CONT,CLALV,AFOUT ,CMOUT terminal as I/F terminal to the microcomputer. This is the typical type at M61006FP.

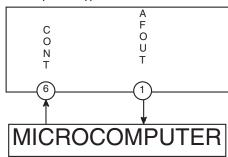

(2) Most simplified type

This type does not connect CLALV,CMOUT terminals to the microcomputer.

When above mentioned terminals are not connected to the microcomputer without changing mask,connect each terminal to the ground. In this case,clamp level becomes 0 And Power on reset in IC is used as reset.

- 3 Explanation of the terminal that can be simplified.

- (a) CLALV • • In the typical type,15 ways clamp levels can be set by the outside control,but also the terminal can be simplified by mask option as follows.

- (I) Clamp level fixation · · · · · · Selects 1 point from 15 steps of clamp level and fixes it.

- (II) Clamp level 2 step changeover · · · · Selects 2 points from clamp level and switches it by changing CLALV terminal HIGH/LOW. However,as selecting 2 points, there is a following constraint.

Fixes 3 parts of 4 switches corresponds to each bit in figure to ON or OFF.controls another part by CLALV terminal.

(b) CMOUT · · · · When an infinity decision function shouldn't be necessary, it is possible that a CMOUT terminal is removed.

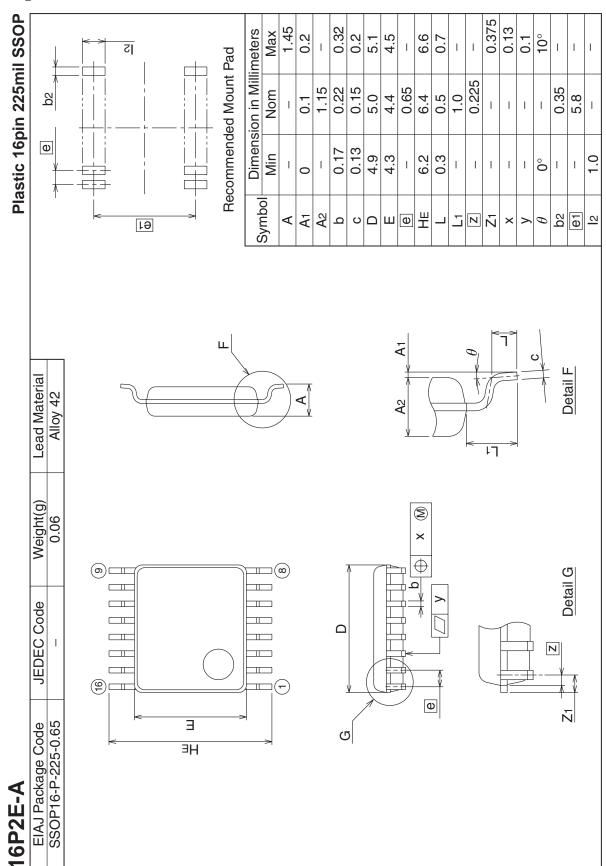

## **Package Dimensions**

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

The pastery in a survival circula designs; and the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss resident product product of the responsibility of the information of the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances i

- use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

**RENESAS SALES OFFICES**

http://www.renesas.com

**Renesas Technology America, Inc.** 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500 Fax: <1> (408) 382-7501

Renesas Technology Europe Limited.

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom Tel: <44> (1628) 585 100, Fax: <44> (1628) 585 900

Renesas Technology Europe GmbH Dornacher Str. 3, D-85622 Feldkirchen, Germany Tel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11

Renesas Technology Hong Kong Ltd. 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2375-6836

Renesas Technology Taiwan Co., Ltd. FL 10, #99, Fu-Hsing N. Rd., Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. 26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001