8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

### **DESCRIPTION**

M66009 silicon gate CMOS (complementary metal oxide semiconductor) integrated circuit converts 8-bit data from serial to parallel and vice versa.

This IC has 5 address setting bits, which enable users to set a distinctive address.

This IC offers a wide range of applications, such as for micro-computer input/output port extension.

### **FEATURES**

- · Has 5 bits for address setting

- Connected to microcomputer via 4 pins (EN,CLK, DI and DO)

- Input/output setting possible by the bit

- Schmitt input (RESET, EN and CLK)

- Wide operating temperature range (Ta =  $-20^{\circ}$ C to 75°C)

### **APPLICATION**

Microcomputer I/O port extension, etc.

### 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

#### **FUNCTION**

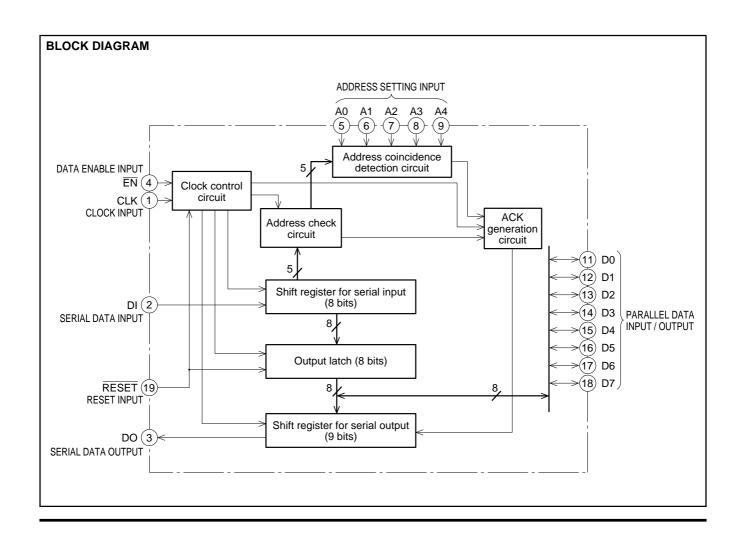

M66009 semiconductor circuit converts data from serial to parallel and vice versa. Address can be set freely at users' option.

It communicates with microcomputer via 4 signals lines:  $\overline{\text{EN}},$  CLK, DI and DO.

It has 5-bit address setting input. Connect each address input pin to Vcc or GND, then the address can be determined from among 32 patterns. When serial data arrives from microcomputer, this IC compares the address in the data to the address

set with these pins. If the two addresses are the same, the given command is executed.

To output serial input data in parallel, this IC converts the lower 8 bits of the 16-bit serial data into parallel, and outputs each to pins D0 to D7. The upper 8 bits are processed as address bits and command bits.

To output parallel input data in series, this IC prefixes one acknowledge bit to the 8 parallel bits which respectively refer to the status of pins D0 to D7, and then outputs 9 bits in series.

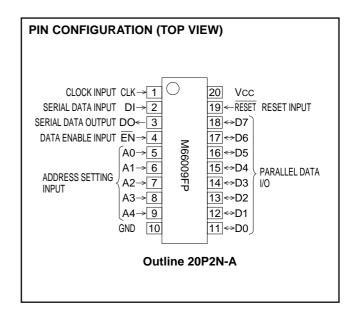

### **PIN DESCRIPTIONS**

| Pin   | Name                           | Input/Output | Functions                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------|--------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RESET | Reset input                    | Input        | "L" level: M66009 is reset to initial state.                                                                                                                                                                                                                 |  |  |  |  |  |

| EN    | Data enable input              | Input        | "L" level: M66009 becomes accessible.                                                                                                                                                                                                                        |  |  |  |  |  |

| CLK   | Serial clock input             | Input        | Serial data that arrives at pin DI from microcomputer is taken into M66009                                                                                                                                                                                   |  |  |  |  |  |

| DI    | Serial data input              | Input        | shift register at CLK rise edge. serial data is output from pin DO synchro-                                                                                                                                                                                  |  |  |  |  |  |

| DO    | Serial data output             | Output       | nously with CLK fall edge. Pin DO status stays at "H" level except during serial data output.                                                                                                                                                                |  |  |  |  |  |

| A0~A4 | Address setting input          | Input        | Connect each to Vcc or GND to set distinctive address. Command is executed only when serial data from microcomputer includes the same address as that set by these pins. When connected to Vcc, pin status is "1". When connected to GND, pin status is "0". |  |  |  |  |  |

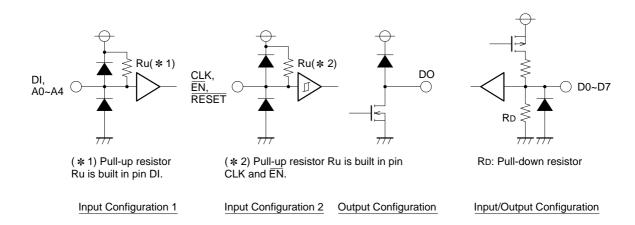

| D0~D7 | Parallel data input/<br>output | Input/Output | Used to input/output parallel data. Because pull-down resistor is built in and output transistor is P-ch open drain, pins in "L" output status (equals to P-ch transistor OFF) function as input pins.                                                       |  |  |  |  |  |

| Vcc   | Positive supply pin            |              | Connected positive supply (5V).                                                                                                                                                                                                                              |  |  |  |  |  |

| GND   | Grounding pin                  |              | Used for grounding (0V).                                                                                                                                                                                                                                     |  |  |  |  |  |

#### **INPUT/OUTPUT DATA LOGIC**

Serial data input from pin DI is output in parallel from pins D0 thru D7, being inverted in logic. Parallel data input from pins D0 thru D7 is output in series from pin DO in the same logic. Therefore, to set I/O pins to input, DI input data should be set to "H".

### 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

# DATA SENDING/RECEIVING PROTOCOL AND OPERATION PROCEDURE

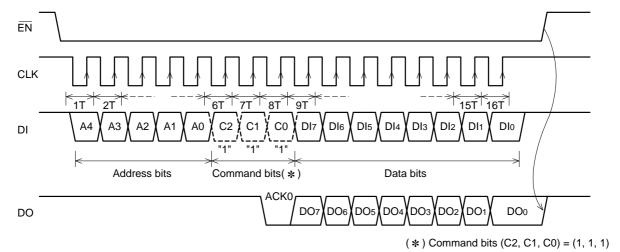

The timing at which microcomputer communicates with M66009 is as shown in the diagram below. When microcomputer accesses to M66009, it declares the start of access by lowering pin  $\overline{EN}$  status from "H" to "L". It then sends data to pins CLK and DI at the timing shown below. The access stops as pin  $\overline{EN}$  status rises from "L" to "H". Given below is more detailed explanation of data sending/receiving procedure:

- (1) At EN fall edge, 8-bit parallel data that arrives at input/output pins D0 thru D7 is loaded into shift register for serial output.

- (2) At CLK rise edge, data at pin DI is taken into serial input shift register, and internal clock counter starts counting up.

- (3) When 5-bit address is taken in, it is compared to address set by pins A0 thru A4. If they are the same, acknowledge bit "0" is output to pin DO synchronously with CLK 8T fall edge.

- (When the addresses are not the same, pin DO output status stays at the "H" level.)

- (4) When command bits C2, C1 and C0 are all "1", operation proceeds to (5) and (6) described below.

- If any of these command bits are not "1" while the addresses are the same, pin DO output is fixed to "H" synchronously with CLK 9T rise, and operation is halted until  $\overline{\text{EN}}$  rises. When  $\overline{\text{EN}}$  rises, clock counter is reset, and M66009 becomes ready to accept a next access.

- (5) When the addresses are the same and the command bits are all "1", serial output operation starts. Eight-bit data latched at step (1) as described above is output in series, starting from the bit at pin D7, through pin DO synchronously with the fall edges of CLK 9T thru 16T. No operation is performed for CLK inputs after 16T, except the count up of CLK.

- (6) When  $\overline{\text{EN}}$  rises: Output pin DO status is fixed to "H", and only when clock counter has counted 16 CLK rise edges (counter output =10H), the lower 8 bits of the 16-bit serial data is sent to output latch synchronously with the  $\overline{\text{EN}}$  rise edge. The latched data is inverted in logic, and output to pins D0 thru D7 in parallel. Clock counter is then reset, completing one sequence.

- (Note) If the clock counter output is not 10 H when  $\overline{\text{EN}}$  rises, data is not sent to output latch. Output pin DO is fixed to "H", clock counter is reset, and M66009 becomes ready to accept a next access.

**Data Communication protocol**

### 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

### **ACKNOWLEDGE BIT ACKO**

Acknowledge bit ACK0 is output only when address in serial input data is the same as that set by pins A0 thru A4. It is output from pin DO as ACK0 ="0" ("L") synchronously with CLK 8T fall.

### **INITIAL STATUS AFTER RESET**

If "L" is input to  $\overline{\text{RESET}}$ , M66009 is put in the conditions specified below:

| I/O pins D0 thru D7 | Input state ("L" output state) (Output p-channel transistor off) |

|---------------------|------------------------------------------------------------------|

| DO output           | "H" output state<br>(Output n-channel transistor off)            |

### **INPUT AND OUTPUT EQUIVALENT CIRCUITS**

# 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                |  | conditions | Ratings             | Unit |

|--------|--------------------------|--|------------|---------------------|------|

| Vcc    | Supply voltage           |  |            | −0.5 ~ <b>+</b> 7.0 | V    |

| Vı     | Input voltage            |  |            | −0.5 ~ VCC + 0.5    | V    |

| Vo     | Output voltage DO, D0~D7 |  |            | −0.5 ~ VCC + 0.5    | V    |

| Pd     | Power dissipation        |  |            | 500                 | mW   |

| Tstg   | Storage temperature      |  |            | <b>−</b> 65 ~ 150   | °C   |

# RECOMMENDED OPERATIONAL CONDITIONS

| Symbol | Paramete              |      | Unit |      |       |

|--------|-----------------------|------|------|------|-------|

| Symbol | Faramete              | Min. | Тур. | Max. | Offic |

| Vcc    | Supply voltage        | 4.5  |      | 5.5  | V     |

| Vı     | Input voltage         | 0    |      | Vcc  | V     |

| Vo     | Output voltage        | 0    |      | Vcc  | V     |

| Topr   | Operating temperature | -20  |      | 75   | °C    |

# **ELECTRICAL CHARACTERISTICS** (Ta = $-20 \sim 75^{\circ}$ C, Vcc = $5V \pm 10\%$ and GND = 0V unless otherwise noted)

| Symbol | Doromotor                        |              | Test conditions              | Limits  |      |      | 1.11  |      |

|--------|----------------------------------|--------------|------------------------------|---------|------|------|-------|------|

| Symbol | Parameter                        | Parameter    |                              | aitions | Min. | Тур. | Max.  | Unit |

| ViH    | "H" input voltage                |              | DI AO A4                     |         | 2.0  |      |       | V    |

| VIL    | "L" input voltage                |              | DI, A0~A4                    |         |      |      | 0.8   | V    |

| VIH    | "H" input voltage                |              | - D0~D7                      |         | 3.8  |      |       | V    |

| VIL    | "L" input voltage                |              | ולו~טו                       |         |      |      | 1.2   | V    |

| VT+    | Positive threshold voltage       |              |                              |         |      |      | 2.4   | V    |

| VT-    | Negative threshold voltage       |              | CLK, EN, RE                  | SET     | 0.7  |      |       | V    |

| Vh     | Hysteresis width                 |              | Ī !                          |         |      | 0.6  |       | V    |

| VoL    | "L" output voltage               | DO           | VI=VT+,VT-,<br>VCC=4.5V, IOI | _=4mA   |      |      | 0.4   | V    |

| Voн    | "H" output voltage               | D0~D7        | VI=VT+, VT-,<br>VCC=4.5V, IO | ⊣=–2mA  | 3.0  |      |       | V    |

| RD     | Pull-down resistance             | 20.27        | Vo=0~Vcc                     |         | 20   |      |       | kΩ   |

| Ru     | Pull-up resistance               | EN, CLK, DI  | VI=0~VCC                     |         | 20   |      |       | kΩ   |

| Iosh   | "H" output short circuit current | D0~D7        | Vo=0V, Vcc=5V                |         |      |      | -25   | mA   |

| lı     | Input current                    | RESET, A0~A4 | VI=0~VCC, VCC=5.5V           |         |      |      | ±5.0  | μΑ   |

| Io     | Output leak current              | DO           | Vo=0~Vcc,<br>Vcc=5.5V        |         |      |      | ±10.0 | μА   |

| Icc    | Static supply current            |              | VCC=5.5V,<br>output open     | VI=VCC  |      |      | 0.4   | mA   |

| 100    | Grand Supply Current             |              | D0~D7:<br>("L" output)       | Vi=GND  |      |      | 1.2   |      |

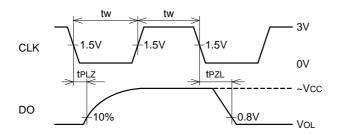

# **SWITCHING CHARACTERISTICS** (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V $\pm 10\%$ and GND = 0V)

| Cumbal | Parameter                     |             | Test conditions  | Limits |      |      | Linit |

|--------|-------------------------------|-------------|------------------|--------|------|------|-------|

| Symbol |                               |             |                  | Min.   | Тур. | Max. | Unit  |

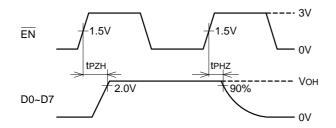

| tPZH   | Output "Z-H" propagation time | EN-D0~D7    | 0. 50 5 (1) ()   |        |      | 1.0  | μs    |

| tPHZ   | Output "H-Z" propagation time | LIN-DO~D7   | CL=50pF (Note 1) |        |      | 2.0  | μs    |

| tPZL   | Output "Z-L" propagation time | CLK-D0      | CL=50pF,         |        |      | 350  | ns    |

| tPLZ   | Output "L-Z" propagation time | CLK-DU      | RL=2kΩ (Note 1)  |        |      | 350  | ns    |

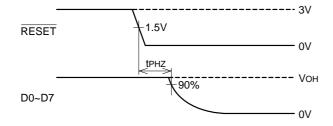

| tphz   | Output "H-Z" propagation time | RESET-D0~D7 | CL=50pF (Note 1) |        | ·    | 2.0  | μs    |

# 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

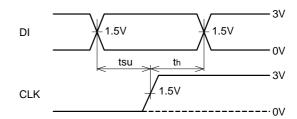

# **TIMING CONDITIONS**

| Cymhal | Symbol Parameter           |          | Test conditions | Limits |      |      | Llait |

|--------|----------------------------|----------|-----------------|--------|------|------|-------|

| Symbol |                            |          |                 | Min.   | Тур. | Max. | Unit  |

| tw     | CLK, EN, RESET pulse width |          |                 | 250    |      |      | ns    |

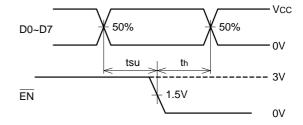

|        |                            | DI-CLK   |                 | 120    |      |      | ns    |

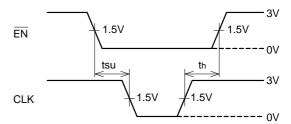

| tsu    | Setup time                 | EN-CLK   | (Note 1)        | 120    |      |      |       |

|        |                            | D0~D7-EN |                 | 120    |      |      |       |

|        |                            | DI-CLK   |                 | 120    |      |      |       |

| th     | Hold time                  | EN-CLK   |                 | 120    |      |      |       |

|        |                            | D0~D7-EN |                 | 120    |      |      |       |

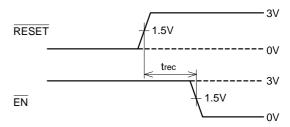

| trec   | Recovery time              | EN-RESET |                 | 120    |      |      | ns    |

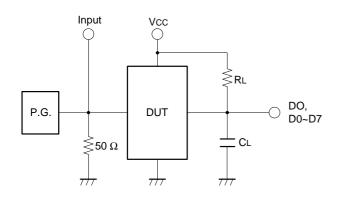

# **NOTE 1: TEST CIRCUIT**

- (1) Pulse generator (PG) characteristics:  $t_r = t_f = 6ns$  (10%–90%)

- (2) Capacitance CL includes connection floating capacitance and probe input capacitance.

# 8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

### **TIMING CHARTS**

8-BIT I/O EXPANDER WITH 5-BIT ADDRESS

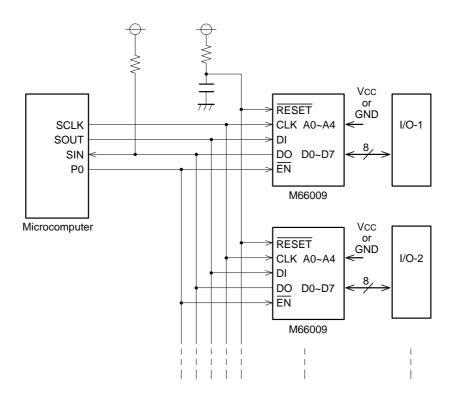

# **APPLICATION EXAMPLE**